Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# TLE7276-2

5-V Low Dropout Voltage Regulator

**Automotive Power**

#### 5-V Low Dropout Voltage Regulator

TLE7276-2

### 1 Overview

#### **Features**

- Ultra Low Current Consumption 20 μA

- Output Voltage 5 V ±2%

- Output Current up to 300 mA

- Enable Input

- Very Low Dropout Voltage

- · Output Current Limitation

- · Overtemperature Shutdown

- Wide Temperature Range From -40 °C up to 150 °C

- Green Product (RoHS compliant)

- AEC Qualified

#### **Description**

The TLE7276-2 is a monolithic integrated low dropout voltage regulator for load currents up to 300 mA. An input voltage up to 42 V is regulated to  $V_{\rm Q,nom}$  = 5.0 V with a precision of  $\pm 2\%$ . The sophisticated design allows to achieve stable operation even with ceramic output capacitors down to 470 nF. The device is designed for the harsh environment of automotive applications. Therefore it is protected against overload, short circuit and overtemperature conditions by the implemented output current limitation and the overtemperature shutdown circuit. The TLE7276-2 can be also used in all other applications requiring a stabilized 5 V voltage.

PG-SSOP-14 Exposed Pad

PG-TO252-5

Due to its ultra low quiescent current of typically 20  $\mu$ A the TLE7276-2 is dedicated for use in applications permanently connected to  $V_{\rm BAT}$ . In addition the device can be switched off via the Enable input reducing the current consumption to typically 5  $\mu$ A. An integrated output sink current circuitry keeps the voltage at the Output pin Q below 5.5 V even in case of occuring reverse currents. Thus connected devices are protected from overvoltage damage. For applications requiring extremely low noise levels the Infineon voltage regulator family TLE 42XX and TLE 44XX is more suited than the TLE7276-2. A mV-range output noise on the TLE7276-2 caused by the charge pump operation is unavoidable due to the ultra low quiescent current concept.

| Туре       | Package                | Marking |

|------------|------------------------|---------|

| TLE7276-2E | PG-SSOP-14 Exposed Pad | 7276-2E |

| TLE7276-2D | PG-TO252-5             | 7276-2D |

Data Sheet 2 Rev. 1.0, 2009-06-01

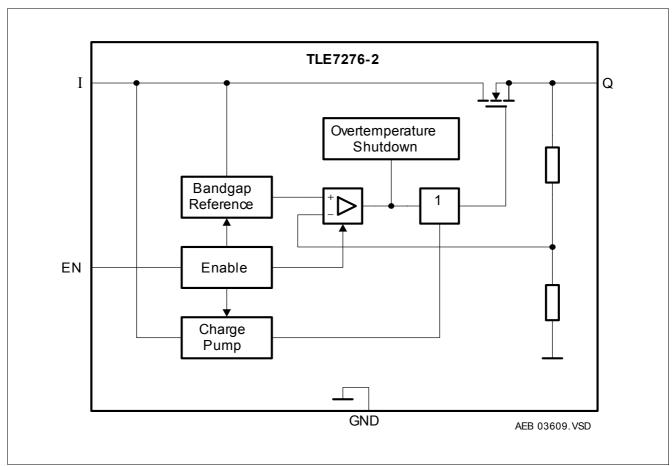

**Block Diagram**

## 2 Block Diagram

Figure 1 Block Diagram

**Pin Configuration**

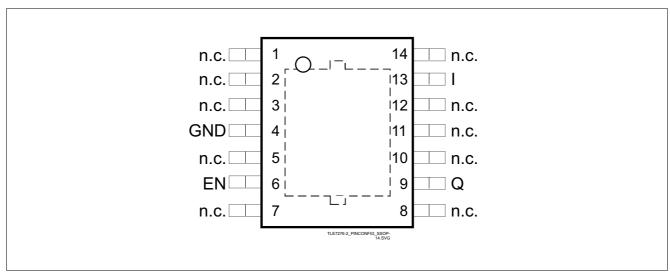

## 3 Pin Configuration

## 3.1 Pin Assignment PG-SSOP-14 Exposed Pad

Figure 2 Pin Configuration (top view)

## 3.2 Pin Definitions and Functions PG-SSOP-14 Exposed Pad

| Pin No.       | Symbol | Function                                                                                |

|---------------|--------|-----------------------------------------------------------------------------------------|

| 1,2,3,5,7     | n.c.   | non connected                                                                           |

|               |        | can be open or connected to GND                                                         |

| 4             | GND    | Ground                                                                                  |

| 6             | EN     | Enable Input                                                                            |

|               |        | high level input signal enables the IC;                                                 |

|               |        | low level input signal disables the IC;                                                 |

|               |        | integrated pull-down resistor                                                           |

| 8,10,11,12,14 | n.c.   | non connected                                                                           |

|               |        | can be open or connected to GND                                                         |

| 9             | Q      | Output                                                                                  |

|               |        | block to ground with a capacitor close to the IC terminals, respecting the values given |

|               |        | for its capacitance and ESR in "Functional Range" on Page 6                             |

| 13            | I      | Input                                                                                   |

|               |        | block to ground directly at the IC with a ceramic capacitor                             |

| Pad           | _      | Exposed Pad                                                                             |

|               |        | connect to GND and heatsink area                                                        |

**Pin Configuration**

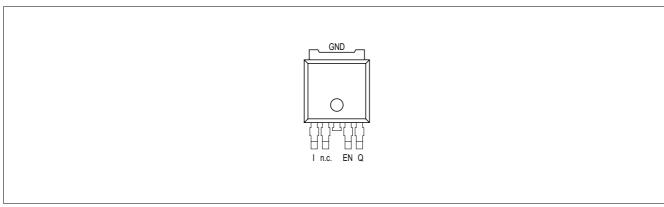

## 3.3 Pin Assignment PG-TO252-5

Figure 3 Pin Configuration (top view)

### 3.4 Pin Definitions and Functions PG-TO252-5

| Pin No.   | Symbol | Function                                                                                |

|-----------|--------|-----------------------------------------------------------------------------------------|

| 1         | I      | Input                                                                                   |

|           |        | block to ground directly at the IC with a ceramic capacitor                             |

| 2         | n.c.   | non connected                                                                           |

|           |        | can be open or connected to GND                                                         |

| 3         | GND    | Ground                                                                                  |

|           |        | internally connected to heat slug                                                       |

| 4         | EN     | Enable Input                                                                            |

|           |        | high level input signal enables the IC;                                                 |

|           |        | low level input signal disables the IC;                                                 |

|           |        | integrated pull-down resistor                                                           |

| 5         | Q      | Output                                                                                  |

|           |        | block to ground with a capacitor close to the IC terminals, respecting the values given |

|           |        | for its capacitance and ESR in "Functional Range" on Page 6                             |

| Heat Slug | _      | Heat Slug                                                                               |

|           |        | internally connected to GND;                                                            |

|           |        | connect to GND and heatsink area                                                        |

**General Product Characteristics**

### 4 General Product Characteristics

### 4.1 Absolute Maximum Ratings

### Absolute Maximum Ratings<sup>1)</sup>

$T_i$  = -40 °C to 150 °C; all voltages with respect to ground, (unless otherwise specified)

| Pos.    | Parameter                                | Symbol    | Lin  | nit Values   | Unit | Test Condition          |

|---------|------------------------------------------|-----------|------|--------------|------|-------------------------|

|         |                                          |           | Min. | Max.         |      |                         |

| Input I |                                          |           | 1    |              | "    | 1                       |

| 4.1.1   | Voltage                                  | $V_1$     | -0.3 | 45           | V    | _                       |

| Output  | Q                                        | *         | *    | <del>-</del> |      |                         |

| 4.1.2   | Voltage                                  | $V_{Q}$   | -0.3 | 6            | V    | _                       |

| 4.1.3   | Voltage                                  | $V_{Q}$   | -0.3 | 6.2          | V    | $t < 10 \text{ s}^{2)}$ |

| Enable  | Input EN                                 | -         | *    | <u> </u>     |      |                         |

| 4.1.4   | Voltage                                  | $V_{EN}$  | -0.3 | 45           | V    | _                       |

| Tempe   | rature                                   | <u> </u>  |      |              |      |                         |

| 4.1.5   | Junction temperature                     | $T_{j}$   | -40  | 150          | °C   | _                       |

| 4.1.6   | Storage temperature                      | $T_{stg}$ | -50  | 150          | °C   | _                       |

| ESD St  | sceptibility                             | •         |      |              |      |                         |

| 4.1.7   | Human Body Model (HBM) <sup>3)</sup>     | Voltage   | -    | 3            | kV   | _                       |

| 4.1.8   | Charged Device Model (CDM) <sup>4)</sup> | Voltage   | -    | 1.5          | kV   | _                       |

- 1) not subject to production test, specified by design

- 2) exposure to these absolute maximum ratings for extended periods (t > 10 s) may affect device reliability

- 3) ESD susceptibility Human Body Model "HBM" according to AEC-Q100-002 JESD22-A114

- 4) ESD susceptibility Charged Device Model "CDM" according to ESDA STM5.3.1

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

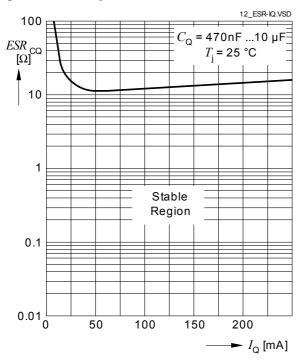

### 4.2 Functional Range

| Pos.  | Parameter            | Symbol       | Lim  | it Values | Unit | Remarks |

|-------|----------------------|--------------|------|-----------|------|---------|

|       |                      |              | Min. | Max.      |      |         |

| 4.2.1 | Input voltage        | $V_1$        | 5.5  | 42        | V    | _       |

| 4.2.2 | Output Capacitor's   | $C_{Q}$      | 470  | _         | nF   | 1)      |

| 4.2.3 | Requirements         | $ESR(C_{Q})$ | _    | 10        | Ω    | 2)      |

| 4.2.4 | Junction temperature | $T_{i}$      | -40  | 150       | °C   | _       |

<sup>1)</sup> the minimum output capacitance requirement is applicable for a worst case capacitance tolerance of 30%

Note: Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

<sup>2)</sup> relevant ESR value at f = 10 kHz

#### **General Product Characteristics**

### 4.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

| Pos.  | Parameter                         | Symbol     | 1    | Limit Val | ues  | Unit     | Conditions                          |

|-------|-----------------------------------|------------|------|-----------|------|----------|-------------------------------------|

|       |                                   |            | Min. | Тур.      | Max. |          |                                     |

| TLE72 | 76-2E (PG-SSOP-14 Exposed         | Pad)       | - 1  |           |      | <u> </u> |                                     |

| 4.3.1 | Junction to Case <sup>1)</sup>    | $R_{thJC}$ | _    | 14        | _    | K/W      | measured to exposed pad             |

| 4.3.2 | Junction to Ambient <sup>1)</sup> | $R_{thJA}$ | _    | 47        | _    | K/W      | 2)                                  |

| 4.3.3 |                                   | $R_{thJA}$ | _    | 141       | _    | K/W      | footprint only <sup>3)</sup>        |

| 4.3.4 |                                   | $R_{thJA}$ | _    | 66        | _    | K/W      | 300 mm² heatsink area <sup>3)</sup> |

| 4.3.5 |                                   | $R_{thJA}$ | _    | 56        | _    | K/W      | 600 mm² heatsink area <sup>3)</sup> |

| TLE72 | 76-2D (PG-TO252-5)                | 1          | - 1  |           |      | <u> </u> |                                     |

| 4.3.1 | Junction to Case <sup>1)</sup>    | $R_{thJC}$ | _    | 6         | _    | K/W      | measured to tab                     |

| 4.3.2 | Junction to Ambient <sup>1)</sup> | $R_{thJA}$ | _    | 32        | _    | K/W      | 2)                                  |

| 4.3.3 |                                   | $R_{thJA}$ | _    | 115       | _    | K/W      | footprint only <sup>3)</sup>        |

| 4.3.4 |                                   | $R_{thJA}$ | -    | 62        | -    | K/W      | 300 mm² heatsink area <sup>3)</sup> |

| 4.3.5 |                                   | $R_{thJA}$ | _    | 47        | _    | K/W      | 600 mm² heatsink area <sup>3)</sup> |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Specified R<sub>thJA</sub> value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm³ board with 2 inner copper layers (2 x 70μm Cu, 2 x 35μm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

<sup>3)</sup> Specified  $R_{\text{thJA}}$  value is according to Jedec JESD 51-3 at natural convection on FR4 1s0p board; The Product (Chip+Package) was simulated on a 76.2  $\times$  114.3  $\times$  1.5 mm³ board with 1 copper layer (1 x 70 $\mu$ m Cu).

## **5** Electrical Characteristics

## 5.1 Electrical Characteristics Voltage Regulator

#### **Electrical Characteristics**

$V_{\rm i}$ =13.5 V;  $T_{\rm i}$  = -40 °C to 150 °C; all voltages with respect to ground (unless otherwise specified)

| Pos.   | Parameter                                   | Symbol                 | Limit Values |      |      | Unit | <b>Measuring Condition</b>                                                     |  |

|--------|---------------------------------------------|------------------------|--------------|------|------|------|--------------------------------------------------------------------------------|--|

|        |                                             |                        | Min.         | Тур. | Max. |      |                                                                                |  |

| Output | Q                                           | "                      |              |      |      | - 1  |                                                                                |  |

| 5.1.1  | Output Voltage                              | $V_{Q}$                | 4.9          | 5.0  | 5.1  | V    | 0.1 mA < I <sub>Q</sub> <300 mA<br>6 V < V <sub>I</sub> < 16 V                 |  |

| 5.1.2  | Output Voltage                              | $V_{Q}$                | 4.9          | 5.0  | 5.1  | V    | 0.1 mA < I <sub>Q</sub> <100 mA<br>6 V < V <sub>I</sub> < 40 V                 |  |

| 5.1.3  | Dropout Voltage                             | $V_{dr}$               | _            | 250  | 500  | mV   | $I_{\rm Q}$ = 200 mA<br>$V_{\rm dr} = V_{\rm I} - V_{\rm Q}^{-1}$              |  |

| 5.1.4  | Load Regulation                             | $\Delta V_{ m Q,  lo}$ | - 40         | 15   | 40   | mV   | $I_{\rm Q}$ = 5 mA to 250 mA                                                   |  |

| 5.1.5  | Line Regulation                             | $\Delta V_{Q, li}$     | - 20         | 5    | 20   | mV   | $V_{\rm I}$ = 10 V to 32 V<br>$I_{\rm Q}$ = 5 mA                               |  |

| 5.1.6  | Output Current Limitation                   | $I_{Q}$                | 301          | _    | _    | mA   | 1)                                                                             |  |

| 5.1.7  | Output Current Limitation                   | $I_{Q}$                | _            | _    | 800  | mA   | $V_{Q} = 0V$                                                                   |  |

| 5.1.8  | Power Supply Ripple Rejection <sup>2)</sup> | PSRR                   | _            | 60   | _    | dB   | $f_{\rm r}$ = 100 Hz; $V_{\rm r}$ = 0.5 Vpp                                    |  |

| 5.1.9  | Temperature Output Voltage Drift            | $\frac{dV_{Q}}{dT}$    | _            | 0.5  | -    | mV/K | -                                                                              |  |

| Curren | t Consumption                               |                        |              |      |      | - 1  |                                                                                |  |

| 5.1.10 | Quiescent Current $I_{q} = I_{1} - I_{Q}$   | $I_{q}$                | _            | 20   | 30   | μΑ   | $I_{\rm Q}$ = 0.1 mA; $V_{\rm EN}$ = 5 V $T_{\rm i}$ = 25 °C                   |  |

| 5.1.11 | Quiescent Current $I_{q} = I_{l} - I_{Q}$   | $I_{q}$                | _            | -    | 40   | μΑ   | $I_{\rm Q}$ = 0.1 mA; $V_{\rm EN}$ = 5 V<br>$T_{\rm j} \le 80~{\rm ^{\circ}C}$ |  |

| 5.1.12 | Current Consumption, Regulator Disabled     | $I_{q}$                | _            | 5    | 9    | μA   | $V_{\rm EN}$ = 0 V; $T_{\rm j}$ < 80°C                                         |  |

<sup>1)</sup> Measured when the output voltage  $V_{\rm Q}$  has dropped 100 mV from the nominal value obtained at  $V_{\rm I}$  = 13.5 V.

<sup>2)</sup> not subject to production test, specified by design

## 5.2 Typical Performance Characteristics Voltage Regulator

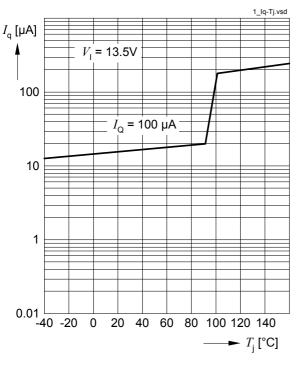

# Current Consumption $I_{\rm q}$ versus Junction Temperature $T_{\rm J}$

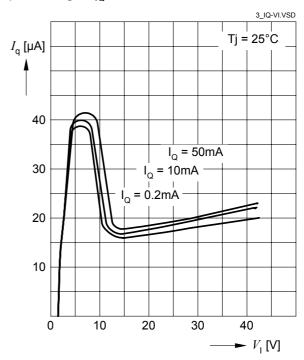

# Current Consumption $I_{\rm q}$ versus Input Voltage $V_{\rm IQ}$

# Current Consumption $I_{\rm q}$ versus Output Current $I_{\rm Q}$

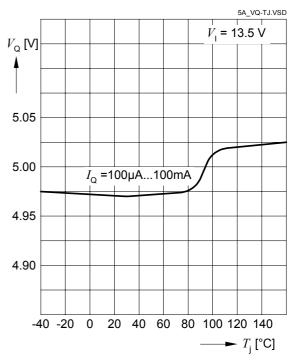

# Output Voltage $V_{\rm Q}$ versus Junction Temperature $T_{\rm J}$

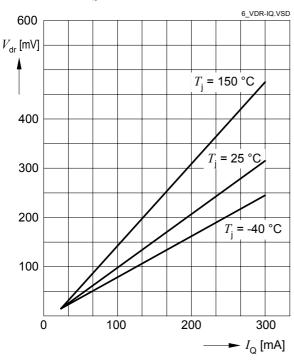

# Dropout Voltage $V_{\mathrm{dr}}$ versus Output Current $I_{\mathrm{Q}}$

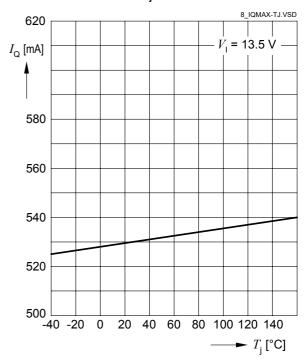

# Maximum Output Current $I_{\rm Q}$ versus Junction Temperature $T_{\rm i}$

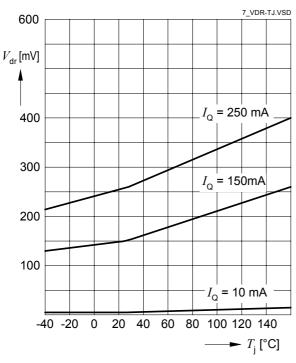

# Dropout Voltage $V_{\mathrm{dr}}$ versus Junction Temperature

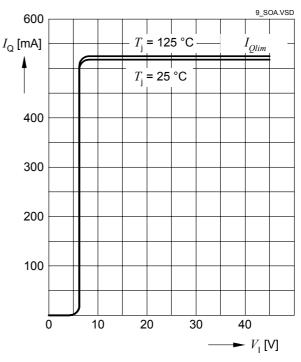

# Maximum Output Current $I_{\mathrm{Q}}$ versus Input Voltage $V_{\mathrm{I}}$

#### **Region of Stability**

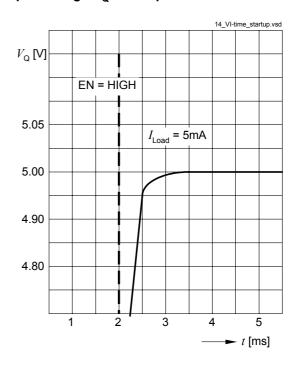

### Output Voltage $V_{\mathsf{Q}}$ Start-up behavior

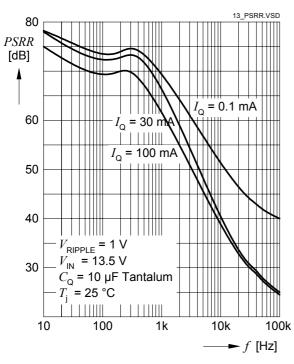

# Power Supply Ripple Rejection PSRR versus Frequency f

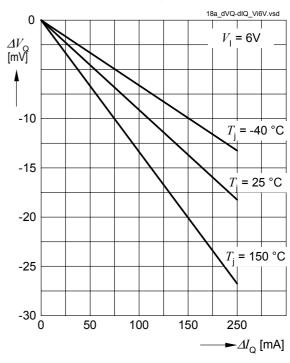

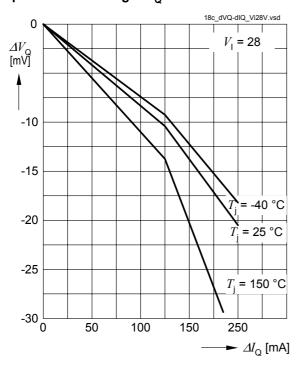

# Load Regulation $\Delta V_{\rm Q}$ versus Output Current Change $\Delta I_{\rm Q}$

# Load Regulation $\Delta V_{ m Q}$ versus Output Current Change $dI_{ m Q}$

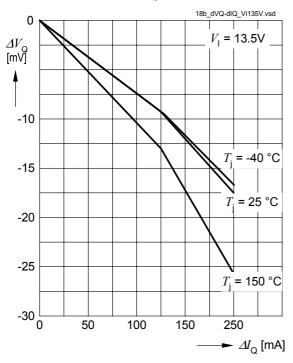

# Load Regulation $\Delta V_{\rm Q}$ versus Output Current Change $\Delta I_{\rm Q}$

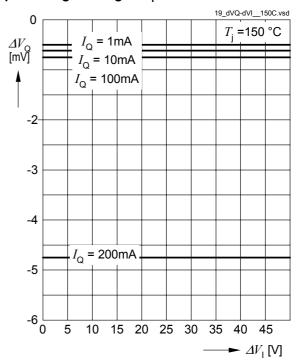

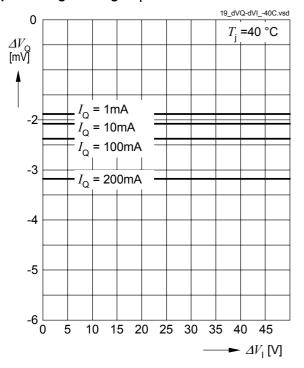

# Line Regulation $\Delta V_{\mathrm{Q}}$ versus Input Voltage Changed $V_{\mathrm{I}}$

# Line Regulation $\Delta V_{\mathrm{Q}}$ versus Input Voltage Changed $V_{\mathrm{I}}$

# Line Regulation $\Delta V_{\rm Q}$ versus Input Voltage Change $V_{\rm I}$

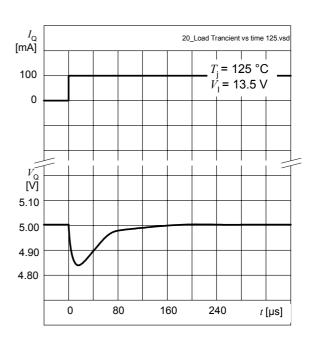

### Load Transient Response Peak Voltage $\Delta V_{ m Q}$

Load Transient Response Peak Voltage  $\Delta V_{

m Q}$

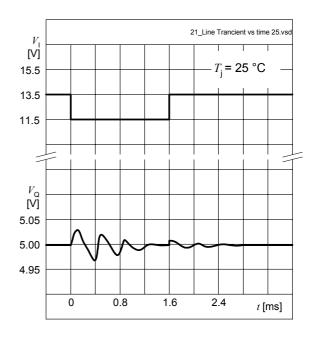

Line Transient Response Peak Voltage  $\Delta V_{\mathrm{Q}}$

## Line Transient Response Peak Voltage $\Delta V_{\mathrm{Q}}$

I

#### **5.3** Electrical Characteristics Enable Function

The Enable Function allows disabling/enabling the regulator via the input pin EN. The regulator is turned on in case the pin EN is connected to a voltage higher than **VEN,H**. This can be e.g. the battery voltage, whereby no additional pull-up resistor is needed. The regulator can be turned off by connecting the pin EN to a voltage less than **VEN,L**, e.g. GND.

Electrical Characteristics Enable  $V_i$ =13.5 V;  $T_j$  = -40 °C to 150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                | Symbol     | Limit Values |      |      | Unit | <b>Measuring Condition</b>   |

|--------|--------------------------|------------|--------------|------|------|------|------------------------------|

|        |                          |            | Min.         | Тур. | Max. |      |                              |

| 5.3.13 | High Level Input Voltage | $V_{EN,H}$ | 3.1          | _    | _    | V    | <i>V</i> <sub>Q</sub> ≥4.9 V |

| 5.3.14 | Low Level Input Voltage  | $V_{EN,L}$ | _            | _    | 8.0  | V    | <i>V</i> <sub>Q</sub> ≤0.3 V |

| 5.3.15 | High Level Input Current | $I_{EN,H}$ | _            | 3    | 4    | μΑ   | V <sub>EN</sub> = 5 V        |

### 5.4 Typical Performance Characteristics Enable Function

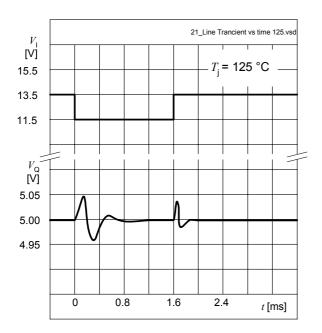

# Enabled Input Current $I_{\mathrm{EN}}$ versus Input Voltage $V_{\mathrm{I}}$ , EN=Off

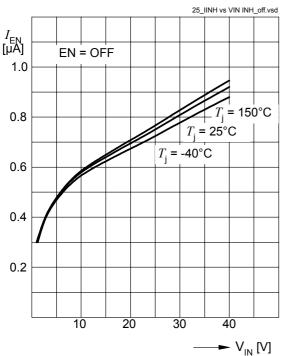

# Enabled Input Current $I_{\rm EN}$ versus Enabled Input Voltage $V_{\rm EN}$

**Package Outlines**

## 6 Package Outlines

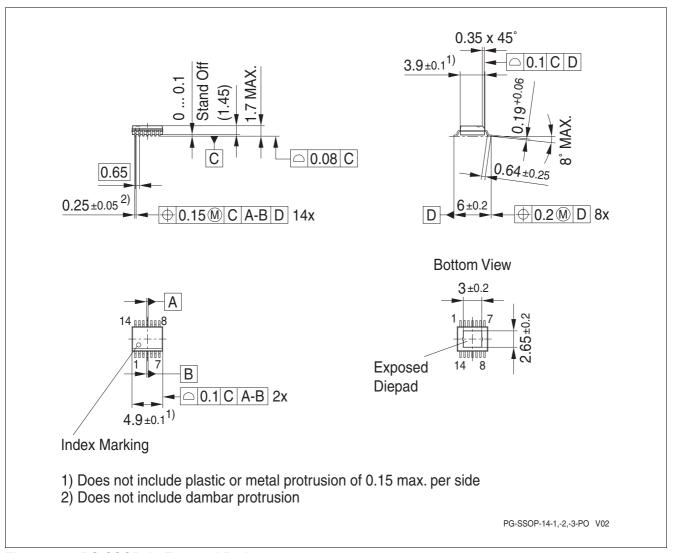

Figure 4 PG-SSOP-14 Exposed Pad

**Package Outlines**

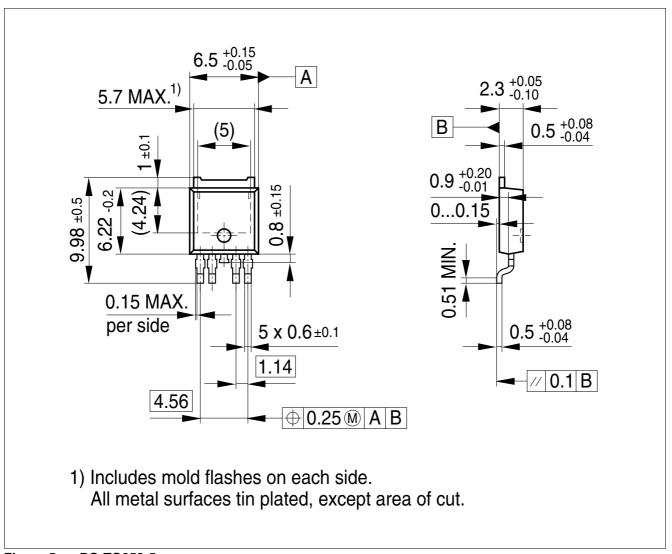

Figure 5 PG-TO252-5

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

**Revision History**

# 7 Revision History

| Revision | Date       | Changes                    |

|----------|------------|----------------------------|

| 1.0      | 2009-06-01 | initial version data sheet |

#### Edition 2009-06-01

Published by Infineon Technologies AG 81726 Munich, Germany © 2009 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.