Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **TLE75242-ESD**

# SPIDER+ 12V

**SPI Driver for Enhanced Relay Control**

| Package | PG-TSDSO-24-21 |

|---------|----------------|

| Marking | TLE75242ESD    |

# 1 Overview

#### **Applications**

- Low-side and High-side switches for 12 V in automotive or industrial applications such as lighting, heating, motor driving, energy and power distribution

- Especially designed for driving relays, LEDs and motors.

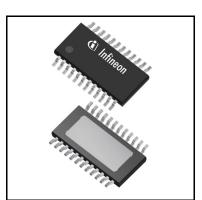

Figure 1 TLE75242-ESD Application Diagram

### TLE75242-ESD SPIDER+ 12V

# infineon

#### Overview

#### **Basic Features**

- 16-bit serial peripheral interface for control and diagnosis

- Daisy Chain capability SPI also compatible with 8-bit SPI devices

- 2 CMOS compatible parallel input pins with Input Mapping functionality

- Cranking capability down to V<sub>S</sub> = 3.0 V (supports LV124)

- Digital supply voltage range compatible with 3.3 V and 5 V microcontrollers

- Independend supply pin (V<sub>S HS</sub>) for high-side channels

- · Very low quiescent current (with usage of IDLE pin)

- Limp Home mode (with usage of IDLE and IN pins)

- Green Product (RoHS compliant)

- · AEC Qualified

#### **Protection Features**

- Reverse battery protection on V<sub>s</sub> without external components

- Short circuit to ground and battery protection

- Stable behavior at under voltage conditions ("Lower Supply Voltage Range for Extended Operation")

- Over Current latch OFF

- · Thermal shutdown latch OFF

- Overvoltage protection

- Loss of ground protection

- Loss of battery protection

- Electrostatic discharge (ESD) protection

#### **Diagnostic Features**

- · Latched diagnostic information via SPI register

- Over Load detection at ON state

- Open Load detection at OFF state using Output Status Monitor function

- Output Status Monitor

- Input Status Monitor

#### **Application Specific Features**

- Fail-safe activation via Input pins in Limp-Home Mode

- SPI with Daisy Chain capability

- Safe operation at low battery voltage (cranking)

- One supply pin for high-side switches independent from main supply pin  $V_{\rm S}$

#### **Description**

The TLE75242-ESD is an eight channel low-side and high-side power switch in PG-TSDSO-24-21 package providing embedded protective functions. It is specially designed to control relays and LEDs in automotive and industrial applications.

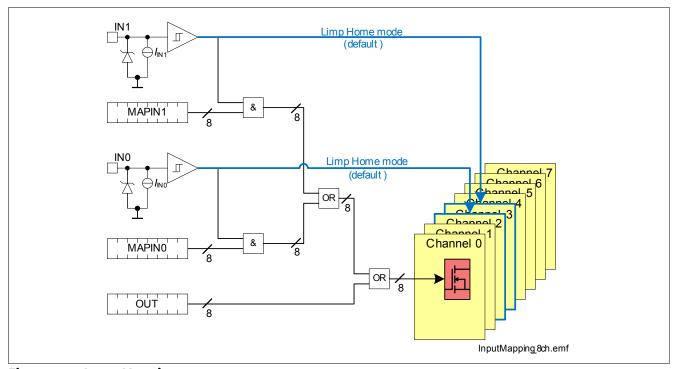

A serial peripheral interface (SPI) is utilized for control and diagnosis of the loads as well as of the device. For direct control and PWM there are two input pins available connected to two outputs by default. Additional or different outputs can be controlled by the same input pins (programmable via SPI).

### TLE75242-ESD SPIDER+ 12V

# infineon

#### Overview

Table 1 Product Summary

| Parameter                                                   | Symbol                                    | Values                                    |  |  |

|-------------------------------------------------------------|-------------------------------------------|-------------------------------------------|--|--|

| Analog supply voltage                                       | V <sub>S</sub>                            | 3.0 V 28 V                                |  |  |

| Digital supply voltage                                      | $V_{DD}$                                  | 3.0 V 5.5 V                               |  |  |

| Minimum overvoltage protection                              | $V_{S(AZ)}$                               | 42 V (see <b>Chapter 8.5</b> for details) |  |  |

| Maximum on-state resistance at $T_J = 150 ^{\circ}\text{C}$ | R <sub>DS(ON)</sub>                       | 2.2 Ω                                     |  |  |

| Nominal load current ( $T_A = 85$ °C, all channels)         | I <sub>L(NOM)</sub>                       | 330 mA                                    |  |  |

| Maximum Energy dissipation - repetitive                     | E <sub>AR</sub>                           | 10 mJ @ I <sub>L(EAR)</sub> = 220 mA      |  |  |

| Minimum Drain to Source clamping voltage                    | V <sub>DS(CL)</sub>                       | 42 V (when used as low-side switches)     |  |  |

| Maximum Source to Ground clamping voltage                   | $V_{\text{OUT\_S(CL)}}V_{\text{OUT(CL)}}$ | -16 V                                     |  |  |

| Maximum overload switch OFF threshold                       | I <sub>L(OVL0)</sub>                      | 2.3 A                                     |  |  |

| Maximum total quiescent current at T <sub>J</sub> ≤ 85 °C   | I <sub>SLEEP</sub>                        | 5 μΑ                                      |  |  |

| Maximum SPI clock frequency                                 | f <sub>SCLK</sub>                         | 5 MHz                                     |  |  |

#### **Detailed Description**

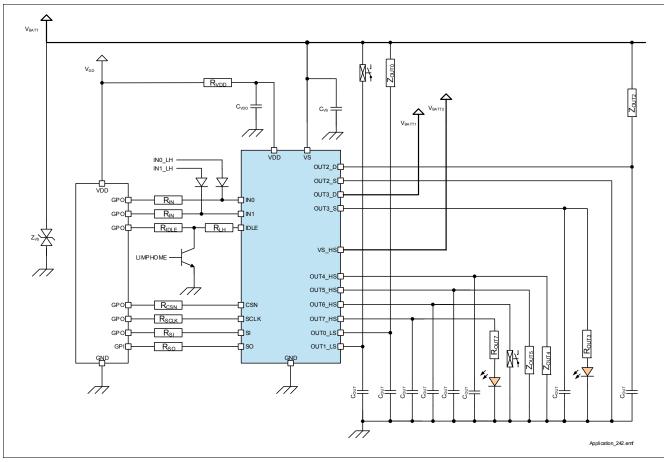

The TLE75242-ESD is an eight channel low-side and high-side switch providing embedded protective functions. The output stages incorporate two low-side, four high-side and two auto-configurable high-side or low-side switches (typical  $R_{\rm DS(ON)}$  at  $T_{\rm J}$  = 25°C is 1  $\Omega$ ). The auto-configurable switches can be utilized in high-side or low-side configuration just by connecting the load accordingly. Protection and diagnosis functions adjust automatically to the hardware configuration.

The 16-bit serial peripheral interface (SPI) is utilized to control and diagnose the device and the loads. The SPI interface provides daisy chain capability in order to assemble multiple devices (also devices with 8 bit SPI) in one SPI chain by using the same number of microcontroller pins.

This device is designed for low supply voltage operation, therefore being able to keep its state at low battery voltage ( $V_S \ge 3.0 \text{ V}$ ). The SPI functionality, including the possibility to program the device, is available only when the digital power supply is present (see **Chapter 6** for more details).

The TLE75242-ESD is equipped with two input pins that are connected to two configurable outputs, making them controllable even when the digital supply voltage is not available. With the Input Mapping functionality it is possible to connect the input pins to different outputs, or assign more outputs to the same input pin. In this case more channels can be controlled with one signal applied to one input pin.

In Limp Home mode (Fail-Safe mode) the input pins are directly routed to channels 2 and 3. When IDLE pin is "low", it is possible to activate the two channels using the input pins independently from the presence of the digital supply voltage.

The device provides diagnosis of the load via Open Load at OFF state (with **DIAG\_OSM.OUTn** bits) and short circuit detection. For Open Load at OFF state detection, a internal current source  $I_{OL}$  can be activated via SPI.

Each output stage is protected against short circuit. In case of Overload, the affected channel switches OFF when the Overload Detection Current  $I_{L(OVLn)}$  is reached and can be reactivated via SPI. In Limp Home mode operation, the channels connected to an input pin set to "high" restart automatically after Output Restart time  $t_{RETRY(LH)}$  is elapsed. Temperature sensors are available for each channel to protect the device against Over Temperature.

The power transistors are built by N-channel power MOSFET with one central chargepump for autoconfigurable and high-side channels. The inputs are ground referenced TTL compatible. The device is monolithically integrated in Smart Power Technology.

#### **Block Diagram and Terms**

# 2 Block Diagram and Terms

# 2.1 Block Diagram

Figure 2 Block Diagram of TLE75242-ESD

# infineon

#### **Block Diagram and Terms**

#### 2.2 Terms

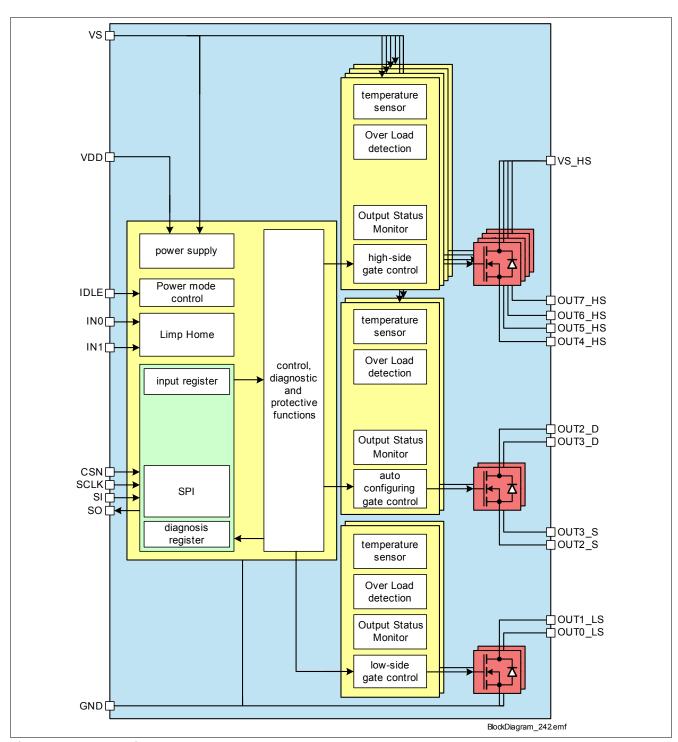

Figure 3 shows all terms used in this data sheet, with associated convention for positive values.

Figure 3 Voltage and Current definition

In all tables of electrical characteristics the channel related symbols without channel numbers are valid for each channel separately (e.g.  $V_{DS}$  specification is valid for  $V_{DS0}$  ...  $V_{DS7}$ ).

Furthermore, parameters relative to output current can be indicated without specifying whether the current is going into the Drain pin or going out of the Source pin, unless otherwise specified. For instance, nominal output current can be indicated in the following ways:  $I_{L(NOM)}$   $I_{L_LS(NOM)}$   $I_{L_LS(NOM)}$

All SPI registers bits are marked as follows: ADDR.PARAMETER (e.g. HWCR.RST) with the exception of the bits in the Diagnosis frames which are marked only with PARAMETER (e.g. UVRVS).

#### **Pin Configuration**

# **3** Pin Configuration

# 3.1 Pin Assignment

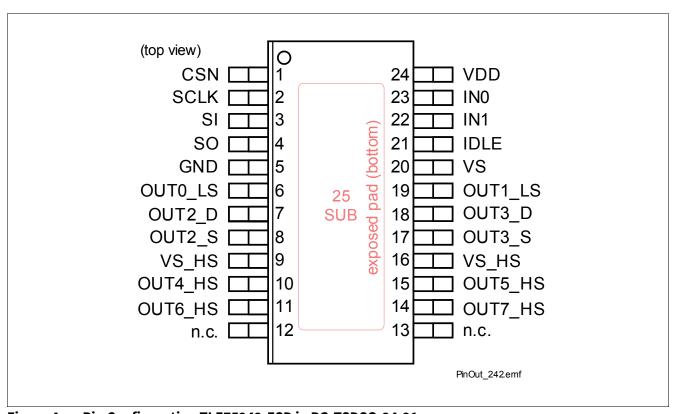

Figure 4 Pin Configuration TLE75242-ESD in PG-TSDSO-24-21

# **Pin Configuration**

# 3.2 Pin Definitions and Functions

| Pin       | Symbol        | I/O | Function                                                                                                           |

|-----------|---------------|-----|--------------------------------------------------------------------------------------------------------------------|

| Power Sup | ply Pins      |     |                                                                                                                    |

| 20        | VS            | _   | Analog supply $V_S$ Positive supply voltage for power switches gate control (incl. protections)                    |

| 9, 16     | VS_HS         | -   | Analog supply V <sub>s_Hs</sub> Positive supply voltage for power switches drain current                           |

| 24        | VDD           | _   | <b>Digital supply <math>V_{DD}</math></b> Supply voltage for SPI with support function to $V_{S}$                  |

| 5         | GND           | _   | <b>Ground</b> Ground connection (also for the low-side switches)                                                   |

| SPI Pins  |               |     |                                                                                                                    |

| 1         | CSN           | I   | Chip Select "low" active, integrated pull-up to $V_{\rm DD}$                                                       |

| 2         | SCLK          | 1   | Serial Clock "high" active, integrated pull-down to ground                                                         |

| 3         | SI            | I   | Serial Input "high" active, integrated pull-down to ground                                                         |

| 4         | so            | 0   | Serial Output "Z" (tri-state) when CSN is "high"                                                                   |

| Input and | Stand-by Pins |     |                                                                                                                    |

| 21        | IDLE          | I   | Idle mode power mode control, "high" activates Idle mode, integrated pull-down to ground                           |

| 23        | INO           | I   | Input pin 0 connected to channel 2 by default and in Limp Home mode, "high" active, integrated pull-down to ground |

| 22        | IN1           | I   | Input pin 1 connected to channel 3 by default and in Limp Home mode, "high" active, integrated pull-down to ground |

| Power Oup | out Pins      |     |                                                                                                                    |

| 6         | OUT0_LS       | 0   | Drain of low-side power transistor (channel 0)                                                                     |

| 7         | OUT2_D        | 0   | Drain of auto configurable power transistor (channel 2)                                                            |

| 8         | OUT2_S        | 0   | Source of auto configurable power transistor (channel 2)                                                           |

| 17        | OUT3_S        | 0   | Source of auto configurable power transistor (channel 3)                                                           |

| 18        | OUT3_D        | 0   | Drain of auto configurable power transistor (channel 3)                                                            |

| 19        | OUT1_LS       | 0   | Drain of low-side power transistor (channel 1)                                                                     |

| 10        | OUT4_HS       | 0   | Source of high-side power transistor (channel 4)                                                                   |

| 11        | OUT6_HS       | 0   | Source of high-side power transistor (channel 6)                                                                   |

| 14        | OUT7_HS       | 0   | Source of high-side power transistor (channel 7)                                                                   |

| -         |               |     |                                                                                                                    |

# TLE75242-ESD SPIDER+ 12V

### **Pin Configuration**

| Pin                              | Symbol  | I/O | Function                                                                                                                                                              |  |  |  |

|----------------------------------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15                               | OUT5_HS | 0   | Source of high-side power transistor (channel 5)                                                                                                                      |  |  |  |

| Not Connected pins / Cooling Tab |         |     |                                                                                                                                                                       |  |  |  |

| 12, 13                           | n.c.    | -   | Not Connected, internally not bonded                                                                                                                                  |  |  |  |

| 25                               | GND     | -   | <b>Exposed pad</b> It is recommended to connect it to PCB ground for cooling and EMC - not usable as electrical GND pin. Electrical ground must be provided by pin 5. |  |  |  |

# infineon

#### **General Product Characteristics**

### 4 General Product Characteristics

# 4.1 Absolute Maximum Ratings

# Table 2 Absolute Maximum Ratings 1)

$T_{\rm J}$  = -40 °C to +150 °C

all voltages with respect to ground, positive current flowing into pin (unless otherwise specified) Voltage ranges specified for  $V_S$  apply also to  $V_{S\_HS}$  (unless otherwise specified)

| Parameter                                                     | Symbol               | Values                   |      |                            | Unit | Note or                                                                                                              | Number   |

|---------------------------------------------------------------|----------------------|--------------------------|------|----------------------------|------|----------------------------------------------------------------------------------------------------------------------|----------|

|                                                               |                      | Min.                     | Тур. | Max.                       |      | <b>Test Condition</b>                                                                                                |          |

| Supply Voltages                                               | 1                    | "                        | 1    |                            | 1    |                                                                                                                      |          |

| Analog Supply voltage                                         | $V_{S}$              | -0.3                     | _    | 28                         | V    | _                                                                                                                    | P_4.1.1  |

| Digital Supply voltage                                        | $V_{\mathrm{DD}}$    | -0.3                     | _    | 5.5                        | V    | -                                                                                                                    | P_4.1.2  |

| Supply voltage for load dump protection                       | $V_{S(LD)}$          | -                        | -    | 42                         | V    | 2)                                                                                                                   | P_4.1.3  |

| Supply voltage for short circuit protection (single pulse)    | $V_{S(SC)}$          | 0                        | -    | 28                         | V    | -                                                                                                                    | P_4.1.4  |

| Reverse polarity voltage                                      | -V <sub>S(REV)</sub> | -                        | -    | 16                         | V    | $T_{J(0)} = 25$ °C<br>$t \le 2$ min<br>See <b>Chapter 11</b> for general setup.<br>$R_L = 70 \Omega$ on all channels | P_4.1.5  |

| Current through VS pin                                        | I <sub>VS</sub>      | -10                      | -    | 10                         | mA   | t ≤ 2 min                                                                                                            | P_4.1.7  |

| Current through VDD pin                                       | $I_{\rm VDD}$        | -50                      | -    | 10                         | mA   | t ≤ 2 min                                                                                                            | P_4.1.8  |

| Power Stages                                                  |                      |                          |      |                            |      |                                                                                                                      |          |

| Load current                                                  | / <sub>L</sub>       | _                        | _    | I <sub>L(OVL0)</sub>       | Α    | single channel                                                                                                       | P_4.1.9  |

| Voltage at power transistor                                   | $V_{DS}$             | -0.3                     | _    | 42                         | V    | -                                                                                                                    | P_4.1.10 |

| Power transistor source voltage                               | V <sub>OUT_S</sub>   | -16                      | _    | V <sub>OUT_D</sub><br>+0.3 | V    | _                                                                                                                    | P_4.1.11 |

| Power transistor drain voltage $(V_{OUT\_S} \ge 0 \text{ V})$ | V <sub>OUT_D</sub>   | V <sub>OUT_S</sub> - 0.3 | _    | 42                         | V    | -                                                                                                                    | P_4.1.12 |

| Power transistor drain voltage (V <sub>OUT_S</sub> < 0 V)     | V <sub>OUT_D</sub>   | -0.3                     | -    | 42                         | V    | -                                                                                                                    | P_4.1.59 |

| Maximum energy dissipation single pulse                       | E <sub>AS</sub>      | -                        | _    | 50                         | mJ   | 4) $T_{J(0)} = 25 ^{\circ}\text{C}$ $I_{L(0)} = 2^{*}I_{L(EAR)}$                                                     | P_4.1.13 |

| Maximum energy dissipation single pulse                       | E <sub>AS</sub>      | -                        | _    | 25                         | mJ   | $T_{J(0)} = 150 ^{\circ}\text{C}$ $I_{L(0)} = 400 \text{mA}$                                                         | P_4.1.14 |

# TLE75242-ESD SPIDER+ 12V

#### **General Product Characteristics**

# Table 2 Absolute Maximum Ratings (cont'd)<sup>1)</sup>

$T_{\rm J}$  = -40 °C to +150 °C

all voltages with respect to ground, positive current flowing into pin (unless otherwise specified) Voltage ranges specified for  $V_S$  apply also to  $V_{S\_HS}$  (unless otherwise specified)

| Parameter                                                    | Symbol            | Values |      |                      | Unit | Note or                                                                    | Number       |

|--------------------------------------------------------------|-------------------|--------|------|----------------------|------|----------------------------------------------------------------------------|--------------|

|                                                              |                   | Min.   | Тур. | Max.                 |      | <b>Test Condition</b>                                                      |              |

| Maximum energy dissipation repetitive pulses - $I_{L(EAR)}$  | $E_{AR}$          | -      | -    | 10                   | mJ   | $T_{J(0)} = 85 \text{ °C}$ $I_{L(0)} = I_{L(EAR)}$ $2*10^6 \text{ cycles}$ | P_4.1.15     |

| IDLE pin                                                     | ,                 | *      |      |                      |      |                                                                            |              |

| Voltage at IDLE pin                                          | V <sub>IDLE</sub> | -0.3   |      | 5.5                  | V    | _                                                                          | P_4.1.23     |

| Current through IDLE pin                                     | I <sub>IDLE</sub> | -0.75  |      | 0.75                 | mA   | -                                                                          | P_4.1.25     |

| Current through IDLE pin                                     | I <sub>IDLE</sub> | -10.0  |      | 2.0                  | mA   | t≤2 min.                                                                   | P_4.1.26     |

| Input Pins                                                   |                   |        |      |                      |      |                                                                            |              |

| Voltage at input pins                                        | V <sub>IN</sub>   | -0.3   |      | 5.5                  | V    | -                                                                          | P_4.1.28     |

| Current through input pins                                   | I <sub>IN</sub>   | -0.75  |      | 0.75                 | mA   | -                                                                          | P_4.1.30     |

| Current through input pins                                   | I <sub>IN</sub>   | -10.0  |      | 2.0                  | mA   | <i>t</i> ≤ 2 min.                                                          | P_4.1.31     |

| SPI Pins                                                     |                   |        |      |                      |      |                                                                            |              |

| Voltage at chip select pin                                   | $V_{\rm CSN}$     | -0.3   |      | 5.5                  | V    | _                                                                          | P_4.1.33     |

| Current through chip select pin                              | I <sub>CSN</sub>  | -0.75  |      | 0.75                 | mA   | _                                                                          | P_4.1.34     |

| Current through chip select pin                              | I <sub>CSN</sub>  | -10.0  |      | 2.0                  | mA   | <i>t</i> ≤ 2 min.                                                          | P_4.1.35     |

| Voltage at serial clock pin                                  | $V_{SCLK}$        | -0.3   |      | 5.5                  | V    |                                                                            | P_4.1.37     |

| Current through serial clock pin                             | I <sub>SCLK</sub> | -0.75  |      | 0.75                 | mA   | -                                                                          | P_4.1.38     |

| Current through serial clock pin                             |                   | -10.0  |      | 2.0                  | mA   | <i>t</i> ≤ 2 min.                                                          | P_4.1.39     |

| Voltage at serial input pin                                  | $V_{\rm SI}$      | -0.3   |      | 5.5                  | V    |                                                                            | P_4.1.41     |

| Current through serial input pin                             | I <sub>SI</sub>   | -0.75  |      | 0.75                 | mA   | -                                                                          | P_4.1.42     |

| Current through serial input pin                             | I <sub>SI</sub>   | -10.0  |      | 2.0                  | mA   | <i>t</i> ≤ 2 min.                                                          | P_4.1.43     |

| Voltage at serial output pin SO                              | $V_{SO}$          | -0.3   |      | V <sub>DD</sub> +0.3 | V    |                                                                            | P_4.1.58     |

| Current through serial output pin SO                         | I <sub>SO</sub>   | -0.75  |      | 0.75                 | mA   |                                                                            | P_4.1.45     |

| Current through serial output pin SO                         | I <sub>so</sub>   | -2.0   |      | 10.0                 | mA   | <i>t</i> ≤ 2 min.                                                          | P_4.1.46     |

| Temperatures                                                 |                   |        |      |                      |      |                                                                            |              |

| Junction Temperature                                         | T                 | -40    | -    | 150                  | °C   | -                                                                          | P_4.1.48     |

| Storage Temperature                                          | $T_{\rm stg}$     | -55    | -    | 150                  | °C   | -                                                                          | P_4.1.49     |

| ESD Susceptibility                                           |                   |        | -    |                      |      |                                                                            | <del>.</del> |

| ESD Susceptibility HBM<br>OUT pins vs. V <sub>S</sub> or GND | V <sub>ESD</sub>  | -4     | _    | 4                    | kV   | 5)<br>HBM                                                                  | P_4.1.50     |

| ESD Susceptibility HBM                                       | V <sub>ESD</sub>  | -2     | _    | 2                    | kV   | 5)                                                                         | P_4.1.51     |

| other pins                                                   |                   |        |      |                      |      | НВМ                                                                        |              |

# TLE75242-ESD SPIDER+ 12V

#### **General Product Characteristics**

#### Table 2 Absolute Maximum Ratings (cont'd)<sup>1)</sup>

$T_1 = -40 \,^{\circ}\text{C} \text{ to } +150 \,^{\circ}\text{C}$

all voltages with respect to ground, positive current flowing into pin (unless otherwise specified) Voltage ranges specified for  $V_S$  apply also to  $V_{S-HS}$  (unless otherwise specified)

| Parameter                                                 | Symbol           | Symbol Values |      |      | Unit | Note or        | Number   |

|-----------------------------------------------------------|------------------|---------------|------|------|------|----------------|----------|

|                                                           |                  | Min.          | Тур. | Max. |      | Test Condition |          |

| ESD Susceptibility CDM<br>Pin 1, 12, 13, 24 (corner pins) | V <sub>ESD</sub> | -750          | _    | 750  | V    | 6)<br>CDM      | P_4.1.52 |

| ESD Susceptibility CDM                                    | V <sub>ESD</sub> | -500          | _    | 500  | V    | 6)<br>CDM      | P_4.1.54 |

- 1) Not subject to production test, specified by design.

- 2) For a duration of  $t_{on}$  = 400 ms;  $t_{on}/t_{off}$  = 10%; limited to 100 pulses

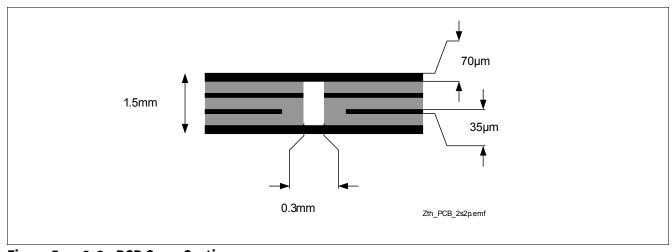

- 3) Device is mounted on a FR4 2s2p board according to Jedec JESD51-2,-5,-7 at natural convection; the Product (Chip+Package) was simulated on a 76.2 \*114.3 \*1.5 mm board with 2 inner copper layers (2 \* 70  $\mu$ m Cu, 2 \* 35  $\mu$ m Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

- 4) Pulse shape represents inductive switch off:  $I_L(t) = I_L(0) \times (1 t / t_{pulse})$ ;  $0 < t < t_{pulse}$

- 5) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS001 (1.5k  $\Omega$ , 100 pF)

- 6) ESD susceptibility, Charged Device Model "CDM" ESDA STM5.3.1 or ANSI/ESD S.5.3.1

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### 4.2 Functional Range

Table 3 Functional range

| Parameter                                         | Symbol                  | Values |      |      | Unit | Note or                      | Number  |  |

|---------------------------------------------------|-------------------------|--------|------|------|------|------------------------------|---------|--|

|                                                   |                         | Min.   | Тур. | Max. |      | <b>Test Condition</b>        |         |  |

| Supply Voltage Range for<br>Normal Operation      | $V_{S(NOR)}$            | 7      | -    | 18   | V    | -                            | P_4.2.1 |  |

| Upper Supply Voltage Range for Extended Operation | $V_{\text{S(EXT,UP)}}$  | 18     | -    | 28   | V    | Parameter deviation possible | P_4.2.2 |  |

| Lower Supply Voltage Range for Extended Operation | V <sub>S(EXT,LOW)</sub> | 3      | -    | 7    | V    | Parameter deviation possible | P_4.2.3 |  |

| Junction Temperature                              | $T_{J}$                 | -40    | _    | 150  | °C   | _                            | P_4.2.4 |  |

| Logic supply voltage                              | $V_{DD}$                | 3      | _    | 5.5  | V    | _                            | P_4.2.5 |  |

Note:

Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

#### **General Product Characteristics**

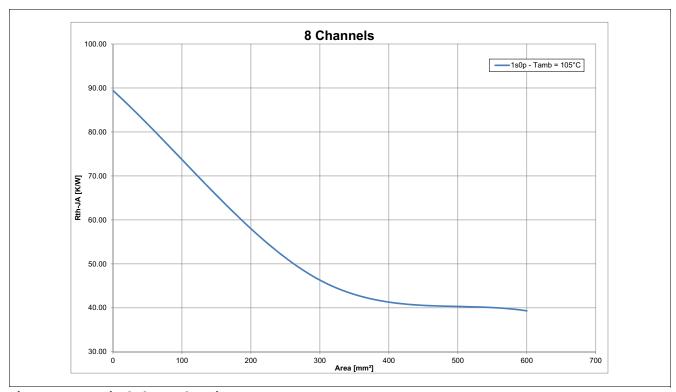

#### **Thermal Resistance** 4.3

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

Table 4 **Thermal Resistance**

| Parameter                   | Symbol             | Symbol Values |      |      | Unit | Note or                          | Numbe   |

|-----------------------------|--------------------|---------------|------|------|------|----------------------------------|---------|

|                             |                    | Min.          | Тур. | Max. |      | <b>Test Condition</b>            | r       |

| Junction to Soldering Point | R <sub>thJSP</sub> | -             | 3    | 5    | K/W  | measured to exposed pad (pin 25) | P_4.3.4 |

| Junction to Ambient         | $R_{thJA}$         | _             | 28   | _    | K/W  | 1)2)                             | P_4.3.5 |

<sup>1)</sup> not subject to production test, specified by design

#### 4.3.1 PCB set up

Figure 5 2s2p PCB Cross Section

<sup>2)</sup> Specified  $R_{th,IA}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; the Product (Chip+Package) was simulated on a 76.2 \* 114.3 \* 1.5 mm board with 2 inner copper layers (2 \* 70  $\mu$ m Cu, 2 \* 35  $\mu$ m Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

#### **General Product Characteristics**

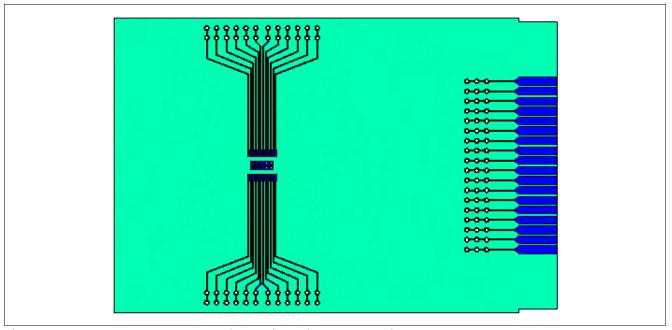

Figure 6 PC Board for Thermal Simulation with 600 mm<sup>2</sup> Cooling Area

13

Figure 7 PC Board for Thermal Simulation with 2s2p Cooling Area

# infineon

#### **General Product Characteristics**

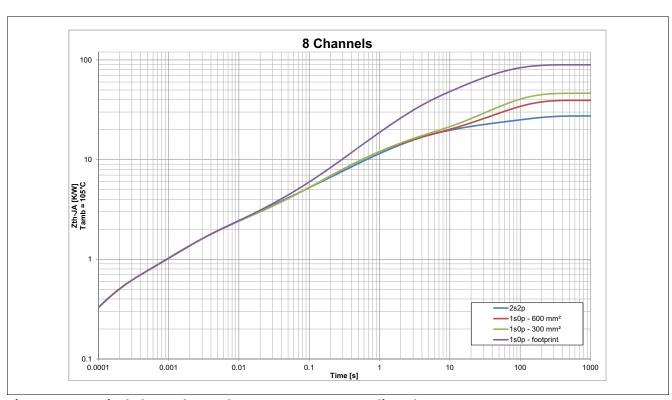

# 4.3.2 Thermal Impedance

Figure 8 Typical Thermal Impedance. PCB setup according Chapter 4.3.1

Figure 9 Typical Thermal Resistance. PCB setup 1s0p

#### **Control Pins**

#### 5 Control Pins

The device has three pins (INO, IN1 and IDLE) to control directly the device without using SPI.

#### 5.1 Input pins

TLE75242-ESD has two input pins available. Each input pin is connected by default to one channel (IN0 to channel 2, IN1 to channel 3). Input Mapping Registers **MAPIN0** and **MAPIN1** can be programmed to connect additional or different channels to each input pin, as shown in **Figure 10**. The signals driving the channels are an OR combination between **OUT** register status, IN0 and IN1 (according to Input Mapping registers status).

Figure 10 Input Mapping

The logic level of the input pins can be monitored via the Input Status Monitor Register (INST). The Input Status Monitor is operative also when TLE75242-ESD is in Limp Home mode. If one of the Input pins is set to "high" and the IDLE pin is set to "low", the device switches into Limp Home mode and activates the channel mapped by default to the input pins. See **Chapter 6.1.5** for further details.

#### 5.2 IDLE pin

The IDLE pin is used to bring the device into Sleep mode operation when is set to "low" and all input pins are set to "low". When IDLE pin is set to "low" while one of the input pins is set to "high" the device enters Limp Home mode.

To ensure a proper mode transition, IDLE pin must be set for at least  $t_{\text{IDLE2SLEEP}}$  (P\_6.3.54, transition from "high" to "low") or  $t_{\text{SLEEP2IDLE}}$  (P\_6.3.53, transition from "low" to "high").

Setting the IDLE pin to "low" has the following consequences:

- All registers in the SPI are reset to default values

- V<sub>DD</sub> and V<sub>S</sub> Undervoltage detection circuits are disabled to decrease current consumption (if both inputs are set to "low")

# **TLE75242-ESD**

# SPIDER+ 12V

#### **Control Pins**

No SPI communication is allowed (SO pin remains in high impedance state also when CSN pin is set to "low") if both input pins are set to "low"

#### **Control Pins**

#### **Electrical Characteristics Control Pins 5.3**

#### **Electrical Characteristics: Control Pins**

$V_{\rm DD}$  = 3 V to 5.5 V,  $V_{\rm S}$  = 7 V to 18 V,  $T_{\rm J}$  = -40 °C to +150 °C (unless otherwise specified) Typical values:  $V_{\rm DD}$  = 5 V,  $V_{\rm S}$  = 13.5 V,  $T_{\rm J}$  = 25 °C

| Parameter       | Symbol               |      | Value | S        | Unit | Note or                   | Number  |

|-----------------|----------------------|------|-------|----------|------|---------------------------|---------|

|                 |                      | Min. | Тур.  | Max.     |      | <b>Test Condition</b>     |         |

| IDLE pin        | ,                    | -    |       | <u> </u> |      |                           | -       |

| L-input level   | $V_{IDLE(L)}$        | 0    |       | 0.8      | V    | _                         | P_5.3.1 |

| H-input level   | $V_{IDLE(H)}$        | 2.0  |       | 5.5      | ٧    | _                         | P_5.3.2 |

| L-input current | I <sub>IDLE(L)</sub> | 5    | 12    | 20       | μΑ   | V <sub>IDLE</sub> = 0.8 V | P_5.3.3 |

| H-input current | I <sub>IDLE(H)</sub> | 14   | 28    | 45       | μΑ   | V <sub>IDLE</sub> = 2.0 V | P_5.3.4 |

| Input Pins      |                      | ·    |       | ·        |      |                           | ·       |

| L-input level   | $V_{IN(L)}$          | 0    |       | 0.8      | ٧    | _                         | P_5.3.5 |

| H-input level   | $V_{\rm IN(H)}$      | 2.0  |       | 5.5      | ٧    | _                         | P_5.3.6 |

| L-input current | I <sub>IN(L)</sub>   | 5    | 12    | 20       | μΑ   | V <sub>IN</sub> = 0.8 V   | P_5.3.7 |

| H-input current | I <sub>IN(H)</sub>   | 14   | 28    | 45       | μΑ   | V <sub>IN</sub> = 2.0 V   | P_5.3.8 |

#### **Power Supply**

### 6 Power Supply

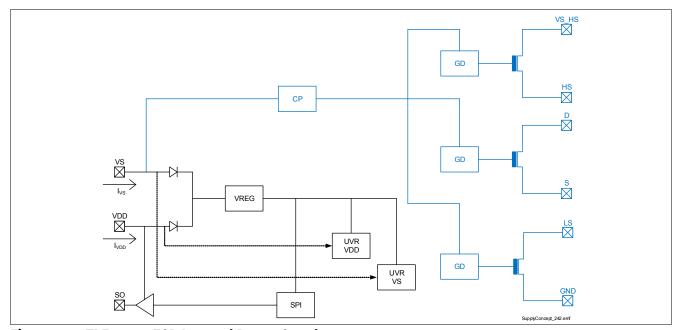

The TLE75242-ESD is supplied by three supply voltages:

- V<sub>S</sub> (analog supply voltage used also for the logic)

- $V_{S\_HS}$  (analog supply voltage used as drain for channels 4, 5, 6 and 7)

- *V*<sub>DD</sub> (digital supply voltage)

The  $V_{\rm S}$  supply line is connected to a battery feed and used, in combination with  $V_{\rm DD}$  supply, for the driving circuitry of the power stages. In situations where  $V_{\rm S}$  voltage drops below  $V_{\rm DD}$  voltage (for instance during cranking events down to 3.0 V), an increased current consumption may be observed at VDD pin.

$V_{\rm S}$  and  $V_{\rm DD}$  supply voltages have an undervoltage detection circuit, which prevents the activation of the associated function in case the measured voltage is below the undervoltage threshold. More in detail:

- An undervoltage on both  $V_S$  and  $V_{DD}$  supply voltages prevents the activation of the power stages and any SPI communication (the SPI registers are reset)

- An undervoltage on V<sub>DD</sub> supply prevents any SPI communication. SPI read/write registers are reset to default values.

- An undervoltage on  $V_S$  supply forces the TLE75242-ESD to drain all needed current for the logic from  $V_{DD}$  supply. All channels are disabled, and are enabled again as soon as  $V_S \ge V_{S(OP)}$ .

**Figure 11** shows a basic concept drawing of the interaction between supply pins VS and VDD, the output stage drivers and SO supply line.

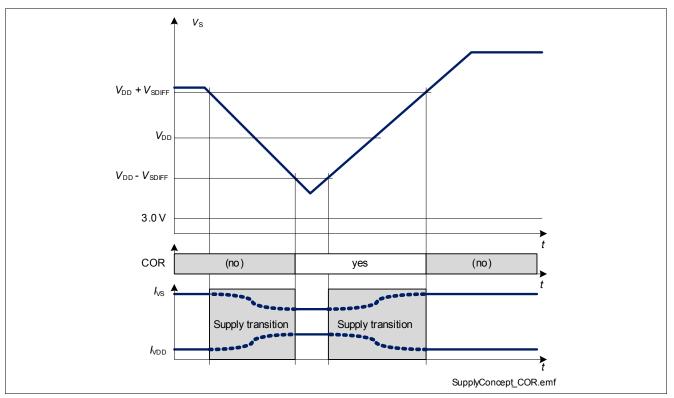

Figure 11 TLE75242-ESD Internal Power Supply concept

When  $3.0 \text{ V} \le V_{\text{S}} \le V_{\text{DD}} - V_{\text{SDIFF}}$  TLE75242-ESD operates in "Cranking Operative Range" (COR). In this condition the current consumption from VDD pin increases while it decreases from VS pin where the total current consumption remains within the specified limits. **Figure 12** shows the voltage levels at VS pin where the device goes in and out of COR. During the transition to and from COR operative region,  $I_{\text{VS}}$  and  $I_{\text{VDD}}$  change between values defined for normal operation and for COR operation. The sum of both current remains within limits specified in "Overall current consumption" section (see **Table 8**).

# infineon

#### **Power Supply**

Figure 12 "Cranking Operative Range"

Furthermore, when  $V_{S(UV)} \le V_S \le V_{S(OP)}$  it may be not possible to switch ON a channel that was previously OFF. All channels that are already ON keep their state unless they are switched OFF via SPI or via INn pins. An overview of channel behavior according to different  $V_S$  and  $V_{DD}$  supply voltages is shown in **Table 6** (the table is valid after a successful power-up, see **Chapter 6.1.1** for more details).

### **Power Supply**

Table 6 Device capability as function of  $V_s$  and  $V_{DD}$

|                                                                                        | _                                                                                        |                                                                                                                   |                                                                                                                   |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

|                                                                                        | $V_{\rm DD} \le V_{\rm DD(UV)}$<br>$(V_{\rm DD(UV)} = P_6.3.25)$                         | $V_{DD} = V_{DD(LOP)}$ $(V_{DD(LOP)} = P_6.3.24)$                                                                 | $V_{\rm DD} > V_{\rm DD(LOP)}$                                                                                    |

| V <sub>S</sub> ≤ 3.0 V                                                                 | channels cannot be controlled                                                            | channels cannot be controlled                                                                                     | channels cannot be controlled                                                                                     |

| $3.0 \text{ V} = V_{\text{S(UV),max}}$                                                 | SPI registers reset                                                                      | SPI registers available                                                                                           | SPI registers available                                                                                           |

| (P_6.3.1)                                                                              | SPI communication not available ( $f_{SCLK} = 0 \text{ MHz}$ )                           | SPI communication possible ( $f_{SCLK} = 1 \text{ MHz}$ ) (P_10.4.34)                                             | SPI communication possible ( $f_{SCLK} = 5 \text{ MHz}$ ) (P_10.4.22)                                             |

|                                                                                        | Limp Home mode not<br>available                                                          | Limp Home mode available (channels are OFF)                                                                       | Limp Home mode available (channels are OFF)                                                                       |

| $3.0 \text{ V} < V_{\text{S}} \le V_{\text{S(OP)}}$<br>$(V_{\text{S(OP)}} = P\_6.3.2)$ | channels cannot be controlled by SPI                                                     | channels can be switched ON and OFF (SPI control) <sup>1)</sup> ( $R_{\rm DS(ON)}$ deviations possible)           | channels can be switched ON and OFF (SPI control) <sup>1)</sup> ( $R_{\rm DS(ON)}$ deviations possible)           |

|                                                                                        | SPI registers reset                                                                      | SPI registers available                                                                                           | SPI registers available                                                                                           |

|                                                                                        | SPI communication not available ( $f_{SCLK} = 0 \text{ MHz}$ )                           | SPI communication possible ( $f_{SCLK} = 1 \text{ MHz}$ ) (P_10.4.34)                                             | SPI communication possible ( $f_{SCLK} = 5 \text{ MHz}$ ) (P_10.4.22)                                             |

|                                                                                        | Limp Home mode<br>available <sup>1)</sup> (R <sub>DS(ON)</sub><br>deviations possible)   | Limp Home mode<br>available <sup>1)</sup> (R <sub>DS(ON)</sub><br>deviations possible)                            | Limp Home mode<br>available <sup>1)</sup> (R <sub>DS(ON)</sub><br>deviations possible)                            |

| $V_{\rm S} \ge V_{\rm S(OP)}$                                                          | channels cannot be controlled by SPI                                                     | channels can be switched ON and OFF (small $R_{\rm DS(ON)}$ dev. possible when $V_{\rm S} = V_{\rm S(EXT,LOW)}$ ) | channels can be switched ON and OFF (small $R_{\rm DS(ON)}$ dev. possible when $V_{\rm S} = V_{\rm S(EXT,LOW)}$ ) |

|                                                                                        | SPI registers reset                                                                      | SPI registers available                                                                                           | SPI registers available                                                                                           |

|                                                                                        | SPI communication not available ( $f_{SCLK} = 0 \text{ MHz}$ )                           | SPI communication possible ( $f_{SCLK} = 5 \text{ MHz}$ ) (P_10.4.22)                                             | SPI communication possible ( $f_{SCLK} = 5 \text{ MHz}$ ) (P_10.4.22)                                             |

|                                                                                        | Limp Home mode available (small $R_{DS(ON)}$ dev. possible when $V_S = V_{S(EXT,LOW)}$ ) | Limp Home mode available (small $R_{DS(ON)}$ dev. possible when $V_S = V_{S(EXT,LOW)}$ )                          | Limp Home mode available (small $R_{DS(ON)}$ dev. possible when $V_S = V_{S(EXT,LOW)}$ )                          |

<sup>1)</sup> undervoltage condition on  $V_s$  must be considered - see **Chapter 6.2.1** for more details

#### **Power Supply**

#### 6.1 Operation Modes

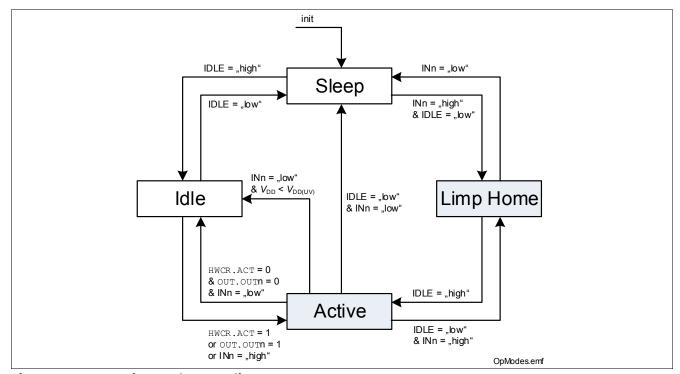

TLE75242-ESD has the following operation modes:

- Sleep mode

- · Idle mode

- Active mode

- · Limp Home mode

The transition between operation modes is determined according to following levels and states:

- · logic level at IDLE pin

- logic level at INn pins

- OUT.OUTn bits state

- HWCR.ACT bit state

The state diagram including the possible transitions is shown in **Figure 13**. The behaviour of TLE75242-ESD as well as some parameters may change in dependence from the operation mode of the device. Furthermore, due to the undervoltage detection circuitry which monitors  $V_S$  and  $V_{DD}$  supply voltages, some changes within the same operation mode can be seen accordingly.

The operation mode of the TLE75242-ESD can be observed by:

- status of output channels

- status of SPI registers

- current consumption at VDD pin (I<sub>VDD</sub>)

- current consumption at VS pin (I<sub>VS</sub>)

The default operation mode to switch ON the loads is Active mode. If the device is not in Active mode and a request to switch ON one or more outputs comes (via SPI or via Input pins), it will switch into Active or Limp Home mode, according to IDLE pin status. Due to the time needed for such transitions, output turn-on time  $t_{\rm ON}$  will be extended due to the mode transition latency.

Figure 13 Operation Mode state diagram

### TLE75242-ESD SPIDER+ 12V

#### **Power Supply**

**Table 7** shows the correlation between device operation modes,  $V_S$  and  $V_{DD}$  supply voltages, and state of the most important functions (channels operativity, SPI communication and SPI registers).

Table 7 Device function in relation to operation modes,  $V_s$  and  $V_{DD}$  voltages

| Operation<br>Mode | Function      | Undervoltage condition on $V_S^{1}$ $V_{DD} \le V_{DD(UV)}$ | Undervoltage condition on $V_S$ $V_{DD} > V_{DD(UV)}$ | $V_{\rm S}$ not in undervoltage $V_{\rm DD} \le V_{\rm DD(UV)}$ | V <sub>S</sub> not in<br>undervoltage<br>V <sub>DD</sub> >V <sub>DD(UV)</sub> |

|-------------------|---------------|-------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------|

| Sleep             | Channels      | not available                                               | not available                                         | not available                                                   | not available                                                                 |

|                   | SPI comm.     | not available                                               | not available                                         | not available                                                   | not available                                                                 |

|                   | SPI registers | reset                                                       | reset                                                 | reset                                                           | reset                                                                         |

| Idle              | Channels      | not available                                               | not available                                         | not available                                                   | not available                                                                 |

|                   | SPI comm.     | not available                                               | 1                                                     | not available                                                   | 1                                                                             |

|                   | SPI registers | reset                                                       | 1                                                     | reset                                                           | 1                                                                             |

| Active            | Channels      | not available                                               | not available                                         | √ (IN pins only)                                                | 1                                                                             |

|                   | SPI comm.     | not available                                               | 1                                                     | not available                                                   | 1                                                                             |

|                   | SPI registers | reset                                                       | 1                                                     | reset                                                           | 1                                                                             |

| Limp Home         | Channels      | not available                                               | not available                                         | √ (IN pins only)                                                | ✓ (IN pins only)                                                              |

|                   | SPI comm.     | not available                                               | √ (read-only)                                         | not available                                                   | √ (read-only)                                                                 |

|                   | SPI registers | reset                                                       | √ (read-only) <sup>2)</sup>                           | reset                                                           | √ (read-only) <sup>2)</sup>                                                   |

<sup>1)</sup> see Chapter 6.2.1 for more details

#### **6.1.1** Power-up

The Power-up condition is satisfied when one of the supply voltages ( $V_S$  or  $V_{DD}$ ) is applied to the device and the INn or IDLE pins are set to "high". If  $V_S$  is above the threshold  $V_{S(OP)}$  or if  $V_{DD}$  is above the threshold  $V_{DD(LOP)}$  the internal power-on signal is set.

#### 6.1.2 Sleep mode

When TLE75242-ESD is in Sleep mode, all outputs are OFF and the SPI registers are reset, independently from the supply voltages. The current consumption is minimum. See parameters  $I_{\text{VDD(SLEEP)}}$  and  $I_{\text{VS(SLEEP)}}$ , or parameter  $I_{\text{SLEEP}}$  for the whole device.

#### 6.1.3 Idle mode

In Idle mode, the current consumption of the device can reach the limits given by parameters  $I_{\text{VDD}(\text{IDLE})}$  and  $I_{\text{VS}(\text{IDLE})}$ , or by parameter  $I_{\text{IDLE}}$  for the whole device. The internal voltage regulator is working. Diagnosis functions are not available. The output channels are switched OFF, independently from the supply voltages. When  $V_{\text{DD}}$  is available, the SPI registers are working and SPI communication is possible. In Idle mode the ERRn bits are not cleared for functional safety reasons.

<sup>2)</sup> see Chapter 6.1.5 for a detailed overview

#### **Power Supply**

#### 6.1.4 Active mode

Active mode is the normal operation mode of TLE75242-ESD when no Limp Home condition is set and it is necessary to drive some or all loads. Voltage levels of  $V_{\rm DD}$  and  $V_{\rm S}$  influence the behavior as described at the beginning of **Chapter 6**. Device current consumption is specified with  $I_{\rm VDD(ACTIVE)}$  and  $I_{\rm VS(ACTIVE)}$  ( $I_{\rm ACTIVE}$  for the whole device). The device enters Active mode when IDLE pin is set to "high" and one of the input pins is set to "high" or one **OUT . OUTn** bit is set to "1". If **HWCR . ACT** is set to "0", the device returns to Idle mode as soon as all inputs pins are set to "low" and **OUT . OUTn** bits are set to "0". If **HWCR . ACT** is set to "1", the device remains in Active mode independently of the status of input pins and **OUT . OUTn** bits. An undervoltage condition on  $V_{\rm DD}$  supply brings the device into Idle mode, if all input pins are set to "low". Even if the registers **MAPINO** and **MAPIN1** are both set to "00<sub>H</sub>" but one of the input pins INn is set to "high", the device goes into Active mode.

#### 6.1.5 Limp Home mode

TLE75242-ESD enters Limp Home mode when IDLE pin is "low" and one of the input pins is set to "high", switching ON the channel connected to it. SPI communication is possible but only in read-only mode (SPI registers can be read but cannot be written). More in detail:

- UVRVS and LOPVDD are set to "1"

- MODE bits are set to "01<sub>B</sub>" (Limp Home mode)

- TER bit is set to "1" on the first SPI command after entering Limp Home mode. Afterwards it works normally

- OLOFF bits is set to "0"

- ERRn bits work normally

- DIAG OSM. OUTn bits can be read and work normally

- All other registers are set to their default value and cannot be programmed as long as the device is in Limp Home mode

See **Table 6** for a detailed overview of supply voltage conditions required to switch ON channels 2 and 3 during Limp Home. All other channels are OFF.

A transmission of SPI commands during transition from Active to Limp Home mode or Limp Home to Active mode may result in undefined SPI responses.

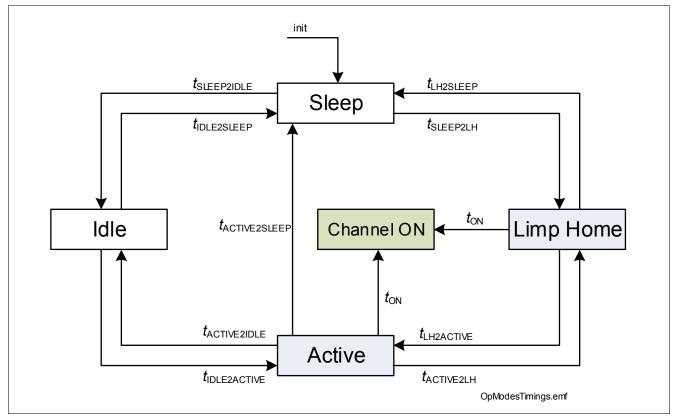

#### 6.1.6 Definition of Power Supply modes transition times

The channel turn-ON time is as defined by parameter  $t_{\rm ON}$  when TLE75242-ESD is in Active mode or in Limp Home mode. In all other cases, it is necessary to add the transition time required to reach one of the two aforementioned Power Supply modes (as shown in **Figure 14**).

# SPIDER+ 12V

#### **Power Supply**

Figure 14 Transition Time diagram

#### 6.2 Reset condition

One of the following 3 conditions resets the SPI registers to the default value:

- $V_{\rm DD}$  is not present or below the undervoltage threshold  $V_{\rm DD(UV)}$

- IDLE pin is set to "low"

- a reset command (HWCR.RST set to "1") is executed

- ERRn bits are not cleared by a reset command (for functional safety)

- UVRVS and LOPVDD bits are cleared by a reset command

In particular, all channels are switched OFF (if there are no input pin set to "high") and the Input Mapping configuration is reset.

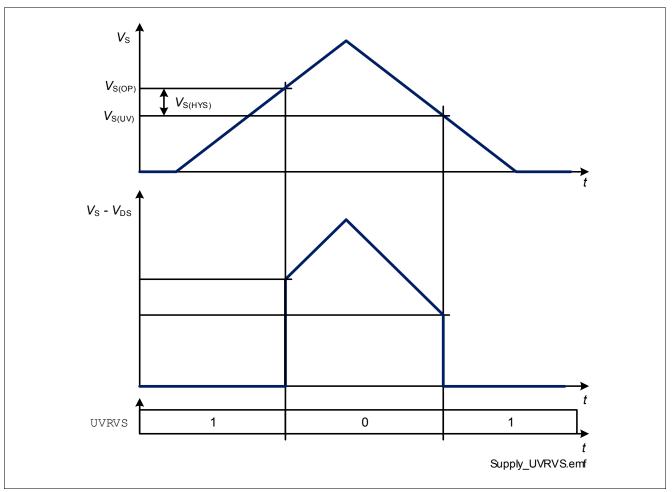

#### 6.2.1 Undervoltage on $V_s$

Between  $V_{S(UV)}$  and  $V_{S(OP)}$  the undervoltage mechanism is triggered. If the device is operative and the supply voltage drops below the undervoltage threshold  $V_{S(UV)}$ , the logic set the bit **UVRVS** to "1". As soon as the supply voltage VS is above the minimum voltage operative threshold  $V_{S(OP)}$ , the bit **UVRVS** is set to "0" after the first Standard Diagnosis readout. Undervoltage condition on VS influences the status of the channels, as described in **Table 6**. **Figure 15** sketches the undervoltage behavior (the " $V_S - V_{DS}$ " line refers to a channel which is programmed to be ON).

# infineon

#### **Power Supply**

Figure 15 V<sub>S</sub> Undervoltage Behavior

# **6.2.2** Low Operating Power on $V_{\rm DD}$

When  $V_{\rm DD}$  supply voltage is in the range indicated by  $V_{\rm DD(LOP)}$ , the bit **LOPVDD** is set to "1". As soon as  $V_{\rm DD} > V_{\rm DD(LOP)}$  the bit **LOPVDD** is set to "0" after the first Standard Diagnosis readout.

If  $V_{\rm DD}$  supply voltage is not present, a voltage applied to pins CSN or SO can supply the internal logic (not recommended in normal operation due to internal design limitations).