Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

## 1 Overview

#### **Features**

- Overvoltage, Overtemperature, ESD-Protection

- Direct Parallel PWM Control of all Channels

- safeCOMMUNICATION (SPI and Parallel)

- Efficient Communication Mode: compactCONTROL

- Compatible with 3.3V- and 5V- Micro Controllers I/O ports

- clampSAFE for highly efficient parallel use of the channels

- Green Product

- AEC Qualified

## **Potential applications**

Power Switch Automotive and Industrial Systems switching Solenoids, Relays and Resistive Loads

#### **Product validation**

Qualified for Automotive Applications. Product Validation according to AEC-Q100/101.

## **Description**

10-channel Low-Side Switch in Smart Power Technology [SPT] with **S**erial **P**eripheral **I**nterface [SPI] and 10 open drain DMOS output stages. The TLE8110ED is protected by embedded protection functions and designed for automotive and industrial applications. The output stages are controlled via Parallel Input Pins for PWM use or SPI Interface. The TLE8110ED is particularly suitable for Engine Management and Powertrain Systems.

| Туре      | Package      | Marking   |  |  |

|-----------|--------------|-----------|--|--|

| TLE8110ED | PG-DSO-36-72 | TLE8110ED |  |  |

## Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **Overview**

**Table 1** Product Summary

| Parameter                                                     | Symbol                | Value     | Unit |

|---------------------------------------------------------------|-----------------------|-----------|------|

| Analogue Suppy Voltage                                        | $V_{DD}$              | 4.50 5.50 | V    |

| Digital Supply Voltage                                        | V <sub>cc</sub>       | 3.00 5.50 | V    |

| Clamping Voltage (CH 1-10)                                    | $V_{\rm DS(CL)typ}$   | 55        | V    |

| On Resistance maximum at $T_j = 25^{\circ}$ C and $I_{Dnom}$  | R <sub>ON1-4</sub>    | 0.30      | Ω    |

|                                                               | R <sub>ON5-6</sub>    | 0.25      | Ω    |

|                                                               | R <sub>ON7-10</sub>   | 0.60      | Ω    |

| On Resistance maximum at $T_j = 150^{\circ}$ C and $I_{Dnom}$ | R <sub>ON1-4</sub>    | 0.60      | Ω    |

|                                                               | R <sub>ON5-6</sub>    | 0.50      | Ω    |

|                                                               | R <sub>ON7-10</sub>   | 1.20      | Ω    |

| Nominal Output current (CH 1-4)                               | I <sub>Dnom</sub>     | 1.50      | А    |

| Nominal Output current (CH 5-6)                               | I <sub>Dnom</sub>     | 1.70      | Α    |

| Nominal Output current (CH 7-10)                              | I <sub>Dnom</sub>     | 0.75      | Α    |

| Output Current Shut-down Threshold (CH 1-4) min.              | I <sub>DSD(low)</sub> | 2.60      | Α    |

| Output Current Shut-down Threshold (CH 5-6) min.              | I <sub>DSD(low)</sub> | 3.70      | А    |

| Output Current Shut-down Threshold (CH 7-10) min.             | I <sub>DSD(low)</sub> | 1.70      | А    |

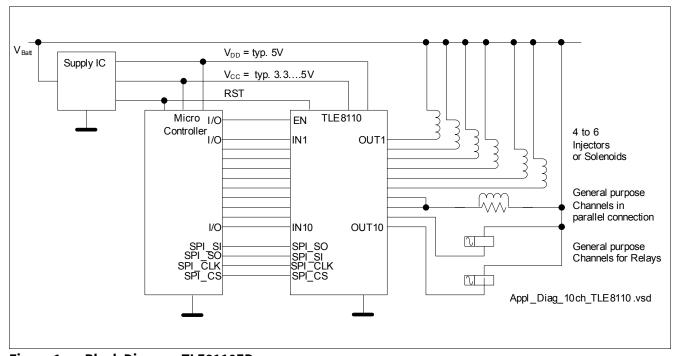

Figure 1 Block Diagram TLE8110ED

## Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

## **Table of Contents**

| 1              | Overview                                                        | . 1 |

|----------------|-----------------------------------------------------------------|-----|

| 2              | Block Diagram                                                   | . 5 |

| 2.1            | Description                                                     | . 5 |

| 3              | Pin Configuration                                               | . 7 |

| 3.1            | Pin Assignment                                                  | . 7 |

| 3.2            | Pin Definitions and Functions                                   |     |

| 3.3            | Terms                                                           | . 9 |

| 4              | General Product Characteristics                                 | 10  |

| 4.1            | Absolute Maximum Ratings                                        |     |

| 4.2            | Functional Range                                                |     |

| 4.3            | Thermal Resistance                                              | 12  |

| 5              | Power Supply                                                    |     |

| 5.1            | Description Power Supply                                        |     |

| 5.2            | Electrical Characteristics Power Supply                         | 14  |

| 6              | Reset and Enable Inputs                                         | 16  |

| 6.1            | Description Reset and Enable Inputs                             |     |

| 6.2            | Electrical Characteristics Reset Inputs                         | 16  |

| 7              | Power Outputs                                                   | 18  |

| 7.1            | Description Power Outputs                                       |     |

| 7.2            | Description of the Clamping Structure                           |     |

| 7.3            | Electrical Characteristics Power Outputs                        |     |

| 7.4            | Parallel Connection of the Power Stages                         |     |

| 8              | Diagnosis                                                       |     |

| 8.1            | Diagnosis Description                                           |     |

| 8.1.1          | Open Load diagnosis                                             |     |

| 8.1.2<br>8.2   | Overcurrent / Overtemperature diagnosis                         |     |

|                | •                                                               |     |

| 9              | Parallel Inputs                                                 |     |

| 9.1<br>9.2     | Description Parallel Inputs                                     |     |

|                | ·                                                               |     |

| 10             | Protection Functions                                            |     |

| 10.1           | Electrical Characteristics Overload Protection Function         |     |

| 11             | 16 bit SPI Interface                                            |     |

| 11.1           | Description 16 bit SPI Interface                                |     |

| 11.2           | Timing Diagrams Electrical Characteristics 16 bit SPI Interface |     |

| 11.3           |                                                                 |     |

| 12             | Control of the device                                           |     |

| 12.1           | Internal Clock                                                  |     |

| 12.2<br>12.2.1 | SPI Interface. Signals and Protocol                             |     |

| 12.2.1         | Daisy Chain                                                     |     |

| 12.2.3         | SPI Protocol                                                    |     |

## Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

| L4       | Revision History                                               | 73 |

|----------|----------------------------------------------------------------|----|

| L3       | Package Outlines                                               | 72 |

| 12.3.6   | DEVS - Device Settings                                         | 71 |

| L2.3.5   | PMx - Parallel Mode Register CHx                               | 70 |

| L2.3.4   | ISx - INPUT or Serial Mode Control Register, Bank A and Bank B | 69 |

| 12.3.3   | OUTx - Output Control Register CHx                             | 68 |

| 12.3.2.3 | DMSx/OPSx - Diagnosis Mode Set / Output Pin Set Commands       | 65 |

| 12.3.2.2 | DRx - Return on DRx Commands                                   |    |

| 12.3.2.1 | DRx - Diagnosis Registers Contents                             |    |

| 12.3.2   | DCC - Diagnosis Registers and compactCONTROL                   |    |

| 12.3.1.4 | CMD_RINx - Command: Return Input Pin (INx) - Status            | 57 |

| 12.3.1.3 | CMD_RPC - Command: Return Pattern Check                        |    |

| 12.3.1.2 | CMD_RSDS - Command: Return Short Diagnosis and Device Status   | 54 |

| 12.3.1.1 | CMD_RSD - Command: Return Short Diagnosis                      | 53 |

| L2.3.1   | CMD - Commands                                                 |    |

| 12.3     | Register and Command - Overview                                |    |

| 12.2.4.2 | Modulo-8 Counter                                               |    |

| L2.2.4.1 | Encoding of the commands                                       |    |

| L2.2.4   | safeCOMMUNICATION                                              |    |

| 12.2.3.4 | Daisy-Chain and 2x8-bit protocol                               |    |

| 12.2.3.3 | 16- and 2x8-bit protocol mixed                                 |    |

| 12.2.3.2 | 2x8-bit protocol                                               |    |

| L2.2.3.1 | 16-bit protocol                                                | 43 |

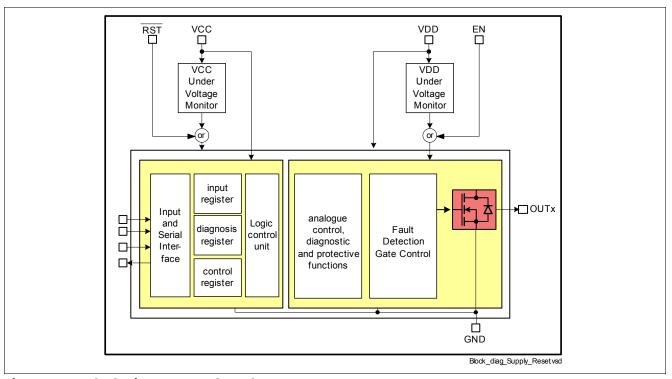

**Block Diagram**

## 2 Block Diagram

Figure 2 Block Diagram

#### 2.1 Description

#### Communication

The TLE8110ED is a 10-channel low-side switch in PG-DSO-36-72 package providing embedded protection functions. The 16-bit serial peripheral interface (SPI) can be utilized for control and diagnosis of the device and the loads. The SPI interface provides daisy-chain capability in order to assemble multiple devices in one SPI chain by using the same number of micro-controller pins <sup>1)</sup>.

The analogue and the digital part of the device is supplied by 5V. Logic Input and Output Signals are then compatible to 5V logic level [TTL - level]. Optionally, the logic part can be supplied with lower voltages to achieve signal compatibility with e.g. 3.3V logic level [CMOS - level].

The TLE8110ED is equipped with 10 parallel input pins that are routed to each output channel. This allows control of the channels for loads driven by Pulse Width Modulation (PWM). The output channels can also be controlled by SPI.

#### Reset

The device is equipped with one Reset Pin and one Enable. Reset [RST] serves the whole device, Enable [EN] serves only the Output Control Unit and the Power Stages.

#### Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **Block Diagram**

#### **Diagnosis**

The device provides diagnosis of the load, including open load, short to GND as well as short circuit to VBatt detection and over-load/ over-temperature indication. The SPI diagnosis flags indicates if latched fault conditions may have occurred.

#### **Protection**

Each output stage is protected against short circuit. In case of over load, the affected channel is switched off. The switching off reaction time is dependent on two switching thresholds. Restart of the channel is done by clearing the Diagnosis Register <sup>1)</sup>. This feature protects the device against uncontrolled repetitive short circuits.

There is a temperature sensor available for each channel to protect the device in case of over temperature. In case of over temperature the affected channel is switched off and the Over-Temperature Flag is set. Restart of the channel is done by deleting the Flag. This feature protects the device against uncontrolled temperature toggling.

#### **Parallel Connection of Channels**

The device is featured with a central clamping structure, so-called CLAMPsafe. This feature ensures a balanced clamping between the channels and allows in case of parallel connection of channels a high efficient usage of the channel capabilities. This parallel mode is additionally featured by best possible parameter- and thermal matching of the channels and by controlling the channels accordingly.

## Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

**Pin Configuration**

## 3 Pin Configuration

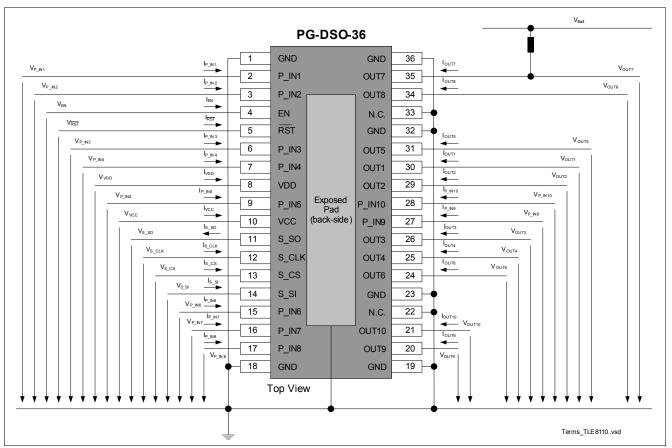

## 3.1 Pin Assignment

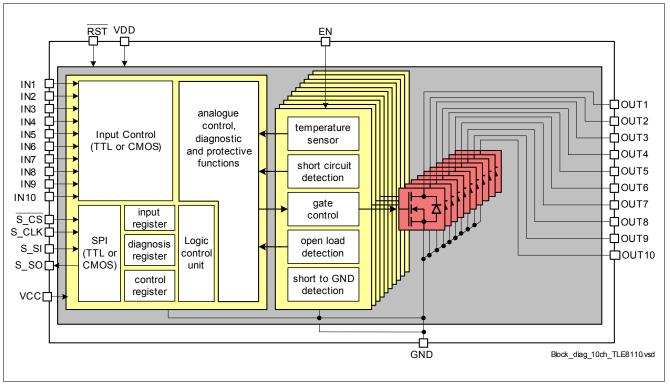

Figure 3 Pin Configuration

## 3.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                                          |

|-----|--------|-----------------------------------------------------------------------------------|

| 1   | GND    | Ground                                                                            |

| 2   | P_IN1  | Parallel Input Pin 1. Default assignment to Output Channel 1                      |

| 3   | P_IN2  | Parallel Input Pin 2. Default assignment to Output Channel 2                      |

| 4   | EN     | Enable Input Pin. If not needed, connect with Pull-up resistor to VCC             |

| 5   | RST    | Reset Input Pin (active low). If not needed, connect with Pull-up resistor to VCC |

| 6   | P_IN3  | Parallel Input Pin 3. Default assignment to Output Channel 3                      |

| 7   | P_IN4  | Parallel Input Pin 4. Default assignment to Output Channel 4                      |

| 8   | VDD    | Analogue Supply Voltage                                                           |

| 9   | P_IN5  | Parallel Input Pin 5. Default assignment to Output Channel 5                      |

| 10  | VCC    | Digital Supply Voltage                                                            |

| 11  | S_S0   | Serial Peripheral Interface [SPI], Serial Output                                  |

| 12  | S_CLK  | Serial Peripheral Interface [SPI], Clock Input                                    |

| 13  | S_CS   | Serial Peripheral Interface [SPI], Chip Select (active low)                       |

| 14  | S_SI   | Serial Peripheral Interface [SPI], Serial Input                                   |

| 15  | P_IN6  | Parallel Input Pin 6. Default assignment to Output Channel 6                      |

## Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **Pin Configuration**

| Pin            | Symbol | Function                                                       |

|----------------|--------|----------------------------------------------------------------|

| 16             | P_IN7  | Parallel Input Pin 7. Default assignment to Output Channel 7   |

| 17             | P_IN8  | Parallel Input Pin 8. Default assignment to Output Channel 8   |

| 18             | GND    | Ground                                                         |

| 19             | GND    | Ground                                                         |

| 20             | OUT9   | Drain of Power Transistor Channel 9                            |

| 21             | OUT10  | Drain of Power Transistor Channel 10                           |

| 22             | N.C.   | internally not connected, connect to Ground                    |

| 23             | GND    | Ground                                                         |

| 24             | OUT6   | Drain of Power Transistor Channel 6                            |

| 25             | OUT4   | Drain of Power Transistor Channel 4                            |

| 26             | OUT3   | Drain of Power Transistor Channel 3                            |

| 27             | P_IN9  | Parallel Input Pin 9. Default assignment to Output Channel 9   |

| 28             | P_IN10 | Parallel Input Pin 10. Default assignment to Output Channel 10 |

| 29             | OUT2   | Drain of Power Transistor Channel 2                            |

| 30             | OUT1   | Drain of Power Transistor Channel 1                            |

| 31             | OUT5   | Drain of Power Transistor Channel 5                            |

| 32             | GND    | Ground                                                         |

| 33             | N.C.   | internally not connected, connect to Ground                    |

| 34             | OUT8   | Drain of Power Transistor Channel 8                            |

| 35             | OUT7   | Drain of Power Transistor Channel 7                            |

| 36             | GND    | Ground                                                         |

| Exposed<br>Pad |        | internally not connected, connect to Ground                    |

Note: The exposed pad of TLE8110ED is not connected to ground pins internally. It is highly recommended to connect the exposed pad to GND pins on the PCB.

**Pin Configuration**

#### 3.3 **Terms**

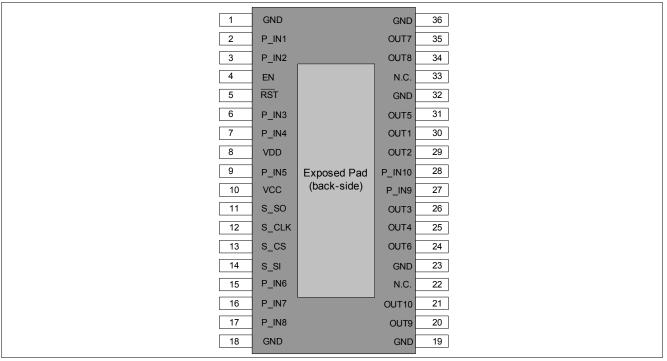

Figure 4 **Terms**

## Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **General Product Characteristics**

## 4 General Product Characteristics

## 4.1 Absolute Maximum Ratings

## Table 2 Absolute Maximum Ratings 1)

$T_j$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                              | Symbol          | ,                      | Values | •                     | Unit | Note or                                  | Number   |

|--------------------------------------------------------|-----------------|------------------------|--------|-----------------------|------|------------------------------------------|----------|

|                                                        |                 | Min.                   | Тур.   | Max.                  |      | Test Condition                           |          |

| Supply Voltages                                        |                 | '                      | 1      | 1                     |      |                                          |          |

| Digital Supply voltage                                 | $V_{\rm cc}$    | -0.3                   | _      | 5.5                   | V    | permanent                                | P_4.1.1  |

| Digital Supply voltage                                 | $V_{\rm cc}$    | -0.3                   | -      | 6.2                   | V    | t < 10s                                  | P_4.1.2  |

| Analogue Supply voltage                                | $V_{DD}$        | -0.3                   | _      | 5.5                   | V    | permanent                                | P_4.1.3  |

| Analogue Supply voltage                                | $V_{\rm DD}$    | -0.3                   | _      | 6.2                   | V    | t < 10s                                  | P_4.1.4  |

| Power Stages                                           |                 | 1                      | 1      | 1                     |      |                                          |          |

| Load Current (CH 1 to 10)                              | $I_{Dn}$        | _                      | -      | I <sub>DSD(low)</sub> | Α    | _                                        | P_4.1.5  |

| Reverse Current Output (CH 1- 10)                      | $I_{Dn}$        | -/ <sub>DSD(low)</sub> | _      | -                     | Α    | -                                        | P_4.1.6  |

| Total Ground Current                                   | $I_{GND}$       | -20                    | _      | 20                    | Α    | -                                        | P_4.1.7  |

| Continuous Drain Source Voltage (Channel 1 to 10)      | $V_{DSn}$       | -0.3                   | -      | 45                    | V    | _                                        | P_4.1.8  |

| maximum Voltage for short circuit protection on Output | $V_{DSn}$       | -                      | -      | 24                    | V    | one event on one single channel          | P_4.1.9  |

| Clamping Energy - Single Pulse 2) 3                    | 3)              | 1                      |        | I.                    |      |                                          |          |

| Single Clamping Energy<br>Channel Group 1-4            | E <sub>AS</sub> | -                      | -      | 29                    | mJ   | I <sub>D</sub> = 2.6A,<br>1 single pulse | P_4.1.10 |

| Single Clamping Energy<br>Channel Group 5-6            | E <sub>AS</sub> | -                      | -      | 31                    | mJ   | I <sub>D</sub> = 3.7A,<br>1 single pulse | P_4.1.11 |

| Single Clamping Energy<br>Channel Group 7-10           | E <sub>AS</sub> | -                      | -      | 11                    | mJ   | I <sub>D</sub> = 1.7A,<br>1 single pulse | P_4.1.12 |

| Logic Pins (SPI, INn, EN, RST)                         |                 | 1                      |        | I.                    | I    |                                          |          |

| Input Voltage at all Logic Pin                         | $V_{x}$         | -0.3                   | _      | 5.5                   | V    | permanent                                | P_4.1.13 |

| Input Voltage at all Logic Pin                         | $V_{x}$         | -0.3                   | _      | 6.2                   | ٧    | t < 10s                                  | P_4.1.14 |

| Input Voltage at Pin 27, 28 (IN9, 10)                  | V <sub>x</sub>  | -0.3                   | _      | 45                    | ٧    | permanent                                | P_4.1.15 |

| Temperatures                                           | -11             | 1                      | 11     | 1                     |      |                                          | 1        |

| Junction Temperature                                   | $T_{\rm i}$     | -40                    | _      | 150                   | °C   | _                                        | P_4.1.16 |

| Junction Temperature                                   | T <sub>j</sub>  | -40                    | -      | 175                   | °C   | max. 100hrs<br>cumulative                | P_4.1.17 |

| Storage Temperature                                    | $T_{\rm stg}$   | -55                    | _      | 150                   | °C   | _                                        | P_4.1.18 |

| ESD Robustness                                         | · · ·           | •                      |        | 1                     |      |                                          |          |

10

## Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **General Product Characteristics**

#### Absolute Maximum Ratings 1) (cont'd) Table 2

$T_i = -40$ °C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                        | Symbol           | ,    | Values | •    | Unit | Note or                                                 | Number   |

|------------------------------------------------------------------|------------------|------|--------|------|------|---------------------------------------------------------|----------|

|                                                                  |                  | Min. | Тур.   | Max. |      | Test Condition                                          |          |

| Electro Static Discharge Voltage<br>"Human Body Model - HBM"     | V <sub>ESD</sub> | -4   | -      | 4    | kV   | All Pins<br>HBM, <sup>4)</sup><br>1.5KOhm, 100pF        | P_4.1.19 |

| Electro Static Discharge Voltage<br>"Charged Device Model - CDM" | $V_{ESD}$        | -500 | _      | 500  | V    | All Pins<br>CDM <sup>5)</sup>                           | P_4.1.20 |

| Electro Static Discharge Voltage<br>"Charged Device Model - CDM" | V <sub>ESD</sub> | -750 | -      | 750  | V    | Pin 1, 18, 19, 36<br>(corner pins)<br>CDM <sup>5)</sup> | P_4.1.21 |

- 1) Not subject to production test, specified by design.

- 2) One single channel per time.

- 3) Triangular Pulse Shape (inductance discharge):  $I_D(t) = I_D(0) \cdot (1 t / t_{pulse})$ ;  $0 < t < t_{pulse}$ .

- 4) ESD susceptibility, HBM according to EIA/JESD 22-A114-B.

- 5) ESD susceptibility, Charged Device Model "CDM" EIA/JESD22-C101-C.

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

1. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### 4.2 **Functional Range**

Table 3 **Functional Range**

| Parameter               | Symbol               | l Values |      |              | Unit | Note or Test Condition                                     | Number  |  |

|-------------------------|----------------------|----------|------|--------------|------|------------------------------------------------------------|---------|--|

|                         |                      | Min.     | Тур. | Max.         |      |                                                            |         |  |

| Supply Voltages         |                      |          |      |              |      |                                                            |         |  |

| Analogue Supply Voltage | $V_{DD}$             | 4.5      | _    | 5.5          | V    | -                                                          | P_4.2.1 |  |

| Digital Supply Voltage  | $V_{\rm cc}$         | 3        | -    | $V_{\rm DD}$ | V    | -                                                          | P_4.2.2 |  |

| Digital Supply Voltage  | $V_{\rm cc}$         | $V_{DD}$ | _    | 5.5          | V    | leakage Currents (ICC) might increase if $V_{CC} > V_{DD}$ | P_4.2.3 |  |

| Power Stages            |                      |          |      |              |      |                                                            |         |  |

| Ground Current          | I <sub>GND_typ</sub> |          | 9    |              | Α    | resistive loads 1)                                         | P_4.2.4 |  |

| Temperatures            |                      |          |      |              |      |                                                            |         |  |

| Junction Temperature    | $T_{\rm j}$          | -40      | -    | 150          | °C   | -                                                          | P_4.2.5 |  |

| Junction Temperature    | $T_{\rm j}$          | -40      | _    | 175          | °C   | for 100hrs 1)                                              | P_4.2.6 |  |

|                         |                      |          |      |              |      | •                                                          |         |  |

<sup>1)</sup> Not subject to production test, specified by design

## Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **General Product Characteristics**

Note:

Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

## 4.3 Thermal Resistance

#### Table 4 Thermal Resistance

| Parameter                   | Symbol              | Values |      | Values |     | Values                                  |         | lues |  | Note or | Number |

|-----------------------------|---------------------|--------|------|--------|-----|-----------------------------------------|---------|------|--|---------|--------|

|                             |                     | Min.   | Тур. | Max.   |     | Test Condition                          |         |      |  |         |        |

| Junction to Soldering Point | $R_{\mathrm{thJC}}$ |        | 1    | 1.50   | K/W | P <sub>vtot</sub> = 3W <sup>1) 2)</sup> | P_4.3.1 |      |  |         |        |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Homogenous power distribution over all channels (All Power stages equally heated), dependent on cooling set-up.

**Power Supply**

## 5 Power Supply

#### 5.1 Description Power Supply

The TLE8110ED is supplied by analogue power supply line  $V_{DD}$  which is used for the analogue functions of the device, such as the gate control of the power stages. The digital power supply line  $V_{CC}$  is used to supply the digital part and offers the possibility to adapt the logic level of the serial output pins to lower logic levels.

Figure 5 Block Diagram Supply and Reset

#### **Description Supply**

The Supply Voltage Pins are monitored during the power-on phase and under normal operating conditions for under voltage.

If during Power-on the increasing supply voltage exceeds the Supply Power-on Switching Threshold, the internal Reset is released after an internal delay has expired.

In case of under voltage, a device internal reset is performed. The Switching Threshold for this case is the Power-on Switching threshold minus the Switching Hysteresis.

In case of under voltage on the analogue supply line  $V_{DD}$  the outputs are turned off but the content of the registers and the functionality of the logic part is kept alive. In case of under voltage on the digital supply  $V_{CC}$  line, a complete reset including the registers is performed.

After returning back to normal supply voltage and an internal delay, the related functional blocks are turned on again. For more details, refer to the chapter "Reset".

The device internal under-voltage set will set the related bits in SDS (Short Diagnosis and Device Status) to allow the micro controller to detect this reset. For more information, refer to the chapter "Control of the Device".

## Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

**Power Supply**

## **5.2** Electrical Characteristics Power Supply

## Table 5 Electrical Characteristics: Power Supply

| Parameter                                                                  | Symbol             |      | Value | S    | Unit | Note or                                                                                                                                                                    | Number        |

|----------------------------------------------------------------------------|--------------------|------|-------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                                                                            |                    | Min. | Тур.  | Max. |      | <b>Test Condition</b>                                                                                                                                                      |               |

| Digital Supply and Power-on Reset                                          | J.                 |      | 1     |      |      |                                                                                                                                                                            |               |

| Digital Supply Voltage                                                     | $V_{cc}$           | 3    | _     | 5.5  | V    | _                                                                                                                                                                          | P_5.2.1       |

| Digital Supply Current during Reset (V <sub>CC</sub> < V <sub>CCpo</sub> ) | I <sub>CCstb</sub> | -    | 15    | 20   | μА   | $f_{SCLK} = 0Hz,$<br>$S_{CS} = V_{CC},$<br>$T_{j} = 85^{\circ}C,$<br>$V_{CC} = 2.0 V,$<br>$V_{DD} > V_{CC},$                                                               | P_5.2.2<br>a) |

|                                                                            |                    | -    | 20    | 40   | μΑ   | $f_{\text{SCLK}} = 0 \text{Hz},$<br>$S_{\text{CS}} = V_{\text{CC}},$<br>$Tj = 150 ^{\circ}\text{C},$<br>$V_{\text{CC}} = 2.0 \text{V},$<br>$V_{\text{DD}} > V_{\text{CC}}$ | b)            |

| Digital Supply Current during Reset<br>(VRST > VRSTI)                      | I <sub>CCstb</sub> | -    | 2     | 5    | μА   | $f_{\text{SCLK}} = 0 \text{Hz},$<br>$S_{\text{CS}} = V_{\text{CC}},$<br>$T_{\text{j}} = 85^{\circ}\text{C},$<br>$V_{\text{DD}} > V_{\text{CC}},$                           | P_5.2.3<br>a) |

|                                                                            |                    | -    | 5     | 15   | μΑ   | $f_{\text{SCLK}} = 0 \text{Hz},$<br>$S_{\text{CS}} = V_{\text{CC}},$<br>$T_{\text{j}} = 150 ^{\circ} \text{C},$<br>$V_{\text{DD}} > V_{\text{CC}}$                         | b)            |

| Digital Supply Operating Current $V_{CC} = 3.3V$                           | I <sub>CC</sub>    | _    | 0.15  | 2    | mA   | $f_{\rm SCLK}$ = 0Hz,<br>$T_{\rm j}$ = 150°C,<br>all Channels ON,                                                                                                          | P_5.2.4<br>a) |

|                                                                            |                    | -    | 0.5   | 5    | mA   | $f_{\rm SCLK}$ = 5MHz,<br>$T_{\rm j}$ = 150°C,<br>all Channels ON,<br>1) 2)                                                                                                | b)            |

| Digital Supply Operating Current $V_{CC} = 5.5V$                           | I <sub>CC</sub>    | -    | 0.25  | 2    | mA   | $f_{\rm SCLK}$ = 0Hz,<br>$T_{\rm j}$ = 150°C,<br>all Channels ON                                                                                                           | P_5.2.5<br>a) |

|                                                                            |                    | -    | 0.8   | 10   | mA   | $f_{\rm SCLK}$ = 5MHz,<br>$T_{\rm j}$ = 150°C,<br>all Channels ON,<br>1) 2)                                                                                                | b)            |

| Digital Supply Power-on Switching<br>Threshold                             | $V_{\rm CCpo}$     | 1.9  | 2.8   | 3    | V    | V <sub>CC</sub> increasing                                                                                                                                                 | P_5.2.6       |

## Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **Power Supply**

#### Table 5 Electrical Characteristics: Power Supply

| Parameter                                                  | Symbol             | Values |      |      | Unit | Note or                                                             | Number         |

|------------------------------------------------------------|--------------------|--------|------|------|------|---------------------------------------------------------------------|----------------|

|                                                            |                    | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                               |                |

| Digital Supply Switching Hysteresis                        | $V_{CChy}$         | 100    | 300  | 500  | mV   | 1)                                                                  | P_5.2.7        |

| Analogue Supply and Power-on Reset                         |                    |        |      |      |      |                                                                     |                |

| Analogue Supply Voltage                                    | $V_{DD}$           | 4.5    | _    | 5.5  | V    | _                                                                   | P_5.2.8        |

| Analogue Supply Current during Reset $(V_{DD} < V_{DDpo})$ | I <sub>DDstb</sub> | _      | 10   | 20   | μΑ   | $f_{SCLK} = 0Hz,$<br>$T_{j} = 85^{\circ}C,$<br>$V_{DD} = 2V,$<br>1) | P_5.2.9<br>a)  |

|                                                            |                    | -      | 15   | 40   | μΑ   | $f_{SCLK} = 0$ Hz,<br>$T_j = 150$ °C,<br>$V_{DD} = 2$ V             | b)             |

| Analogue Supply Current during Reset $(V_{EN} < V_{ENI})$  | I <sub>DDstb</sub> | _      | 1    | 5    | μΑ   | $f_{SCLK} = 0Hz,$<br>$T_{j} = 85^{\circ}C,$                         | P_5.2.10<br>a) |

|                                                            |                    | -      | 2    | 15   | μΑ   | $f_{\text{SCLK}} = 0$ Hz,<br>$T_{\text{j}} = 150$ °C                | b)             |

| Analogue Supply Operating Current                          | I <sub>DD</sub>    | _      | 8    | 25   | mA   | $f_{\rm SCLK}$ = 05MHz,<br>$T_{\rm j}$ = 150°C,<br>all Channels ON, | P_5.2.11       |

| Analogue Supply Power-on Switching<br>Threshold            | $V_{ m DDpo}$      | 3      | 4.2  | 4.5  | V    | $V_{\rm DD}$ increasing                                             | P_5.2.12       |

| Analogue Supply Switching Hysteresis                       | $V_{\rm DDhy}$     | 100    | 200  | 400  | mV   | 1)                                                                  | P_5.2.13       |

| Analogue Supply Power-on Delay Time                        | $t_{ m VDDpo}$     | -      | 100  | 200  | μs   | $V_{\rm DD}$ increasing,                                            | P_5.2.14       |

<sup>1)</sup> Parameter not subject to production test. Specified by design.

<sup>2)</sup> C = 50pF connected to  $S_SO$ .

#### Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

**Reset and Enable Inputs**

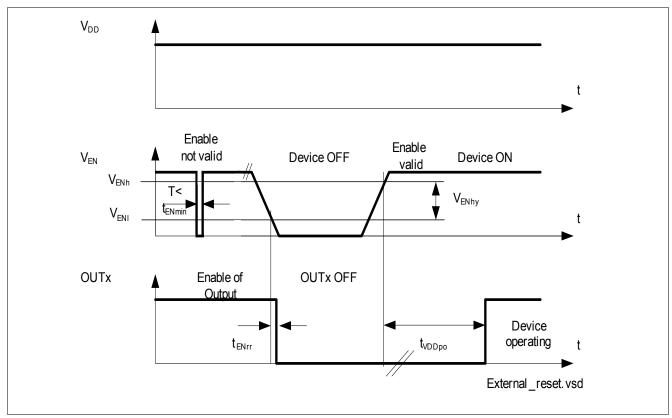

## 6 Reset and Enable Inputs

### 6.1 Description Reset and Enable Inputs

The TLE8110ED contains one Reset- and one Enable Input Pin as can be seen in Figure 5.

Description:

Reset Pin  $[\overline{RST}]$  is the main reset and acts as the internal under voltage reset monitoring of the digital supply voltage  $V_{CC}$ : As soon as  $\overline{RST}$  is pulled low, the whole device including the control registers is reset.

The Enable Pin [EN] resets only the Output channels and the control circuits. The content of the all registers is kept. This functions offers the possibility of a "soft" reset turning off only the Output lines but keeping alive the SPI communication and the contents of the control registers. This allows the read out of the diagnosis and setting up the device during or directly after Reset.

## 6.2 Electrical Characteristics Reset Inputs

#### Table 6 Electrical Characteristics: Reset Inputs

| Parameter                               | Symbol               | Values               |      |                      | Unit                 | Note or                               | Number   |

|-----------------------------------------|----------------------|----------------------|------|----------------------|----------------------|---------------------------------------|----------|

|                                         |                      | Min.                 | Тур. | Max.                 |                      | <b>Test Condition</b>                 |          |

| Reset Input Pin [RST]                   |                      |                      | •    |                      |                      |                                       |          |

| Low Level of RST                        | $V_{RSTI}$           | -0.3                 | -    | V <sub>cc</sub> *0.2 | V                    | _                                     | P_6.2.1  |

| High Level of RST                       | $V_{RSTh}$           | V <sub>CC</sub> *0.4 | -    | V <sub>cc</sub>      | V                    | _                                     | P_6.2.2  |

| RST Switching Hysteresis                | $V_{RSThy}$          | 20                   | 100  | 300                  | mV                   | 1)                                    | P_6.2.3  |

| Reset Pin pull-down Current             | I <sub>RSTresh</sub> | 20                   | 40   | 85                   | μΑ                   | $V_{\overline{RST}} = 5V$             | P_6.2.4  |

|                                         | I <sub>RSTresl</sub> | 2.4                  | _    | _                    | μΑ                   | $V_{\overline{RST}} = 0.6 \text{ V},$ |          |

| Required Reset Duration time RST        | $t_{RSTmin}$         | 2                    | _    | _                    | μs                   | 1)                                    | P_6.2.5  |

| Enable Input Pin [EN]                   |                      | 1                    |      |                      |                      |                                       | 1        |

| Low Level of EN                         | V <sub>ENI</sub>     | -0.3                 | -    | V *0.2               | V <sub>CC</sub> *0.2 | _                                     | P_6.2.6  |

| High Level of EN                        | $V_{ENh}$            | V <sub>CC</sub> *0.4 | -    | VCC                  | V                    | _                                     | P_6.2.7  |

| EN Switching Hysteresis                 | V <sub>ENhy</sub>    | 20                   | 60   | 300                  | mV                   | 1)                                    | P_6.2.8  |

| Enable Pin pull-down Current            | I <sub>ENresh</sub>  | 5                    | 35   | 85                   | μΑ                   | $V_{\overline{EN}} = 5V$              | P_6.2.9  |

|                                         | I <sub>ENresl</sub>  | 2.4                  | -    | _                    | μΑ                   | $V_{\overline{EN}} = 0.6V,$           |          |

| Enable Reaction Time (reaction of OUTx) | t <sub>ENrr</sub>    | -                    | 4    | _                    | μs                   | 1)                                    | P_6.2.10 |

| Required Enable Duration time EN        | t <sub>ENmin</sub>   | 2                    | _    | _                    | μs                   | 1)                                    | P_6.2.11 |

<sup>1)</sup> Parameter not subject to production test. Specified by design.

## Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **Reset and Enable Inputs**

Figure 6 Timing

**Power Outputs**

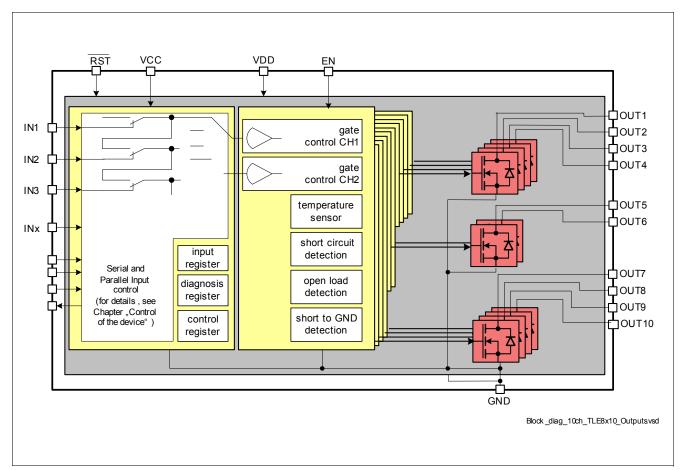

## 7 Power Outputs

#### 7.1 Description Power Outputs

The TLE8110ED is a 10 channel low-side powertrain switch. The power stages are built by N-channel power MOSFET transistors. The device is a universal multichannel switch but mostly suited for the use in Engine Management Systems [EMS]. Within an EMS, the best fit of the channels to the typical loads is:

- · Channel 1 to 4 for Injector valves or mid-sized solenoids with a nominal current requirement of 1.5A,

- Channel 5 to 6 for mid-sized solenoids or Injector valves with nominal current requirement of 1.7A,

- Channel 7 to 10 for small solenoids or relays with a nominal current requirement of 0.75A.

Channel 1 to 10 provide enhanced clamping capabilities of typically 55V best suited for inductive loads such as injectors and valves. It is recommended in case of an inductive load, to connect an external free wheeling-or clamping diode, where-ever possible to reduce power dissipation.

All channels can be connected in parallel. Channels 1 to 4, 5 to 6 and 7 to 10 are prepared by matching for parallel connection with the possibility to use a high portion of the capability of each single channel also in parallel mode (refer to **Chapter 7.4**).

Channel 5 and 6 have a higher current shut down threshold to allow to connect in parallel mode a load with high inrush-current, such as a lambda sensor heater.

Figure 7 Block Diagram of Control and Power Outputs

#### Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **Power Outputs**

#### 7.2 Description of the Clamping Structure

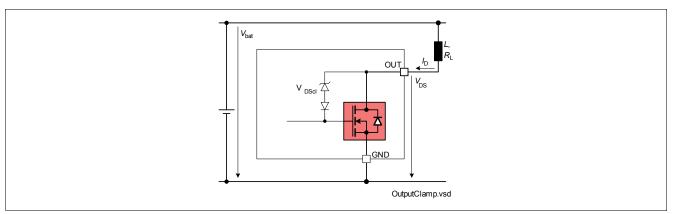

When switching off inductive loads, the potential at pin OUT rises to V<sub>DS(CL)</sub> potential, because the inductance intends to continue driving the current. The clamping voltage is necessary to prevent destruction of the device, see **Figure 8** for the clamping circuit principle. Nevertheless, the maximum allowed load inductance is limited.

Figure 8 Internal Clamping Principle

#### **Clamping Energy**

During demagnetization of inductive loads, energy has to be dissipated in the device. This energy can be calculated with following equation:

$$E = V_{DS(CL)} \cdot \frac{L_L}{R_L} \cdot \left[ I_L - \frac{V_{DS(CL)} - V_{BAT}}{R_L} \cdot ln \left( 1 + \frac{R_L \cdot I_L}{V_{DS(CL)} - V_{BAT}} \right) \right]$$

(7.1)

The maximum energy, which is converted into heat, is limited by the thermal design of the component.

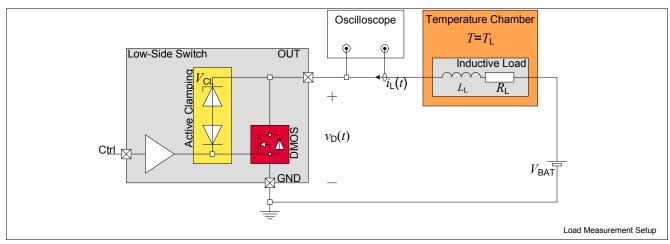

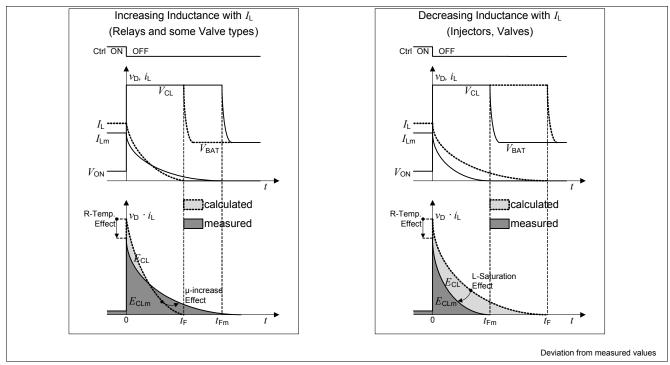

Attention: It is strongly recommended to measure the load Energy and Current under operating conditions, example of measurement setup is shown in Figure 9. Load small-signal parameters might not reflect the real load behavior under operating conditions, see Figure 10. For more details please refer to the Application Note "Switching Inductive Loads".

## Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **Power Outputs**

Figure 9  $E_{CL}$  measurement setup

Figure 10 Deviation of calculation from measurement

## Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **Power Outputs**

## 7.3 Electrical Characteristics Power Outputs

## **Table 7 Electrical Characteristics: Power Outputs**

| Parameter                                                         | Symbol            | Values |      |      | Unit | Note or                                                                   | Number  |

|-------------------------------------------------------------------|-------------------|--------|------|------|------|---------------------------------------------------------------------------|---------|

|                                                                   |                   | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                     |         |

| Output Channel Resistance                                         | ·                 |        |      |      |      |                                                                           | ·       |

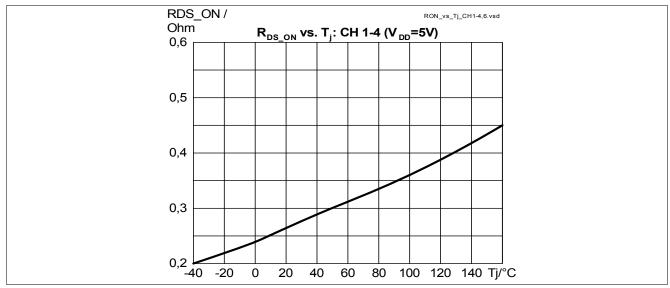

| On State Resistance<br>Channel Group 1-4                          | R <sub>DSon</sub> | -      | 0.3  | _    | Ohm  | $I_{\text{Dnom}} = 1.5A,$<br>Tj = 25°C 1)                                 | P_7.3.1 |

|                                                                   |                   | -      | 0.45 | 0.6  | Ohm  | $I_{\text{Dnom}} = 1.5A,$<br>$T_{\text{j}} = 150^{\circ}\text{C}$         |         |

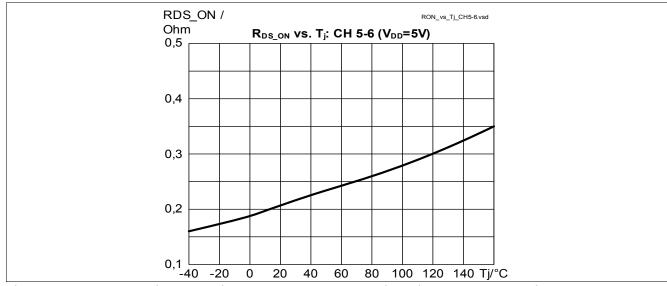

| On State Resistance<br>Channel Group 5-6                          | R <sub>DSon</sub> | -      | 0.25 | -    | Ohm  | $I_{\text{Dnom}} = 1.7A,$<br>$T_{\text{j}} = 25^{\circ}\text{C}^{1)}$     | P_7.3.2 |

|                                                                   |                   | _      | 0.35 | 0.5  | Ohm  | $I_{\text{Dnom}} = 1.7\text{A},$<br>$T_{\text{j}} = 150^{\circ}\text{C}$  |         |

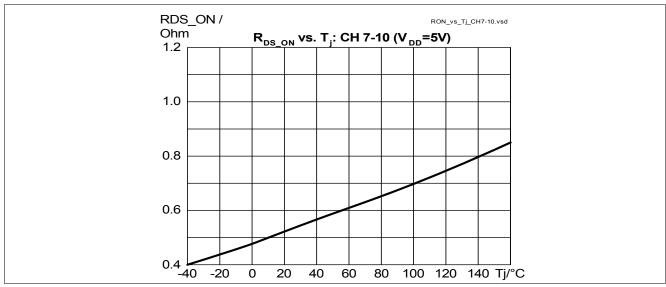

| On State Resistance<br>Channel Group 7-10                         | R <sub>DSon</sub> | -      | 0.6  | _    | Ohm  | $I_{\text{Dnom}} = 0.75A,$<br>$T_{\text{j}} = 25^{\circ}\text{C}^{1)}$    | P_7.3.3 |

|                                                                   |                   | -      | 0.85 | 1.2  | Ohm  | $I_{\text{Dnom}} = 0.75\text{A},$<br>$T_{\text{j}} = 150^{\circ}\text{C}$ |         |

| Clamping Energy - Repetitive <sup>1)2)</sup><br>Channel Group 1-4 | 3)4)              |        |      |      |      |                                                                           |         |

| Repetitive Clamping Energy                                        | $E_{AR}$          | -      | -    | 11   | mJ   | I <sub>D</sub> = 1.0A,<br>10 <sup>9</sup> cycles                          | P_7.3.4 |

|                                                                   |                   | -      | -    | 12   | mJ   | <i>I</i> <sub>D</sub> = 2.1A,<br>10 <sup>4</sup> cycles                   |         |

|                                                                   |                   | -      | -    | 15   | mJ   | <i>I</i> <sub>D</sub> = 2.6A,<br>10 cycles <sup>5)</sup>                  |         |

| Channel 5-6                                                       | ·                 |        |      | •    |      |                                                                           |         |

| Repetitive Clamping Energy                                        | E <sub>AR</sub>   | _      | _    | 13   | mJ   | <i>I</i> <sub>D</sub> = 1.3A,<br>10 <sup>9</sup> cycles                   | P_7.3.5 |

|                                                                   |                   | -      | _    | 15   | mJ   | $I_D = 2.7A$ ,<br>$10^4$ cycles                                           |         |

|                                                                   |                   | -      | -    | 20   | mJ   | <i>I</i> <sub>D</sub> = 3.2A,<br>10 cycles <sup>5)</sup>                  |         |

| Channel 7-10                                                      | ·                 |        | •    | •    |      |                                                                           |         |

| Repetitive Clamping Energy                                        | $E_{AR}$          | -      | _    | 4    | mJ   | <i>I</i> <sub>D</sub> = 0.7A,<br>10 <sup>9</sup> cycles                   | P_7.3.6 |

|                                                                   |                   | -      | _    | 4    | mJ   | <i>I</i> <sub>D</sub> = 1.4A,<br>10 <sup>4</sup> cycles                   |         |

|                                                                   |                   | -      | _    | 5    | mJ   | <i>I</i> <sub>D</sub> = 1.7A,<br>10 cycles <sup>5)</sup>                  |         |

#### Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **Power Outputs**

#### **Table 7 Electrical Characteristics: Power Outputs** (cont'd)

| Parameter                                               | Symbol            | Values |      |      | Unit | Note or                                                                                                                                                              | Number   |

|---------------------------------------------------------|-------------------|--------|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                         |                   | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                                                                                                                |          |

| Leakage Current                                         |                   |        |      |      |      |                                                                                                                                                                      |          |

| Output Leakage Current in standby mode, Channel 1 to 4  | I <sub>Doff</sub> | -      | -    | 3    | μΑ   | $V_{\rm DS} = 13.5 \text{V},$<br>$V_{\rm DD} = 5 \text{V},$<br>$T_{\rm j} = 85^{\circ} \text{C}^{1)}$                                                                | P_7.3.7  |

|                                                         |                   | _      | _    | 8    | μΑ   | $V_{\rm DS} = 13.5 \text{V},$<br>$V_{\rm DD} = 5 \text{V},$<br>$T_{\rm j} = 150 ^{\circ} \text{C}$                                                                   |          |

| Output Leakage Current in standby mode, Channel 5 to 6  | I <sub>Doff</sub> | -      | -    | 6    | μΑ   | $V_{\rm DS} = 13.5 \text{V},$<br>$V_{\rm DD} = 5 \text{V},$<br>$T_{\rm j} = 85^{\circ} \text{C}^{1)}$                                                                | P_7.3.8  |

|                                                         |                   | -      | -    | 12   | μΑ   | $V_{\rm DS} = 13.5 \text{V},$<br>$V_{\rm DD} = 5 \text{V},$<br>$T_{\rm j} = 150 ^{\circ} \text{C}$                                                                   |          |

| Output Leakage Current in standby mode, Channel 7 to 10 | I <sub>Doff</sub> | _      | _    | 2    | μΑ   | $V_{DS} = 13.5V,$<br>$V_{DD} = 5V,$<br>$T_{j} = 85^{\circ}C^{1)}$                                                                                                    | P_7.3.9  |

|                                                         |                   | _      | _    | 5    | μΑ   | $V_{\rm DS} = 13.5 \text{V},$<br>$V_{\rm DD} = 5 \text{V},$<br>$T_{\rm j} = 150 ^{\circ} \text{C}$                                                                   |          |

| Clamping Voltage                                        |                   |        | •    |      |      |                                                                                                                                                                      |          |

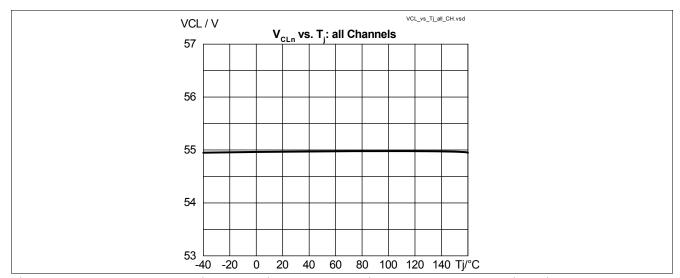

| Output Clamping Voltage, Channel 1 to 10                | V <sub>DScl</sub> | 45     | 55   | 60   | V    | -                                                                                                                                                                    | P_7.3.10 |

| Timing                                                  | 1                 |        |      |      |      |                                                                                                                                                                      |          |

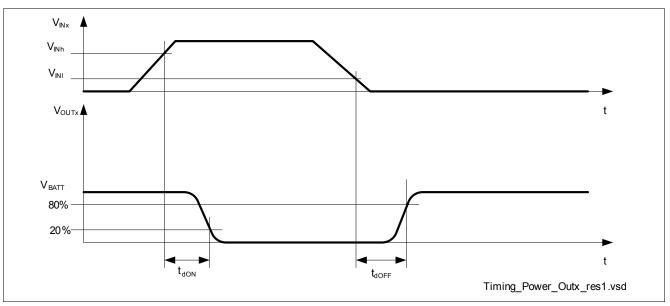

| Output Switching Frequency                              | $f_{OUTx}$        | -      | -    | 20   | kHz  | resistive load,<br>duty cycle > 25%                                                                                                                                  | P_7.3.11 |

| Turn-on Time                                            | t <sub>dON</sub>  | _      | 5    | 10   | μs   | $V_{\rm DS}$ = 20% of Vbatt<br>$V_{\rm batt}$ = 13.5V,<br>$I_{\rm DS1}$ to $I_{\rm DS6}$ = 1A,<br>$I_{\rm DS7}$ to $I_{\rm DS10}$ = 0.5A,<br>resistive load          | P_7.3.12 |

| Turn-off Time                                           | $t_{dOFF}$        | -      | 5    | 10   | μs   | $V_{\rm DS}$ = 80% of $V_{\rm batt}$<br>$V_{\rm batt}$ = 13.5V,<br>$I_{\rm DS1}$ to $I_{\rm DS6}$ = 1A,<br>$I_{\rm DS7}$ to $I_{\rm DS10}$ = 0.5A,<br>resistive load | P_7.3.13 |

<sup>1)</sup> Parameter is not subject to production test, specified by design.

<sup>2)</sup> Either one of the values has to be considered as worst case limitation. Cumulative scenario and wide range of operating conditions are treated in the Application Note "Switching Inductive Loads - TLE8110 addendum".

#### Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **Power Outputs**

- 3) This lifetime statement is an anticipation based on an extrapolation of Infineon's qualification test results. The actual lifetime of a component depends on its form of application and type of use etc. and may deviate from such statement. The lifetime statement shall in no event extend the agreed warranty period.

- 4) Triangular Pulse Shape (inductance discharge):  $I_D(t) = I_D(0) \cdot (1 t / t_{pulse})$ ;  $0 < t < t_{pulse}$ .

- 5) Repetitive operation not allowed. Starting  $T_i$  must be kept within specs. In case of high energy pulse an immediate switch-off strategy is recommended.

Figure 11 CH 1-4: typical behavior of RDS\_ON versus the junction temperature Tj

Figure 12 CH5-6: typical behavior of RDS\_ON versus the junction temperature Tj

#### **Power Outputs**

Figure 13 CH7-10: typical behavior of RDS\_ON versus the junction temperature Tj

Figure 14 All Channels: typical behavior of the clamping voltage versus the junction temperature

#### Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

#### **Power Outputs**

Figure 15 Timing of Output Channel switching (resistive load)

## 7.4 Parallel Connection of the Power Stages

The TLE8110ED is equipped with a structure which improves the capability of parallel-connected channels. The device can be "informed" via the PMx.PMx - bits (see chapter "Control of the device") which of the channels are connected in parallel. The input channels can be mapped to the parallel connected output channels in order to apply the PWM signals. This feature allows a flexible adaptation to different load situations within the same hardware setup.

In case of overload the ground current and the power dissipation is increasing. The application has to take into account that all maximum ratings are observed (e.g. operating temperature  $T_J$  and total ground current  $I_{GND}$ , see Maximum Ratings). In case of parallel connection of channels with or w/o PM-bit set, the defined maximum clamping energy must not be exceeded.

All stages are switched on and off simultaneously. The  $\mu$ C has to ensure that the stages which are connected in parallel have always the same state (on or off). The PM-bit should be set according to the parallel connected power stages in order to achieve the best possible performance.

The PM-bit is set to its default value in case of a Reset event (Reset pin Low or at Digital Supply undervoltage), that means the improved Parallel Mode is no longer active. In the event of reset the channels will be switched off causing the clamping energy to be dissipated with low performance of the current sharing as without PM-bit set, for more details please refer to the Application Note Switching Inductive Loads - TLE8110 addendum.

The performance during parallel connection of channels is specified by design and not subject to the production test. All channels at the same junction temperature level.

#### **ON-Resistance**

The typical ON-Resistance  $R_{DSsum(typ)}$  of parallel connected channels is given by:

$$R_{DSsum(typ)} = \left[ \frac{1}{R_{DSon, n(typ)}} + \frac{1}{R_{DSon, n+1(typ)}} \right]^{-1}$$

(7.2)