Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## LIN Transceiver with integrated Voltage Regulator

#### 1 Overview

#### **Features**

- Single-wire LIN transceiver for transmission rates up to 20 kBit/s

- Compliant to ISO 17987-4, LIN specification 2.2A and SAE J2602

- 5 V or 3.3 V Low Drop-Out Linear Voltage Regulator with 70 mA current capability

- Stable with ceramic output capacitor of 1 μF

- Ultra low current consumption in Sleep Mode of max. 16μA

- Ultra low current consumption in Standby Mode: typical 20 μA

- · Very low leakage current on the BUS pin

- V<sub>CC</sub> undervoltage detection with RESET output

- TxD protected with dominant time-out function and state check after mode change to Normal Operation Mode

- · Initialization watchdog with automatic transition to Sleep Mode

- BUS short to V<sub>BAT</sub> protection and BUS short to GND handling

- Over-temperature protection and supply undervoltage detection

- Very high ESD robustness; ±8kV according to IEC61000-4-2

- Optimized for high Electromagnetic Compatibility (EMC);

Very low emission and high immunity to interference

- Available in standard PG-DSO-8 and leadless PG-TSON-8 packages

- PG-TSON-8 package supports Automated Optical Inspection (AOI)

1

- Green Product (RoHS compliant)

- AEC Qualified

#### **Applications**

- LIN slave satellite modules

- Window lifters

- Rain/light sensors

- Sun roof control modules

- · Wiper modules

- Ambient lighting

#### LIN Transceiver with integrated Voltage Regulator

#### Overview

#### Description

The TLE8457 is a monolithic integrated LIN transceiver and Low Drop-Out voltage regulator. The device is designed to supply a microcontroller and peripherals with up to 70mA, provide protection through  $V_{\rm CC}$  undervoltage reset, while also offering bi-directional bus communication compliant to LIN Specification 2.2A and SAE J2602. With the ultra low quiescent current consumption of typical 20  $\mu$ A in Standby Mode the TLE8457 is especially suited for applications that are permanently supplied by the battery.

Based on the Infineon BiCMOS technology the TLE8457 provides excellent ESD robustness together with a very high level of electromagnetic compatibility (EMC). The TLE8457 is AEC qualified and tailored to withstand the harsh conditions of the automotive environment.

| Туре       | LDO V <sub>CC</sub> Output Voltage | Package   | Marking |

|------------|------------------------------------|-----------|---------|

| TLE8457ASJ | 5 V                                | PG-DSO-8  | 8457A   |

| TLE8457ALE | 5 V                                | PG-TSON-8 | 8457A   |

| TLE8457BSJ | 3.3 V                              | PG-DSO-8  | 8457B   |

| TLE8457BLE | 3.3 V                              | PG-TSON-8 | 8457B   |

## LIN Transceiver with integrated Voltage Regulator

# **Table of Contents**

| 1                                                                                                                                           | Overview                                                                                                                                                                                                                                                                                                                         | 1                                |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|                                                                                                                                             | Table of Contents                                                                                                                                                                                                                                                                                                                | 3                                |

| 2                                                                                                                                           | Block Diagram                                                                                                                                                                                                                                                                                                                    | 4                                |

| <b>3</b><br>3.1<br>3.2                                                                                                                      | Pin Configuration                                                                                                                                                                                                                                                                                                                | 5                                |

| 4                                                                                                                                           | Functional Description                                                                                                                                                                                                                                                                                                           | 6                                |

| 4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.2<br>4.2.1<br>4.2.2<br>4.3<br>4.3.1<br>4.3.2<br>4.4<br>4.5<br>4.5.1<br>4.5.2 | Operating Modes  Normal Operation Mode  Standby Mode Init Mode Sleep Mode Bus Wake-up event Mode Transition via EN pin  Power Supplies Power-Up / Power-Down V <sub>S</sub> Undervoltage Detection  Voltage Regulator VCC Undervoltage Detection Reset Output Initialization Watchdog LIN Transceiver TxD Time-out Short Circuit | 6 8 9 10 12 12 13 14 14 15 17 18 |

| 4.6<br><b>-</b>                                                                                                                             | Over-temperature Protection                                                                                                                                                                                                                                                                                                      |                                  |

| 5<br>5.1<br>5.2<br>5.3<br>6                                                                                                                 | General Product Characteristics  Absolute Maximum Ratings  Functional Range  Thermal Characteristics  Electrical Characteristics                                                                                                                                                                                                 | . 19<br>. 20<br>. 21             |

| 6.1<br>6.2                                                                                                                                  | Functional Device Characteristics                                                                                                                                                                                                                                                                                                | . 22                             |

| 7<br>7.1<br>7.2<br>7.3<br>7.4                                                                                                               | Application Information  Application Example  ESD Robustness according to IEC61000-4-2  Transient Robustness according to ISO 7637-2  LIN Physical Layer Compatibility                                                                                                                                                           | . 29<br>. 30                     |

| 8                                                                                                                                           | Package Outlines                                                                                                                                                                                                                                                                                                                 | . 31                             |

| 9                                                                                                                                           | Revision History                                                                                                                                                                                                                                                                                                                 | . 32                             |

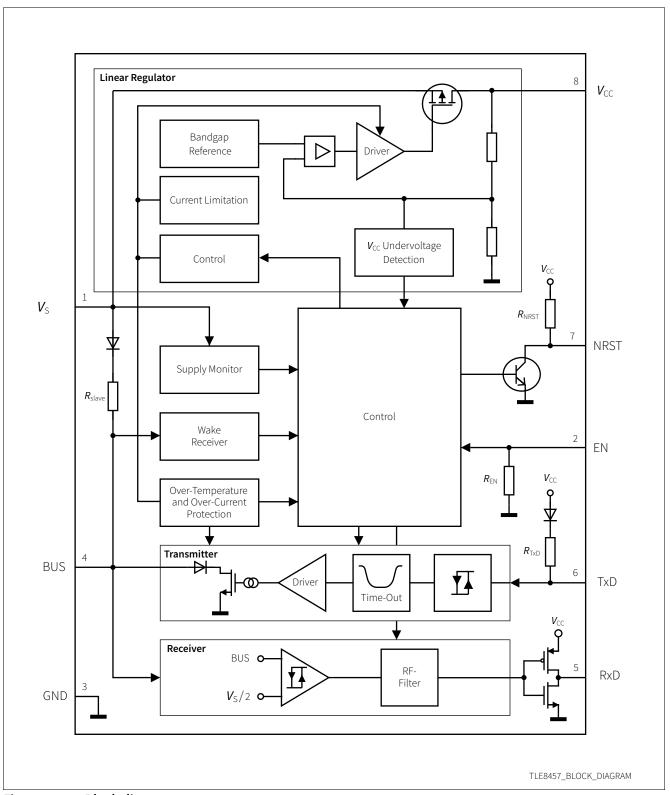

**Block Diagram**

# 2 Block Diagram

Figure 1 Block diagram

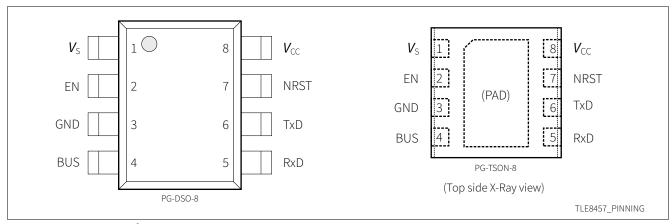

**Pin Configuration**

# 3 Pin Configuration

## 3.1 Pin Assignment

Figure 2 Pin configuration

## 3.2 Pin Definitions and Functions

| Pin | Symbol          | Function                                                                                                          |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>S</sub>  | Battery Supply Voltage; Decoupling capacitor required                                                             |

| 2   | EN              | Enable Input; Integrated pull-down resistor Logical "high" to select Normal Operation Mode                        |

| 3   | GND             | Ground                                                                                                            |

| 4   | BUS             | BUS Input / Output;<br>Integrated LIN Slave Termination                                                           |

| 5   | RxD             | Receive Data Output;  Monitors the LIN bus signal in Normal Operation Mode Indicates a wake-up event in Init Mode |

| 6   | TxD             | Transmit Data Input; Integrated pull-up resistor Logical "low" to drive a dominant signal on the LIN bus          |

| 7   | NRST            | Undervoltage Reset Output;<br>Integrated pull-up resistor<br>Logical "low" during Reset                           |

| 8   | V <sub>cc</sub> | Voltage Regulator Output; Output capacitor requirements specified in Functional Device Characteristics            |

| PAD | _               | Connect to PCB heat sink area. Do not connect to other potential than GND                                         |

## 4 Functional Description

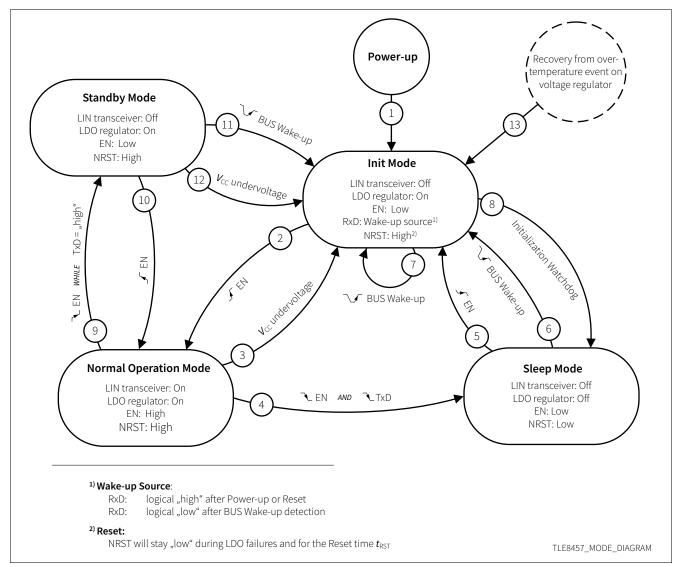

### 4.1 Operating Modes

The operation mode of the TLE8457 is controlled with the EN and TxD input pins (see Figure 3 and Table 2). The TLE8457 has 3 major operation modes:

- Normal Operation Mode

- Standby Mode

- Sleep Mode

Additionally the TLE8457 has an Init Mode that is automatically entered when powering up, detecting wakeup events or in case of malfunctions.

Figure 3 Operation mode state diagram

## LIN Transceiver with integrated Voltage Regulator

#### **Functional Description**

Table 1 Operation mode transitions

| No. | Reason for transition                        | Comment                                                                                                                                                               |

|-----|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Power-on detection                           | The $V_{\rm S}$ supply voltage rise above the $V_{\rm S,PON}$ power-on reset level                                                                                    |

| 2   | Mode change with EN input                    | Triggered by logical "high" level                                                                                                                                     |

| 3   | V <sub>CC</sub> undervoltage detection       | $V_{\rm CC}$ output voltage fall below the reset threshold level                                                                                                      |

| 4   | Mode change with EN and TxD inputs           | Triggered by logical "low" level on EN and TxD                                                                                                                        |

| 5   | Mode change with EN input                    | Triggered by logical "high" level                                                                                                                                     |

| 6   | Bus wake-up detection                        | RxD set "low" for signalling the bus wake-up event to the microcontroller                                                                                             |

| 7   | Bus wake-up detection                        | RxD set "low" for signalling the bus wake-up event to the microcontroller                                                                                             |

| 8   | Initialization watchdog timer elapsed        | Forced transition to Sleep Mode because of no response from microcontroller after power-on, wake-up, reset or if local errors are preventing $V_{\rm CC}$ to power up |

| 9   | Mode change with EN and TxD inputs           | Triggered by logical "low" level on EN while TxD is held "high"                                                                                                       |

| 10  | Mode change with EN input                    | Triggered by logical "high" level                                                                                                                                     |

| 11  | Bus wake-up detection                        | RxD set "low" for signalling the bus wake-up event to the microcontroller                                                                                             |

| 12  | V <sub>CC</sub> undervoltage detection       | Detection of failure due to $V_{\rm CC}$ undervoltage or recovery from an over-temperature event                                                                      |

| 13  | Recovery from LDO over-<br>temperature event | When over-temperature on the LDO is detected the TLE8457 is disabled. After recover the device is activated in Init Mode                                              |

## Table 2 Operating Mode Control

| Mode                | Control |                    | Function | onality            |             | Comments                                                             |  |

|---------------------|---------|--------------------|----------|--------------------|-------------|----------------------------------------------------------------------|--|

|                     | EN      | TxD                | $V_{cc}$ | NRST               | RxD         |                                                                      |  |

| Sleep               | Low     | Low                | Off      | Low                | Floating    | -                                                                    |  |

| Init                | Low     | High <sup>1)</sup> | On       | High <sup>2)</sup> | Low<br>High | RxD "low" after a bus wake-up<br>RxD "high" after power-up or reset  |  |

| Standby             | Low     | High <sup>1)</sup> | On       | High               | High        | -                                                                    |  |

| Normal<br>Operation | High    | Low<br>High        | On       | High               | Low<br>High | RxD reflects the signal on the bus TxD driven by the microcontroller |  |

<sup>1)</sup> The TxD input has a pull-up structure to  $V_{\rm CC}$  and is default set to logical "high" if left open.

<sup>2)</sup> NRST is logical "low" during  $V_{CC}$  undervoltage and while issuing a reset pulse to the microcontroller.

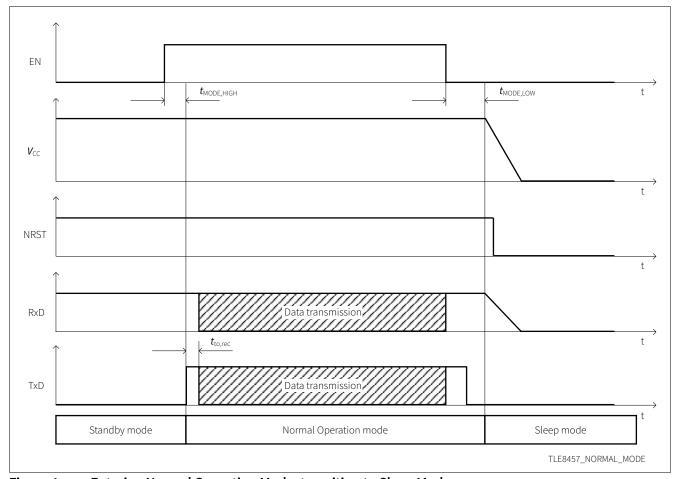

#### 4.1.1 **Normal Operation Mode**

In Normal Operation Mode both the voltage regulator and the LIN transceiver are active. The TLE8457 supports data transmission rates up to 20 kBit/s: Data from the microcontroller is transmitted to the LIN bus via the TxD input, while the receiver detects the data stream on the LIN bus and forwards it to the RxD output. After entering Normal Operation Mode the TLE8457 requires a logical "high" signal for the time  $t_{to,rec}$  on the

TxD input before releasing the data communication; The transmitter remains deactivated as long as the signal on the TxD input pin remains logical "low", preventing possible bus communication disturbance (see Figure 4).

From Normal Operation Mode the TLE8457 can be set to Standby Mode or Sleep Mode.

Figure 4 **Entering Normal Operation Mode, transition to Sleep Mode**

#### Standby Mode 4.1.2

Standby Mode is a low power mode with ultra low quiescent current consumption while the voltage regulator remains active, supplying for example a microcontroller in Stop mode. No LIN bus communication is possible, the transmitter and the receiver are disabled. The low power receiver is still active and the device can wakeup by a message on the LIN bus.

For changing the operation mode change from Standby Mode to Sleep Mode, the device has first to be set in Normal Operation Mode, then in Sleep Mode (see Figure 4).

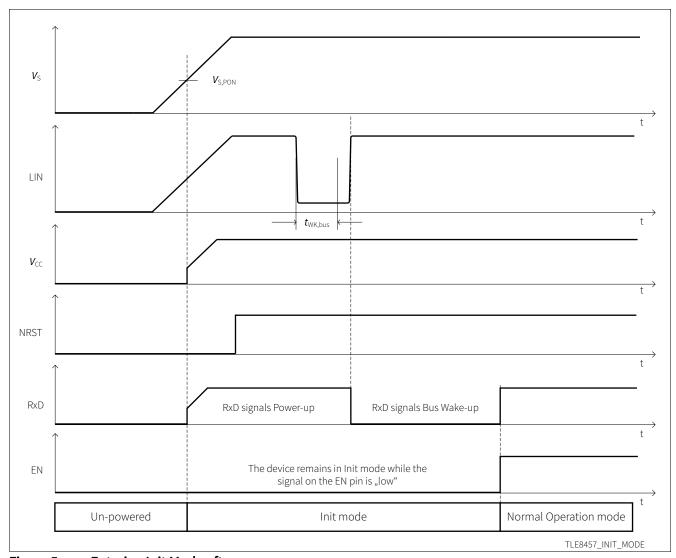

#### 4.1.3 Init Mode

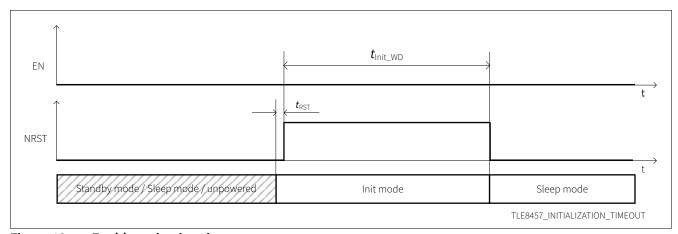

After a power-up event the TLE8457 enters Init Mode by default. In this mode the LIN transceiver is disabled, but the voltage regulator is switched on. Following the linear voltage regulator has reached its nominal output voltage  $V_{CC}$  and the NRST output set "high", the external microcontroller can change the mode to Normal Operation Mode. If the Initialization Watchdog timer elapses before a "high" signal is detected on the EN input, the TLE8457 will autonomously transition to Sleep Mode (see "Initialization Watchdog" on Page 15). The Initialization Watchdog protection in Init Mode is always activated after starting up the voltage regulator and after a reset pulse, triggered by the NRST output going "high".

In Init Mode the TLE8457 indicates wake-up information on the RxD output. After a power-up and reset event, the RxD output will be "high". If the TLE8457 is in Init Mode after BUS wake-up detection, the RxD output will be "low".

Transitions to Init Mode can be controlled with the EN input when in Sleep Mode, or automatic forced after:

- Bus wake-up event on the BUS pin.

- Power-up event on the supply  $V_s$ .

- Power-on reset caused by the supply  $V_s$ .

- Voltage regulator failure event due to V<sub>S</sub> undervoltage.

- Recovery of an over-temperature event on the voltage regulator.

Figure 5 Entering Init Mode after power-up

### 4.1.4 Sleep Mode

Sleep Mode is a low power mode with quiescent current consumption reduced to a minimum while the device can still wake-up by a message on the LIN bus. Both the transceiver and the voltage regulator are switched off.

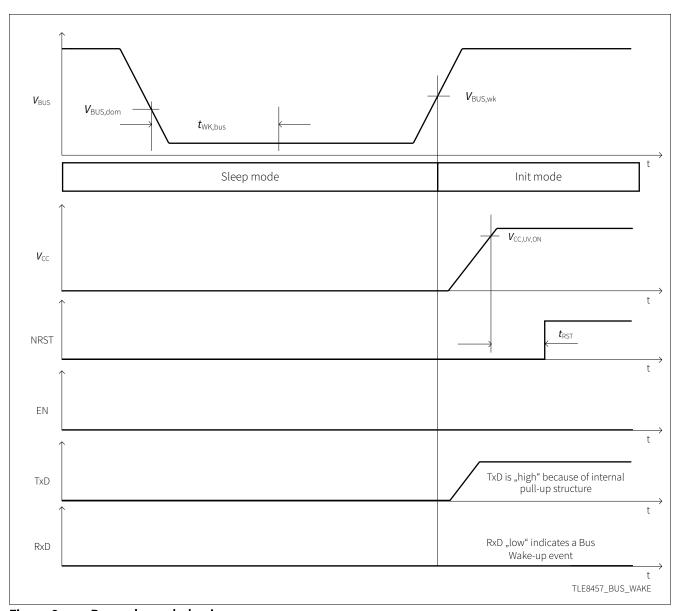

#### 4.1.5 Bus Wake-up event

A bus wake-up event, also called remote wake-up, causes a transition from a low power mode to Init Mode. A falling edge on the LIN bus, followed by a dominant bus signal for the time  $t_{\rm WK,bus}$  results in a bus wake-up event. The mode change to Init Mode becomes active with the following rising edge on the LIN bus, when bus voltage exceeds  $V_{\rm BUS,wk}$ . The TLE8457 remains in low power mode until it detects a state change on the LIN bus from dominant to recessive (see **Figure 6**). In Init Mode a logical "low" signal on the RxD output indicates a bus wake-up event.

In case the TLE8457 detects a bus wake-up event while already being in Init, the wake-up event will be signalled with a logical "low" level on RxD and override the previous wake source (see Figure 5).

Figure 6 Bus wake-up behavior

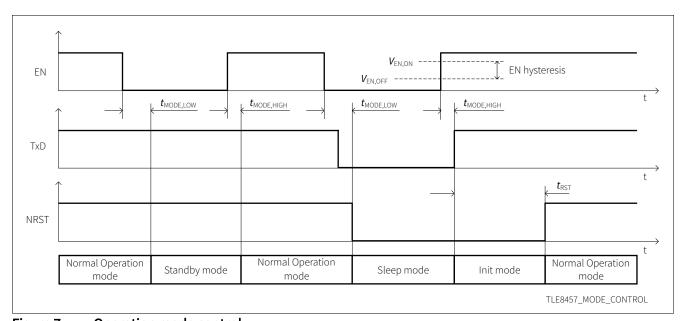

#### 4.1.6 Mode Transition via EN pin

The EN input is used for operation mode control of the TLE8457. By setting the EN input logical "high" for the time  $t_{\text{MODE},\text{HIGH}}$  while being in Init Mode or Standby Mode, a transition to Normal Operation Mode will be triggered.

If the voltage level at the EN input is set logical "high" while the TLE8457 is in Sleep Mode, a transition to Init Mode is initiated. If the EN input is continuously held "high" though powering up the voltage regulator and the following reset pulse, Normal Operation Mode will be entered.

From Normal Operation Mode the TLE8457 can be set to either Sleep Mode or Standby Mode. If the EN input is set "low" for the time  $t_{\text{MODE,LOW}}$  while the TxD input is held logical "high", the mode will change to Standby Mode. For a transition to Sleep Mode, the TxD must be set logical "low" before the time  $t_{\text{MODE,LOW}}$  elapses after EN goes "low" (see **Figure 7**). It is recommended to program a short delay time from EN is set "low" until TxD is set "low", for preventing driving the bus dominant though mode transition to Sleep Mode.

The EN input has an integrated pull-down resistor to ensure the device remains in a low power mode if the EN input is left open. The EN input has an integrated hysteresis (see Figure 7).

The TLE8457 changes the operation modes regardless of the signal on the BUS pin. In the case of a short circuit failure between the LIN bus and GND, resulting in a permanent dominant signal, the TLE8457 can be set to Sleep Mode.

Figure 7 Operation mode control

The EN input is blocked while the TLE8457 is in Init Mode and NRST is "low", no mode transitions to Normal Operation Mode is possible while a reset pulse is issued. After the NRST output goes "high", mode control with the EN input is released. At the same time the Initialization Watchdog timer starts (see "Initialization Watchdog" on Page 15).

Note:

If the TLE8457 is being forced to Sleep Mode by the Initialization Watchdog while the EN input is externally being held at a logical "high" level, the device will reinitiate Init Mode after the VCC voltage has been discharged below ~1 V. In such applications additional supervision means are recommended.

### 4.2 Power Supplies

The TLE8457 is designed for being supplied by the battery line through an external reverse polarity protection diode at the  $V_S$  pin (see **Figure 18**). An input capacitor is needed for damping input line transients.

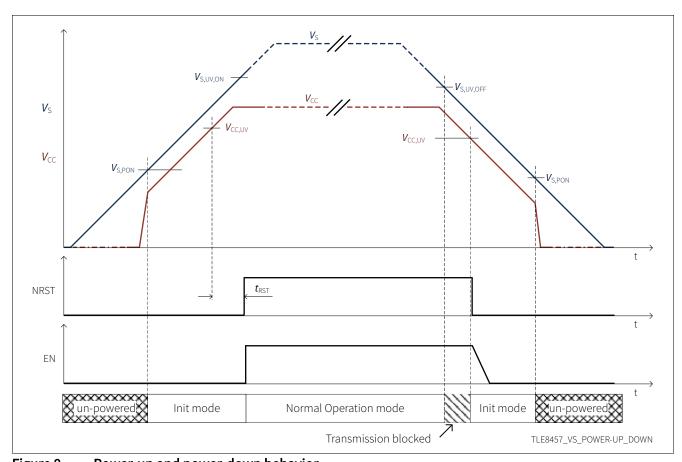

## 4.2.1 Power-Up / Power-Down

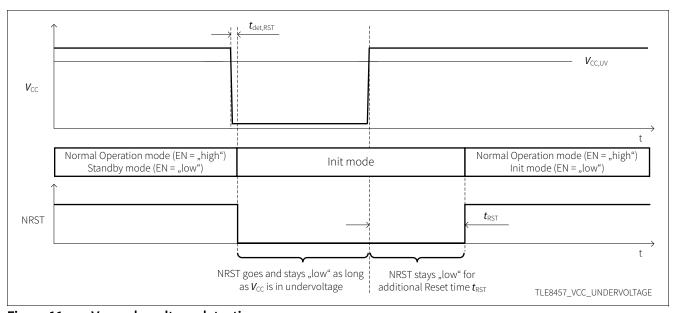

During power-up the TLE8457 will enter Init Mode when the  $V_S$  supply reaches the power-on reset level  $V_{S,PON}$ . The voltage regulator output  $V_{CC}$  will track the  $V_S$  supply voltage until  $V_{CC}$  reaches its nominal voltage level. As  $V_{CC}$  reaches the under-voltage level  $V_{CC,UVC}$ , a reset pulse is issued, the NRST output will stay logical "low" for the reset time  $t_{RST}$  and then be set logical "high". As NRST goes "high", the EN input will become active and the TLE8457 can change operating mode accordingly (see **Table 2**).

Figure 8 Power-up and power-down behavior

While powering down the TLE8457 will block the LIN transmitter if being in Normal Operation Mode as the  $V_{\rm S}$  supply voltage falls below  $V_{\rm S,UV,OFF}$ . The voltage regulator will start tracking the  $V_{\rm S}$  supply voltage when falling below  $V_{\rm CC} + V_{\rm DR}$ . As  $V_{\rm CC}$  falls below the undervoltage level  $V_{\rm CC,UV}$  the NRST output will be set logical "low" and the TLE8457 will enter Init Mode. When the  $V_{\rm S}$  supply voltage falls below the power-on-reset level  $V_{\rm S,PON}$  the voltage regulator will be disabled and the TLE8457 considered un-powered.

### 4.2.2 V<sub>S</sub> Undervoltage Detection

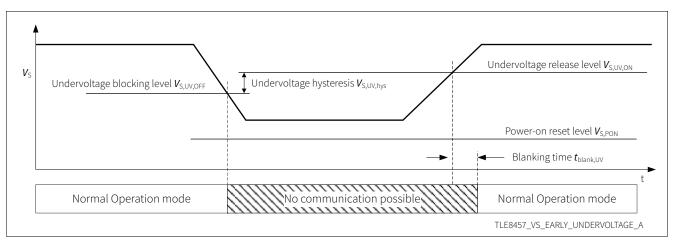

Figure 9 V<sub>S</sub> early undervoltage detection

The TLE8457 has an undervoltage detection on the supply pin  $V_S$  with two different thresholds:

- In Normal Operation Mode the TLE8457 blocks the communication between the LIN bus and the

microcontroller when detecting an early undervoltage event. The RxD output will be set "high". However,

no mode change will occur. After V<sub>S</sub> rises above the undervoltage release level V<sub>S,UV,REL</sub>, the bus

communication interface will be released when the signal on the TxD input goes "high". See Figure 9.

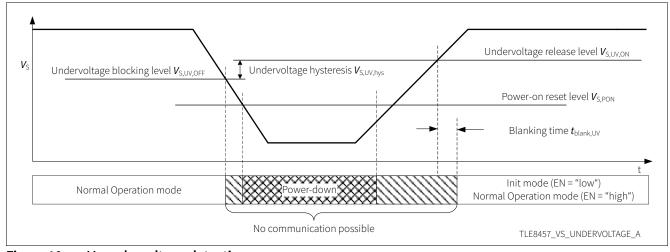

- In case the power supply V<sub>S</sub> drops below the power-on reset level V<sub>S,PON</sub> the TLE8457 not only blocks the

transceiver communication, it also changes the operation mode to Init mode after recovery of V<sub>S</sub>, see

Figure 10. In Init Mode the TLE8457 indicates a power-up event on the RxD pin. The power-on reset

detection is active in all operation modes.

Figure 10 V<sub>S</sub> undervoltage detection

### 4.3 Voltage Regulator

The TLE8457 has an integrated voltage regulator dedicated for supplying microcontrollers and/or on-board sensors under harsh automotive environment conditions. It can supply a load current up to 70 mA with an output voltage tolerance within  $\pm$  2%. Because of the ultra low current consumption, the TLE8457 is perfectly suited for applications permanently connected to the battery supply. Additionally, in Sleep Mode, the voltage regulator is switched off and an even lower quiescent current can be achieved.

The voltage regulator output is protected against undervoltage, overcurrent, over-temperature and power-up failures. In case the load current rises above the functional range, for example during  $V_{\rm CC}$  short circuits, the output current is limited to  $I_{\rm CC,lim}$ . Therefore the  $V_{\rm CC}$  output voltage will drop and a reset pulse will be issued if falling below the undervoltage reset threshold.

The  $V_{CC}$  supply output provides a stable supply voltage with output capacitors down to 1  $\mu$ F, including low ESR multi-layer ceramic capacitors.

### 4.3.1 VCC Undervoltage Detection

The TLE8457 has undervoltage detection on the voltage regulator  $V_{\rm CC}$  output. If the  $V_{\rm CC}$  voltage falls below the undervoltage threshold  $V_{\rm CC,UV}$  for longer than detection time  $t_{\rm det,RST}$  the NRST output will be set logical "low" and the TLE8457 will automatically enter Init Mode and start the Initialization Watchdog (see **Chapter 4.3.2** and **Chapter 4.4**).

Figure 11 V<sub>CC</sub> undervoltage detection

#### 4.3.2 Reset Output

The NRST output is used for issuing reset pulses to for example an external microcontroller. In case of voltage regulator undervoltage or over-temperature events the NRST output will go "low" and a mode transition to Init Mode will be triggered. The NRST output will stay "low" until a complete recovery from the failure and additionally for the reset time  $t_{\rm RST}$ , then go "high" (see Figure 11).

While the TLE8457 is in Init Mode and NRST is "low" mode transition to Normal Operation Mode is blocked.

The NRST pin is internally pulled up to  $V_{CC}$ . If needed in the application, an additional external pull-up resistor can be implemented.

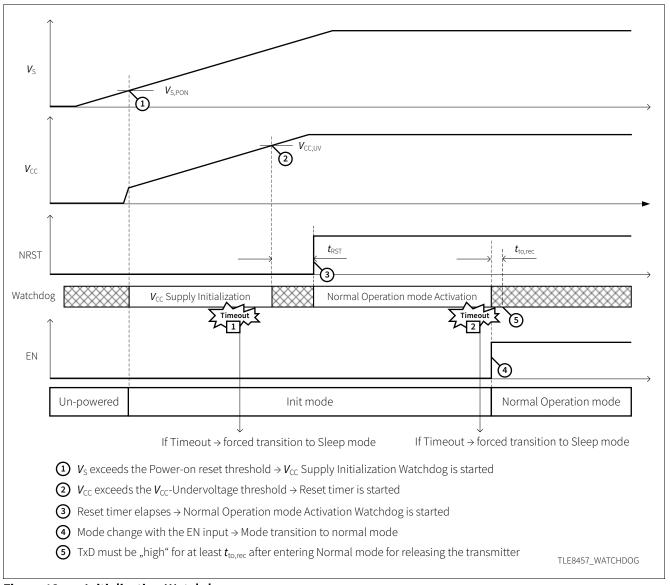

#### 4.4 Initialization Watchdog

The TLE8457 features an enhanced Initialization Watchdog timer for detection of local failures and error handling for minimizing system current consumption. The benefit of this safety function is to prevent a malfunctioning ECU being stuck in Init Mode with high current consumption and draining the car battery. The Initialization Watchdog is only active in Init Mode, with the two use cases:  $V_{\rm CC}$  supply initialization and Normal Operation Mode activation.

Figure 12 Initialization Watchdog

#### **VCC Supply Initialization**

The  $V_{\rm CC}$  supply Initialization watchdog is detecting if local errors on the ECU is preventing the  $V_{\rm CC}$  supply to power up correctly because of short circuits to ground or if components on the board are drawing too high currents. The timer is started when the linear regulator is switched on after power-up events or after mode transitions to Init mode triggered by either bus wake-up or the EN input being set "high" in Sleep Mode. Additionally, the timer will start when detecting  $V_{\rm CC}$  undervoltage and after recovery from an overtemperature event.

#### LIN Transceiver with integrated Voltage Regulator

#### **Functional Description**

In case the  $V_{\rm CC}$  voltage rise above the  $V_{\rm CC,UV}$  undervoltage threshold before the timer elapses,  $V_{\rm CC}$  is considered successfully initialized and the timer is disabled. If the timer elapses before  $V_{\rm CC}$  powers up correctly, the TLE8457 will autonomously transition to Sleep Mode.

#### **Normal Operation Mode Activation**

After the TLE8457 has generated a reset pulse the Initialization Watchdog is started for monitoring the activation of Normal Operation Mode. The microcontroller must set the EN input "high" before the timer elapses after  $t_{\text{Init WD}}$ , else the TLE8457 will autonomously transition to Sleep Mode.

Figure 13 Enable activation time-out

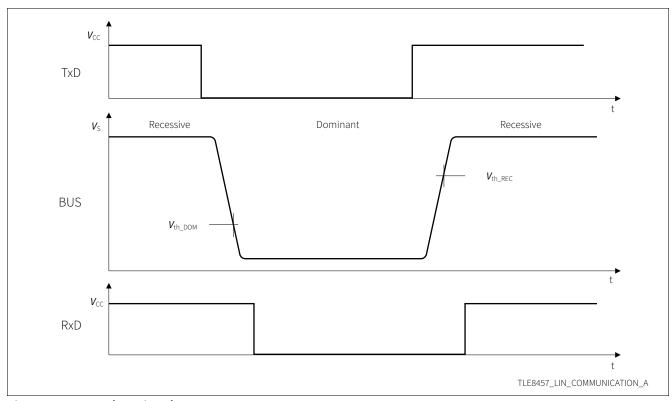

#### 4.5 LIN Transceiver

The LIN interface is a single wire, bi-directional bus, used for in-vehicle networks. The integrated LIN transceiver of the TLE8457 is the interface between the microcontroller and the physical LIN bus (see Figure 18). Data from the microcontroller is driven to the LIN bus via the TxD input. The transmit data stream on the TxD input is converted to a LIN bus signal with optimized slew rates in order to minimize the electromagnetic emission of the LIN network. The RxD output reads back the information from the LIN bus to the microcontroller. The receiver has an integrated filter network for noise suppression from the LIN bus and to increase the electromagnetic immunity level of the transceiver.

The LIN specification defines two valid bus levels (see Figure 14):

- Dominant state with the LIN bus voltage level near GND, actively driven by a transceiver.

- Recessive state with the LIN bus voltage pulled up to the supply voltage  $V_S$  through the bus termination.

By setting the TxD input of the TLE8457 to a logical "low" signal, the transceiver generates a dominant level on the BUS interface pin. The receiver reads back the signal on the LIN bus and indicates the dominant LIN bus signal with a logical "low" on the RxD output to the microcontroller. By setting the TxD input "high", the transceiver sets the LIN interface pin to the recessive level. At the same time the recessive level on the LIN bus is indicated by a logical "high" signal on the RxD output.

Every LIN network consists of a master node and one or more slave nodes. To configure the TLE8457 for master node applications, a termination resistor of 1 k $\Omega$  and a diode must be connected between the LIN bus and the power supply  $V_S$  (see Figure 18).

Figure 14 LIN bus signals

#### LIN Transceiver with integrated Voltage Regulator

#### **Functional Description**

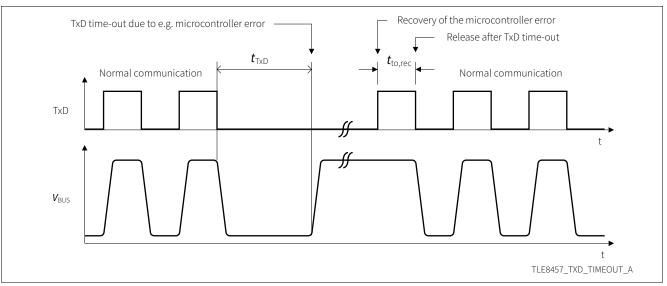

#### 4.5.1 TxD Time-out

The TxD time-out feature protects the LIN bus against permanent blocking in case the logical signal on the TxD input is continuously "low", caused by for example a malfunctioning microcontroller or a short circuit on the printed circuit board. In Normal Operation Mode, a logical "low" signal on the TxD input for time  $t > t_{TxD}$  disables the transmitter's output driver stage (see **Figure 15**). The receiver will remain active and the data on the bus are still monitored on the RxD output.

The TLE8457 will release the output stage after a TxD time-out event first when detecting a logical "high" signal on the respective TxD input for the time  $t_{\text{to,rec}}$ .

Figure 15 TxD time-out

#### 4.5.2 Short Circuit

The BUS pin of TLE8457 can withstand short circuits to either GND or to the power supply  $V_S$ . The integrated over-temperature protection may disable the transmitter if a permanent short circuit on the BUS pin causes the TLE8457 to overheat.

#### 4.6 Over-temperature Protection

The TLE8457 has two independent over-temperature detectors for protecting the device against thermal overstress; on the voltage regulator pass element and on the LIN bus transmitter. In case the junction temperature at the LIN transmitter increase above the thermal shut down level  $T_{\rm JSD}$ , it will be disabled until the transmitter's junction temperature cools down below  $T_{\rm JSD}$  -  $\Delta T$ . No other effect nor mode change will occur. After a LIN transmitter over-temperature recovery the TxD input requires a logical "high" signal before restarting data transmission.

If an over-temperature event is detected on the voltage regulator, it will be disabled and the NRST output will be set "low". During the over-temperature condition no functionality of the TLE8457 is available. After the junction temperature cools down below  $T_J < T_{JSD} - \Delta T$ , the TLE8457 will automatically enter Init Mode and be reactivated.

Note:

Depending on the over-temperature circumstance, either only the LIN transmitter will detect over-temperature, for example due to bus short circuit or severe EMC injection, only the voltage regulator detector or both (simultaneously or sequentially).

**General Product Characteristics**

#### 5 General Product Characteristics

### 5.1 Absolute Maximum Ratings

Table 3 Absolute Maximum Ratings Voltages, Currents and Temperatures<sup>1)</sup>

All voltages with respect to ground; positive current flowing into pin; unless otherwise specified

| Parameter                                                | Symbol              |      | Value | 5                     | Unit | Note or                                              | Number   |

|----------------------------------------------------------|---------------------|------|-------|-----------------------|------|------------------------------------------------------|----------|

|                                                          |                     | Min. | Тур.  | Max.                  |      | <b>Test Condition</b>                                |          |

| Voltage                                                  | 11                  |      |       |                       |      |                                                      | 1        |

| Supply input voltage                                     | $V_{S}$             | -0.3 | _     | 45                    | V    | LIN Spec 2.2A (Par. 11)                              | P_5.1.1  |

| Bus input voltage                                        | $V_{BUS}$           | -27  | _     | 40                    | V    | -                                                    | P_5.1.2  |

| Logic voltages at EN and TxD                             | $V_{\rm logic,in}$  | -0.3 | -     | 7.0                   | V    | -                                                    | P_5.1.3  |

| Logic voltages at RxD and NRST                           | $V_{\rm logic,out}$ | -0.3 | -     | V <sub>CC</sub> + 0.3 | V    | -                                                    | P_5.1.4  |

| Voltage regulator output                                 | $V_{cc}$            | -0.3 | -     | 7.0                   | V    | -                                                    | P_5.1.5  |

| Currents                                                 |                     |      |       |                       | •    |                                                      |          |

| Output current at RxD                                    | I <sub>RxD</sub>    | -15  | _     | 15                    | mA   | _                                                    | P_5.1.6  |

| Output current at NRST                                   | I <sub>NRST</sub>   | -    | -     | 10                    | mA   | -                                                    | P_5.1.7  |

| Temperature                                              | •                   | •    | •     |                       |      |                                                      | •        |

| Junction temperature                                     | T <sub>j</sub>      | -40  | -     | 150                   | °C   | -                                                    | P_5.1.8  |

| Storage temperature                                      | T <sub>s</sub>      | -55  | -     | 150                   | °C   | -                                                    | P_5.1.9  |

| ESD Susceptibility                                       |                     |      |       |                       |      |                                                      |          |

| Electrostatic discharge voltage at $V_S$ and BUS vs. GND | $V_{ESD}$           | -8   | -     | 8                     | kV   | Human Body Model<br>(100pF via 1.5 kΩ) <sup>2)</sup> | P_5.1.10 |

| Electrostatic discharge voltage all other pins           | $V_{ESD}$           | -2   | -     | 2                     | kV   | Human Body Model<br>(100pF via 1.5 kΩ) <sup>2)</sup> | P_5.1.11 |

| Electrostatic discharge voltage corner pins              | $V_{ESD}$           | -750 | -     | 750                   | V    | Charged Device<br>Model <sup>3)</sup>                | P_5.1.12 |

| Electrostatic discharge voltage at all other pins        | $V_{ESD}$           | -500 | -     | 500                   | V    | Charged Device<br>Model <sup>3)</sup>                | P_5.1.13 |

- 1) Not subject to production test, specified by design

- 2) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS-001 (1.5 k $\Omega$ , 100pF)

- 3) ESD susceptibility, Charged Device Model "CDM" EIA / JESD 22-C101 or ESDA STM5.3.1

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

### LIN Transceiver with integrated Voltage Regulator

#### **General Product Characteristics**

## 5.2 Functional Range

### Table 4 Operating Range

| Parameter                                   | Symbol                 | Values |      |      | Unit | Note or                               | Number   |

|---------------------------------------------|------------------------|--------|------|------|------|---------------------------------------|----------|

|                                             |                        | Min.   | Тур. | Max. |      | <b>Test Condition</b>                 |          |

| Supply Voltage                              |                        |        |      | 1    |      |                                       |          |

| Supply Voltage range for Normal Operation   | $V_{S(nor)}$           | 5.5    | -    | 28   | V    | LIN Spec 2.2A Param.<br>10            | P_5.2.12 |

| Extended Supply Voltage Range for Operation | $V_{S(ext)}$           | 3.0    | -    | 40   | V    | Parameter deviations possible         | P_5.2.22 |

| Stability Requirement on VCC                |                        | Ш      | II.  | U.   |      |                                       |          |

| Output capacitor range                      | C <sub>VCC</sub>       | 1.0    | -    | -    | μF   | 1), 3)                                | P_5.2.3  |

| Output capacitor ESR                        | ESR(C <sub>VCC</sub> ) | _      | _    | 5.0  | Ω    | 2), 3)                                | P_5.2.4  |

| Thermal parameter                           | 1                      | Ш      |      | 11.  |      | 1                                     |          |

| Junction temperature                        | $T_{\rm j}$            | -40    | -    | 150  | °C   | 3)                                    | P_5.2.5  |

|                                             |                        | •      |      | -    |      | · · · · · · · · · · · · · · · · · · · |          |

<sup>1)</sup> The minimum output capacitance requirement is applicable for a worst case capacitance tolerance of 30%.

Note:

Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

<sup>2)</sup> Relevant ESR value at f = 10 kHz.

<sup>3)</sup> Not subject to production test, specified by design.

### LIN Transceiver with integrated Voltage Regulator

#### **General Product Characteristics**

#### 5.3 Thermal Characteristics

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, please visit www.jedec.org.

Table 5 Thermal Resistance<sup>1)</sup>

| Parameter                       | Symbol     |        | Value | 5    | Unit | Note or<br>Test Condition            | Number  |

|---------------------------------|------------|--------|-------|------|------|--------------------------------------|---------|

|                                 |            | Min.   | Тур.  | Max. |      |                                      |         |

| Thermal Resistance, PG-DSO-8 Pa | ackage Ver | sion   | -     |      |      |                                      |         |

| Junction ambient                | $R_{thJA}$ | -      | 130   | _    | K/W  | 2)                                   | P_5.3.1 |

| Thermal Resistance, PG-TSON-8 I | Package Ve | ersion | -     |      |      |                                      |         |

| Junction ambient                | $R_{thJA}$ | -      | 60    | -    | K/W  | 2)                                   | P_5.3.2 |

| Junction ambient                |            | _      | 190   | _    | K/W  | Footprint only <sup>3)</sup>         | P_5.3.5 |

| Junction ambient                |            | -      | 70    | -    | K/W  | 300mm2 heatsink on PCB <sup>3)</sup> | P_5.3.6 |

| Thermal Shutdown Junction Ten   | perature   |        |       |      |      |                                      |         |

| Thermal shutdown temperature    | $T_{JSD}$  | 160    | 180   | 200  | °C   | $T_{\rm JSD}$ increasing             | P_5.3.3 |

| Thermal shutdown hysteresis     | $\Delta T$ | -      | 10    | _    | K    | $T_{\rm JSD}$ decreasing             | P_5.3.4 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Specified  $R_{thJA}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70  $\mu$ m Cu, 2 x 35  $\mu$ m Cu). Where applicable a thermal via array under the exposed pad contacted to the first inner copper layer.

<sup>3)</sup> Specified RthJA value is according to Jedec JESD51-3 at natural convection on FR4 1s0p board; The product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 1 inner copper layer (1 x 70  $\mu$ m Cu).

**Electrical Characteristics**

#### 6 **Electrical Characteristics**

#### 6.1 **Functional Device Characteristics**

#### Table 6 **Electrical Characteristics**

$5.5 \text{ V} < \text{V}_{\text{S}} < 28 \text{ V}; \text{ R}_{\text{LIN}} = 500 \,\Omega; -40 \,^{\circ}\text{C} < T_{j} < 150 \,^{\circ}\text{C};$  all voltages with respect to ground; positive current flowing into pin<sup>1)</sup>; unless otherwise specified.

| Parameter                                                                       | Symbol                 | Values |      |      | Unit | Note or Test Condition                                                                       | Number   |  |

|---------------------------------------------------------------------------------|------------------------|--------|------|------|------|----------------------------------------------------------------------------------------------|----------|--|

|                                                                                 |                        | Min.   | Тур. | Max. |      |                                                                                              |          |  |

| Current Consumption                                                             | •                      | •      |      |      |      |                                                                                              |          |  |

| Current consumption at $V_{\rm S}$ , transmitter in Recessive state             | I <sub>S,rec</sub>     | 0.1    | 0.3  | 0.7  | mA   | $I_{CC} = 50 \mu A$ ; Without $R_{LIN}$ ;<br>TxD = "high"; $V_{BUS} = V_{S}$                 | P_6.1.1  |  |

| Current consumption at V <sub>s</sub> ,<br>transmitter in Dominate state        | I <sub>S,dom</sub>     | 0.1    | 1.0  | 3.0  | mA   | $I_{CC} = 50 \mu A$ ; Without R <sub>LIN</sub> ;<br>TxD = "low"; V <sub>BUS</sub> = 0 V      | P_6.1.2  |  |

| Current consumption at V <sub>S</sub> ,<br>Dominate State                       | I <sub>S,dom_max</sub> | 70     | 71   | 73   | mA   | $I_{CC} = 70 \text{ mA}$ ; Without R <sub>LIN</sub> ;<br>TxD = "low"; V <sub>BUS</sub> = 0 V | P_6.1.3  |  |

| Current consumption at $V_S$ in Standby Mode $I_{S,standby} = I_S - I_{CC}$     | I <sub>S,standby</sub> | -      | 20   | 40   | μΑ   | Standby Mode;<br>$I_{CC} = 50 \mu A;$<br>$V_S = V_{BUS} = 13.5 V;$                           | P_6.1.4  |  |

| Current consumption at $V_{\rm S}$ in Sleep Mode                                | I <sub>S,Sleep</sub>   | -      | 7    | 16   | μΑ   | Sleep Mode; $V_S = 13.5 \text{ V}$ ; $V_{BUS} = V_S$ ; $V_{CC} = 0 \text{V}$                 | P_6.1.5  |  |

| Current consumption at V <sub>S</sub> in Sleep Mode. Bus shorted to GND         | I <sub>S,SC_GND</sub>  | 250    | _    | 800  | μΑ   | Sleep Mode;<br>$V_S = 13.5 \text{ V}; V_{BUS} = 0 \text{ V};$<br>$V_{CC} = 0 \text{ V}$      | P_6.1.6  |  |

| Power-up / Power-down                                                           | l                      |        | -1   |      | 1    |                                                                                              |          |  |

| Power-on reset level on V <sub>S</sub>                                          | $V_{S,PON}$            | -      | -    | 3.0  | ٧    | -                                                                                            | P_6.1.7  |  |

| Undervoltage threshold, V <sub>S</sub> on                                       | $V_{\rm S,UV,ON}$      | 4.7    | 5.15 | 5.5  | ٧    | Rising edge                                                                                  | P_6.1.8  |  |

| Undervoltage threshold, V <sub>S</sub> off                                      |                        | 4.4    | 4.85 | 5.2  | ٧    | Falling edge                                                                                 | P_6.1.9  |  |

| Undervoltage hysteresis on $V_S$<br>$V_{S,UV,hys} = V_{S,UV,ON} - V_{S,UV,OFF}$ | V <sub>S,UV,hys</sub>  | 200    | 300  | -    | mV   | 2)                                                                                           | P_6.1.10 |  |

| Undervoltage blanking time                                                      | t <sub>BLANK,UV</sub>  | -      | 10   | -    | μs   | 2)                                                                                           | P_6.1.11 |  |

| Enable Input: EN                                                                |                        |        |      |      |      |                                                                                              |          |  |

| HIGH level input voltage                                                        | $V_{\rm EN,ON}$        | 2      | _    | -    | V    | -                                                                                            | P_6.1.12 |  |

| LOW level input voltage                                                         | $V_{\rm EN,OFF}$       | _      | _    | 0.8  | ٧    | -                                                                                            | P_6.1.13 |  |

| Input hysteresis                                                                | V <sub>EN,hys</sub>    | 50     | 200  | -    | mV   | -                                                                                            | P_6.1.14 |  |

| Pull-down resistance                                                            | R <sub>EN</sub>        | 15     | 30   | 60   | kΩ   | -                                                                                            | P_6.1.15 |  |

| Delay time for mode change,<br>EN → "low"                                       | $t_{MODE,LOW}$         | 10     | -    | 50   | μs   | -                                                                                            | P_6.1.16 |  |

| Delay time for mode change,<br>EN → "high"                                      | t <sub>MODE,HIGH</sub> | -      | -    | 5    | μs   | 2)                                                                                           | P_6.1.17 |  |

| Initialization Watchdog time                                                    | $t_{Init\_WD}$         | 200    | -    | 1000 | ms   | -                                                                                            | P_6.1.18 |  |

### LIN Transceiver with integrated Voltage Regulator

#### **Electrical Characteristics**

#### Electrical Characteristics (cont'd) Table 6

$5.5 \text{ V} < \text{V}_{\text{S}} < 28 \text{ V}; \text{ R}_{\text{LIN}} = 500 \,\Omega; -40 \,^{\circ}\!\text{C} < \textit{T}_{j} < 150 \,^{\circ}\!\text{C};$  all voltages with respect to ground; positive current flowing into pin<sup>1)</sup>; unless otherwise specified.

| Parameter                                            | Symbol                 |         | Value  | 5       | Unit   | Note or Test Condition                                                                 | Number   |

|------------------------------------------------------|------------------------|---------|--------|---------|--------|----------------------------------------------------------------------------------------|----------|

|                                                      |                        | Min.    | Тур.   | Max.    |        |                                                                                        |          |

| Input capacitance                                    | Ci <sub>EN</sub>       | _       | 5      | _       | pF     | 2)                                                                                     | P_6.1.83 |

| Reset Output: NRST                                   |                        |         |        |         |        | ,                                                                                      |          |

| HIGH level leakage current                           | I <sub>NRST,H</sub>    | _       | -      | 5       | μΑ     | 2)                                                                                     | P_6.1.19 |

| LOW level output voltage                             | $V_{NRST}$             | _       | -      | 0.4     | V      | $I_{NRST} = 1.5 \text{ mA}; V_{CC} > 1 \text{ V};$                                     | P_6.1.20 |

| Reset time                                           | $t_{RST}$              | 4       | 10     | 16      | ms     | -                                                                                      | P_6.1.21 |

| Internal pull-up resistance                          | R <sub>NRST</sub>      | 5       | 10     | 20      | kΩ     | -                                                                                      | P_6.1.22 |

| Voltage Regulator Output, 5 V                        | versions (TL           | .E8457A | SJ and | TLE84   | 57ALE) | : VCC                                                                                  |          |

| Output voltage                                       | V <sub>cc</sub>        | 4.9     | 5.0    | 5.1     | V      | 0.05 mA < I <sub>CC</sub> < 70 mA;<br>5.8 V < VS < 28 V                                | P_6.1.23 |

| Output voltage drop $V_{DR} = V_S - V_{CC}^{3)}$     | $V_{DR}$               | -       | 250    | 650     | mV     | I <sub>CC</sub> < 70 mA                                                                | P_6.1.24 |

| Output voltage drop, 50mA<br>$V_{DR} = V_S - V_{CC}$ | $V_{\mathrm{DR,50}}$   | -       | 180    | 480     | mV     | / <sub>CC</sub> < 50 mA                                                                | P_6.1.25 |

| Output voltage drop, 20mA<br>$V_{DR} = V_S - V_{CC}$ | V <sub>DR,20</sub>     | -       | 80     | 200     | mV     | I <sub>CC</sub> < 20 mA                                                                | P_6.1.26 |

| Output current limitation                            | I <sub>CC,lim</sub>    | -150    | -      | -70     | mA     | 0 V < V <sub>CC</sub> < 4.8 V                                                          | P_6.1.27 |

| Load regulation                                      | $\Delta V_{\rm CC,lo}$ | -       | 25     | 50      | mV     | 0.05 mA < I <sub>CC</sub> < 70 mA;<br>VS = 13.5 V                                      | P_6.1.28 |

| Line regulation                                      | $\Delta V_{\rm CC,li}$ | -       | 25     | 50      | mV     | I <sub>CC</sub> = 1 mA;<br>5.8 V < V <sub>S</sub> < 28 V                               | P_6.1.29 |

| Power supply ripple rejection                        | PSRR                   | 50      | 60     | -       | dB     | <sup>2)</sup> ; $I_{CC}$ = 50 mA; f = 100 Hz;<br>$V_r$ = 0.5 $V_{pp}$ ; $V_S$ = 13.5 V | P_6.1.30 |

| Undervoltage reset threshold                         | $V_{\rm CC,UV}$        | 4.27    | 4.4    | 4.5     | V      | $V_{\rm CC}$ decreasing                                                                | P_6.1.31 |

| Undervoltage reset hysteresis                        | $V_{\rm CC,UV,hy}$     | 50      | 100    | -       | mV     | -                                                                                      | P_6.1.32 |

| Undervoltage detection time                          | $t_{ m det,RST}$       | 1       | -      | 20      | μs     | $^{2)}$ ; $V_{CC} = 3.5 \text{ V}$<br>$C_{NRST} = 20 \text{ pF}$                       | P_6.1.33 |

| Voltage Regulator Output, 3.3                        | V versions (           | TLE8457 | BSJ ar | nd TLE8 | 3457BL | .E): VCC                                                                               |          |

| Output voltage                                       | V <sub>cc</sub>        | 3.234   | 3.300  | 3.366   | V      | 0.05 mA < I <sub>CC</sub> < 70 mA;<br>4.066 V < VS < 28 V                              | P_6.1.34 |

| Output voltage drop $V_{DR} = V_S - V_{CC}$          | $V_{DR}$               | -       | 380    | 770     | mV     | I <sub>CC</sub> < 70 mA                                                                | P_6.1.35 |

| Output voltage drop, 50mA<br>$V_{DR} = V_S - V_{CC}$ | V <sub>DR,50</sub>     | -       | 280    | 550     | mV     | I <sub>CC</sub> < 50 mA                                                                | P_6.1.36 |

| Output voltage drop, 20mA<br>$V_{DR} = V_S - V_{CC}$ | V <sub>DR,20</sub>     | -       | 110    | 220     | mV     | I <sub>CC</sub> < 20 mA                                                                | P_6.1.37 |

| Output current limitation                            | I <sub>CC,lim</sub>    | -150    | -      | -70     | mA     | 0 V < V <sub>CC</sub> < 3.1 V                                                          | P_6.1.38 |

### LIN Transceiver with integrated Voltage Regulator

#### **Electrical Characteristics**

#### Electrical Characteristics (cont'd) Table 6

$5.5 \text{ V} < \text{V}_{\text{S}} < 28 \text{ V}; \text{ R}_{\text{LIN}} = 500 \Omega; -40^{\circ} \text{C} < T_{\text{j}} < 150^{\circ} \text{C};$

all voltages with respect to ground; positive current flowing into pin<sup>1)</sup>; unless otherwise specified.

| Parameter                                              | Symbol                 |                           | Value                    | S                         | Unit | Note or Test Condition                                                                                        | Number   |

|--------------------------------------------------------|------------------------|---------------------------|--------------------------|---------------------------|------|---------------------------------------------------------------------------------------------------------------|----------|

|                                                        |                        | Min.                      | Тур.                     | Max.                      |      |                                                                                                               |          |

| Load regulation                                        | $\Delta V_{\rm CC,lo}$ | -                         | 25                       | 50                        | mV   | $0.05 \text{ mA} < I_{CC} < 70 \text{ mA};$<br>$V_{S} = 13.5 \text{ V}$                                       | P_6.1.39 |

| Line regulation                                        | $\Delta V_{\rm CC,li}$ | -                         | 25                       | 50                        | mV   | I <sub>CC</sub> = 1 mA;<br>4.066 V < V <sub>S</sub> < 28 V                                                    | P_6.1.40 |

| Power supply ripple rejection                          | PSRR                   | 50                        | 60                       | _                         | dB   | <sup>2)</sup> ; $I_{CC} = 50 \text{ mA}$ ; $f = 100 \text{ Hz}$ ; $V_r = 0.5 V_{pp}$ ; $V_S = 13.5 \text{ V}$ | P_6.1.41 |

| Undervoltage reset threshold                           | $V_{\rm CC,UV}$        | 2.82                      | 2.90                     | 2.96                      | V    | $V_{\rm CC}$ decreasing                                                                                       | P_6.1.42 |

| Undervoltage reset hysteresis                          | $V_{\rm CC,UV,hy}$     | 33                        | 66                       | _                         | mV   | -                                                                                                             | P_6.1.43 |

| Undervoltage detection time                            | $t_{ m det,RST}$       | 1                         | -                        | 20                        | μs   | $V_{CC} = 2.31 \text{ V}$<br>$C_{NRST} = 20 \text{ pF}$                                                       | P_6.1.44 |

| Receiver Output: RxD                                   |                        |                           |                          |                           |      |                                                                                                               |          |

| HIGH level output voltage                              | $V_{RxD,H}$            | 0.8<br>× V <sub>CC</sub>  | -                        | _                         | V    | $I_{\text{RXD}} = -2 \text{ mA}; V_{\text{BUS}} = V_{\text{S}}$                                               | P_6.1.45 |

| LOW level output voltage                               | $V_{RxD,L}$            | -                         | -                        | 0.2<br>× V <sub>CC</sub>  | V    | $I_{RXD} = 2 \text{ mA}; V_{BUS} = 0 \text{ V}$                                                               | P_6.1.46 |

| Transmission Input: TxD                                |                        |                           |                          |                           |      |                                                                                                               |          |

| HIGH level input voltage range                         | $V_{TxD,H}$            | 0.7<br>× V <sub>CC</sub>  | -                        | -                         | V    | Recessive state                                                                                               | P_6.1.47 |

| LOW level input voltage range                          | $V_{TxD,L}$            | -                         | -                        | 0.3<br>× V <sub>cc</sub>  | V    | Dominant state                                                                                                | P_6.1.48 |

| Input hysteresis                                       | $V_{TxD,hys}$          | 200                       | _                        | -                         | mV   | -                                                                                                             | P_6.1.49 |

| Pull-up resistance                                     | $R_{TxD}$              | 15                        | 30                       | 60                        | kΩ   | -                                                                                                             | P_6.1.50 |

| TxD time-out                                           | $t_{TxD}$              | 8                         | 18                       | 28                        | ms   | -                                                                                                             | P_6.1.51 |

| TxD recessive release time                             | $t_{ m to,rec}$        | -                         | -                        | 10                        | μs   | 2)                                                                                                            | P_6.1.52 |

| Input capacitance                                      | Ci                     | -                         | 5                        | -                         | pF   | 2)                                                                                                            | P_6.1.93 |

| Bus Receiver: BUS                                      |                        |                           |                          |                           |      |                                                                                                               |          |

| Receiver threshold voltage, recessive to dominant edge | $V_{\mathrm{th\_dom}}$ | 0.4<br>× V <sub>S</sub>   | 0.44<br>× V <sub>S</sub> | -                         | V    | V <sub>S</sub> < 18V;                                                                                         | P_6.1.53 |

| Receiver dominant state                                | V <sub>BUSdom</sub>    | -27                       | -                        | 0.4<br>× V <sub>S</sub>   | V    | LIN Spec 2.2A (Par. 17) <sup>4)</sup>                                                                         | P_6.1.54 |

| Receiver threshold voltage, dominant to recessive edge | $V_{\mathrm{th\_rec}}$ | -                         | 0.56<br>× V <sub>S</sub> | 0.6<br>× V <sub>s</sub>   | V    | V <sub>S</sub> < 18V;                                                                                         | P_6.1.55 |

| Receiver recessive state                               | V <sub>BUSrec</sub>    | 0.6<br>× V <sub>s</sub>   | -                        | 40                        | V    | LIN Spec 2.2A (Par. 18) <sup>5)</sup>                                                                         | P_6.1.56 |

| Receiver center voltage                                | V <sub>BUS_CNT</sub>   | 0.475<br>× V <sub>S</sub> | 0.5<br>× V <sub>S</sub>  | 0.525<br>× V <sub>s</sub> | V    | LIN Spec 2.2A (Par. 19) <sup>6)</sup><br>V <sub>S</sub> < 18V;                                                | P_6.1.57 |

### LIN Transceiver with integrated Voltage Regulator

#### **Electrical Characteristics**

#### Electrical Characteristics (cont'd) Table 6

$5.5 \text{ V} < \text{V}_{\text{S}} < 28 \text{ V}; \text{ R}_{\text{LIN}} = 500 \Omega; -40^{\circ} \text{C} < T_{\text{j}} < 150^{\circ} \text{C};$

all voltages with respect to ground; positive current flowing into pin<sup>1)</sup>; unless otherwise specified.

| Parameter                                                                          | Symbol                   | Values                   |                          |                           | Unit     | Note or Test Condition                                                                                                         | Number   |

|------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|---------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                    |                          | Min.                     | Тур.                     | Max.                      |          |                                                                                                                                |          |

| Receiver hysteresis                                                                | V <sub>HYS</sub>         | 0.07<br>× V <sub>S</sub> | 0.12<br>× V <sub>S</sub> | 0.175<br>× V <sub>S</sub> | V        | LIN Spec 2.2A (Par. 20) <sup>7)</sup><br>V <sub>S</sub> < 18V;                                                                 | P_6.1.58 |

| Wake-Up threshold voltage                                                          | V <sub>BUS,wk</sub>      | 0.4<br>× V <sub>S</sub>  | 0.5<br>× V <sub>S</sub>  | 0.6<br>× V <sub>s</sub>   | V        | -                                                                                                                              | P_6.1.59 |

| Bus Transmitter: BUS                                                               |                          |                          |                          | 1                         | 1        |                                                                                                                                | - 1      |

| Bus recessive output voltage                                                       | $V_{BUS,ro}$             | 0.8<br>× V <sub>S</sub>  | -                        | V <sub>s</sub>            | V        | TxD = "high"; Open load                                                                                                        | P_6.1.60 |

| Bus short circuit current                                                          | I <sub>BUS_LIM</sub>     | 40                       | 85                       | 125                       | mA       | V <sub>BUS</sub> = 18 V;<br>LIN Spec 2.2A (Par. 12);                                                                           | P_6.1.61 |

| Leakage current                                                                    | I <sub>BUS_NO_GND</sub>  | -1                       | -0.5                     | _                         | mA       | V <sub>S</sub> = 0 V; V <sub>BUS</sub> = -12 V;<br>LIN Spec 2.2A (Par. 15)                                                     | P_6.1.62 |

| Leakage current                                                                    | I <sub>BUS_NO_BAT</sub>  | _                        | 1                        | 5                         | μΑ       | V <sub>S</sub> = 0 V; V <sub>BUS</sub> = 18 V;<br>LIN Spec 2.2A (Par. 16)                                                      | P_6.1.63 |

| Leakage current                                                                    | I <sub>BUS_PAS_dom</sub> | -1                       | -0.5                     | _                         | mA       | $V_{\rm S}$ = 18 V; $V_{\rm BUS}$ = 0 V;<br>LIN Spec 2.2A (Par. 13)                                                            | P_6.1.64 |

| Leakage current                                                                    | I <sub>BUS_PAS_rec</sub> | -                        | 1                        | 5                         | μΑ       | V <sub>S</sub> = 8 V; V <sub>BUS</sub> = 18 V;<br>Driver stage "off";<br>TxD = "high";<br>LIN Spec 2.2A (Par. 14)              | P_6.1.65 |

| Forward voltage serial diode                                                       | V <sub>SerDiode</sub>    | 0.4                      | -                        | 1.0                       | V        | / <sub>SerDiode</sub> = - 75 μA<br>LIN Spec 2.2A (Par.21)                                                                      | P_6.1.66 |

| Bus pull-up resistance                                                             | R <sub>slave</sub>       | 20                       | 40                       | 60                        | kΩ       | LIN Spec 2.2A (Par. 26)                                                                                                        | P_6.1.67 |

| Bus dominant output voltage maximum load                                           | $V_{\mathrm{BUS,do}}$    | _                        | _                        | 1.4                       | V        | $V_{\text{TXD}} = 0 \text{ V}; R_{\text{LIN}} = 500 \Omega;$<br>$V_{\text{S}} = 5.5 \text{ V};$                                | P_6.1.68 |

| Bus dominant output voltage maximum load                                           | $V_{BUS,do}$             | _                        | _                        | 2.0                       | V        | $V_{\text{TXD}} = 0 \text{ V}; R_{\text{LIN}} = 500 \Omega;$<br>$V_{\text{S}} = 18 \text{ V};$                                 | P_6.1.98 |

| Input capacitance                                                                  | Ci <sub>BUS</sub>        |                          | -                        | 30                        | pF       | 2)                                                                                                                             | P_6.1.95 |

| Dynamic Transceiver Characte                                                       |                          |                          | +                        | +                         |          |                                                                                                                                | +        |

| Dominant time for Bus Wake-<br>up                                                  | t <sub>WK,bus</sub>      | 30                       | -                        | 150                       | μs       | -                                                                                                                              | P_6.1.69 |

| Propagation delay:<br>LIN bus Dominant to RxD Low<br>LIN bus Recessive to RxD High | t <sub>rx_pdft</sub>     | 1                        | 3.5<br>3.5               | 6                         | μs<br>μs | LIN Spec 2.2A (Par. 31)<br>C <sub>RxD</sub> = 20 pF                                                                            | P_6.1.70 |

| Receiver delay symmetry                                                            | t <sub>rx_sym</sub>      | -2                       | -                        | 2                         | μs       | LIN Spec 2.2A (Par. 32)<br>$t_{\text{rx\_sym}} = t_{\text{rx\_pdf}} - t_{\text{rx\_pdr}};$<br>$C_{\text{RxD}} = 20 \text{ pF}$ | P_6.1.71 |