Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# TLE8888-1QK

Engine Management System IC for 4 Cylinder Cars

Engine Management System IC TLE8888-1QK TLE8888QK TLE8888-2QK

# **Data Sheet**

Rev. 1.1, 2014-08-20

**Automotive Power**

### **Table of Contents**

# **Table of Contents**

| <b>1</b><br>1.1               | Overview     Abbreviations                                                                                  |          |

|-------------------------------|-------------------------------------------------------------------------------------------------------------|----------|

| 2                             | Block Diagram                                                                                               | . 8      |

| <b>3</b><br>3.1<br>3.2        | Pin Configuration         Pin Assignment         Pin Definitions and Functions                              | . 9      |

| 4                             | General Product Characteristics                                                                             | 13       |

| <b>5</b><br>5.1<br>5.2<br>5.3 | Operation Behavior Operation States Reset and Operation Modes Electrical Characteristics Operation Behavior | 18<br>22 |

| 6                             | Monitoring Watchdog Module (Signature Watchdog)                                                             |          |

| 6.1<br>6.2<br>6.2.1           | Window Watchdog  Functional Watchdog  Question and Response Definition                                      | 35       |

| 6.3                           | Total Error Counter Module                                                                                  |          |

| 6.4                           | Watchdog Reset Counter                                                                                      |          |

| 6.5                           | Power Down Counter                                                                                          |          |

| 6.6<br>6.7                    | Secure Shut Off Timer                                                                                       |          |

| 6.8                           | Synchronisation of Window Watchdog Sequence and Heartbeat                                                   |          |

| 6.9                           | Electrical Characteristics Monitoring Watchdog Module                                                       |          |

| 7                             | Wake Up Detection and Main Relay Driver                                                                     |          |

| 7.1                           | Wake Up Detection by Pin $KEY$ and Key Off Delay                                                            |          |

| 7.2<br>7.3                    | Wake Up Detection by Pin $WK$                                                                               |          |

| 7.4                           | Engine Off Timer                                                                                            |          |

| 7.5                           | Electrical Characteristics Key Detection, Wake Up Detection and Main Relay Driver                           |          |

| В                             | Power Supply                                                                                                |          |

| 8.1                           | Pre-Regulator                                                                                               |          |

| 8.2<br>8.3                    | 5V Main Supply                                                                                              |          |

| 3.3<br>8.4                    | IO Supply                                                                                                   |          |

| 8.5                           | Standby Supply                                                                                              |          |

| 8.6                           | Charge Pump                                                                                                 |          |

| 8.7                           | Voltage Monitoring                                                                                          |          |

| 8.8                           | Electrical Characteristics Power Supply                                                                     |          |

| <b>9</b><br>9.1               | Power Stages                                                                                                |          |

| 9. i<br>9.2                   | Power Stages Enable                                                                                         |          |

| 9.3                           | Power Stages Configuration                                                                                  |          |

| 9.4                           | Special Function "Delayed Switch Off" for $OUT17$ and $OUT21$                                               |          |

| 9.5                           | Electrical Characteristics Direct Drive Inputs                                                              |          |

| 9.6<br>9.6.1                  | Low Side Switches $OUT1$ to $OUT7$ and $OUT14$ to $OUT20$                                                   |          |

| 9.6.2                         | Diagnosis of $OUT1$ to $OUT7$ and $OUT14$ to $OUT20$                                                        |          |

|                               |                                                                                                             |          |

### **Table of Contents**

| 9.6.3<br>9.7      | Electrical Characteristics Low Side Switches $OUT1$ to $OUT7$ and $OUT14$ to $OUT20$ |     |

|-------------------|--------------------------------------------------------------------------------------|-----|

| 9.7.1             | Protection of Half Bridges OUT21 to OUT24                                            |     |

| 9.7.2             | Diagnosis of Half Bridges OUT21 to OUT24                                             |     |

| 9.7.3<br>9.8      | Electrical Characteristics Half Bridges                                              |     |

| 9.8.1             | Protection of OUT8 to OUT13 and DI-B8 to DI-B13                                      |     |

| 9.8.2             | Diagnosis of $OUT8$ to $OUT13$                                                       | 80  |

| 9.8.3             | Electrical Characteristics Push Pull Stages OUT8 to OUT13                            |     |

| 9.9<br>9.9.1      | Push Pull Stages $IGN1$ to $IGN4$                                                    |     |

| 9.9.1             | Diagnosis of $IGN1$ to $IGN4$                                                        |     |

| 9.9.3             | Electrical Characteristics Push Pull Stages $IGNI$ to $IGN4$                         |     |

| 10                | VR and Hall Sensor Interface                                                         | 85  |

| 10.1              | Signal Detection                                                                     |     |

| 10.2<br>10.3      | Detection Modes                                                                      |     |

| 10.3              | Electrical Characteristics VR Sensor Interface                                       |     |

| 11                | Local Interconnect Network (LIN)                                                     |     |

| 11.1              | Operation Modes                                                                      |     |

| 11.2              | Failure Modes in LIN/K-Line Operation                                                |     |

| 11.2.1            | Performance in Non Operation Supply Voltage Range                                    |     |

| 11.2.2<br>11.2.3  | Loss of Supply Voltage and GND Connection                                            |     |

| 11.2.4            | TX Time Out                                                                          |     |

| 11.2.5            | Over Temperature Protection                                                          |     |

| 11.3              | Electrical Characteristics LIN                                                       |     |

| 12                | High Speed Controller Area Network (CAN) Transceiver                                 |     |

| 12.1<br>12.2      | Functional Description                                                               |     |

| 12.2.1            | Normal Operation Mode                                                                |     |

| 12.2.2            | Receive Only Mode                                                                    | 102 |

| 12.2.3            | Power Down Mode                                                                      |     |

| 12.2.4<br>12.3    | Remote Wake Up                                                                       |     |

| 12.3.1            | CAN Bus Failure Detection                                                            |     |

| 12.3.2            | Local Failure Detection                                                              |     |

| 12.4              | Electrical Characteristics CAN Transceiver                                           | 105 |

| 13                | Micro Second Channel MSC                                                             |     |

| 13.1<br>13.1.1    | Downstream Communication                                                             |     |

| 13.1.1            | Command Frame                                                                        |     |

| 13.1.3            | Data Frame                                                                           |     |

| 13.2              | Upstream Communication                                                               |     |

| 13.3<br>13.4      | Timing Characteristics                                                               |     |

|                   | Electrical Characteristics                                                           |     |

| <b>14</b><br>14.1 | Register and Commands                                                                |     |

| 14.1              | Command Register                                                                     |     |

# **TLE8888-1QK**

### **Table of Contents**

| 14.3<br>14.4<br>14.5<br>14.6 | Diagnosis Register Status Register Configuration Register Control Register | 149<br>156 |

|------------------------------|----------------------------------------------------------------------------|------------|

| 15                           | SPI                                                                        |            |

| 15.1                         | SPI Protocol                                                               |            |

| 15.2                         | SPI Frame Definition                                                       |            |

| 15.3                         | Electrical Characteristics SPI                                             |            |

| 16                           | EMC Requirements                                                           | 195        |

| 16.1                         | ISO Pulse Tests                                                            | 195        |

| 17                           | Application Information                                                    | 196        |

| 17.1                         | Supply Systems                                                             | 197        |

| 17.2                         | VR Sensor Interface                                                        | 198        |

| 18                           | Package Outlines                                                           | 200        |

| 19                           | Revision History                                                           | 201        |

### **TLE8888-1QK**

### **Engine Management System IC**

### 1 Overview

#### **Features**

- Voltage pre-regulator

- Integrated 5V regulator

- 2 integrated 5V trackers

- · Standby regulator

- Separate internal supply

- · Voltage monitoring

- High speed CAN interface with wake up by bus

- LIN interface with high speed mode for K-Line operation

- · Variable reluctance sensor interface

- Micro Second Channel interface (MSC) with low voltage differential signal (LVDS) inputs pads for low EME

- · SPI and direct control inputs for high flexibility

- · Main relay driver

- · Ignition Key detection with key off delay output

- Wake up input

- Engine off timer

- 4 low side power stages especially to drive injectors ( $R_{on}$ =550m $\Omega$ ) with enable input

- 3 low side power stages ( $R_{on}$ =350m $\Omega$ )

- 6 push pull stages for driving on-board MOSFET with drain feedback

- 7 low side power stages especially to drive relays ( $R_{\rm on}$ =1.5 $\Omega$ ), one with delayed switch off functionality

- 4 half bridge stages for high flexibility, one with delayed switch off functionality

- 4 push pull stages for driving on- and off- board IGBT with back supply suppression and high voltage capability

- · Open-load, short-to-GND and short-to-BAT diagnostic

- Over temperature and short-to-BAT protection

- · Monitoring watchdog module

- Green Product (RoHS compliant)

- AEC Qualified

#### **Description**

The device is a U-Chip suitable for automotive engine management systems. It contains the basic functionality to supply the micro controller and the ECU, establish the communication on- and off- board and drive EMS typical actuators. Furthermore it controls the main relay driver.

| Туре        | Package  | Marking          |

|-------------|----------|------------------|

| TLE8888-1QK | LQFP-100 | TLE8888-1QK      |

| TLE8888QK   | LQFP-100 | TLE8888QK        |

| TLE8888-2QK | LQFP-100 | TLE8888-2QK      |

| D-4- Ol4    |          | D 1.1 0014 00 00 |

LQFP-100

Overview

### Device Variants TLE8888QK and TLE8888-2QK

The device variants TLE8888QK and TLE8888-2QK differ from the main version TLE8888-1QK in the watchdog functionality.

The TLE8888QK has a fixed set of parameter for the watchdog (see datasheet addendum "TLE8888QK - Addendum").

For the TLE8888-2QK the watchdog function is disabled (see datasheet addendum "TLE8888-2QK - Addendum"). Only the main version TLE8888-1QK is described in this datasheet.

For order conditions please contact the nearest Infineon Technologies office.

Overview

# 1.1 Abbreviations

### Table 1 Abbreviations

| Symbol | Explanation                        |

|--------|------------------------------------|

| MSC    | Micro second channel               |

| SPI    | Serial peripheral interface        |

| LVDS   | Low voltage differential signal    |

| EME    | Electromagnetic emission           |

| EMI    | Electromagnetic interference       |

| LIN    | Local interconnect network         |

| HS CAN | High speed controller area network |

**Block Diagram**

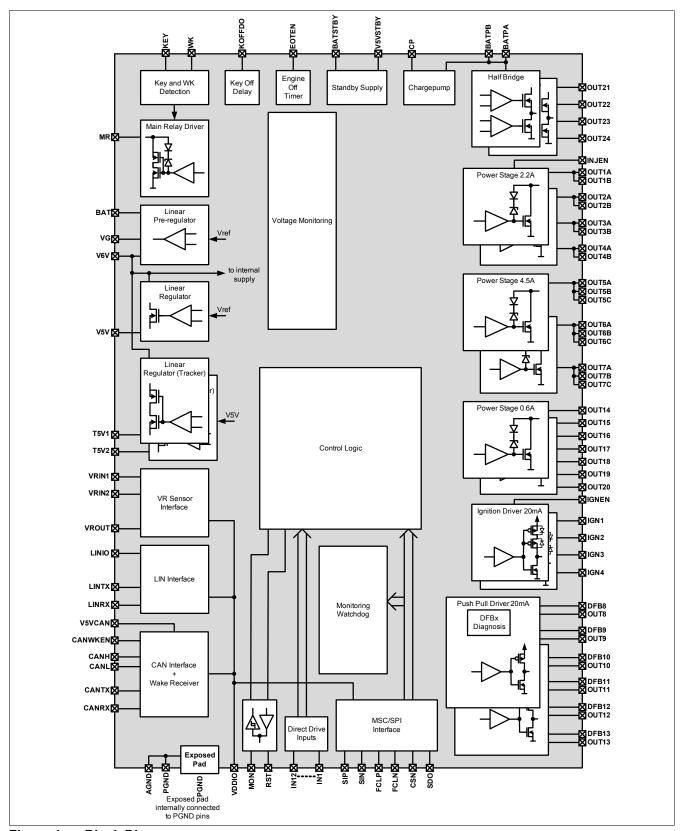

# 2 Block Diagram

Figure 1 Block Diagram

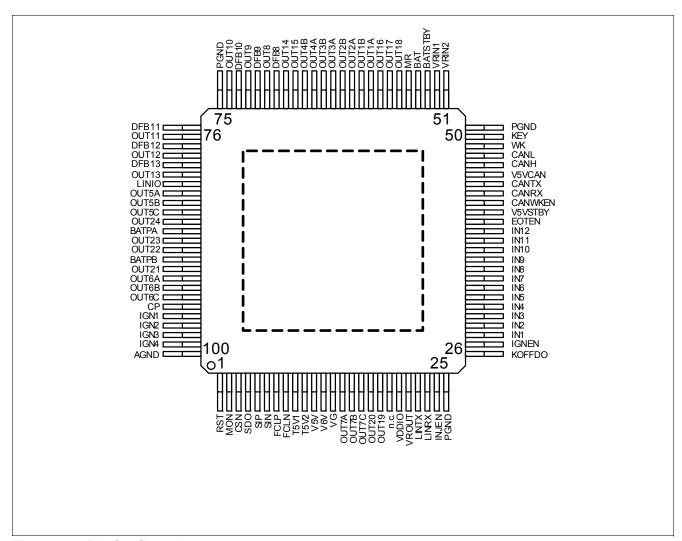

# 3 Pin Configuration

# 3.1 Pin Assignment

Figure 2 Pin Configuration

# 3.2 Pin Definitions and Functions

| Pin | Symbol | Function | Function                                                                                           |  |  |  |  |  |  |

|-----|--------|----------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1   | RST    | IN/OUT   | eset; Bidirectional pin for reset functions                                                        |  |  |  |  |  |  |

| 2   | MON    | IN/OUT   | nitor; Bidirectional pin for monitoring functions                                                  |  |  |  |  |  |  |

| 3   | CSN    | IN       | SC/SPI slave chip select; Single ended chip select for MSC and SPI                                 |  |  |  |  |  |  |

| 4   | SDO    | OUT      | SC/SPI serial data output; Output for MSC and SPI                                                  |  |  |  |  |  |  |

| 5   | SIP    | IN       | MSC/SPI Data input; positive data input of LVDS in MSC mode or single ended data input in SPI mode |  |  |  |  |  |  |

| Pin | Symbol | Function | Function                                                                                                                     |  |  |  |  |  |  |

|-----|--------|----------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 6   | SIN    | IN       | <b>MSC data input or select input</b> ; negative data input of LVDS in MSC mode or select input for SPI mode                 |  |  |  |  |  |  |

| 7   | FCLP   | IN       | MSC/SPI Clock input; positive clock input of LVDS in MSC mode or single ended clock input in SPI mode                        |  |  |  |  |  |  |

| 8   | FCLN   | IN       | Select input or MSC clock input; negative clock input of LVDS in MSC mode or select input for single ended mode (SPI or MSC) |  |  |  |  |  |  |

| 9   | T5V1   | OUT      | <b>5V tracker</b> ; Supply voltage for off- board sensors                                                                    |  |  |  |  |  |  |

| 10  | T5V2   | OUT      | <b>5V tracker</b> ; Supply voltage for off- board sensors                                                                    |  |  |  |  |  |  |

| 11  | V5V    | OUT      | <b>5V supply</b> ; Supply voltage for main functions of the ECU                                                              |  |  |  |  |  |  |

| 12  | V6V    | IN       | Source of external pre-regulator                                                                                             |  |  |  |  |  |  |

| 13  | VG     | OUT      | Gate of external pre-regulator                                                                                               |  |  |  |  |  |  |

| 14  | OUT7A  | OUT      | Low side power stage; Must be connected to $OUT7B$ and $OUT7C$ without any parasitic                                         |  |  |  |  |  |  |

| 15  | OUT7B  | OUT      | Low side power stage; Must be connected to $OUT7A$ and $OUT7C$ without any parasitic                                         |  |  |  |  |  |  |

| 16  | OUT7C  | OUT      | Low side power stage; Must be connected to $OUT7A$ and $OUT7B$ without any parasitic                                         |  |  |  |  |  |  |

| 17  | OUT20  | OUT      | Low side small signal stage;                                                                                                 |  |  |  |  |  |  |

| 18  | OUT19  | OUT      | Low side small signal stage;                                                                                                 |  |  |  |  |  |  |

| 19  | n.c.   |          | leave open or connect to GND                                                                                                 |  |  |  |  |  |  |

| 20  | VDDIO  | Supply   | Supply input for logic level inputs and outputs                                                                              |  |  |  |  |  |  |

| 21  | VROUT  | OUT      | Output of variable reluctance sensor interface; Digital output to micro controller                                           |  |  |  |  |  |  |

| 22  | LINTX  | IN       | Transmit digital input for LIN interface;                                                                                    |  |  |  |  |  |  |

| 23  | LINRX  | OUT      | Receive digital output for LIN interface;                                                                                    |  |  |  |  |  |  |

| 24  | INJEN  | IN       | Injector enable input;                                                                                                       |  |  |  |  |  |  |

| 25  | PGND   | GND      | Power ground; internally connected to cooling tab                                                                            |  |  |  |  |  |  |

| 26  | KOFFDO | OUT      | Key off delay output;                                                                                                        |  |  |  |  |  |  |

| 27  | IGNEN  | IN       | Ignition enable input;                                                                                                       |  |  |  |  |  |  |

| 28  | IN1    | IN       | Parallel input; Input pin for direct control of power stage OUT1,                                                            |  |  |  |  |  |  |

| 29  | IN2    | IN       | Parallel input; Input pin for direct control of power stage OUT2                                                             |  |  |  |  |  |  |

| 30  | IN3    | IN       | Parallel input; Input pin for direct control of power stage OUT3                                                             |  |  |  |  |  |  |

| 31  | IN4    | IN       | Parallel input; Input pin for direct control of power stage OUT4                                                             |  |  |  |  |  |  |

| 32  | IN5    | IN       | Parallel input; Input pin for direct control of push pull state IGN1                                                         |  |  |  |  |  |  |

| 33  | IN6    | IN       | Parallel input; Input pin for direct control of push pull state IGN2                                                         |  |  |  |  |  |  |

| 34  | IN7    | IN       | Parallel input; Input pin for direct control of push pull state IGN3                                                         |  |  |  |  |  |  |

| 35  | IN8    | IN       | Parallel input; Input pin for direct control of push pull state IGN4                                                         |  |  |  |  |  |  |

| 36  | IN9    | IN       | Parallel input; Input pin for direct control of power stages, could be multiplexed to various stages                         |  |  |  |  |  |  |

| 37  | IN10   | IN       | Parallel input; Input pin for direct control of power stages, could be multiplexed to various stages                         |  |  |  |  |  |  |

| 38  | IN11   | IN       | Parallel input; Input pin for direct control of power stages, could be multiplexed to various stages                         |  |  |  |  |  |  |

| Pin | Symbol      | Function | Function                                                                                             |

|-----|-------------|----------|------------------------------------------------------------------------------------------------------|

| 39  | IN12        | IN       | Parallel input; Input pin for direct control of power stages, could be multiplexed to various stages |

| 40  | EOTEN       | IN       | Engine off timer enable input;                                                                       |

| 41  | V5VSTBY     | OUT      | 5V standby supply; Supply voltage in sleep mode                                                      |

| 42  | CANWKE<br>N | IN       | Enable input for remote CAN wake up;                                                                 |

| 43  | CANRX       | OUT      | Receive digital output for CAN;                                                                      |

| 44  | CANTX       | IN       | Transmit digital input for CAN;                                                                      |

| 45  | V5VCAN      | Supply   | 5V supply input for CAN;                                                                             |

| 46  | CANH        | IN/OUT   | CAN bus high;                                                                                        |

| 47  | CANL        | IN/OUT   | CAN bus low;                                                                                         |

| 48  | WK          | IN       | Wake up input; Input signal and supply for MR                                                        |

| 49  | KEY         | IN       | Key input; Input signal and supply for MR                                                            |

| 50  | PGND        | GND      | Power ground; internally connected to cooling tab                                                    |

| 51  | VRIN2       | IN       | Differential input of variable reluctance sensor; Analog input from sensor                           |

| 52  | VRIN1       | IN       | Differential input of variable reluctance sensor; Analog input from sensor                           |

| 53  | BATSTBY     | Supply   | Battery input for standby supply; Battery supply voltage standby supply regulator                    |

| 54  | BAT         | Supply   | Battery; Supply voltage for main functions of the device.                                            |

| 55  | MR          | OUT      | Low side power stage for main relay;                                                                 |

| 56  | OUT18       | OUT      | Low side power stage;                                                                                |

| 57  | OUT17       | OUT      | Low side power stage;                                                                                |

| 58  | OUT16       | OUT      | Low side power stage;                                                                                |

| 59  | OUT1A       | OUT      | Low side power stage; Must be connected to $OUT1B$ without any parasitic                             |

| 60  | OUT1B       | OUT      | Low side power stage; Must be connected to $OUTIA$ without any parasitic                             |

| 61  | OUT2A       | OUT      | Low side power stage; Must be connected to $OUT2B$ without any parasitic                             |

| 62  | OUT2B       | OUT      | Low side power stage; Must be connected to $OUT2A$ without any parasitic                             |

| 63  | OUT3A       | OUT      | Low side power stage; Must be connected to $OUT3B$ without any parasitic                             |

| 64  | OUT3B       | OUT      | Low side power stage; Must be connected to $OUT3A$ without any parasitic                             |

| 65  | OUT4A       | OUT      | Low side power stage; Must be connected to $OUT4B$ without any parasitic                             |

| 66  | OUT4B       | OUT      | Low side power stage; Must be connected to $OUT4A$ without any parasitic                             |

| 67  | OUT15       | OUT      | Low side power stage;                                                                                |

| 68  | OUT14       | OUT      | Low side power stage;                                                                                |

| 69  | DFB8        | IN       | Drain Feedback; Related to OUT8                                                                      |

| 70  | OUT8        | OUT      | Push pull stage; To control on- board MOSFET                                                         |

| 71  | DFB9        | IN       | Drain Feedback; Related to OUT9                                                                      |

| 72  | OUT9        | OUT      | Push pull stage; To control on- board MOSFET                                                         |

| 73  | DFB10       | IN       | Drain Feedback; Related to OUT10                                                                     |

| 74  | OUT10       | OUT      | Push pull stage; To control on- board MOSFET                                                         |

| 75  | PGND        | GND      | Power ground; internally connected to cooling tab                                                    |

| 76  | DFB11       | IN       | Drain Feedback; Related to OUT11                                                                     |

| 77  | OUT11       | OUT      | Push pull stage; To control on- board MOSFET                                                         |

| Pin                        | Symbol | Function | Function                                                                                                                 |  |  |  |  |  |  |

|----------------------------|--------|----------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 78                         | DFB12  | IN       | Drain Feedback; Related to OUT12                                                                                         |  |  |  |  |  |  |

| 79                         | OUT12  | OUT      | Push pull stage; To control on- board MOSFET                                                                             |  |  |  |  |  |  |

| 80                         | DFB13  | IN       | ain Feedback; Related to OUT13                                                                                           |  |  |  |  |  |  |

| 81                         | OUT13  | OUT      | ush pull stage; To control on- board MOSFET                                                                              |  |  |  |  |  |  |

| 82                         | LINIO  | IN/OUT   | BUS for LIN interface;                                                                                                   |  |  |  |  |  |  |

| 83                         | OUT5A  | OUT      | ow side power stage; Must be connected to $OUT5B$ and $OUT5C$ without ny parasitic                                       |  |  |  |  |  |  |

| 84                         | OUT5B  | OUT      | <b>Low side power stage</b> ; Must be connected to $OUT5A$ and $OUT5C$ without any parasitic                             |  |  |  |  |  |  |

| 85                         | OUT5C  | OUT      | Low side power stage; Must be connected to $OUT5A$ and $OUT5B$ without any parasitic                                     |  |  |  |  |  |  |

| 86                         | OUT24  | OUT      | Half bridge stage;                                                                                                       |  |  |  |  |  |  |

| 87                         | BATPA  | Supply   | <b>Battery;</b> Supply voltage for half bridges and the charge pump; must be connected to $BATPB$ without any parasitic  |  |  |  |  |  |  |

| 88                         | OUT23  | OUT      | Half bridge stage;                                                                                                       |  |  |  |  |  |  |

| 89                         | OUT22  | OUT      | Half bridge stage;                                                                                                       |  |  |  |  |  |  |

| 90                         | BATPB  | Supply   | <b>Battery</b> ; Supply voltage for half bridges and the charge pump; must be connected to $BATPA$ without any parasitic |  |  |  |  |  |  |

| 91                         | OUT21  | OUT      | Half bridge stage;                                                                                                       |  |  |  |  |  |  |

| 92                         | OUT6A  | OUT      | Low side power stage; Must be connected to $OUT6B$ and $OUT6C$ without any parasitic                                     |  |  |  |  |  |  |

| 93                         | OUT6B  | OUT      | <b>Low side power stage</b> ; Must be connected to $OUT6A$ and $OUT6C$ without any parasitic                             |  |  |  |  |  |  |

| 94                         | OUT6C  | OUT      | Low side power stage; Must be connected to $OUT6A$ and $OUT6B$ without any parasitic                                     |  |  |  |  |  |  |

| 95                         | CP     | OUT      | Charge pump; add external capacitance to stabilise charge pump voltage                                                   |  |  |  |  |  |  |

| 96                         | IGN1   | OUT      | Push pull stage; To control on- or off- board IGBT                                                                       |  |  |  |  |  |  |

| 97                         | IGN2   | OUT      | Push pull stage; To control on- or off- board IGBT                                                                       |  |  |  |  |  |  |

| 98                         | IGN3   | OUT      | Push pull stage; To control on- or off- board IGBT                                                                       |  |  |  |  |  |  |

| 99                         | IGN4   | OUT      | Push pull stage; To control on- or off- board IGBT                                                                       |  |  |  |  |  |  |

| 100                        | AGND   | GND      | <b>Signal ground;</b> internally connected to $PG\!N\!D$ and cooling tab                                                 |  |  |  |  |  |  |

| Coolin g tab <sup>1)</sup> | PGND   | GND      | Power ground; internally connected PGND pins                                                                             |  |  |  |  |  |  |

<sup>1)</sup> Cooling tab is also called exposed pad

# 4 General Product Characteristics

General definition:

$V_{\rm S}$  is the short cut for all battery supplies of the TLE8888-1QK (BAT, BATPA, BATPB, BATSTBY) unless otherwise specified

$\mathit{GND}$  is the short cut for all grounds of the TLE8888-1QK ( $\mathit{AGND}$ ,  $\mathit{PGND}$ ) unless otherwise specified.

Table 2 Absolute Maximum Ratings<sup>1)</sup>

$T_i$ =-40 to 150°C, all voltages with respect to GND, positive current flowing into pin, (unless otherwise specified)

| Parameter                                                                             | Symbol                                                                                                                               |      | Value | S    | Unit | Note /<br>Test Condition                                        | Number |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|-----------------------------------------------------------------|--------|

|                                                                                       |                                                                                                                                      | Min. | Тур.  | Max. |      |                                                                 |        |

| Voltages                                                                              |                                                                                                                                      |      | •     |      |      |                                                                 | 1      |

| BATPA, BATPB, OUT813,<br>DFB813                                                       | V <sub>BATPA,MR</sub> ,<br>V <sub>BATPB,MR</sub> ,<br>V <sub>OUT813,MR</sub> ,<br>V <sub>DFB813,MR</sub> ,                           | -0.3 | _     | 40   | V    | _                                                               | P_4.1  |

| CP                                                                                    | $V_{CP,MR}$                                                                                                                          | -0.3 | _     | 45   | V    | $\text{-0.3V} < V_{\text{CP}} - V_{\text{BATPA}} < \text{5V}$   | P_4.2  |

| OUT17, OUT1420                                                                        | V <sub>OUT17,MR</sub> ,<br>V <sub>OUT1420,MR</sub>                                                                                   | -0.3 | _     | 50   | V    | OUTn is switched off, clamping is allowed according Chapter 9.6 | P_4.3  |

| V6V                                                                                   | $V_{V6V,MR}$                                                                                                                         | -0.3 | _     | 10   | V    | _                                                               | P_4.4  |

| VG                                                                                    | $V_{VG,MR}$                                                                                                                          | -0.3 | _     | 12   | V    | $V_{\rm VG}$ - $V_{\rm V6V}$ <5V                                | P_4.5  |

| V5V, V5VSTBY, VDDIO,<br>V5VCAN                                                        | V <sub>V5V,MR</sub> ,<br>V <sub>V5VSTBY,MR</sub><br>V <sub>VDIO,MR</sub> ,<br>V <sub>V5VCAN,MR</sub>                                 | -0.3 | -     | 5.5  | V    | _                                                               | P_4.6  |

| T5V1, T5V2, IGN14                                                                     | $\begin{matrix} V_{T5V1,MR}, \\ V_{T5V2,MR}, \\ V_{IGN14,MR} \end{matrix}$                                                           | -1   | _     | 40   | V    | _                                                               | P_4.7  |

| BAT, BATSTBY, KEY, WK, MR                                                             |                                                                                                                                      | -16  | _     | 40   | V    | _                                                               | P_4.8  |

| IN112, SIP, SIN, FCLP,<br>FCLN, CSN, LINTX, CANTX,<br>IGNEN, INJEN, CANWKEN,<br>EOTEN | VIN112,MR, VFCLP,MR, VSIP,MR, VSIP,MR, VCSN,MR, VCSN,MR, VLINTX,MR, VCANTX,MR, VIGNEN,MR, VIJEN,MR, VIJEN,MR, VEOTEN,MR, VCANWKEN,MR | -0.3 | _     | 5.5  | V    | _                                                               | P_4.9  |

Table 2 Absolute Maximum Ratings<sup>1)</sup> (cont'd)

$T_i$ =-40 to 150°C, all voltages with respect to GND, positive current flowing into pin, (unless otherwise specified)

| Parameter                                                                                                                                                        | Symbol                                                                                                            | Values |      |                   | Unit | Note /                                                                                                                                 | Number |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------|------|-------------------|------|----------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                                                                                                                                  |                                                                                                                   | Min.   | Тур. | Max.              |      | Test Condition                                                                                                                         |        |

| SDO, RST,VROUT, LINRX,<br>CANRX                                                                                                                                  | $V_{SDO,MR},$ $V_{RST,MR},$                                                                                       | -0.3   | _    | <i>VDDIO</i> +0.3 | V    | both conditions must be observed                                                                                                       | P_4.31 |

|                                                                                                                                                                  | V <sub>VROUT,MR</sub> , V <sub>LINRX,MR</sub> , V <sub>CANRX,MR</sub>                                             | -0.3   | _    | 5.5               | V    |                                                                                                                                        |        |

| MON, KOFFDO                                                                                                                                                      | $V_{MON,MR}$ , $V_{KOFFDO,MR}$                                                                                    | -0.3   | _    | <i>V5V</i> +0.    | V    | both conditions must be observed                                                                                                       | P_4.10 |

|                                                                                                                                                                  |                                                                                                                   | -0.3   | _    | 5.5               | V    |                                                                                                                                        |        |

| VRIN1                                                                                                                                                            | $V_{VRIN1,MR}$                                                                                                    | -0.3   | _    | 40                | V    | VRIN2 open                                                                                                                             | P_4.11 |

| VRIN2                                                                                                                                                            | $V_{VRIN2\_MR}$                                                                                                   | -0.3   | _    | 40                | V    | VRIN1 open                                                                                                                             | P_4.12 |

| LINIO, CANH, CANL                                                                                                                                                | $egin{array}{c} V_{\text{LINIO},\text{MR}}, \ V_{\text{CANH},\text{MR}}, \ V_{\text{CANL},\text{MR}} \end{array}$ | -40    | -    | 40                | V    | _                                                                                                                                      | P_4.13 |

| OUT2124                                                                                                                                                          | V <sub>OUT2124,MR</sub>                                                                                           | -0.3   | _    | BATPx+<br>0.3     | V    | _                                                                                                                                      | P_4.14 |

| Currents                                                                                                                                                         |                                                                                                                   |        |      |                   |      |                                                                                                                                        |        |

| DFB813                                                                                                                                                           | $I_{\rm DFB813,MR}$                                                                                               | -5     | _    | 5                 | mA   | 2)                                                                                                                                     | P_4.15 |

| Common Mode Input Current of VRIN1 and VRIN2                                                                                                                     |                                                                                                                   | -5     | _    | 5                 | mA   | $I_{\substack{\text{VRIN,CM,MR} = I \\ \text{VRIN2}}} = I_{\substack{\text{VRIN1} + I \\ \text{VRIN2}}} + I$                           | P_4.16 |

| Common Mode Input Current of VRIN1 and VRIN2, non permanent                                                                                                      | $I_{ m VRIN,CM,MR}$                                                                                               | -15    | _    | 15                | mA   | $I_{\mathrm{VRIN,CM,MR}}$ = $I_{\mathrm{VRIN1}}$ + $I_{\mathrm{VRIN2}}^{2)}$ , maximum duty cycle 60% and maximum on time of 1ms, 100h | P_4.34 |

| Differential Current of VRIN1 and VRIN2                                                                                                                          | ΔI VRIN,MR                                                                                                        | -50    | _    | 50                | mA   | ΔI VRIN,MR=(I<br>VRIN1-I VRIN2)/2 <sup>2)</sup>                                                                                        | P_4.17 |

| PGND                                                                                                                                                             | $I_{PGND,MR}$                                                                                                     | -25    | _    | 25                | Α    | _                                                                                                                                      | P_4.18 |

| IGN14                                                                                                                                                            | $I_{\mathrm{IGN14,MR}}$                                                                                           | -50    | _    | _                 | mA   | 2)                                                                                                                                     | P_4.19 |

| Temperatures                                                                                                                                                     |                                                                                                                   |        | ,    |                   |      |                                                                                                                                        |        |

| Junction Temperature                                                                                                                                             | T <sub>j</sub>                                                                                                    | -40    | _    | 150               | °C   | 3)                                                                                                                                     | P_4.20 |

| Storage Temperature                                                                                                                                              | T <sub>stg</sub>                                                                                                  | -55    | _    | 150               | °C   | _                                                                                                                                      | P_4.21 |

| ESD Susceptibility                                                                                                                                               |                                                                                                                   |        |      |                   |      |                                                                                                                                        |        |

| ESD Susceptibility                                                                                                                                               | V <sub>ESDHBM</sub>                                                                                               | -2     | _    | 2                 | kV   | HBM <sup>4)</sup>                                                                                                                      | P_4.22 |

| ESD Susceptibility BAT,<br>BATPA, BATPB, T5V1, T5V2,<br>BATSTBY, KEY, WK, MR,<br>OUT17, OUT1424,<br>DFB813, IGN14, CANH,<br>CANL, LINIO, VRIN1, VRIN2 to<br>PGND | V <sub>ESD,HBM</sub>                                                                                              | -4     | -    | 4                 | kV   | HBM <sup>4)</sup>                                                                                                                      | P_4.23 |

## Table 2 Absolute Maximum Ratings<sup>1)</sup> (cont'd)

$T_i$ =-40 to 150°C, all voltages with respect to GND, positive current flowing into pin, (unless otherwise specified)

| Parameter                                                               | Symbol Values                                  |      |      | Unit | Note / | Number            |        |

|-------------------------------------------------------------------------|------------------------------------------------|------|------|------|--------|-------------------|--------|

|                                                                         |                                                | Min. | Тур. | Max. |        | Test Condition    |        |

| ESD Susceptibility                                                      | V <sub>ESDCDM</sub>                            | -500 | _    | 500  | V      | CDM <sup>5)</sup> | P_4.24 |

| ESD Susceptibility Pin 1, 25, 26, 50, 51, 75, 76, and 100 (corner pins) | V <sub>ESD1, 25, 26,</sub> 50, 51, 75, 76, 100 | -750 | _    | 750  | V      | CDM <sup>5)</sup> | P_4.25 |

- 1) not subject to production test

- 2) Current has to be limited when maximum voltages are exceeded

- 3) according to qualification

- 4) ESD susceptibility, HBM according to EIA/JESD 22-A114F (1.5kΩ, 100pF)

- 5) ESD susceptibility, Charged Device Model "CDM" EIA/JESD22-C101 or ESDA STM5.3.1

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### Table 3 Functional Range

$T_i$ =-40 to 150°C, all voltages with respect to GND, positive current flowing into pin, (unless otherwise specified)

| Parameter                                  | Symbol        |      | Values |      |   | Note /                                                                                                                                                          | Number |  |

|--------------------------------------------|---------------|------|--------|------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|

|                                            |               | Min. | Тур.   | Max. |   | Test Condition                                                                                                                                                  |        |  |

| Supply Voltage - Reduced<br>Operation      | $V_{BAT,ro}$  | 4.5  | -      | 6    | V | reduced operation range, main relay and delayed off power stages are on if enabled, remaining functions not working                                             | P_4.26 |  |

| Supply Voltage - Low Drop<br>Range         | $V_{BAT,Id}$  | 6    | -      | 9    | V | low drop<br>operation range,<br>supply regulators<br>working with<br>supply out of the<br>charge pump,<br>standby supply<br>regulator out of<br>operation range | P_4.27 |  |

| Supply Voltage - Normal<br>Operation range | $V_{BAT,nop}$ | 9    | _      | 28   | V | normal operation range <sup>1)</sup>                                                                                                                            | P_4.28 |  |

### Table 3 Functional Range (cont'd)

$T_i$ =-40 to 150°C, all voltages with respect to GND, positive current flowing into pin, (unless otherwise specified)

| Parameter                               | Symbol                            | Values |      |      | Unit | Note /                                            | Number |

|-----------------------------------------|-----------------------------------|--------|------|------|------|---------------------------------------------------|--------|

|                                         |                                   | Min.   | Тур. | Max. |      | Test Condition                                    |        |

| Supply Voltage - Over<br>Voltage Range  | $V_{BAT,ov}$                      | 28     | _    | 40   | V    | over voltage,<br>power stages are<br>switched off | P_4.29 |

| Supply Voltage transients <sup>2)</sup> | d <sub>VBAT</sub> /d <sub>t</sub> | -1     | _    | 1    | V/µs | -                                                 | P_4.30 |

<sup>1)</sup> over temperature due to bad  $R_{\rm thJA}$  of the ECU or overload can happen

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

Table 4 Thermal Resistance

| Parameter                      | Symbol            | Values |      | Unit | Note / | Number         |        |

|--------------------------------|-------------------|--------|------|------|--------|----------------|--------|

|                                |                   | Min.   | Тур. | Max. |        | Test Condition |        |

| Junction to Case <sup>1)</sup> | $R_{thJC}$        | _      | 2.4  | _    | K/W    | _              | P_4.32 |

| Junction to Ambient            | R <sub>thJA</sub> | _      | _    | _    | K/W    | 2)             | P_4.33 |

<sup>1)</sup> Not subject to production test, specified by design.

Data Sheet 16 Rev. 1.1, 2014-08-20

<sup>2)</sup> not subject to production test, specified by design

<sup>2)</sup> EIA/JESD 52\_2, FR4, 80 × 80 × 1.5 mm; 35 × Cu, 5 × Sn; 300 mm<sup>2</sup>

# 5 Operation Behavior

The TLE8888-1QK has implemented the whole supply of an ECU. Therefore a complex control logic is implemented to provide several operation states.

In this chapter

- · the ramp up and down behavior and

- the status of the TLE8888-1QK during special conditions like 5V undervoltage

is described. For the description of the monitoring watchdog module see Chapter 6.

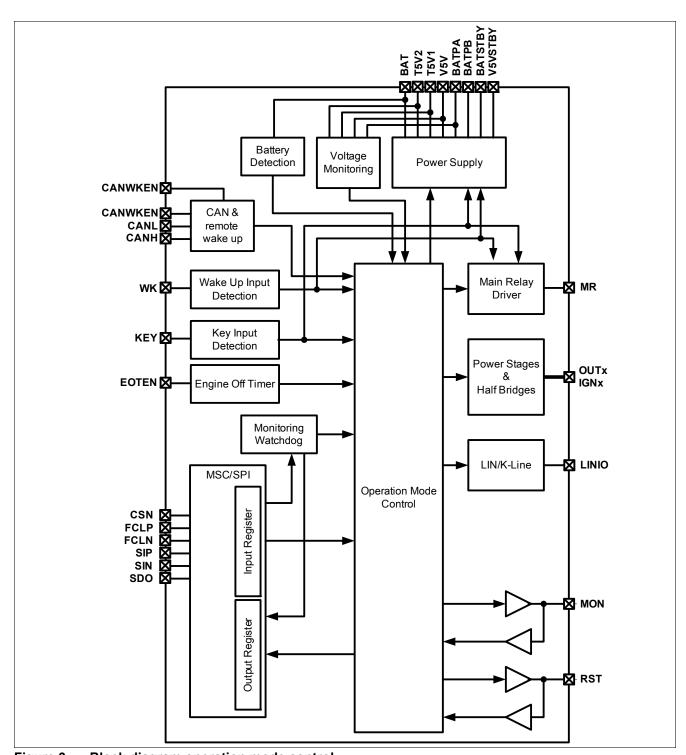

In **Figure 3** the block diagram with all blocks affecting the status of the device and the ECU are shown. Following blocks are influenced during the different operation states and reset functions:

- · Serial Interface MSC/SPI: with the serial interface the setup of the device is done

- Key input detection: start signal from key switch (KL15)

- · Wake up input detection: additional start signal e.g. from external CAN with wake up by bus function

- Engine off timer: wake up signal in comparator mode

- Power supply: ECU 5V supply and 5V sensor supplies, 5V standby supply

- Voltage monitoring: supervision of all supplies (BAT, V5V, T5V1, T5V2)

- Main relay driver: controls external main relay to switch battery voltage to an ECU supply pin (see also application setups in Chapter 17)

- Power stages and half-bridges control block

- LIN/K-Line: transmission mode depends on operation state of the ECU

- CAN: transmission mode depends on operation state of the ECU, remote wake up function

- Reset outputs MON and RST

- Monitoring watchdog module: signature watchdog for safety applications

- Operation Mode Control

The operation mode control block consists of:

- ramp up and down sequence control logic

- the reset control logic and

- status output logic.

Figure 3 Block diagram operation mode control

### 5.1 Operation States

In Figure 4 the state diagram of the whole ramp up and down sequence is shown. There are seven operation states:

• **ECU sleep state:** *KEY* and *WK* input are "low", no wake up signals from engine off timer or CAN are active, main relay is off, the whole ECU inclusive TLE8888-1QK is not supplied, 5V standby supply is working if pin *BATSTBY* is supplied, engine off timer and CAN wake up circuits are active if enabled and supplied.

- Supply ramp up state: KEY input or  $wake^{1)}$  are "high" and the supply of the TLE8888-1QK starts working, the voltage of V6V, V5V, T5V1 and T5V2 are ramping up but the voltage levels are below the under voltage threshold. For wake up by  $wake^{1)}$  the ramp up of the main supply has to be finished before the ramp up timer overflow. The main relay is switched on depending on the voltage level at the pin BAT (see Chapter 7.2)

- Normal operation state: KEY input or wake are "high" and main relay is switched on depending on the voltage level at the pin BAT or the status of bit MR in the status register OpStat0 (see Chapter 7.2), the whole ECU is supplied and the status of the different functions and registers is according Table 6 and Table 7.

- Afterrun state: KEY is "low" but afterrun enable bit is set and therefore the whole ECU is supplied, the status

of the different functions and registers is according Table 6 and Table 7 and the micro controller can execute

afterrun routines

- Afterrun reset state: the reset procedure before direct reentry in normal operation is executed if bit AR =1 in the configuration register OpConfig0

- General power down state: the supplies of the ECU (V5V, T5V1, T5V2) are disabled and the power down timer is counting, main relay remains in the switching status and the TLE8888-1QK is supplied to ensure the power down (V5V drops down to 0V) of the ECU, V5VSTBY is working if BATSTBY is supplied, all functions to external are disabled.

- Wake clear state: this state avoids permanent wake up in failure cases. The wake clear command is executed

(function according setting bit WKCLR in the command register Cmd0). All wake signals which are active after

the supply ramp up and the general power down state are reset.

Data Sheet 19 Rev. 1.1, 2014-08-20

<sup>1)</sup> description see Figure 4, Chapter 7.2, Chapter 7.4 and Chapter 12.2.4

Figure 4 Operation state diagram

Description of the transitions:

**Table 5** Operation State Transitions

| Table 5 Operation State Transitions                |                                                                                          |                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Transition                                         | Condition                                                                                | Description                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| from all states to ECU sleep state                 | internal supply voltage < internal por threshold and $KEY$ =0 and $wake^{1)}$ =0 $^{2)}$ | internal power on reset is active and reset the whole digital logic, ECU sleep state is entered due to no wake up signal at $KEY$ or wake                                                                                                                                                     |  |  |  |  |  |

| from all states to supply ramp up state            | internal supply voltage < internal por threshold and $KEY$ =1 or $wake$ =1 $^{2)}$       | internal power on reset is active and reset the whole digital logic, supply ramp up state is entered due to a wake up signal at $KEY$ or $wake$                                                                                                                                               |  |  |  |  |  |

| ECU sleep state to supply ramp up state            | $KEY>V_{KEY,th}$ or wake=1                                                               | With a "high" voltage at $KEY$ or wake the wake up of the TLE8888-1QK starts                                                                                                                                                                                                                  |  |  |  |  |  |

| Supply ramp up state to ECU sleep state            | $KEY$ < $V_{\rm KEY,th}$ and $wake$ = $0^{2)}$                                           | The external supply ramp up is not finished but the wake up signals are low                                                                                                                                                                                                                   |  |  |  |  |  |

| Supply ramp up state to wake clear state           | $KEY$ < $V_{\rm KEY,th}$ and $wake$ =1 $^{2)}$ and RT_OF=1                               | The $KEY$ signal is low and the wake up signals are active. The ramp up timer has an overflow which indicates a ramp up problem of the external supply (e.g. short to GND). To avoid permanent high current consumption the internal wake signals must be reset to enter the ECU sleep state. |  |  |  |  |  |

| Supply ramp up state to normal operation state     | $(KEY>V_{\rm KEY,th} \text{ or } wake=1)$ and V5V>V <sub>uv</sub> ,V5V <sup>2)</sup>     | normal operation state is entered if the main supply voltage $V5V$ is above the under voltage threshold, $KEY$ is high or one of the wake up conditions are active                                                                                                                            |  |  |  |  |  |

| Normal operation state to afterrun state           | $KEY < V_{\rm KEY,th}$ and AE=1 <sup>2)</sup>                                            | KEY is "low" and afterrun function is enabled: no changes in the setup of the TLE8888-1QK                                                                                                                                                                                                     |  |  |  |  |  |

| Normal operation state to ECU sleep state          | AE=0 and KEY< $V_{\rm KEY,th}$ and $wake=0^2$                                            | normal shut off                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Normal operation state to general power down state | (PD_OF=1 or SSOT_OF=1) and KEY< $V_{\rm KEY,th}$ <sup>2)</sup>                           | KEY is low and watchdog error shut off with overflow of the power down counter or secure shut off due to expired secure shut off timer                                                                                                                                                        |  |  |  |  |  |

| Afterrun state to ECU sleep state                  | AE=0 and KEY< $V_{\rm KEY,th}$ and wake=0 $^{2)}$                                        | normal shut off in afterrun mode with the reset of the afterrun enable bit AE by the micro controller                                                                                                                                                                                         |  |  |  |  |  |

| Afterrun state to general power down state         | PD_OF=1<br>or<br>SSOT_OF=1                                                               | watchdog error shut off with overflow of the power down counter or secure shut off due to expired secure shut off timer                                                                                                                                                                       |  |  |  |  |  |

| Afterrun state to normal operation state           | $KEY>V_{\rm KEY,th}$ and AR=0 <sup>2)</sup>                                              | reentry of normal operation with $KEY$ on during afterrun operation, no reset is performed (AR=0)                                                                                                                                                                                             |  |  |  |  |  |

| Afterrun state to afterrun reset state             | $KEY>V_{\rm KEY,th}$ and AR=1 $^{2)}$                                                    | reentry of normal operation with $KEY$ on during afterrun operation with reset (AR=1)                                                                                                                                                                                                         |  |  |  |  |  |

| Afterrun reset state to normal operation state     |                                                                                          | transition to normal operation with the next active internal clock edge after entry to the afterrun reset state                                                                                                                                                                               |  |  |  |  |  |

| General power down state to wake clear state       | PDT_OF=1                                                                                 | with the power down timer overflow the reset of the internal wake signals must be performed                                                                                                                                                                                                   |  |  |  |  |  |

Table 5 Operation State Transitions (cont'd)

| Transition                               | Condition                 | Description                                                                                                                                                                           |

|------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wake clear state to ECU sleep state      | KEY <v<sub>KEY,th</v<sub> | after reset of the internal wake signals and $KEY$ is low the ECU sleep state is entered, no unwanted wake up due to a failure condition will occur                                   |

| Wake clear state to supply ramp up state | $KEY>V_{KEY,th}$          | after reset of the internal wake signals and $KEY$ is high the supply ramp up state is entered, no unwanted wake up due to a failure condition at the CAN bus and pin $WK$ will occur |

- 1) wake = WKINT or CANWK or EOTWK (see Chapter 7.2, Chapter 7.4 and Chapter 12.2.4)

- 2) including defined filter times

#### The two states:

- · normal operation

- afterrun

are reflected in the bit OM of the status register OpStat0.

The power down time is defined with the bits PDT of the configuration register OpConfig0.

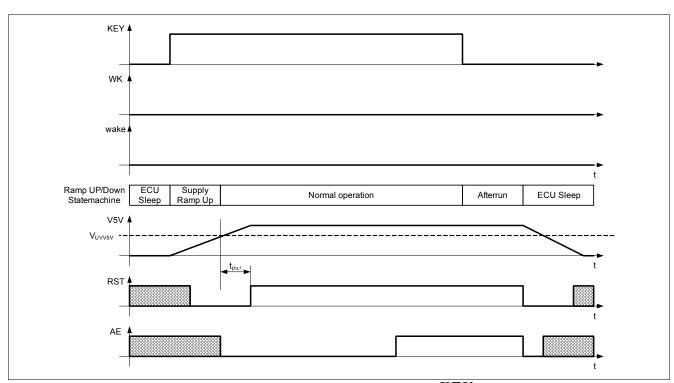

In **Figure 5** a sequence with wake up by KEY and go to sleep with afterrun mode is shown.

Figure 5 Ramp up and down sequence diagram with wake up by KEY and afterrun mode

### 5.2 Reset and Operation Modes

The TLE8888-1QK provides several supervision functions which lead to some dedicated reset states and special operation modes of the device and the ECU.

There are two bidirectional reset pins MON and RST implemented. For the behavior during reset of the reset pins MON and RST and the other status of the TLE8888-1QK see **Table 6** and **Table 7**.

Following reset functions and special states are implemented:

- Internal power on reset: the internal power on reset detection circuit monitors the voltage level of the internal supply. For an internal supply voltage below the internal power on reset threshold the whole digital logic of the TLE8888-1QK is reset which results in the ECU sleep state or supply ramp up state depending on the state of *KEY* and *wake*. If the voltage level for operation is high enough the 6V pre regulator is working. The 5V supplies are disabled till the internal supply level is over the power on threshold level.

- **ECU power on reset:** this is the reset at ramp up of the power supplies and the beginning of the operation. The pins RST and MON are pulled to GND to reset the micro controller and all devices connected to the pin MON. The device is reset to the initial reset status. The reset is released with a voltage at pin V5V higher than the V5V **Under Voltage Detection Hysteresis** after  $t_{\text{pur}}$ .

- Reset during under voltage of the 5V supply V5V: this reset occurs during under voltage of the 5V ECU supply. The pins RST and MON are pulled to GND to reset the micro controller and all devices connected to the pin MON. The delayed switch off function is active regarding the configuration setup. The status of the main relay is according to the status of the wake up pins KEY and WK and the voltage level of the supply pin BAT.

- State during under voltage of the 5V supplies T5V1 and T5V2: with the under voltage detection of the tracker supplies diagnosis bits are set but there is no effect to the behavior of the device.

- Reset during over voltage of the 5V supply V5V: with the over voltage detection of the 5V ECU supply all functions of the device which have an effect externally or can lead to over current or over temperature are disabled (e.g. power stages, LIN/CAN/MSC/SPI communication). The pins RST and MON are low.

- State during over voltage of the 5V supplies T5V1 and T5V2: with the detection of over voltage of the tracker supplies diagnosis bits are set but there is no effect to the behavior of the device.

- Power stages switch off during over voltage of the battery supply BAT: For voltages at the supply pin BAT higher than the over voltage threshold the power stages are disabled to avoid too high clamping energy during switch off. Damage of the switches is prevented.

- Watchdog reset: If the reset counter is incremented and the reset is enabled (bit WDREN = 1) the micro controller is reset with a "low" at the pin RST. The power stages are disabled and the LIN/CAN communication is set to receive only mode.

- Software reset from micro controller: with the software reset command (command register CmdSR) the software reset is activated. The device is reset to the reset status defined in Table 6 and Table 7. The activation of the software reset triggers an increase of the power down counter by 1.

- Reset with an external forced "low" at RST: With a detected "low" at the RST pin the TLE8888-1QK is reset to the reset status defined in Table 6 and Table 7.

- Power stages switch off with an external forced "low" at MON: With a detected "low" at the MON pin

the power stages are disabled (O1E to O24E, IGN1E to IGN4E are set to "0"). After MON=0 event the power

stages must be enabled again.

- State with time out of the MSC communication: With the time out of the MSC communication the power stages are disabled (O1E to O24E, IGN1E to IGN4E are set to "0"). After the next valid received data frame the power stages must be enabled again.

- Afterrun reset: This reset is executed if the bit AR of register OpConfig0 is 1 and the transition from afterrun state to normal operation is triggered (definition see Table 7).

Data Sheet 23 Rev. 1.1, 2014-08-20

Table 6 Overview Behavior at Reset and Operation Conditions (part 1)

Effect to functions: Conditions

| Effect to functions:                                     | Conditions                 |                                                                                    |                                                                               |                                        |                                                                        |                                  |                                  |  |

|----------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------|----------------------------------|----------------------------------|--|

|                                                          | Internal power<br>on reset | ECU power on reset                                                                 | Under voltage<br>V5V                                                          | Undervoltage<br>T5V1, T5V2             | Over voltage V5V <sup>1)</sup>                                         | Overvoltage<br>T5V1, T5V2        | Over voltage BAT                 |  |

| notes                                                    | forces state change        | only after transition from Supply Ramp Up to Normal Operation state for $t_{pu,r}$ | timing see Chapter 8.7 and Table 8                                            | timing see Chapter 8.7                 | timing see Chapter 8.7 and Table 8                                     | timing see Chapter 8.7           | timing see<br>Chapter 8.7        |  |

| V5VSTBY, V6V                                             | en.                        | en.                                                                                | en.                                                                           | en.                                    | en.                                                                    | en.                              | en.                              |  |

| V5V, T5V1, T5V2                                          | dis.                       | en.                                                                                | en.                                                                           | en.                                    | en.                                                                    | en.                              | en.                              |  |

| MSC/SPI communication                                    | dis.                       | dis.                                                                               | dis.                                                                          | en.                                    | dis.                                                                   | en.                              | en.                              |  |