Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **Features**

- Three half bridge power outputs

- Very low power consumption in sleep mode

- 3.3V / 5V compatible inputs with hysteresis

- All outputs with overload and short circuit protection

- · Direct interface for control and diagnosis

- Overtemperature protection

- Over- and Undervoltage lockout

- · Cross-current protection

## **Potential applications**

- HVAC Flap DC motors

- Monostable and bistable relays

- Side mirror x-y adjustment

### **Product validation**

Qualified for Automotive Applications. Product Validation according to AEC-Q100

# **Description**

The TLE94003EP is a protected triple half-bridge driver designed especially for automotive motion control applications such as side mirror x-y adjustment. It is part of a larger family offering half-bridge drivers from three outputs to twelve outputs with direct interface or SPI interface.

The half bridge drivers are designed to drive DC motor loads in sequential or parallel operation. Operation modes forward (cw), reverse (ccw), brake and high impedance are controlled from a direct interface. It offers diagnosis features such as short circuit, power supply failure and overtemperature detection. In combination with its low quiescent current, this device is attractive among others for automotive applications. The small fine pitch exposed pad package, PG-TSDSO-14, provides good thermal performance and reduces PCB-board space and costs.

| Туре       | Package     | Marking  |

|------------|-------------|----------|

| TLE94003EP | PG-TSDSO-14 | TLE94003 |

## Table 1 Product Summary

| Operating Voltage                                  | $V_{S}$                          | 5.5 20 V    |

|----------------------------------------------------|----------------------------------|-------------|

| Logic Supply Voltage                               | $V_{DD}$                         | 3.0 5.5 V   |

| Maximum Supply Voltage for Load Dump<br>Protection | $V_{S(LD)}$                      | 40 V        |

| Minimum Overcurrent Threshold                      | I <sub>SD</sub>                  | 0.9 A       |

| Maximum On-State Path Resistance at $T_j = 150$ °C | R <sub>DSON(total)_HSx+LSy</sub> | 1.8 + 1.8 Ω |

| Typical Quiescent Current at T <sub>i</sub> = 85°C | I <sub>so</sub>                  | 0.1 μΑ      |

# **Table of Contents**

| <b>1</b><br>1.1<br>1.2                          | Pin Configuration       Pin Assignment         Pin Definitions and Functions       Pin Definitions                                     | 4                            |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| <b>2</b><br>2.1                                 | Block Diagram                                                                                                                          | 6                            |

| 3.1<br>3.2<br>3.3<br>3.4                        | General Product Characteristics Absolute Maximum Ratings Functional Range Thermal Resistance Electrical Characteristics                | {<br>. 1(<br>. 1)            |

| 4                                               | Characterization results                                                                                                               | . 15                         |

| 5<br>5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.3<br>5.4 | General Description Power Supply Operation modes Normal mode Sleep mode Reset Behaviour Reverse Polarity Protection                    | . 20<br>. 20<br>. 20<br>. 20 |

| 6<br>6.1<br>6.2<br>6.3<br>6.3.1<br>6.3.2        | Half-Bridge Outputs Output Stages Diagnosis Monitoring Protection Short Circuit of Output to Supply or Ground Cross-current protection | . 22<br>. 25<br>. 25         |

| 6.3.3<br>6.3.4<br>6.3.5<br>6.3.6                | Temperature monitoring and shutdown  VS Undervoltage Behaviour  VS Overvoltage Behaviour  VDD Undervoltage                             | . 28<br>. 30                 |

| <b>7</b><br>7.1<br>7.2                          | Application Information                                                                                                                | . 32                         |

| 8                                               | Package Outlines                                                                                                                       | . 36                         |

| 9                                               | Revision History                                                                                                                       | . 37                         |

3

### **Pin Configuration**

# 1 Pin Configuration

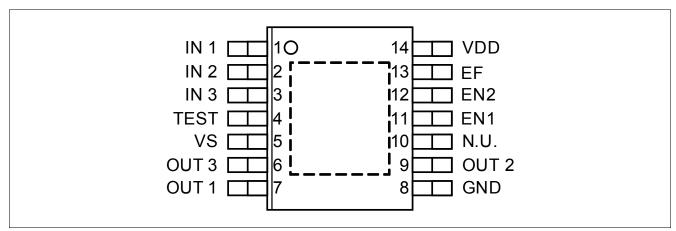

# 1.1 Pin Assignment

Figure 1 Pin Configuration TLE94003EP with direct interface

### 1.2 Pin Definitions and Functions

| Symbol                                           | Function                                                                                                                               |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| IN1                                              | Direct input control for power half-bridge 1                                                                                           |

| IN2 Direct input control for power half-bridge 2 |                                                                                                                                        |

| IN3 Direct input control for power half-bridge 3 |                                                                                                                                        |

| TEST                                             | Test input. This pin can be left open or be terminated to ground                                                                       |

| VS                                               | Main supply voltage for power half bridges.                                                                                            |

| OUT 3                                            | Power half-bridge 3                                                                                                                    |

| OUT 1                                            | Power half-bridge 1                                                                                                                    |

| GND                                              | Ground                                                                                                                                 |

| OUT 2                                            | Power half-bridge 2                                                                                                                    |

| N.U.                                             | Not used. This pin should either be left open or terminated to ground.                                                                 |

| EN1                                              | Enable input for Half-bridges 1/2 with internal pull-down                                                                              |

| EN2                                              | Enable input for Half-bridge 3 with internal pull-down                                                                                 |

| EF                                               | Error Flag                                                                                                                             |

| VDD                                              | Logic supply voltage                                                                                                                   |

| -                                                | Exposed Die Pad; For cooling and EMC purposes only - not usable as electrical ground. Electrical ground must be provided by pins 8. 1) |

|                                                  | IN1 IN2 IN3 TEST VS OUT 3 OUT 1 GND OUT 2 N.U. EN1 EN2 EF                                                                              |

<sup>1)</sup> The exposed die pad at the bottom of the package allows better heat dissipation from the device via the PCB. The exposed pad (EP) must be either left open or connected to GND. It is recommended to connect EP to GND for best EMC and thermal performance.

### **Pin Configuration**

Note:

Not used (N.U.) pins and unused outputs are recommended to be left unconnected (open) on the application board. If N.U. pins or unused output pins are routed to an external connector which leaves the PCB, then these outputs should have provision for a zero ohm jumper (depopulated if unused) or ESD protection. In other words, they should be treated like used pins.

### **Block Diagram**

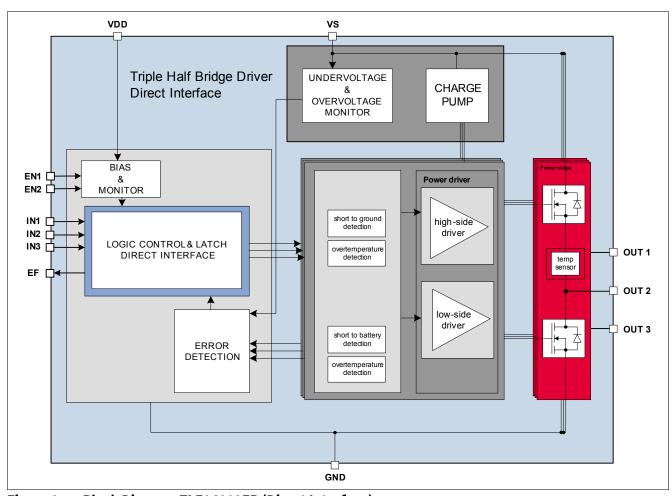

# 2 Block Diagram

Figure 2 Block Diagram TLE94003EP (Direct Interface)

### **Block Diagram**

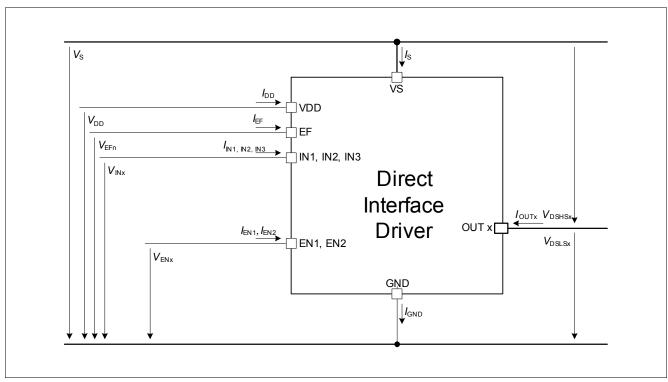

# 2.1 Voltage and current definition

Figure 3 shows terms used in this datasheet, with associated convention for positive values.

Figure 3 Voltage and Current Definition

### 3 General Product Characteristics

### 3.1 Absolute Maximum Ratings

Table 2 Absolute Maximum Ratings<sup>1)</sup> $T_i = -40$ °C to +150°C

| Parameter                                                                | Symbol                     |      | Value | S    | Unit | Note or                                                                                     | Number   |  |

|--------------------------------------------------------------------------|----------------------------|------|-------|------|------|---------------------------------------------------------------------------------------------|----------|--|

|                                                                          |                            | Min. | Тур.  | Max. |      | <b>Test Condition</b>                                                                       |          |  |

| Voltages                                                                 |                            | 1    | JI.   | 1    |      |                                                                                             |          |  |

| Supply voltage                                                           | $V_{S}$                    | -0.3 | _     | 40   | V    |                                                                                             | P_4.1.1  |  |

| Supply Voltage Slew Rate                                                 | dV <sub>s</sub> /dt        | -    | -     | 10   | V/µs | V <sub>S</sub> increasing and decreasing <sup>1)</sup>                                      | P_4.2.2  |  |

| Power half-bridge output voltage                                         | V <sub>OUT</sub>           | -0.3 | _     | 40   | V    | $0 \text{ V} < V_{\text{OUT}} < V_{\text{S}}^{2)}$                                          | P_4.1.2  |  |

| Logic supply voltage                                                     | $V_{DD}$                   | -0.3 | _     | 5.5  | V    | 0 V < V <sub>S</sub> < 40 V                                                                 | P_4.1.3  |  |

| Logic input voltages<br>(EN1, EN2, IN1, IN2, IN3)                        | $V_{\rm ENn}, V_{\rm INn}$ | -0.3 | _     | VDD  | V    | 0 V < V <sub>S</sub> < 40 V<br>0 V < V <sub>DD</sub> < 5.5V                                 | P_4.1.16 |  |

| Logic output voltage<br>(EF)                                             | V <sub>EF</sub>            | -0.3 | -     | VDD  | V    | $0 \text{ V} < V_{\text{S}} < 40 \text{ V}$<br>$0 \text{ V} < V_{\text{DD}} < 5.5 \text{V}$ | P_4.1.17 |  |

| Currents                                                                 |                            |      |       |      |      |                                                                                             |          |  |

| Continuous Supply Current for V <sub>S</sub>                             | Is                         | 0    | _     | 1.5  | Α    | _                                                                                           | P_4.1.20 |  |

| Current per GND pin                                                      | I <sub>GND</sub>           | 0    | _     | 2.0  | Α    | _                                                                                           | P_4.1.14 |  |

| Output Currents                                                          | $I_{OUT}$                  | -2.0 | -     | 2.0  | Α    | _                                                                                           | P_4.1.15 |  |

| Temperatures                                                             |                            |      |       |      |      |                                                                                             |          |  |

| Junction temperature                                                     | T <sub>j</sub>             | -40  | _     | 150  | °C   | _                                                                                           | P_4.1.8  |  |

| Storage temperature                                                      | $T_{\rm stg}$              | -50  | _     | 150  | °C   | _                                                                                           | P_4.1.9  |  |

| ESD Susceptibility                                                       |                            |      |       |      |      |                                                                                             |          |  |

| ESD susceptibility OUTn and VS pins versus GND. All other pins grounded. | V <sub>ESD</sub>           | -4   | _     | 4    | kV   | JEDEC HBM <sup>1)3)</sup>                                                                   | P_4.1.10 |  |

| ESD susceptibility all pins                                              | $V_{ESD}$                  | -2   | -     | 2    | kV   | JEDEC HBM <sup>1)3)</sup>                                                                   | P_4.1.11 |  |

| ESD susceptibility all pins                                              | $V_{ESD}$                  | -500 | -     | 500  | V    | CDM <sup>1)4)</sup>                                                                         | P_4.1.12 |  |

| ESD susceptibility corner pins                                           | $V_{ESD}$                  | -750 | _     | 750  | V    | CDM <sup>1)4)</sup>                                                                         | P_4.1.13 |  |

- 1) Not subject to production test, specified by design

- 2) Also applicable to not used (N.U.) pins

- 3) ESD susceptibility, "JEDEC HBM" according to ANSI/ ESDA/ JEDEC JS001 (1.5 k $\Omega$ , 100pF)

- 4) ESD susceptibility, Charged Device Model "CDM" according JEDEC JESD22-C101

### **Notes**

1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **General Product Characteristics**

2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

# 3.2 Functional Range

Table 3 Functional Range

| Parameter                                         | Symbol                     |      | Values |      |    | Note or               | Number  |

|---------------------------------------------------|----------------------------|------|--------|------|----|-----------------------|---------|

|                                                   |                            | Min. | Тур.   | Max. |    | <b>Test Condition</b> |         |

| Supply voltage range for normal operation         | V <sub>S(nor)</sub>        | 5.5  | -      | 20   | V  | -                     | P_4.2.1 |

| Logic supply voltage range for normal operation   | $V_{DD}$                   | 3.0  | -      | 5.5  | V  | -                     | P_4.2.3 |

| Logic input voltages<br>(EN1, EN2, IN1, IN2, IN3) | $V_{\rm INn}, V_{\rm ENn}$ | -0.3 | -      | 5.5  | V  | -                     | P_4.2.6 |

| Junction temperature                              | $T_{j}$                    | -40  | -      | 150  | °C |                       | P_4.2.5 |

Note:

Within the normal functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

### 3.3 Thermal Resistance

Table 4 Thermal Resistance TLE94003EP

| Parameter                                                                     | Symbol                   | Symbol Values |      |      | Unit | Note or               | Number |

|-------------------------------------------------------------------------------|--------------------------|---------------|------|------|------|-----------------------|--------|

|                                                                               |                          | Min.          | Тур. | Max. |      | <b>Test Condition</b> |        |

| Junction to Case, $T_A = -40$ °C                                              | $R_{\rm thjC\_cold}$     | _             | 16   | _    | K/W  | 1)                    |        |

| Junction to Case, $T_A = 85^{\circ}C$                                         | R <sub>thjC_hot</sub>    | _             | 19   | -    | K/W  | 1)                    |        |

| Junction to ambient, $T_A = -40^{\circ}C$ (1s0p, minimal footprint)           | R <sub>thjA_cold_</sub>  | _             | 136  | -    | K/W  | 1) 2)                 |        |

| Junction to ambient, $T_A = 85$ °C (1s0p, minimal footprint)                  | R <sub>thjA_hot_m</sub>  | _             | 148  | -    | K/W  | 1) 2)                 |        |

| Junction to ambient, $T_A = -40^{\circ}\text{C}$ (1s0p, 300mm2 Cu)            | R <sub>thjA_cold_3</sub> | _             | 79   | -    | K/W  | 1) 3)                 |        |

| Junction to ambient, $T_A = 85^{\circ}\text{C}$ (1s0p, 300mm2 Cu)             | R <sub>thjA_hot_30</sub> | _             | 95   | -    | K/W  | 1) 3)                 |        |

| Junction to ambient, $T_A = -40^{\circ}\text{C}$ (1s0p, 600mm2 Cu)            | R <sub>thjA_cold_6</sub> | -             | 77   | -    | K/W  | 1) 4)                 |        |

| Junction to ambient, $T_A = 85^{\circ}C$ (1s0p, 600mm2 Cu)                    | R <sub>thjA_hot_60</sub> | -             | 94   | -    | K/W  | 1) 4)                 |        |

| Junction to ambient, $T_A = -40^{\circ}\text{C}$ $R_{\text{thjA\_co}}$ (2s2p) |                          | -             | 63   | -    | K/W  | 1) 5)                 |        |

| Junction to ambient, $T_A = 85^{\circ}\text{C}$ (2s2p)                        | R <sub>thjA_hot_2s</sub> | _             | 82   | -    | K/W  | 1) 5)                 |        |

- 1) Not subject to production test, specified by design.

- 2) Specified  $R_{thJA}$  value is according to JEDEC JESD51-2, -3 at natural convection on FR4 1s0p board; The product (chip + package) was simulated on a 76.2 x 114.3 x 1.5mm board with minimal footprint copper area and 35 $\mu$ m thickness. Ta = -40°C, each channel dissipates 0.2W. Ta = 85°C, each channel dissipates 0.135W.

- 3) Specified  $R_{thJA}$  value is according to JEDEC JESD51-2, -3 at natural convection on FR4 1s0p board; The product (chip + package) was simulated on a 76.2 x 114.3 x 1.5mm board with additional cooling of 300mm2 copper area and 35 $\mu$ m thickness. Ta = -40°C, each channel dissipates 0.2W. Ta = 85°C, each channel dissipates 0.135W.

- 4) Specified  $R_{thJA}$  value is according to JEDEC JESD51-2, -3 at natural convection on FR4 1s0p board; The product (chip + package) was simulated on a 76.2 x 114.3 x 1.5mm board with additional cooling of 600mm2 copper area and 35 $\mu$ m thickness. Ta = -40°C, each channel dissipates 0.2W. Ta = 85°C, each channel dissipates 0.135W.

- 5) Specified  $R_{thJA}$  value is according to JEDEC JESD51-2, -3 at natural convection on FR4 2s2p board; The product (chip + package) was simulated on a 76.2 x 114.3 x 1.5mm board with two inner copper layers (4 x 35 $\mu$ m Cu). Ta = -40°C, each channel dissipates 0.2W. Ta = 85°C, each channel dissipates 0.135W.

### 3.4 Electrical Characteristics

Table 5 Electrical Characteristics,  $V_S$  = 5.5 V to 20 V,  $V_{DD}$  = 3.0V to 5.5V,  $T_j$  = -40°C to +150°C, EN1= HIGH and EN2= HIGH,  $I_{OUTn}$ = 0 A; Typical values refer to  $V_{DD}$  = 5.0 V,  $V_S$  = 13.5 V and  $T_J$  = 25 °C unless otherwise specified; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                             | Symbol                                   |          | Value   | S        | Unit     | Note or                                                                   | Number    |

|-------------------------------------------------------|------------------------------------------|----------|---------|----------|----------|---------------------------------------------------------------------------|-----------|

|                                                       |                                          | Min.     | Тур.    | Max.     |          | <b>Test Condition</b>                                                     |           |

| Current Consumption, EN1 = E                          | N2 = GND                                 |          |         | ·        | į.       |                                                                           |           |

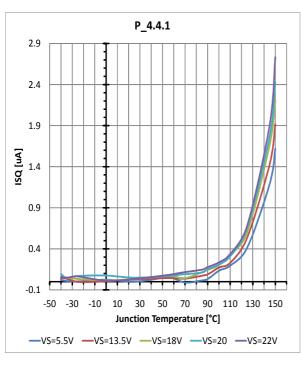

| Supply Quiescent current                              | $I_{SQ}$                                 | _        | 0.1     | 2        | μΑ       | $-40^{\circ}\text{C} \le T_{j} \le 85^{\circ}\text{C}$                    | P_4.4.1   |

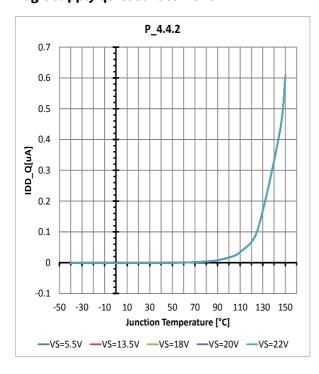

| Logic supply quiescent current                        | $I_{\mathrm{DD}_{\mathrm{Q}}}$           | _        | 0.1     | 1        | μΑ       | $-40$ °C ≤ $T_j$ ≤ $85$ °C                                                | P_4.4.2   |

| Total quiescent current                               | $I_{SQ} + I_{DD_Q}$                      | _        | 0.6     | 3        | μΑ       | -40°C ≤ $T_j$ ≤ 85°C                                                      | P_4.4.3   |

| Current Consumption, EN=HIG                           | Н                                        |          |         |          |          |                                                                           |           |

| Supply current                                        | I <sub>S_HSON</sub>                      | _        | 1.5     | 3        | mA       | All high-sides ON <sup>1)2)</sup>                                         | P_4.4.101 |

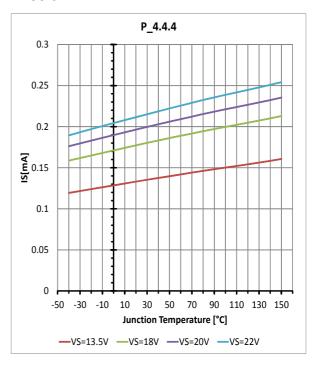

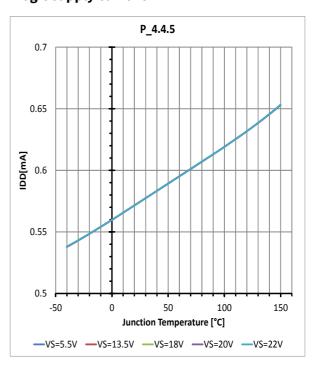

| Logic supply current                                  | I <sub>DD</sub>                          | _        | 0.6     | 2.5      | mA       |                                                                           | P_4.4.5   |

| Over- and Undervoltage Locko                          | ut                                       | •        |         |          |          | •                                                                         | •         |

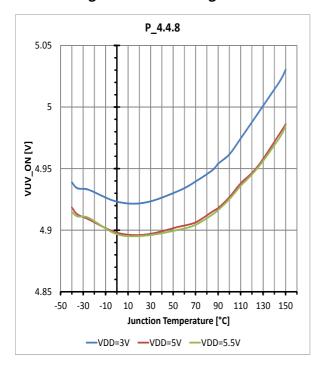

| Undervoltage Switch ON voltage threshold              | V <sub>UV ON</sub>                       | 4.4      | 4.90    | 5.3      | V        | V <sub>s</sub> increasing                                                 | P_4.4.8   |

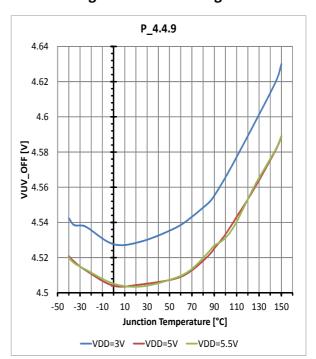

| Undervoltage Switch OFF voltage threshold             | V <sub>UV OFF</sub>                      | 4        | 4.50    | 4.9      | V        | $V_{\rm S}$ decreasing                                                    | P_4.4.9   |

| Undervoltage Switch ON/OFF hysteresis                 | V <sub>UV HY</sub>                       | _        | 0.40    | -        | V        | V <sub>UV ON</sub> - V <sub>UV OFF</sub> <sup>2)</sup>                    | P_4.4.10  |

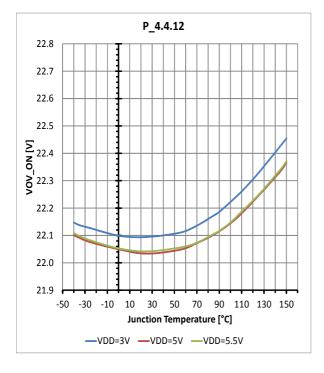

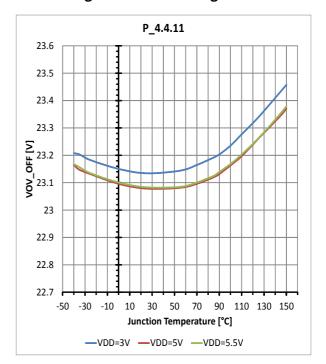

| Overvoltage Switch OFF voltage threshold              | V <sub>OV OFF</sub>                      | 21       | 23      | 25       | V        | V <sub>S</sub> increasing                                                 | P_4.4.11  |

| Overvoltage Switch ON voltage threshold               | V <sub>OV ON</sub>                       | 20       | 22      | 24       | V        | V <sub>S</sub> decreasing                                                 | P_4.4.12  |

| Overvoltage Switch ON/OFF hysteresis                  | V <sub>OV HY</sub>                       | _        | 1       | -        | V        | V <sub>OV OFF</sub> - V <sub>OV ON</sub> <sup>2)</sup>                    | P_4.4.13  |

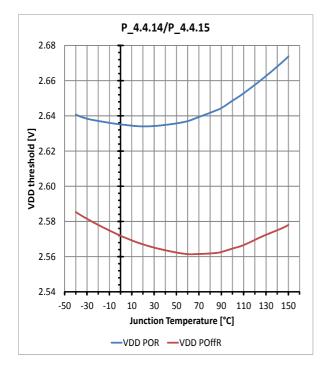

| V <sub>DD</sub> Power-On-Reset                        | $V_{\rm DDPOR}$                          | 2.40     | 2.63    | 2.90     | ٧        | $V_{\rm DD}$ increasing                                                   | P_4.4.14  |

| V <sub>DD</sub> Power-Off-Reset                       | $V_{\rm DD\ POffR}$                      | 2.35     | 2.57    | 2.85     | ٧        | $V_{\rm DD}$ decreasing                                                   | P_4.4.15  |

| V <sub>DD</sub> Power ON/OFF hysteresis               | V <sub>DD POR HY</sub>                   | -        | 0.06    | -        | V        | $V_{\rm DD\ POR}$ - $V_{\rm DD\ POffR}^{2)}$                              | P_4.4.98  |

| Static Drain-source ON-Resista                        | nce (High-Si                             | ide or L | .ow-Sid | e)       | *        |                                                                           | -!        |

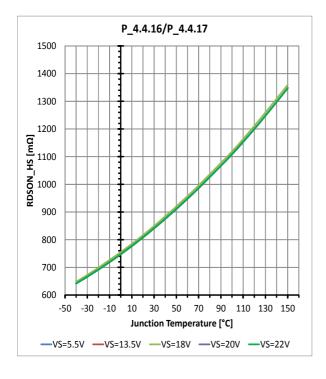

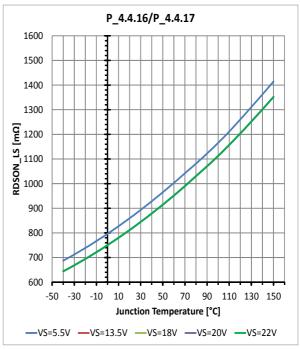

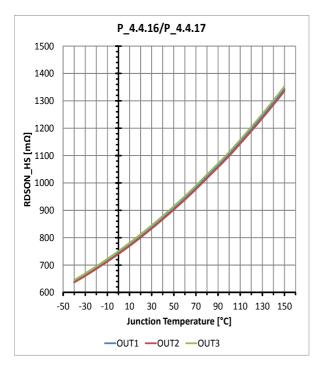

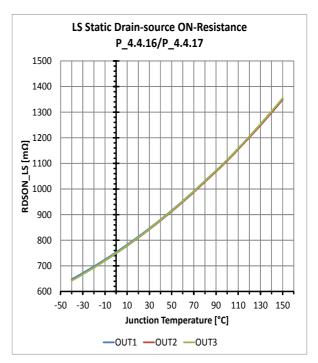

| High-Side or Low-Side R <sub>DSON</sub> (all outputs) | R <sub>DSON_HB_25C</sub>                 | -        | 825     | 1200     | mΩ       | $I_{OUT} = \pm 0.5 \text{ A};$<br>$T_i = 25 \text{ °C}$                   | P_4.4.16  |

| High-Side or Low-Side R <sub>DSON</sub> (all outputs) | R <sub>DSON_HB_150</sub>                 | -        | 1350    | 1800     | mΩ       | $I_{OUT} = \pm 0.5 \text{ A};$<br>$T_i = 150 ^{\circ}\text{C}$            | P_4.4.17  |

| Output Protection and Diagno                          | 1                                        | de (HS)  | chann   | els of h | alf-brid | ,                                                                         | 1         |

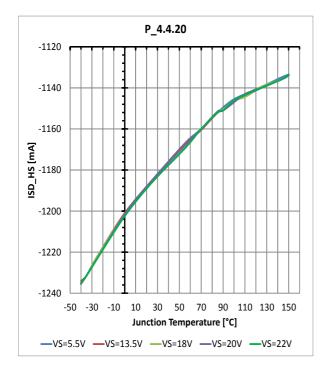

| HS Overcurrent Shutdown<br>Threshold                  | I <sub>SD_HS</sub>                       | -1.5     | -1.2    | -0.9     | А        | See Figure 7                                                              | P_4.4.20  |

| Difference between shutdown and limit current         | I <sub>LIM_HS</sub> - I <sub>SD_HS</sub> | -1.2     | -0.6    | 0        | А        | 2)   I <sub>LIM_HS</sub>   ≥  I <sub>SD_HS</sub>  <br>See <b>Figure 7</b> | P_4.4.21  |

Table 5 Electrical Characteristics,  $V_S$  = 5.5 V to 20 V,  $V_{DD}$  = 3.0V to 5.5V,  $T_j$  = -40°C to +150°C, EN1= HIGH and EN2= HIGH,  $I_{OUTn}$ = 0 A; Typical values refer to  $V_{DD}$  = 5.0 V,  $V_S$  = 13.5 V and  $T_J$  = 25 °C unless otherwise specified; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified) (cont'd)

| Parameter                                       | Symbol                                   |          | Value  | <b>S</b> | Unit     | Note or                                                                                             | Number   |  |

|-------------------------------------------------|------------------------------------------|----------|--------|----------|----------|-----------------------------------------------------------------------------------------------------|----------|--|

|                                                 |                                          | Min.     | Тур.   | Max.     |          | <b>Test Condition</b>                                                                               |          |  |

| Overcurrent Shutdown filter time                | t <sub>dSD_HS</sub>                      | 15       | 19     | 23       | μs       | 2)                                                                                                  | P_4.4.22 |  |

| <b>Output Protection and Diagno</b>             | sis of low-s                             | ide (LS) | channe | ls of ha | lf-bridg | e output                                                                                            |          |  |

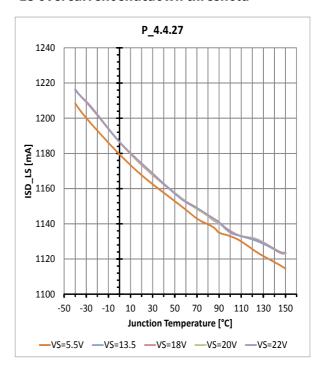

| LS Overcurrent Shutdown<br>Threshold            | I <sub>SD_LS</sub>                       | 0.9      | 1.2    | 1.5      | A        | See Figure 8                                                                                        | P_4.4.27 |  |

| Difference between shutdown and limit current   | I <sub>LIM_LS</sub> - I <sub>SD_LS</sub> | 0        | 0.6    | 1.2      | А        | $I_{\text{LIM\_LS}} \ge I_{\text{SD\_LS}}$ Figure 8                                                 | P_4.4.28 |  |

| Overcurrent Shutdown filter time                | $t_{ m dSD\_LS}$                         | 15       | 19     | 23       | μs       | 2)                                                                                                  | P_4.4.29 |  |

| Outputs OUT(1n) leakage cu                      | rrent                                    |          | 1      |          |          |                                                                                                     | 1        |  |

| HS leakage current in off state                 | $I_{\mathrm{QLHn\_NOR}}$                 | -2       | -0.5   | _        | μΑ       | V <sub>OUTn</sub> = 0V; OUT1/2:<br>EN1=GND,<br>EN2=High; OUT3:<br>EN1=High,EN2=GN<br>D              | P_4.4.32 |  |

| HS leakage current in off state                 | I <sub>QLHn_SLE</sub>                    | -2       | -0.5   | _        | μΑ       | V <sub>OUTn</sub> = 0V; EN1 =<br>EN2 =GND                                                           | P_4.4.33 |  |

| LS Leakage current in off state                 | $I_{\mathrm{QLLn\_NOR}}$                 | _        | 0.5    | 2        | μΑ       | V <sub>OUTn</sub> = V <sub>S</sub> ; OUT1/2:<br>EN1=GND,<br>EN2=High; OUT3:<br>EN1=High,EN2=GN<br>D | P_4.4.34 |  |

| LS Leakage current in off state                 | I <sub>QLLn_SLE</sub>                    | -        | 0.5    | 2        | μΑ       | $V_{\text{OUTn}} = V_{\text{S}}$ ; EN1 = EN2 = GND                                                  | P_4.4.35 |  |

| Output Switching Times. See                     | igure 9 and                              | Figure : | 10.    | *        |          |                                                                                                     |          |  |

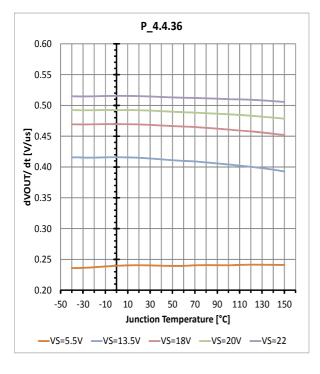

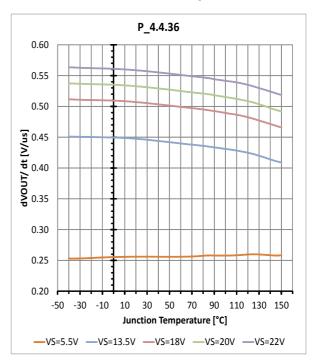

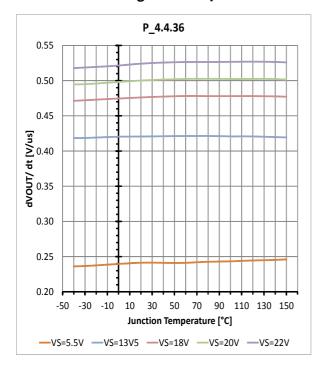

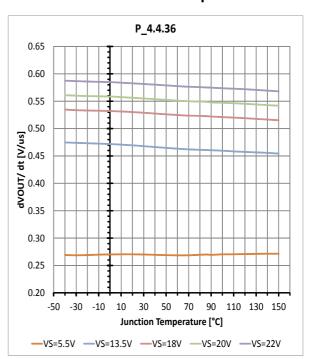

| Slew rate of high-side and low-<br>side outputs | $d_{VOUT}/dt$                            | 0.1      | 0.45   | 0.75     | V/µs     | Resistive load = $100\Omega$ ; $V_S$ =13.5V <sup>3)</sup>                                           | P_4.4.36 |  |

| Output delay time high side driver on           | $t_{dONH}$                               | 5        | 20     | 35       | μs       | Resistive load = 100Ω to GND                                                                        | P_4.4.37 |  |

| Output delay time high side driver off          | $t_{dOFFH}$                              | 15       | 45     | 75       | μs       | Resistive load = 100Ω to GND                                                                        | P_4.4.38 |  |

| Output delay time low side driver on            | $t_{ m dONL}$                            | 5        | 20     | 35       | μs       | Resistive load = 100Ω to VS                                                                         | P_4.4.39 |  |

| Output delay time low side driver off           | t <sub>dOFFL</sub>                       | 15       | 45     | 75       | μs       | Resistive load = 100Ω to VS                                                                         | P_4.4.40 |  |

| Cross current protection time, high to low      | $t_{DHL}$                                | 100      | 130    | 160      | μs       | Resistive load = $100\Omega^{2}$                                                                    | P_4.4.41 |  |

| Cross current protection time, low to high      | t <sub>DLH</sub>                         | 100      | 130    | 160      | μs       | Resistive load = $100\Omega^{2}$                                                                    | P_4.4.42 |  |

Table 5 Electrical Characteristics,  $V_S$  = 5.5 V to 20 V,  $V_{DD}$  = 3.0V to 5.5V,  $T_j$  = -40°C to +150°C, EN1= HIGH and EN2= HIGH,  $I_{OUTn}$  = 0 A; Typical values refer to  $V_{DD}$  = 5.0 V,  $V_S$  = 13.5 V and  $T_J$  = 25 °C unless otherwise specified; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified) (cont'd)

| Parameter                             | Symbol                |                       | Value                 | s                     | Unit | Note or                                   | Number    |

|---------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|------|-------------------------------------------|-----------|

|                                       |                       | Min.                  | Тур.                  | Max.                  |      | <b>Test Condition</b>                     |           |

| Input Interface: Logic Inputs E       | N1, EN2               |                       | <u> </u>              |                       |      |                                           | -         |

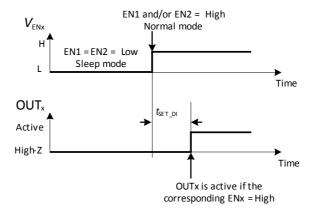

| Set up time after sleep mode          | $t_{SET\_DI}$         | _                     | _                     | 150                   | μs   | <sup>2)</sup> See <b>Figure 5</b>         | P_4.4.49  |

| High-input voltage                    | V <sub>ENH</sub>      | 0.7 * V <sub>DD</sub> | -                     | $V_{DD}$              | V    | -                                         | P_4.4.43  |

| Low-input voltage                     | V <sub>ENL</sub>      | 0                     | _                     | 0.3 * V <sub>DD</sub> | V    | -                                         | P_4.4.44  |

| Hysteresis of input voltage           | V <sub>ENHY</sub>     | _                     | 500                   | _                     | mV   | 2)                                        | P_4.4.45  |

| Pull down resistor                    | R <sub>PD_EN</sub>    | 20                    | 40                    | 70                    | kΩ   | $V_{\rm EN} = 0.2 \times V_{\rm DD}$      | P_4.4.46  |

| EF reset time                         | t <sub>EF_RESET</sub> | 250                   | _                     | -                     | ns   | $t_{\rm EF\_RESET}$ 2) Set ENx to Low for | P_4.4.121 |

| Input Interface: Logic Inputs I       | N1, IN2, IN3          | 3                     |                       |                       |      |                                           |           |

| High input voltage threshold          | V <sub>INnH</sub>     | 0.7 * V <sub>DD</sub> | _                     | $V_{\rm DD}$          | V    | -                                         | P_4.4.90  |

| Low input voltage threshold           | V <sub>INnL</sub>     | 0                     | _                     | 0.3 * V <sub>DD</sub> | V    | -                                         | P_4.4.91  |

| Hysteresis of input voltage           | $V_{\rm INnHY}$       | _                     | 500                   | -                     | mV   | 2)                                        | P_4.4.92  |

| Pull-down resistor                    | $R_{PD}$              | 20                    | 40                    | 70                    | kΩ   | _                                         | P_4.4.94  |

| Output Interface: Logic Output        | t EF                  | •                     |                       |                       | •    | •                                         | •         |

| High output voltage level             | V <sub>EFH</sub>      | V <sub>DD</sub> - 0.4 | V <sub>DD</sub> - 0.2 | $V_{\rm DD}$          | V    | I <sub>EFH</sub> = -1.6 mA                | P_4.4.88  |

| Low output voltage level              | $V_{EFL}$             | 0                     | 0.2                   | 0.4                   | V    | I <sub>EFL</sub> = 1.6 mA                 | P_4.4.95  |

| Leakage current                       | I <sub>EFLK</sub>     | -1                    | -                     | 1                     | μΑ   | 0V < V <sub>EF</sub> < 5.5V               | P_4.4.96  |

| Thermal Shutdown                      |                       |                       |                       |                       |      | '                                         |           |

| Thermal shutdown junction temperature | $T_{\rm jSD}$         | 160                   | 175                   | 190                   | °C   | See <b>Figure 11</b> <sup>2)</sup>        | P_4.4.81  |

| Thermal comparator hysteresis         | $T_{\rm jHYS}$        | _                     | 4                     | -                     | °C   | 2)                                        | P_4.4.82  |

| -                                     |                       |                       |                       | -1                    |      | 1                                         |           |

<sup>1)</sup>  $I_{S \text{ HSON}}$  does not include the load current

<sup>2)</sup> Not subject to production test, specified by design

<sup>3)</sup> Measured for 20% - 80% of  $V_{\rm S}$ .

### **Characterization results**

### 4 Characterization results

Performed on 5 devices, over operating temperature and nominal/extended supply range.

### **Typical performance characteristics**

### **Supply quiescent current**

### **Supply current**

### Logic supply quiescent current

### Logic supply current

1.0

# infineon

### **Characterization results**

### **HS static Drain-source ON-resistance**

# LS static Drain-source ON-resistance

# HS static drain-source ON-resistance VS = 13.5V and VDD = 5V

# LS static drain-source ON-resistance VS = 13.5V and VDD = 5V

### **Characterization results**

### Slew rate ON of high-side outputs

### Slew rate ON of low-side outputs

### Slew rate OFF of high-side outputs

### Slew rate OFF of low-side outputs

### **Characterization results**

### **HS** overcurrent shutdown threshold

### LS overcurrent shutdown threshold

### **Undervoltage switch ON voltage threshold**

### Undervoltage switch OFF voltage threshold

# infineon

### **Characterization results**

### Overvoltage switch ON voltage threshold

### Overvoltage switch OFF voltage threshold

### VDD Power-on-reset and VDD Power-off-reset

# infineon

### **General Description**

### 5 General Description

### 5.1 Power Supply

The TLE94003EP has two power supply inputs,  $V_{\rm S}$  and  $V_{\rm DD}$ . The half bridge outputs are supplied by  $V_{\rm S}$ , which is connected to the 12V automotive supply rail.  $V_{\rm DD}$  is used to supply the I/O buffers and internal voltage regulator of the device.

$V_{\rm S}$  and  $V_{\rm DD}$  supplies are separated so that information stored in the logic block remains intact in the event of voltage drop outs or disturbances on  $V_{\rm S}$ . The system can therefore continue to operate once  $V_{\rm S}$  has recovered, without having to resend commands to the device.

A rising edge on  $V_{\rm DD}$  crossing  $V_{\rm DD\,POR}$  triggers an internal Power-On Reset (POR) to initialize the IC at power-on. All data stored internally is deleted, and the outputs are switched off (high impedance).

An electrolytic and 100nF ceramic capacitors are recommended to be placed as close as possible to the  $V_{\rm S}$  supply pin of the device for improved EMC performance in the high and low frequency band. The electrolytic capacitor must be dimensioned to prevent the VS voltage from exceeding the absolute maximum rating. In addition, decoupling capacitors are recommended on the  $V_{\rm DD}$  supply pin.

### 5.2 Operation modes

### 5.2.1 Normal mode

The TLE94003EP enters normal mode by setting EN1 or EN2 to High. In normal mode, the charge pump is active and all output transistors can be activated or deactivated according to **Chapter 6.1**.

### 5.2.2 Sleep mode

The TLE94003EP enters sleep mode by setting the EN1 and EN2 pins to Low. The EN1 and EN2 inputs have an internal pull-down resistor.

In sleep mode, all output transistors are turned off and the logic content is reset. The current consumption is reduced to  $I_{SQ} + I_{DD\_Q}$ .

### 5.3 Reset Behaviour

The following reset triggers have been implemented in the TLE94003EP:

### **V**<sub>DD</sub> Undervoltage Reset:

The digital block will be deactivated, the logic contents cleared and the output stages are switched off if  $V_{\rm DD}$  is below the undervoltage threshold,  $V_{\rm DD\ POffR}$ . The digital block is initialized once  $V_{\rm DD}$  voltage levels is above the undervoltage threshold,  $V_{\rm DD\ POR}$ .

### Reset on EN1/2 pins:

If the EN1/2 pins are pulled Low, the logic content is reset and the device enters sleep mode.

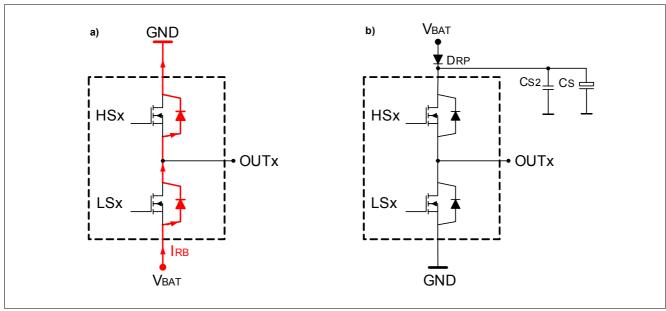

### 5.4 Reverse Polarity Protection

The TLE94003EP requires an external reverse polarity protection. During reverse polarity, the free-wheeling diodes across the half bridge output will begin to conduct, causing an undesired current flow ( $I_{RB}$ ) from ground potential to battery and excessive power dissipation across the diodes. As such, a reverse polarity protection diode is recommended (see **Figure 4**).

### **General Description**

Figure 4 Reverse Polarity Protection

# **infineon**

### **Half-Bridge Outputs**

### 6 Half-Bridge Outputs

The half-bridge outputs of the TLE94003EP are intended to drive motor loads. They consist of a total of three DMOS half-bridges, which can be driven either continuously or in PWM via INx pins. The output stages integrated circuits protect the outputs against overcurrent and overtemperature.

### 6.1 Output Stages

EN1 and EN2 inputs control the state of the device according to **Table 6**.

- When EN1 = 0 and EN2 = 0, the device enters sleep mode with low power consumption and all outputs are OFF (high impedance).

- When EN1=1, HB1 and HB2 are enabled

- When EN2=1, HB3 is enabled

Table 6 Device states

| EN1 | EN2 | HB1/2   | HB 3    | Device state                    |

|-----|-----|---------|---------|---------------------------------|

| 0   | 0   | OFF     | OFF     | Sleep mode, all outputs are OFF |

| 0   | 1   | OFF     | Enabled | Device is in normal mode        |

| 1   | 0   | Enabled | OFF     | Device is in normal mode        |

| 1   | 1   | Enabled | Enabled | Device is in normal mode        |

Note: After the transition from sleep mode to normal mode, the outputs are OFF for a duration  $t_{SET\_DI}$ . See **Figure 5**

Figure 5 Output setup time after a transition from standby to normal mode

The control inputs consist of CMOS-compatible schmitt-triggers with hysteresis. There are altogether three control inputs, i.e. IN1, IN2 and IN3 with internal pull-down resistors.

If EN1 = 0, HB1 and HB2 are OFF. If EN1 = 1, HB1 and HB2 are controlled according to Table 7

Table 7 Functional Truth Table for HB1 and HB2

| EN1 | IN1 | IN2 | HB1 | HB2 | Mode                |

|-----|-----|-----|-----|-----|---------------------|

| 0   | Х   | Х   | OFF | OFF | HB1 and HB2 are OFF |

| 1   | 0   | 0   | L   | L   | Brake Low           |

### **Half-Bridge Outputs**

Table 7 Functional Truth Table for HB1 and HB2

| EN1 | IN1 | IN2 | HB1 | HB2 | Mode                    |

|-----|-----|-----|-----|-----|-------------------------|

| 1   | 0   | 1   | L   | Н   | Motor counter-clockwise |

| 1   | 1   | 0   | Н   | L   | Motor clockwise         |

| 1   | 1   | 1   | Н   | Н   | Brake High              |

If EN2 = 0, HB3 is high impedance. If EN2 = 1, the states of HB3 is controlled according to Table 8

Table 8 Functional Truth table for HB3

| EN2 | IN3 | НВЗ |

|-----|-----|-----|

| 0   | Х   | OFF |

| 1   | 0   | L   |

| 1   | 1   | Н   |

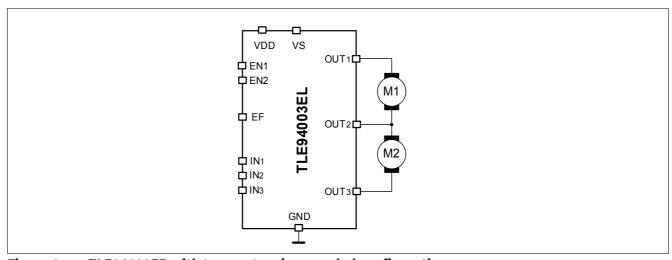

If two motors are connected in cascaded configuration (see **Figure 6**), the motors and the half-bridges behave according to **Table 9**.

Figure 6 TLE94003EP with two motors in cascaded configuration

Table 9 Functional Truth Table for HB1, HB2 and HB3 controlling two cascaded motors

| EN1 | EN2 | IN1 | IN2 | IN3 | HB1 | HB2 | HB3 | Motor1            | Motor 2           |

|-----|-----|-----|-----|-----|-----|-----|-----|-------------------|-------------------|

| 0   | 0   | Χ   | Х   | Х   | OFF | OFF | OFF | OFF               | OFF               |

| 1   | 0   | 0   | 0   | Х   | L   | L   | OFF | Brake Low         | OFF               |

| 1   | 0   | 0   | 1   | Х   | L   | Н   | OFF | Counter-clockwise | OFF               |

| 1   | 0   | 1   | 0   | Х   | Н   | L   | OFF | Clockwise         | OFF               |

| 1   | 0   | 1   | 1   | Х   | Н   | Н   | OFF | Brake High        | OFF               |

| 1   | 1   | 0   | 0   | 0   | L   | L   | L   | Brake Low         | Brake Low         |

| 1   | 1   | 0   | 0   | 1   | L   | L   | Н   | Brake Low         | Counter-clockwise |

| 1   | 1   | 0   | 1   | 0   | L   | Н   | L   | Counter-clockwise | Clockwise         |

| 1   | 1   | 0   | 1   | 1   | L   | Н   | Н   | Counter-clockwise | Brake High        |

| 1   | 1   | 1   | 0   | 0   | Н   | L   | L   | Clockwise         | Brake Low         |

### **Half-Bridge Outputs**

Table 9 Functional Truth Table for HB1, HB2 and HB3 controlling two cascaded motors

| EN1 | EN2 | IN1 | IN2 | IN3 | HB1 | HB2 | НВ3 | Motor1     | Motor 2           |

|-----|-----|-----|-----|-----|-----|-----|-----|------------|-------------------|

| 1   | 1   | 1   | 0   | 1   | Н   | L   | Н   | Clockwise  | Counter-clockwise |

| 1   | 1   | 1   | 1   | 0   | Н   | Н   | L   | Brake High | Clockwise         |

| 1   | 1   | 1   | 1   | 1   | Н   | Н   | Н   | Brake High | Brake High        |

### **Half-Bridge Outputs**

### 6.2 Diagnosis Monitoring

The EF pin (push-pull output) reports the following error conditions:

- Overcurrent (OC)

- Overtemperature (OT)

- VS overvoltage and VS undervoltage

EF reports an overcurrent event on HB1/2 only if EN1 = 1. Likewise, EF reports an overcurrent on HB3 only if EN2 = 1.

After an overcurrent event is detected on HB1/2, EF is latched to 1, until EN1 = 0.Likewise, after an overcurrent event detected on HB3, EF is latched to 1 until EN2 = 0.

EF reports overtemperature or VS overvoltage/undervoltage events if the device is in normal mode (EN1 = 1 or EN2 = 1). The error flag is latched to 1 for these fault conditions until EN1 = 0 and EN2 = 0

Table 10 Error reporting by EF pin

| EN1 | EN2 | Error reported by EF pin                         |  |

|-----|-----|--------------------------------------------------|--|

| 0   | 0   | Not applicable, the device is in sleep mode      |  |

| 1   | 0   | OC on HB1/2, OT, VS under/overvoltage            |  |

| 0   | 1   | OC on HB3, OT, VS under/overvoltage              |  |

| 1   | 1   | OC on HB1/2, OC on HB3, OT, VS under/overvoltage |  |

The table below depicts the EF behaviour:

Table 11 Error flag behaviour and reset conditions

| Fault condition           | EF          | Reset conditions                                                      |

|---------------------------|-------------|-----------------------------------------------------------------------|

| No fault                  | 0           | -                                                                     |

| Overcurrent on HB1 or HB2 | 1 (latched) | Set EN1 pin to 0 for <b>tEF_RESET</b>                                 |

| Overcurrent on HB3        | 1 (latched) | Set EN2 pin to 0 for tEF_RESET                                        |

| VS overvoltage            | 1 (latched) | $V_{\rm S} < V_{\rm OVON}$ , EN1 = 0 and EN2 = 0 for tEF_RESET        |

| VS undervoltage           | 1 (latched) | $V_{\rm S} > V_{\rm UVON}$ , EN1 = 0 and EN2 = 0 for <b>tEF_RESET</b> |

| Overtemperature           | 1 (latched) | EN1 = 0 and EN2 = 0 for tEF_RESET                                     |

### 6.3 Protection

This device has embedded protective functions which are designed to prevent the destruction of the device under fault conditions described in this section. Fault conditions are treated as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

### 6.3.1 Short Circuit of Output to Supply or Ground

The high-side switches are protected against short circuits to ground whereas the low-side switches are protected against short circuits to supply.

The high-side and low-side switches will enter into an over-current condition if the current within the switch exceeds the overcurrent shutdown detection threshold,  $I_{SD}$ . Upon detection of the  $I_{SD}$  threshold, an