Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# TLE9834QX

Microcontroller with LIN and Power Switches for Automotive Applications

# **Data Sheet**

Rev. 1.1, 2012-03-08

# **Automotive Power**

Edition 2012-03-08

Published by Infineon Technologies AG 81726 Munich, Germany © 2012 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### **Table of Contents**

# **Table of Contents**

|                 | Table of Contents                        | . 3 |

|-----------------|------------------------------------------|-----|

| I               | Summary of Features                      | . 5 |

| 1.1             | Device Types / Ordering Information      |     |

| 1.2             | Abbreviations                            | . 7 |

| <u> </u>        | General Device Information               | g   |

| -<br>2.1        | Pin Configuration                        |     |

| 2.2             | Pin Definitions and Functions            |     |

|                 |                                          |     |

| <b>s</b><br>3.1 | Functional Description                   |     |

| 3.1<br>3.1.1    | Power Management Unit (PMU)              |     |

| 3.1.1<br>3.1.2  | Voltage Regulator 5.0V (VDDP)            |     |

| 3.1.2<br>3.1.3  | Voltage Regulator 1.5V (VDDC)            |     |

| 3.1.3<br>3.2    | External Voltage Regulator 5.0V (VDDEXT) |     |

| 3.2.1           | System Control Unit - Power Modules      |     |

| 3.2.1           | System Control Unit - Digital Part       |     |

| 3.2.2<br>3.3    | XC800 Core                               |     |

| 3.4             | Memory Architecture                      |     |

| 3. <del>5</del> | Flash Memory                             |     |

| 3.6             | Watchdog Timer 1 (WDT1)                  |     |

| 3.7             | Watchdog Timer (WDT)                     |     |

| 3.8             | Interrupt System                         |     |

| 3.9             | Multiplication/Division Unit             |     |

| 3.10            | Parallel Ports                           |     |

| 3.11            | Timer 0 and Timer 1                      |     |

| 3.12            | Timer 2 and Timer 21                     |     |

| 3.13            | Timer 3                                  |     |

| 3.14            | Capture/Compare Unit 6 (CCU6)            |     |

| 3.15            | UART                                     |     |

| 3.16            | LIN Transceiver                          | 47  |

| 3.17            | High-Speed Synchronous Serial Interface  | 47  |

| 3.18            | Measurement Unit                         | 49  |

| 3.19            | Measurement Core Module (incl. ADC2)     | 51  |

| 3.20            | Analog Digital Converter (ADC1)          | 52  |

| 3.21            | High Voltage Monitor Input               | 53  |

| 3.22            | High Side Switches                       | 54  |

| 3.23            | Low Side Switches                        | 55  |

| 3.24            | PWM Generator                            | 56  |

| 3.25            | Debug System                             | 57  |

| 1               | Application Information                  | 58  |

| <b>1</b> .1     | Electric Drive Application               |     |

| 1.2             | Connection of N.C. Pins                  |     |

| 1.3             | Connection of ADCGND Pin                 |     |

| 1.4             | Connection of Exposed Pad                | 59  |

| 1.5             | Voltage Regulators-Blocking Capacitors   | 59  |

| 1.6             | Additional External Components           | 59  |

| 1.7             | ESD Tests                                | 60  |

| 5               | Electrical Characteristics               | 61  |

|                 |                                          |     |

# TLE9834QX

# **Table of Contents**

| 7       | Revision History                                          | 92  |

|---------|-----------------------------------------------------------|-----|

| 6       | Package Outlines                                          | 91  |

| 5.12.2  | Electrical Characteristics                                | 89  |

| 5.12.1  | Functional Range                                          |     |

| 5.12    | Low Side Switches                                         |     |

| 5.11.2  | Electrical Characteristics                                |     |

| 5.11.1  | Functional Range                                          |     |

| 5.11    | High Side Switches                                        |     |

| 5.10    | High-Voltage Monitor Input                                | 85  |

| 5.9.2   | Analog/Digital Converter Parameters                       |     |

| 5.9.1.2 | Electrical Characteristics                                |     |

| 5.9.1.1 | Functional Range                                          |     |

| 5.9.1   | VAREF                                                     |     |

| 5.9     | ADC - 10-Bit                                              |     |

| 5.8.4   | Temperature Sensor Module                                 |     |

| 5.8.3   | Measurement Functions Monitoring Input Voltage Attenuator |     |

| 5.8.2   | Measurement Unit (VBAT_SENSE - Supply Voltage Attenuator) |     |

| 5.8.1   | Analog Digital Converter 8-Bit                            |     |

| 5.8     | Measurement Unit                                          |     |

| 5.7     | High-Speed Synchronous Serial Interface                   |     |

| 5.6.1   | Electrical Characteristics                                |     |

| 5.6     | LIN Transceiver                                           |     |

| 5.5.2   | DC Parameters                                             |     |

| 5.5.1   | Functional Range                                          |     |

| 5.5     | Parallel Ports (GPIO)                                     |     |

| 5.4     | Flash Parameters                                          |     |

| 5.3.2   | External Clock Parameters XTAL1, XTAL2                    |     |

| 5.3.1   | Oscillators and PLL                                       |     |

| 5.3     | System Clocks                                             |     |

| 5.2.3   | VDDEXT Voltage Regulator 5.0V                             |     |

| 5.2.2   | PMU Core Supply Parameters VDDC                           |     |

| 5.2.1   | PMU I/O Supply Parameters VDDP                            |     |

| 5.2     | Power Management Unit (PMU)                               |     |

| 5.1.5   | Timing Characteristics                                    |     |

| 5.1.4   | Thermal Resistance                                        |     |

| 5.1.3   | Current Consumption                                       |     |

| 5.1.2   | Functional Range                                          |     |

| 5.1.1   | <u> </u>                                                  |     |

| - 4 4   | Absolute Maximum Ratings                                  | 0.4 |

# 1 Summary of Features

- High performance XC800 core

- compatible to standard 8051 core

- up to 40 MHz clock frequency

- two clocks per machine cycle architecture

- two data pointers

- On-chip memory

- 60 kByte + 4 kByte Flash for program code and data (4 kByte EEPROM emulation built-in)

- 512 Byte One Time Programmable Memory (OTP)

- 512 Byte 100 Time Programmable Memory (100TP)

- 256 Byte RAM, 3 kByte XRAM

- BootROM for startup firmware and Flash routines

- Core logic supply at 1.5 V

- On-chip OSC and PLL for clock generation

- Loss of clock detection with fail safe mode for power switches

- Watchdog timer (WDT) with programmable window feature for refresh operation and warning prior to overflow

- General-purpose I/O Port (GPIO) with wake-up capability

- Multiplication/division unit (MDU) for arithmetic calculation

- Software libraries to support floating point and MDU calculations

- Five 16-Bit timers Timer 0, Timer 1, Timer 2, Timer 21 and Timer 3

- Capture/compare unit for PWM signal generation (CCU6) with Timer 12 and Timer 13

- Full duplex serial interface (UART) with LIN support

- Synchronous serial channel (SSC)

- On-chip debug support via 2-wire Device Access Port (DAP)

- LIN Bootstrap loader (LIN BSL)

- LIN transceiver compliant to LIN 1.3, LIN 2.0 and LIN 2.1

- 2 x Low Side Switches with clamping capability incl. PWM functionality, e.g. as relay driver

- 2 x High Side Switches with cyclic sense option and PWM functionality, e.g. for LED or powering of switches

- 5 x High Voltage Monitor Input pins for wake-up and with cyclic sense and analog measurement option

- Measurement unit with 10 channels, 8-Bit A/D Converter (ADC2) and data post processing

- 8 channels, 10-Bit A/D Converter (including battery voltage and supply voltage measurement) (ADC1)

- Single power supply from 3.0 V to 27 V

- Low-dropout voltage regulators (LDO)

- Dedicated 5 V voltage regulator for external loads (e.g. hall sensor)

- Programmable window watchdog (WDT1) with independent on-chip clock source

- · Power saving modes

- MCU slow-down mode

- Stop Mode

- Sleep Mode

- Cyclic wake-up and cyclic sense during Stop Mode and Sleep Mode

- Power-on and undervoltage/brownout reset generator

- Overtemperature protection

- Overcurrent protection with shutdown

- Supported by a full range of development tools including C compilers, macro assembler packages, emulators, evaluation boards, HLL debugger, programming tools, software packages

- Temperature Range T<sub>.i</sub>: -40 °C up to 150 °C

- Package VQFN-48-29

- · Green package (RoHS compliant)

Data Sheet 5 Rev. 1.1, 2012-03-08

# 1.1 Device Types / Ordering Information

The TLE983x product family features devices with different peripheral modules, configurations and program memory sizes to offer cost-effective solutions for different application requirements. **Table 1** describes the TLE9834QX device configuration.

Table 1 Device Configuration

| Device Name | Max Clock<br>Frequency | High Side<br>Switches | High Voltage<br>Monitor<br>Inputs | Flash Size | Bidirectional<br>Parallel Port<br>I/O's | Operational<br>Amplifier |

|-------------|------------------------|-----------------------|-----------------------------------|------------|-----------------------------------------|--------------------------|

| TLE9834QX   | 40 MHz                 | 2                     | 5                                 | 64 kByte   | 11                                      | no                       |

Data Sheet 6 Rev. 1.1, 2012-03-08

# 1.2 Abbreviations

The following acronyms and terms are used within this document. List see in Table 2.

Table 2 Acronyms

| Acronyms | Name                                                 |  |  |  |  |

|----------|------------------------------------------------------|--|--|--|--|

| ALU      | Arithmetic Logic Unit                                |  |  |  |  |

| CCU6     | Capture Compare Unit 6                               |  |  |  |  |

| CGU      | Clock Generation Unit                                |  |  |  |  |

| CMU      | Cyclic Management Unit                               |  |  |  |  |

| DAP      | Device Access Port                                   |  |  |  |  |

| DPP      | Data Post Processing                                 |  |  |  |  |

| ECC      | Error Correction Code                                |  |  |  |  |

| EEPROM   | Electrically Erasable Programmable Read Only Memory  |  |  |  |  |

| GPIO     | General Purpose Input Output                         |  |  |  |  |

| FSR      | Full Scale Range                                     |  |  |  |  |

| ICU      | Interrupt Control Unit                               |  |  |  |  |

| IRAM     | Internal Random Access Memory - Internal Data Memory |  |  |  |  |

| LDO      | Low DropOut voltage regulator                        |  |  |  |  |

| LIN      | Local Interconnect Network                           |  |  |  |  |

| LSB      | Least Significant Bit                                |  |  |  |  |

| MCU      | Micro Controller Unit                                |  |  |  |  |

| MDU      | Multiplication Division Unit                         |  |  |  |  |

| MMC      | Monitor Mode Control                                 |  |  |  |  |

| MSB      | Most Significant Bit                                 |  |  |  |  |

| NMI      | Non Maskable Interrupt                               |  |  |  |  |

| OCDS     | On Chip Debug Support                                |  |  |  |  |

| OTP      | One Time Programmable                                |  |  |  |  |

| OSC      | Oscillator                                           |  |  |  |  |

| PC       | Program Counter                                      |  |  |  |  |

| PCU      | Power Control Unit                                   |  |  |  |  |

| PD       | Pull Down                                            |  |  |  |  |

| PGU      | Power supply Generation Unit                         |  |  |  |  |

| PLL      | Phase Locked Loop                                    |  |  |  |  |

| PMU      | Power Management Unit                                |  |  |  |  |

| PSW      | Program Status Word                                  |  |  |  |  |

| PU       | Pull Up                                              |  |  |  |  |

| PWM      | Pulse Width Modulation                               |  |  |  |  |

| RAM      | Random Access Memory                                 |  |  |  |  |

| RCU      | Reset Control Unit                                   |  |  |  |  |

| RMU      | Reset Management Unit                                |  |  |  |  |

# Table 2 Acronyms

| Acronyms | Name                                        |

|----------|---------------------------------------------|

| ROM      | Read Only Memory                            |

| SCK      | SSC Clock                                   |

| SFR      | Special Function Register                   |

| SOW      | Short Open Window (for WDT1)                |

| SPI      | Serial Peripheral Interface                 |

| SSC      | Synchronous Serial Channel                  |

| SSU      | System Status Unit                          |

| TMS      | Test Mode Select                            |

| UART     | Universal Asynchronous Receiver Transmitter |

| UDIG     | Universal Digital Controller for ADC1       |

| VBG      | Voltage reference Band Gap                  |

| WDT      | Watchdog timer                              |

| WMU      | Wake-up Management Unit                     |

| XRAM     | On-Chip eXternal Data Memory                |

| XSFR     | On-Chip eXternal Special Function Register  |

# 2 General Device Information

# 2.1 Pin Configuration

Figure 1 TLE9834QX pin configuration, VQFN-48-29 package (top view)

# 2.2 Pin Definitions and Functions

After reset, all pins are configured as input (except supply and LIN pins) with one of the following settings:

- Pull-up device enabled only (PU)

- Pull-down device enabled only (PD)

- Input with both pull-up and pull-down devices disabled (I)

- Output with output stage deactivated = high impedance state (Hi-Z)

The functions and default states of the TLE9834QX external pins are provided in the following table.

Type: indicates the pin type.

- I/O: Input or output

- I: Input only

- O: Output only

- P: Power supply

Table 3 Pin Definitions and Functions

| Symbol | Pin Number | Туре | Reset<br>State | Function                                                      |                                                                                                                                                                          |

|--------|------------|------|----------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0     |            |      |                | Alternate fun<br>DAP, CCU6,                                   | 6-Bit bidirectional general purpose I/O port. actions can be assigned as follows: Timer 0, Timer 1, Timer 2, Timer 21, UART, SSC, rrupt input and clock output.          |

| P0.0   | 20         | I/O  | I/PU           | T12HR_0<br>T2_0<br>DAP0<br>EXINT2_3<br>EXF21_0<br>RXDO        | CCU6 Timer 12 hardware run input Timer 2 input Debug Access Port 0 External interrupt input 0 Timer 21 external flag output UART transmit data output (synchronous mode) |

| P0.1   | 17         | I/O  | I/PU           | T13HR_0<br>RXD_1<br>T2EX_1<br>T21_0<br>EXINT0_3               | CCU6 Timer 13 hardware run input UART receive input Timer 2 external trigger input Timer 21 input External interrupt input 0                                             |

| P0.2   | 22         | I/O  | I/PU           | CTRAP_0<br>T21EX_0<br>EXINT1_3<br>TXD_1<br>EXF2_0             | CCU6 trap input Timer 21 external trigger input External interrupt input 1 UART transmit output Timer 2 external flag output                                             |

| P0.3   | 23         | I/O  | I/PU           | SCK_0<br>EXINT1_2<br>T0<br>CCPOS0_1<br>EXF21_2                | SSC clock input (for slave) / output (for master) External interrupt input 1 Timer 0 input CCU6 hall input 0 Timer 21 external flag output                               |

| P0.4   | 24         | I/O  | I/PU           | MTSR_0<br>CC60_0<br>T21_2<br>EXINT2_2<br>CCPOS1_1<br>CLKOUT_0 | SSC master transmit output / slave receive input CCU6 capture/compare channel 0 input/output Timer 21 input External interrupt input 2 CCU6 hall input 1 Clock output    |

Table 3

Pin Definitions and Functions (cont'd)

| Symbol | Pin Number | Туре | Reset<br>State | Function                                                    |                                                                                                                                                                                      |

|--------|------------|------|----------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0.5   | 25         | I/O  | I/PU           | MRST_0<br>EXINT0_0<br>T21EX_2<br>T1<br>CCPOS2_1<br>COUT60_0 | SSC master receive input / slave transmit output External interrupt input 0 Timer 21 external trigger input Timer 1 input CCU6 hall input 2 CCU6 capture/compare channel 0 output    |

| P1     |            |      |                | Alternate fun                                               | 5-Bit bidirectional general purpose I/O port.<br>ctions can be assigned as follows:<br>· 0, Timer 1 Timer 21, SSC, external interrupt input<br>tput.                                 |

| P1.0   | 14         | I/O  | I              | T0_1<br>CC61_0<br>SCK_1<br>EXF21_3                          | Timer 0 input CCU6 capture/compare channel 1 input/output SSC clock input (for slave) / output (for master) Timer 21 external flag output                                            |

| P1.1   | 15         | I/O  | I              | T1_1<br>MTSR_1<br>T21EX_3<br>COUT61_0                       | Timer 1 input SSC master transmit output/slave receive input Timer 21 external trigger input CCU6 capture/compare channel 1 output                                                   |

| P1.2   | 16         | I/O  | I              | EXINT0_1<br>T21_1<br>MRST_1<br>CCPOS2_2<br>COUT63_0         | External interrupt input 0 Timer 21 input SSC master receive input/slave transmit output CCU6 hall input 2 CCU6 capture/compare channel 3 output                                     |

| P1.3   | 39         | I/O  | I              | EXINT1_1<br>CC62_0<br>CCPOS0_2<br>EXF21_1                   | External interrupt input 1 CCU6 capture/compare channel 2 input/output CCU6 hall input 0 Timer 21 external flag output                                                               |

| P1.4   | 26         | I/O  | I              | EXINT2_1<br>T21EX_1<br>CCPOS1_2<br>CLKOUT_1<br>COUT62_0     | External interrupt input 2 Timer 21 external trigger input CCU6 hall input 1 Clock output CCU6 capture/compare channel 2 output                                                      |

| P2     |            |      |                | Alternate fun<br>CCU6, Timer                                | 5-Bit general purpose input-only port.<br>ctions can be assigned as follows:<br>- 0, Timer 1, Timer 21 and external interrupt input<br>d as analog inputs for the 10-Bit ADC (ADC1). |

| P2.1   | 37         | I    | I              | AN1<br>CCPOS0_0<br>EXINT1_0<br>T12HR_1<br>CC61_1            | ADC1 analog input channel 1 CCU6 hall input 0 External interrupt input 1 CCU6 Timer 12 hardware run input CCU6 capture/compare channel 1 input                                       |

Table 3

Pin Definitions and Functions (cont'd)

| Symbol        | Pin Number        | Туре     | Reset<br>State | Function                                                                                                                                                                            |  |  |

|---------------|-------------------|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P2.3          | 36                | I        | I              | AN3 ADC1 analog input channel 3 CCPOS1_0 CCU6 hall input 1 EXINT0_2 External interrupt input 0 CTRAP_1 CCU6 trap input CC60_1 CCU6 capture/compare channel 0 input                  |  |  |

| P2.4          | 32                | I        | I              | AN4 ADC1 analog input channel 4 T0_2 Timer 0 input                                                                                                                                  |  |  |

| P2.5          | 31                | I        | 1              | AN5 ADC1 analog input channel 5 T1_2 Timer 1 input                                                                                                                                  |  |  |

| P2.7          | 35                | I        | I              | AN7 ADC1 analog input channel 7 CCPOS2_0 CCU6 hall input 2 EXINT2_0 External interrupt input 2 T13HR_1 CCU6 timer 13 hardware run input CC62_1 CCU6 capture/compare channel 2 input |  |  |

| Power Supp    | ly                |          |                |                                                                                                                                                                                     |  |  |

| VS            | 47                | Р        | _              | Battery supply input                                                                                                                                                                |  |  |

| VDDP          | 44                | Р        | _              | I/O port supply (5.0 V). Do not connect external loads. For buffer and bypass capacitors.                                                                                           |  |  |

| VDDC          | 42                | Р        | -              | Core supply (1.5 V during Active Mode, 0.9 V during Stop Mode). Do not connect external loads. For buffer/bypass capacitor.                                                         |  |  |

| VDDEXT        | 45                | Р        | _              | External voltage supply output (5.0 V, 20 mA)                                                                                                                                       |  |  |

| LSGND         | 13                | Р        | _              | Low Side ground LS1, LS2                                                                                                                                                            |  |  |

| GND           | 30, 43, 19,<br>38 | Р        | -              | Core supply ground; analog supply ground                                                                                                                                            |  |  |

| ADCGND        | 33                | Р        | _              | Analog supply ground for ADC1                                                                                                                                                       |  |  |

| LINGND        | 2                 | Р        | _              | LIN ground                                                                                                                                                                          |  |  |

| Monitor Inpu  | uts               | 1        | <u>I</u>       | •                                                                                                                                                                                   |  |  |

| MON1          | 5                 | I        | I              | High Voltage Monitor Input 1                                                                                                                                                        |  |  |

| MON2          | 6                 | I        | I              | High Voltage Monitor Input 2                                                                                                                                                        |  |  |

| MON3          | 7                 | I        | I              | High Voltage Monitor Input 3                                                                                                                                                        |  |  |

| MON4          | 8                 | I        | 1              | High Voltage Monitor Input 4                                                                                                                                                        |  |  |

| MON5          | 9                 | I        | I              | High Voltage Monitor Input 5                                                                                                                                                        |  |  |

| High Side Sv  | witch / Low Side  | e Switch | Outputs        | s                                                                                                                                                                                   |  |  |

| LS1           | 11                | 0        | Hi-Z           | Low Side Switch output 1                                                                                                                                                            |  |  |

| LS2           | 12                | 0        | Hi-Z           | Low Side Switch output 2                                                                                                                                                            |  |  |

| HS1           | 3                 | 0        | Hi-Z           | High Side Switch output 1                                                                                                                                                           |  |  |

| HS2           | 4                 | 0        | Hi-Z           | High Side Switch output 2                                                                                                                                                           |  |  |

| LIN Interface | <del></del>       | 1        | II.            |                                                                                                                                                                                     |  |  |

| LIN           | 1                 | I/O      | PU             | LIN bus interface input/output                                                                                                                                                      |  |  |

|               |                   | -1       | -1             | - 1                                                                                                                                                                                 |  |  |

Table 3 Pin Definitions and Functions (cont'd)

| Symbol     | Pin Number            | Туре | Reset<br>State | Function                                            |  |  |  |  |

|------------|-----------------------|------|----------------|-----------------------------------------------------|--|--|--|--|

| Others     |                       |      |                |                                                     |  |  |  |  |

| VAREF      | 34                    | I/O  | 0              | 5V ADC1 reference voltage                           |  |  |  |  |

| XTAL1      | 27                    | I    | I              | External oscillator input                           |  |  |  |  |

| XTAL2      | 28                    | 0    | Hi-Z           | External oscillator output                          |  |  |  |  |

| TMS        | 18                    | I    | I/PD           | TMS test mode select input DAP1 Debug Access Port 1 |  |  |  |  |

| RESET      | 21                    | I/O  | I/O/PU         | Reset input, not available during Sleep Mode        |  |  |  |  |

| VBAT_SENSE | 48                    | I    | I              | Battery supply voltage sense input                  |  |  |  |  |

| N.C.       | 10, 29, 40,<br>41, 46 | _    | _              | Not connected - can be connected to GND             |  |  |  |  |

# 3 Functional Description

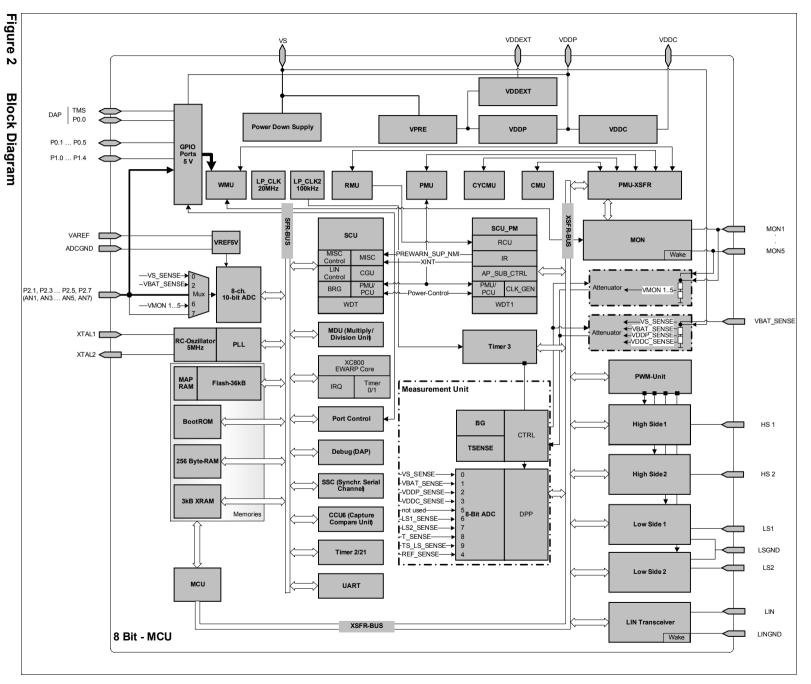

This highly integrated circuit contains analog and digital functional blocks. For system and interface control an embedded 8-Bit state-of-the-art microcontroller, compatible to the standard 8051 core with On-Chip Debug Support (OCDS), is available. For internal and external power supply purposes, on-chip low drop-out regulators are existent. An internal oscillator provides a cost effective and suitable clock in particular for LIN slave nodes. As communication interface, a LIN transceiver and several High Voltage Monitor Inputs with adjustable threshold and filters are available. Furthermore two High Side Switches (e.g. for driving LEDs or cyclic powering of switches), two Low Side Switches (e.g. for relays) and several general purpose input/outputs (GPIO) with pulse-width modulation (PWM) capabilities are available.

The Micro Controller Unit (MCU) supervision and system protection including reset feature is controlled by a programmable window watchdog. A cyclic wake-up circuit, supply voltage supervision and integrated temperature sensors are available on-chip.

All relevant modules offer power saving modes in order to support terminal 30 connected automotive applications. A wake-up from the power saving mode is possible via a LIN bus message, via the monitoring inputs, via the GPIO ports or repetitive with a programmable time period (cyclic wake-up).

The integrated circuit is available in a VQFN-48-29 package with 0.5 mm pitch and is designed to withstand the severe conditions of automotive applications.

Data Sheet 14 Rev. 1.1, 2012-03-08

# **Block Diagram**

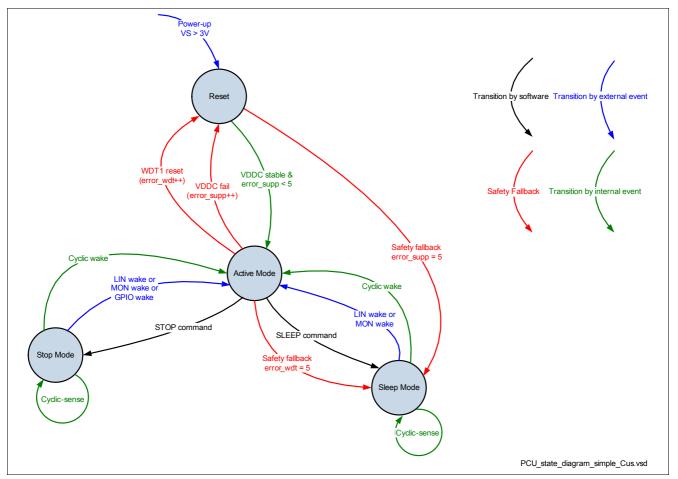

The TLE9834QX has several operational modes mainly to support low power consumption requirements. power modes and state transitions are depicted in **Figure 3** below. The low

Figure 3 Power Control State Diagram

#### **Reset Mode**

The Reset Mode is a transition mode e.g. during power-up of the device after a power-on reset. In this mode the on-chip power supplies are enabled and all other modules are initialized. Once the core supply VDDC is stable, the Active Mode is entered. In case the watchdog timer WDT1 fails for more than four times, a fail-safe transition to the Sleep Mode is done.

#### **Active Mode**

In Active Mode all modules are activated and the TLE9834QX is fully operational.

#### **Stop Mode**

The Stop Mode is one out of two low power modes. The transition to the low power modes is done by setting the respective Bits in the mode control register. In Stop Mode the embedded microcontroller is still powered allowing faster wake-up reaction times. A wake-up from this mode is possible by LIN bus activity, the High Voltage Monitor Input pins or the respective 5V GPIOs.

#### Sleep Mode

The Sleep Mode is the second low-power mode. The transition to the low-power modes is done by setting the respective Bits in the MCU mode control register. In Sleep Mode the embedded microcontroller power supply is deactivated allowing the lowest system power consumption, but the wake-up time is longer compared to the Stop Mode. A wake-up from this mode is possible by LIN bus activity or the High Voltage Monitor Input pins. A wake-up from Sleep Mode behaves similar to a power-on reset.

#### Cyclic Wake-up Mode

The cyclic wake-up mode is a special operating mode of the Sleep Mode and the Stop Mode. The transition to the cyclic wake-up mode is done by first setting the respective Bits in the mode control register followed by the SLEEP or STOP command. Additional to the cyclic wake-up behavior (wake-up after a programmable time period), the wake-up sources of the normal Stop Mode and Sleep Mode are available.

#### **Cyclic Sense Mode**

The cyclic sense mode is a special operating mode of the Sleep Mode and the Stop Mode. The transition to the cyclic sense mode is done by first setting the respective Bits in the mode control register followed by the STOP or SLEEP command. In cyclic sense mode a High Side Switch can be switched on periodically for biasing some switches for example. The wake-up condition is configurable, when the sense result of defined monitor inputs at a window of interest changed compared to the previous wake-up period or reached a defined state respectively. In this case the Active Mode is entered immediately. For cyclic sense in Stop Mode VDDEXT can be switched on periodically. Furthermore cyclic sense allows to sense dedicated GPIO port states and transitions when in Stop Mode.

The following table shows the possible power mode configurations of each major module or function respectively.

Table 4 Power mode configurations

| Module/function              | Active Mode                     | Stop Mode                              | Sleep Mode                 | Comment                        |

|------------------------------|---------------------------------|----------------------------------------|----------------------------|--------------------------------|

| VDD1V5PD                     | ON                              | ON                                     | ON                         | Power Down Supply              |

| VPRE, VDDP, VDDC             | ON                              | ON (no dynamic load)                   | OFF                        | -                              |

| VDDEXT                       | ON/OFF                          | ON (no dynamic load)/OFF cyclic ON/OFF | OFF                        | -                              |

| HSx                          | ON/OFF                          | cyclic ON/OFF                          | cyclic ON/OFF              | cyclic sense                   |

| LSx                          | ON/OFF                          | OFF                                    | OFF                        | _                              |

| PWM GEN.                     | ON/OFF                          | OFF                                    | OFF                        | _                              |

| LIN TRx                      | ON/OFF                          | wake-up only/<br>OFF                   | wake-up only/<br>OFF       | -                              |

| MON1 - MON5 (wake-up)        | n.a.                            | disabled/static/cyclic                 | disabled/static/<br>cyclic | cyclic: combined with HS=on    |

| MON1 - MON5<br>(measurement) | ON/OFF                          | OFF                                    | OFF                        | available on four channels     |

| VS sense                     | ON/OFF<br>brownout<br>detection | brownout detection                     | brownout<br>detection      | brownout detection done in PCU |

| VBAT_SENSE                   | ON/OFF                          | OFF                                    | OFF                        | -                              |

| GPIO 5V (wake-up)            | n.a.                            | disabled/static/cyclic                 | OFF                        | -                              |

| GPIO 5V (active)             | ON                              | ON                                     | OFF                        | _                              |

| WDT1                         | ON                              | OFF                                    | OFF                        | _                              |

Table 4 Power mode configurations

| Module/function   | <b>Active Mode</b>    | Stop Mode                           | Sleep Mode                          | Comment                                                                                                                  |

|-------------------|-----------------------|-------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| CYCLIC Modes      | n.a.                  | cyclic wake-up/<br>cyclic sense/OFF | cyclic wake-up/<br>cyclic sense/OFF | cyclic sense with HS,<br>VDDEXT; wake-up<br>from cyclic wake<br>needs MC for<br>entering Sleep Mode /<br>Stop Mode again |

| Measurement Unit  | ON <sup>1)</sup>      | OFF                                 | OFF                                 | _                                                                                                                        |

| MCU               | ON/slow-<br>down/HALT | STOP <sup>2)</sup>                  | OFF                                 | -                                                                                                                        |

| CLOCK GEN (MC)    | ON                    | OFF                                 | OFF                                 | _                                                                                                                        |

| LP_CLK (20 MHz)   | ON                    | OFF                                 | OFF                                 | WDT1                                                                                                                     |

| LP_CLK2 (100 kHz) | ON                    | ON                                  | ON                                  | for cyclic wake-up                                                                                                       |

<sup>1)</sup> Cannot not be switched off due to safety reasons

#### **Wake-up Source Prioritization**

All wake-up sources have the same priority. In order to handle the asynchronous nature of the wake-up sources, the first wake-up signal will initiate the wake-up sequence. Nevertheless all wake-up sources are latched in order to provide all wake-up events to the application software. The software can clear the wake-up source flags. It is ensured, that no wake-up event is lost.

As default wake-up sources, the LIN and MON inputs are activated after power-on reset only. GPIO ports as wake-up sources are disabled by default after power-on reset. The application software can reconfigure the wake-up sources according to the application needs.

# Wake-up Levels and Transitions

The wake-up can be triggered by rising, falling or both signal edges for each monitor and GPIO input individually.

<sup>2)</sup> MC PLL clock disabled, MC supply reduced to 0.9 V

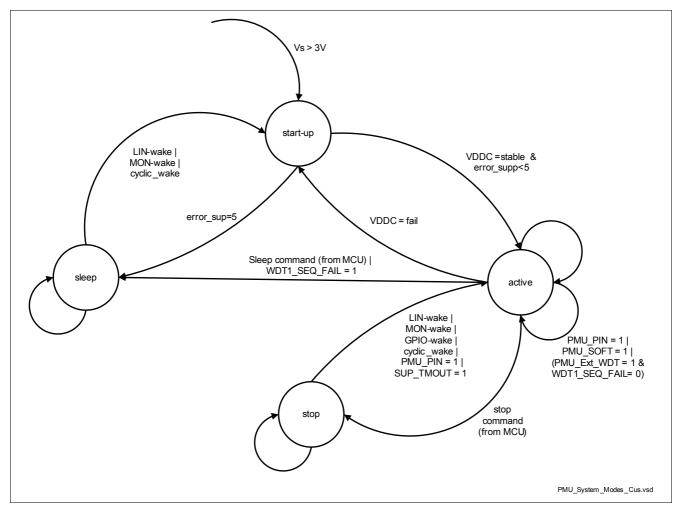

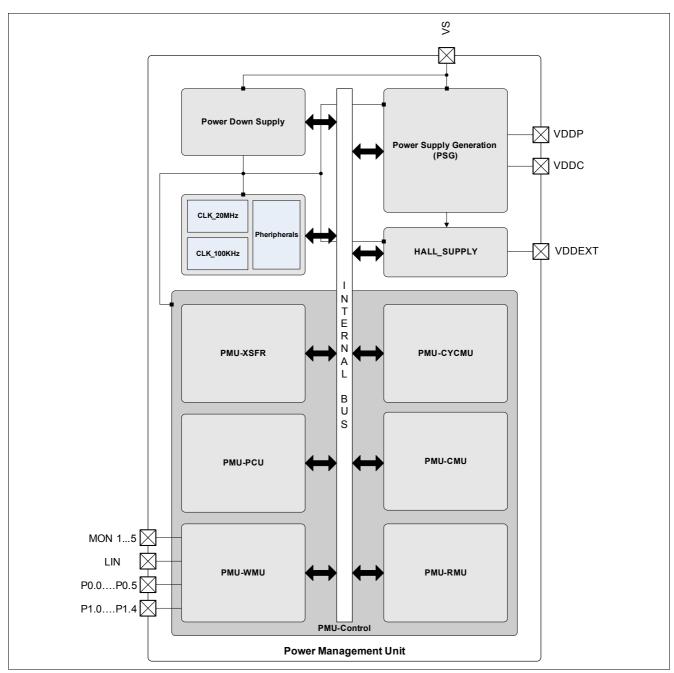

# 3.1 Power Management Unit (PMU)

The purpose of the power management unit is to ensure the fail safe behavior of embedded automotive systems. Therefore the power management unit controls all system modes including the corresponding transitions. The power management unit is responsible for generating all required voltage supplies for the embedded MCU (VDDC, VDDP) and the external sensor supply (VDDEXT). Additionally, the PMU provides well defined sequences for the system mode transitions and generates hierarchical reset priorities. The reset priorities control the reset behavior of all system functionalities, especially the reset behavior of the embedded MCU, including the test hardware. All these functions are controlled by finite state machines. The system master functionality of the PMU forces the generation of an independent logic supply (Power Down Supply) and system clock (LP\_CLK). Therefore the PMU needs a module internal logic supply and system clock which works independently of the MCU clock.

The following state diagram shows the available modes of the device.

Figure 4 Power Management Unit System Modes

Figure 5 Power Management Unit Block Diagram

Table 5 Description of PMU Submodules

| Mod.<br>Name                             | Modules                                                                                                                    | Functions                                                                                                                                                                                      |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Down<br>Supply                     | Independent Supply Voltage<br>Generation for PMU                                                                           | This supply is only dedicated to the PMU to ensure a independent operation of generated power supplies (VDDP, VDDC).                                                                           |

| LP_CLK<br>(= 20 MHz)                     | <ul><li>Clock Source for all PMU submodules</li><li>Backup Clock Source for System</li><li>Clock Source for WDT1</li></ul> | This ultra low power oscillator generates the clock for the PMU.  This clock is also used as backup clock for the system in case of PLL clock failure and as independent clock source for WDT1 |

| LP_CLK2<br>(= 100 kHz)                   | Clock Source for PMU                                                                                                       | This ultra low power oscillator generates the clock for the PMU mainly in Stop Mode and in the cyclic modes.                                                                                   |

| Peripherals                              | Peripheral blocks of PMU                                                                                                   | This blocks includes all relevant peripherals to ensure a stable and fail safe PMU startup and operation                                                                                       |

| Power Supply<br>Generation<br>Unit (PGU) | Voltage regulators for VDDP and VDDC                                                                                       | This block includes the voltage regulators for the pad supply (VDDP) and the core supply (VDDC) including all diagnosis and safety features                                                    |

| VDDEXT (Hall<br>Sensor<br>Supply)        | Voltage regulator for VDDEXT to supply external modules (e.g. Hall Sensors)                                                | This voltage regulator is a dedicated supply for external modules and can also be used for cyclic sense operations (e.g. with hall sensor)                                                     |

| PMU-XSFR                                 | All PMU relevant Extended Special Function Registers                                                                       | This module contains all PMU relevant registers, which are needed to control and monitor the PMU.                                                                                              |

| PMU-PCU                                  | Power Control Unit of the PMU                                                                                              | This block is responsible for controlling all power related actions within the PGU Module.                                                                                                     |

| PMU-WMU                                  | Wake-up Management Unit of the PMU                                                                                         | This block is responsible for controlling all wake-up related actions within the PMU Module.                                                                                                   |

| PMU-CYCMU                                | Cyclic Management Unit of the PMU                                                                                          | This block is responsible for controlling all actions within cyclic mode.                                                                                                                      |

| PMU-CMU                                  | Clock Management Unit of the PMU                                                                                           | This block is responsible for controlling all clocking actions within the PMU.                                                                                                                 |

| PMU-RMU                                  | Reset Management Unit of the PMU                                                                                           | This block is responsible for generating all system required resets.                                                                                                                           |

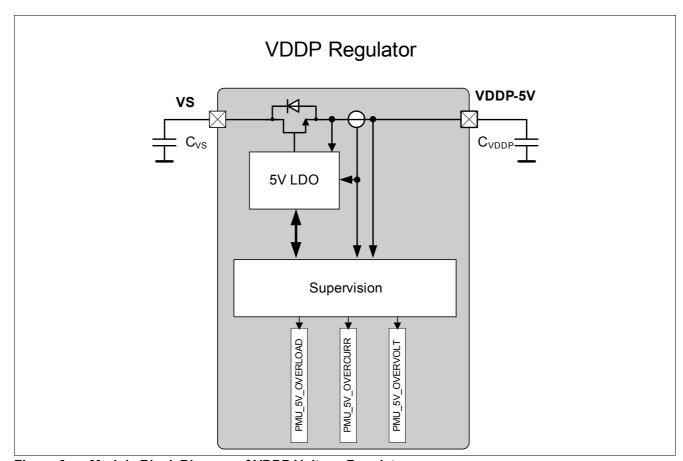

# 3.1.1 Voltage Regulator 5.0V (VDDP)

This module represents the 5 V voltage regulator, which serves as pad supply for the parallel port pins and other 5 V analog functions.

#### **Features**

- 5 V low-drop voltage regulator

- Current limitation

- Overcurrent monitoring and shutdown with MCU signalling (Interrupt)

- Overvoltage monitoring with MCU signalling (Interrupt)

- Undervoltage monitoring with MCU signalling (Interrupt)

- Preregulator for VDDC regulator

- GPIO supply

- Pull-down current source at the output for Sleep Mode (100 μA)

The output capacitor  $C_{VDDP}$  is mandatory to ensure a proper regulator functionality.

Figure 6 Module Block Diagram of VDDP Voltage Regulator

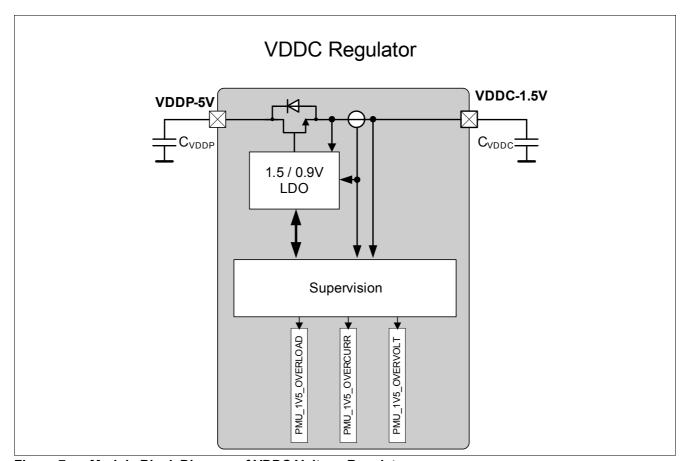

# 3.1.2 Voltage Regulator 1.5V (VDDC)

This module represents the 1.5 V voltage regulator, which serves as core supply for the 8-bit  $\mu$ C and other chip internal analog 1.5 V functions (e.g. 8 Bit ADC). To further reduce the current consumption of the 8-bit MCU during Stop Mode the output voltage is optionally reduced to 0.9 V.

#### **Features**

- 1.5 V low-drop voltage regulator

- Optional 0.9 V in Stop Mode

- · Current limitation

- Overcurrent monitoring and shutdown with MCU signalling (interrupt)

- Overvoltage monitoring with MCU signalling (interrupt)

- Undervoltage monitoring with MCU signalling (interrupt)

- Pull-down current source at the output for Sleep Mode (100 μA)

The output capacitor  $C_{VDDC}$  is mandatory to ensure a proper regulator functionality.

Figure 7 Module Block Diagram of VDDC Voltage Regulator

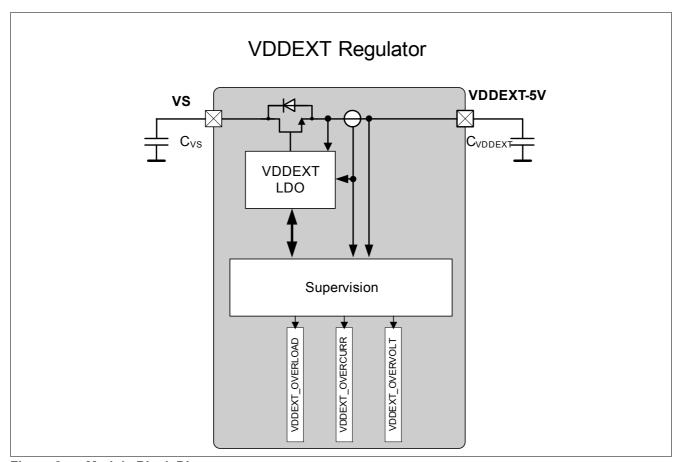

# 3.1.3 External Voltage Regulator 5.0V (VDDEXT)

The external voltage regulator provides 5 V output voltage in order to supply external circuitry like LEDs, hall sensors or potentiometers.

#### **Features**

- Switchable +5 V, 20 mA low-drop voltage regulator

- · Switch-on overcurrent blanking time in order to drive small capacitive loads

- Short circuit robust

- Overvoltage monitoring with MCU interrupt signalling

- · Undervoltage monitoring with MCU interrupt signalling

- Selectable switch-on slew-rate 0.95 V/µs max. @10 mA supply current, 10 nF capacitive load

- Pull-down current source at the output for Sleep Mode and off mode (100 μA)

- Cyclic sense option together with GPIOs

Figure 8 Module Block Diagram

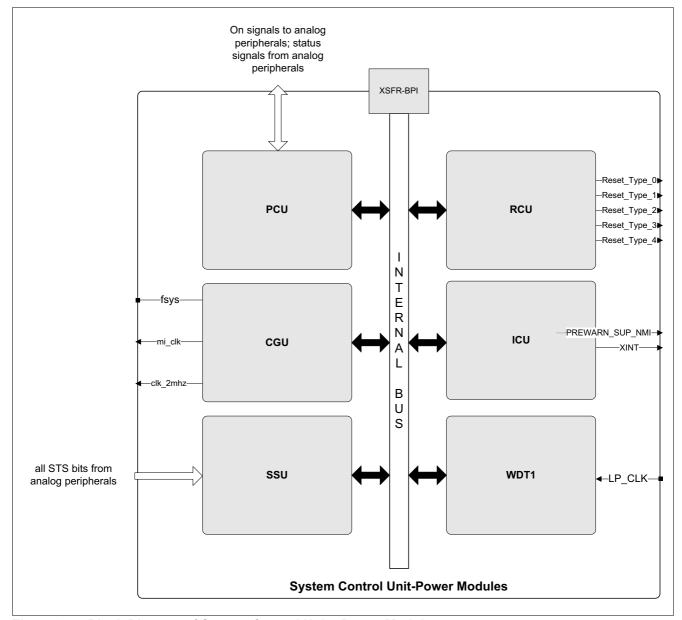

# 3.2 System Control Unit

# 3.2.1 System Control Unit - Power Modules

The System Control Unit of the power modules consists of the following sub-modules:

- Reset Control Unit (RCU): generation of all required subsystem resets

- · Clock Generation Unit (CGU): providing all required clocks to the analog subsystem

- Interrupt Control Unit (ICU): all system relevant interrupt flags and status flags

- Power Control Unit (PCU): takes over control when device enters and exits Sleep Mode and Stop Mode

- · System Status Unit (SSU): controls mode changes due to system failures

- External Watchdog (WDT1): independent system watchdog to monitor system activity

Figure 9 Block Diagram of System Control Unit - Power Modules