Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# TLE9845QX

Microcontroller with LIN and Power Switches for Automotive Applications

# **Data Sheet**

Rev. 1.0, 2016-05-06

# **Automotive Power**

#### **Table of Contents**

| <b>1</b><br>1.1                                                              | Overview     Abbreviations                                                                                                                                                                                                                     |                                        |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2                                                                            | Block Diagram                                                                                                                                                                                                                                  | 10                                     |

| <b>3</b><br>3.1<br>3.2                                                       | Device Pinout and Pin Configuration         Device Pinout         Pin Configuration                                                                                                                                                            | 11                                     |

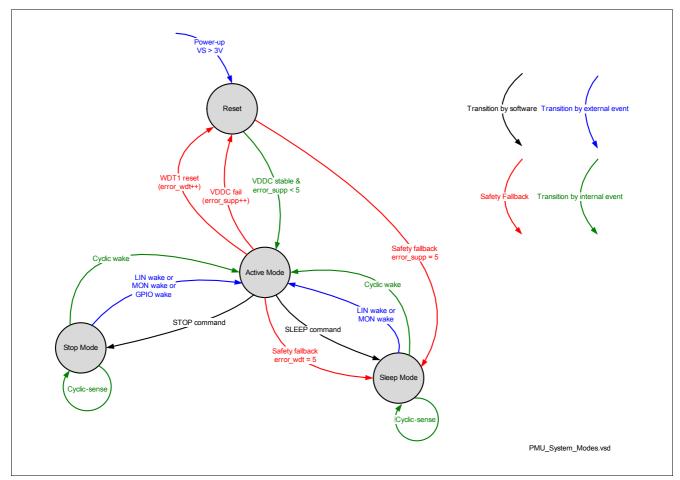

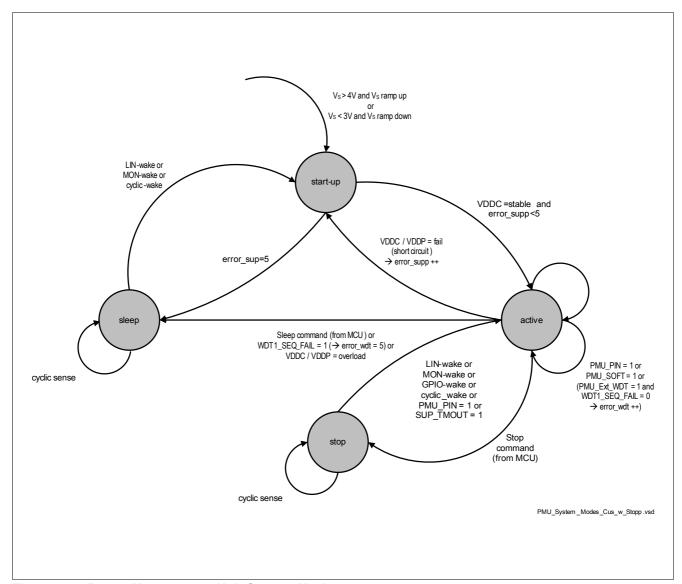

| 4                                                                            | Modes of Operation                                                                                                                                                                                                                             | 15                                     |

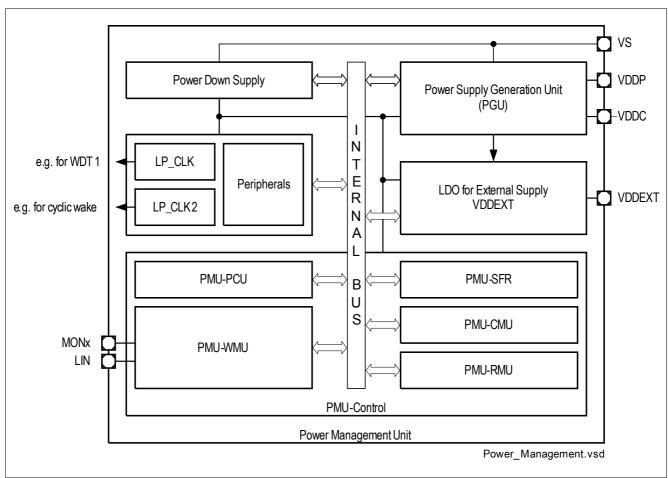

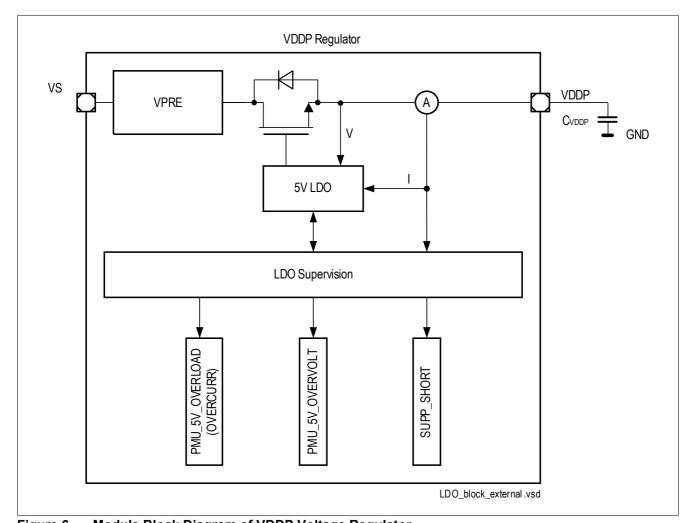

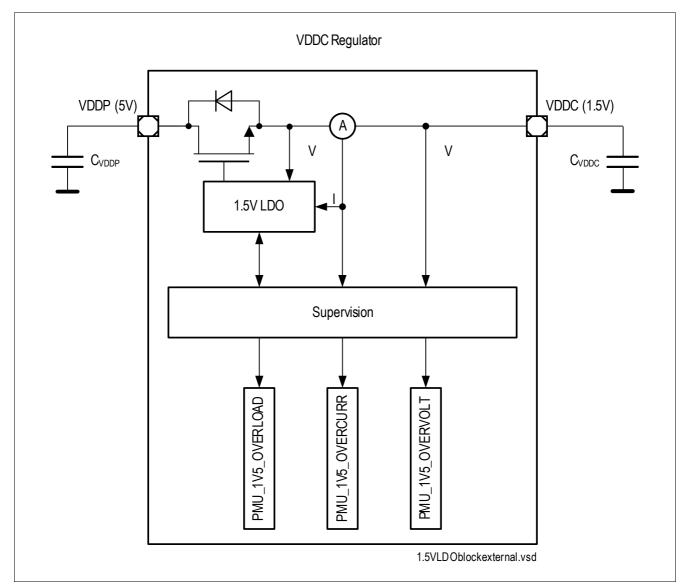

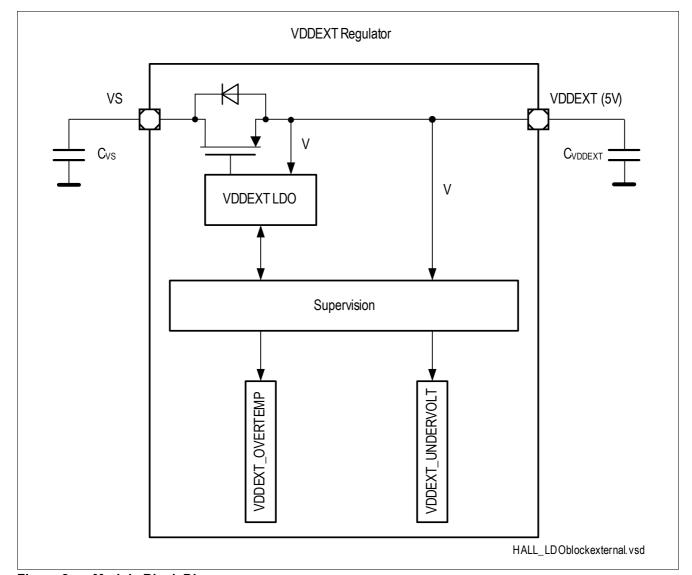

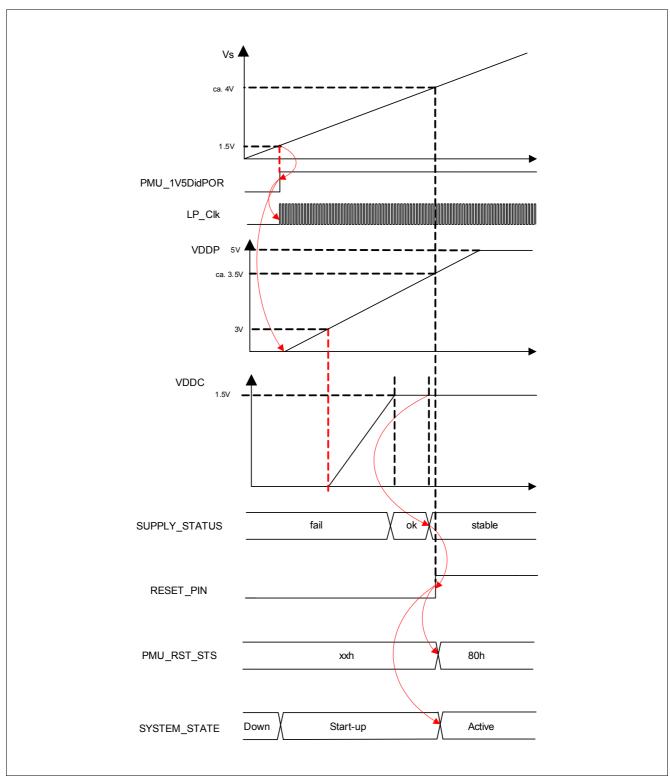

| 5<br>5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4 | Power Management Unit (PMU)  Features Introduction Block Diagram PMU Modes Overview  Power Supply Generation (PGU) Voltage Regulator 5.0V (VDDP) Voltage Regulator 1.5V (VDDC) External Voltage Regulator 5.0V (VDDEXT) Power-on Reset Concept | 18<br>19<br>21<br>22<br>22<br>23<br>24 |

| 6                                                                            | System Control Unit - Digital Modules (SCU-DM)                                                                                                                                                                                                 | 26                                     |

| 6.1<br>6.2<br>6.2.1<br>6.3<br>6.3.1<br>6.3.2<br>6.3.2.1<br>6.3.2.2           | Features Introduction Block Diagram Clock Generation Unit Low Precision Clock High Precision Oscillator Circuit (OSC_HP) External Input Clock Mode External Crystal Mode                                                                       | 26<br>27<br>29<br>29<br>29<br>29       |

| 6.3.3                                                                        | Clock Control Unit                                                                                                                                                                                                                             | 31                                     |

| <b>7</b><br>7.1<br>7.2<br>7.2.1                                              | System Control Unit - Power Modules (SCU-PM)  Description of the Power Modules System Control Unit  Introduction  Block Diagram                                                                                                                | 33<br>33                               |

| <b>8</b><br>8.1<br>8.2<br>8.2.1                                              | ARM Cortex-M0 Core  Features  Introduction  Block Diagram                                                                                                                                                                                      | 35<br>36                               |

| 9                                                                            | Address Space Organization                                                                                                                                                                                                                     | 37                                     |

| <b>10</b><br>10.1<br>10.2<br>10.2.1                                          | Memory Control Unit Features Introduction Block Diagram                                                                                                                                                                                        | 39<br>39                               |

| <b>11</b><br>11.1<br>11.1.1                                                  | NVM Module (Flash Memory)  Definitions  General Definitions                                                                                                                                                                                    | 42                                     |

| <b>12</b><br>12.1                                                            | Interrupt System                                                                                                                                                                                                                               |                                        |

| 12.2<br>12.2.1                                               | Introduction                                                                                                                               |                                        |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1 <b>3</b><br>13.1<br>13.2                                   | Watchdog Timer (WDT1) Features Introduction                                                                                                | 47                                     |

| 14                                                           | GPIO Ports and Peripheral I/O                                                                                                              |                                        |

| 14.1<br>14.2                                                 | Features                                                                                                                                   |                                        |

| 14.2.1<br>14.2.2                                             | Port 0 and Port 1                                                                                                                          | 50                                     |

| 14.3                                                         | TLE9845QX Port Implementation Details                                                                                                      | 52                                     |

| 14.3.1<br>14.3.1.1                                           | Port 0 Port 0 Functions                                                                                                                    | 52                                     |

| 14.3.2<br>14.3.2.1                                           | Port 1                                                                                                                                     |                                        |

| 14.3.3<br>14.3.3.1                                           | Port 2  Port 2 Functions                                                                                                                   |                                        |

| 15                                                           | General Purpose Timer Units (GPT12)                                                                                                        |                                        |

| 15.1<br>15.1.1                                               | Features Block GPT1 Features Block GPT1                                                                                                    |                                        |

| 15.1.2<br>15.2                                               | Features Block GPT2                                                                                                                        |                                        |

| 15.2.1<br>15.2.2                                             | Block Diagram GPT1                                                                                                                         | 60                                     |

| 16                                                           | Timer2 and Timer21                                                                                                                         | 62                                     |

| 16.1<br>16.2                                                 | Features                                                                                                                                   |                                        |

| 16.2.1                                                       | Timer2 and Timer21 Modes Overview                                                                                                          |                                        |

| <b>17</b><br>17.1                                            | Capture/Compare Unit 6 (CCU6)                                                                                                              | 64                                     |

| 17.2<br>17.2.1                                               | Introduction                                                                                                                               |                                        |

| <b>18</b><br>18.1                                            | UART1/UART2 Features                                                                                                                       |                                        |

| 18.2                                                         | Introduction                                                                                                                               | 66                                     |

| 18.2.1<br>18.3                                               | Block Diagram                                                                                                                              |                                        |

| 10.3                                                         | Of the modes                                                                                                                               | 67                                     |

| 19                                                           | LIN Transceiver                                                                                                                            | 68                                     |

| 1 <b>9</b><br>19.1<br>19.2                                   | LIN Transceiver Features Introduction                                                                                                      | 68<br>68<br>68                         |

| <b>19</b><br>19.1                                            | LIN Transceiver                                                                                                                            | 68<br>68<br>68<br>69                   |

| 19.1<br>19.2<br>19.2.1<br>20                                 | LIN Transceiver  Features Introduction Block Diagram  High-Speed Synchronous Serial Interface SSC1/SSC2 Features                           | 68<br>68<br>69<br>70<br>70             |

| 19<br>19.1<br>19.2<br>19.2.1<br>20<br>20.1<br>20.2<br>20.2.1 | LIN Transceiver Features Introduction Block Diagram  High-Speed Synchronous Serial Interface SSC1/SSC2 Features Introduction Block Diagram | 68<br>68<br>69<br>70<br>70<br>71       |

| 19<br>19.1<br>19.2<br>19.2.1<br>20<br>20.1<br>20.2           | LIN Transceiver  Features Introduction Block Diagram  High-Speed Synchronous Serial Interface SSC1/SSC2 Features Introduction              | 68<br>68<br>69<br>70<br>70<br>71<br>72 |

| 21.2.1         | Block Diagram                                                                    | 72 |

|----------------|----------------------------------------------------------------------------------|----|

| 22             | Measurement Core Module (incl. ADC2)                                             | 74 |

| 22.1           | Features                                                                         |    |

| 22.2           | Introduction                                                                     |    |

| 22.2.1         | Block Diagram                                                                    |    |

| 23             | 10-Bit Analog Digital Converter (ADC1)                                           |    |

| -              | · · ·                                                                            |    |

| 23.1<br>23.2   | Features                                                                         |    |

| 23.2<br>23.2.1 | Block Diagram                                                                    |    |

|                | · ·                                                                              |    |

| 24             | High-Voltage Monitor Input                                                       |    |

| 24.1           | Features                                                                         |    |

| 24.2           | Introduction                                                                     |    |

| 24.2.1         | Block Diagram                                                                    | 77 |

| 25             | High-Side Switch                                                                 | 78 |

| 25.1           | Features                                                                         | 78 |

| 25.2           | Introduction                                                                     | 79 |

| 25.2.1         | Block Diagram                                                                    | 79 |

| 25.2.2         | General                                                                          | 79 |

| 26             | Low-Side Switch                                                                  | ΩN |

| 2 <b>6</b> .1  | Features                                                                         |    |

| 26.2           | Functional Description                                                           |    |

|                | ·                                                                                |    |

| 27             | Application Information                                                          |    |

| 27.1           | Relay Window Lift Application diagram                                            |    |

| 27.2           | Motor Drive with P/N-channel Power MOSFET Half Bridge Application                |    |

| 27.2.1         | P/N-channel Half Bridge Application diagram                                      |    |

| 27.2.2         | Functional description                                                           |    |

| 27.2.2.1       | Gate Driver Stages                                                               |    |

| 27.2.2.2       | PWM operation                                                                    |    |

| 27.2.2.3       | MOSFET protection with integrated Differential Units for drain-source-monitoring |    |

| 27.3           | Connection of N.C.                                                               |    |

| 27.4           | Connection of unused pins                                                        |    |

| 27.5           | Connection of P0.2 for SWD debug mode                                            |    |

| 27.6           | Connection of TMS                                                                |    |

| 27.7           | ESD Immunity According to IEC61000-4-2                                           |    |

| 28             | Electrical Characteristics                                                       | 87 |

| 28.1           | General Characteristics                                                          | 87 |

| 28.1.1         | Absolute Maximum Ratings                                                         |    |

| 28.1.2         | Functional Range                                                                 |    |

| 28.1.3         | Current Consumption                                                              |    |

| 28.1.4         | Thermal Resistance                                                               |    |

| 28.1.5         | Timing Characteristics                                                           |    |

| 28.2           | Power Management Unit (PMU)                                                      |    |

| 28.2.1         | PMU Input Voltage VS                                                             |    |

| 28.2.2         | PMU I/O Supply Parameters VDDP                                                   |    |

| 28.2.3         | PMU Core Supply Parameters VDDC                                                  |    |

| 28.2.4         | VDDEXT Voltage Regulator 5.0V                                                    |    |

| 28.2.5         | VPRE Voltage Regulator (PMU Subblock) Parameters                                 |    |

| 28.2.5.1       | Load Sharing of VPRE Regulator                                                   | 98 |

## TLE9845QX

| 28.2.6   | Power Down Voltage Regulator (PMU Subblock) Parameters |     |

|----------|--------------------------------------------------------|-----|

| 28.3     | System Clocks                                          |     |

| 28.3.1   | Electrical Characteristics Oscillators and PLL         | 100 |

| 28.3.2   | External Clock Parameters XTAL1, XTAL2                 | 101 |

| 28.4     | Flash Parameters                                       | 103 |

| 28.4.1   | Flash Characteristics                                  | 103 |

| 28.5     | Parallel Ports (GPIO)                                  | 104 |

| 28.5.1   | Description of Keep and Force Current                  | 104 |

| 28.5.2   | DC Parameters Port 0, Port 1, TMS, Reset               | 105 |

| 28.5.3   | DC Parameters Port 2                                   | 107 |

| 28.5.4   | Operating Conditions                                   | 108 |

| 28.6     | LIN Transceiver                                        | 110 |

| 28.6.1   | Electrical Characteristics                             | 110 |

| 28.7     | High-Speed Synchronous Serial Interface                | 114 |

| 28.7.1   | SSC Timing                                             | 114 |

| 28.8     | Measurement Unit                                       | 115 |

| 28.8.1   | Electrical Characteristics                             | 115 |

| 28.8.2   | Central Temperature Sensor Module                      | 118 |

| 28.8.2.1 | Electrical Characteristics                             | 118 |

| 28.9     | ADC1 (10-Bit)                                          | 119 |

| 28.9.1   | ADC1 Reference Voltage                                 | 119 |

| 28.9.2   | Electrical Characteristics ADC1 (10-Bit)               | 119 |

| 28.10    | High-Voltage Monitoring Input                          | 121 |

| 28.10.1  | Electrical Characteristics                             | 121 |

| 28.11    | High Side Switches                                     | 122 |

| 28.11.1  | Electrical Characteristics                             | 122 |

| 28.12    | Low Side Switches                                      | 125 |

| 28.12.1  | Electrical Characteristics                             | 125 |

| 29       | Package Outlines                                       | 127 |

| 30       | Revision History                                       | 128 |

# Microcontroller with LIN and Power Switches for Automotive Applications

#### TLE9845QX

#### 1 Overview

#### **Summary of Features**

- 32-bit ARM Cortex-M0 Core

- up to 40 MHz clock frequency

- one clock per machine cycle architecture

- single cycle multiplier

- On-chip memory

- 48 KB Flash (including EEPROM)

- 4 KB EEPROM (emulated in Flash)

- 768 bytes 100 Time Programmable Memory (100TP)

- 4 KB RAM

- Boot ROM for startup firmware and Flash routines

- On-chip OSC

- 2 Low-Side Switches incl. PWM functionality, can be used e.g. as relay driver

- 2 High-Side Switches with cyclic sense option and PWM functionality, e.g. for supplying LEDs or switch panels (min. 150 mA)

- 5 High Voltage Monitor Input pins for wake-up and with cyclic sense with analog measurement option

- 10 General-purpose I/O Ports (GPIO)

- · 6 Analog input Ports

- 10-Bit A/D Converter with 6 analog inputs + VBAT\_SENSE + VS + 5 high voltage monitoring inputs

- 8-Bit A/D Converter with 7 inputs for voltage and temperature supervision

- · Measurement unit with 12 channels together with the onboard 10-Bit A/D converter and data post processing

- 16-Bit timers GPT12, Timer 2 and Timer 21

- Capture/compare unit for PWM signal generation (CCU6)

- 2 full duplex serial interfaces (UART1, UART2), UART1 with LIN support

- 2 synchronous serial channels (SSC1, SSC2)

- Usage as P/N-channel Power MOSFET driver (Half Bridge Application) supported by four additional differential channels in ADC1

- · On-chip debug support via 2-wire SWD

- LIN Bootstrap loader to program the Flash via LIN (LIN BSL)

- 1 LIN 2.2 transceiver

- Single power supply from 3.0 V to 28 V

- Low-dropout voltage regulators (LDO)

- 5 V voltage supply VDDEXT for external loads (e.g. Hall-sensor)

- Core logic supply at 1.5 V

- Programmable window watchdog (WDT1) with independent on-chip clock source

| Туре      | Package    | Marking   |

|-----------|------------|-----------|

| TLE9845QX | VQFN-48-31 | TLE9845QX |

**VQFN-48-31**

Overview

- · Power saving modes:

- Micro Controller Unit slow-down mode

- Sleep Mode with cyclic sense option

- Cyclic wake-up during Sleep Mode

- Stop Mode with cyclic sense option

- Power-on and undervoltage/brownout reset generator

- Overtemperature protection

- · Short circuit protection for all voltage regulators and actuators (High Side, Low Side)

- Loss of clock detection with fail safe mode for power switches

- Temperature Range T<sub>J</sub>: -40 °C up to 150 °C

- Package VQFN-48-31 with LTI feature

- Green package (RoHS compliant)

- AEC Qualified

Overview

## 1.1 Abbreviations

The following acronyms and terms are used within this document. List see in Table 1.

Table 1 Acronyms

| AHB ARM Advanced High-Performance Bus  CCU6 Capture Compare Unit 6  CGU Clock Generation Unit  CLKMU Clock Management Unit  CMU Cyclic Management Unit  DPP Data Post Processing  ECC Error Correction Code  EEPROM Electrically Erasable Programmable Read Only Memory  GPIO General Purpose Input Output  HV High Voltage  ICU Interrupt Control Unit  LDO Low DropOut voltage regulator  LIN Local Interconnect Network  LSB Least Significant Bit  LTI Lead Tip Inspection  LV Low Voltage  MCU Microcontroller Unit  MF Measurement Functions  MPU Memory Protection Unit  MRST Master Receive / Slave Transmit, corresponds to MISO in SPI  MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MIU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Supply Generation Unit  PD Pull Down  PGU Power supply Generation Unit  PPB Private Peripheral Bus                                                                                                                                                                 | Acronyms | Name                                                        |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------|--|--|--|--|--|

| CGU Clock Generation Unit CLKMU Clock Management Unit CMU Cyclic Management Unit DPP Data Post Processing ECC Error Correction Code EEPROM Electrically Erasable Programmable Read Only Memory GPIO General Purpose Input Output HV High Voltage ICU Interrupt Control Unit LDO Low DropOut voltage regulator LIN Local Interconnect Network LSB Least Significant Bit LTI Lead Tip Inspection LV Low Voltage MCU Microcontroller Unit MF Measurement Functions MPU Memory Protection Unit MRST Master Receive / Slave Transmit, corresponds to MISO in SPI MSB Most Significant Bit MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI MU Measurement Unit NMI Non Maskable Interrupt NVIC Nested Vector Interrupt OTP One Time Programmable PBA Peripheral Bridge PC Program Counter PCU Power Control Unit PLL Phase Locked Loop PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                 | AHB      | ARM Advanced High-Performance Bus                           |  |  |  |  |  |

| CLKMU Clock Management Unit  CMU Cyclic Management Unit  DPP Data Post Processing  ECC Error Correction Code  EEPROM Electrically Erasable Programmable Read Only Memory  GPIO General Purpose Input Output  HV High Voltage  ICU Interrupt Control Unit  LDO Low DropOut voltage regulator  LIN Local Interconnect Network  LSB Least Significant Bit  LTI Lead Tip Inspection  LV Low Voltage  MCU Microcontroller Unit  MF Measurement Functions  MPU Memory Protection Unit  MRST Master Receive / Slave Transmit, corresponds to MISO in SPI  MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PLL Phase Locked Loop  PMU Power Management Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                   | CCU6     | Capture Compare Unit 6                                      |  |  |  |  |  |

| CMU Cyclic Management Unit DPP Data Post Processing ECC Error Correction Code EEPROM Electrically Erasable Programmable Read Only Memory GPIO General Purpose Input Output HV High Voltage ICU Interrupt Control Unit LDO Low DropOut voltage regulator LIN Local Interconnect Network LSB Least Significant Bit LTI Lead Tip Inspection LV Low Voltage MCU Microcontroller Unit MF Measurement Functions MPU Memory Protection Unit MRST Master Receive / Slave Transmit, corresponds to MISO in SPI MSB Most Significant Bit MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI MU Measurement Unit NMI Non Maskable Interrupt NVIC Nested Vector Interrupt Controller OSC Oscillator OTP One Time Programmable PBA Peripheral Bridge PC Program Counter PCU Power Control Unit PLL Phase Locked Loop PMU Power Management Unit PLL Phase Locked Loop                                                                                                                                                                                                                                                                                                                                       | CGU      | Clock Generation Unit                                       |  |  |  |  |  |

| DPP Data Post Processing  ECC Error Correction Code  EEPROM Electrically Erasable Programmable Read Only Memory  GPIO General Purpose Input Output  HV High Voltage  ICU Interrupt Control Unit  LDO Low DropOut voltage regulator  LIN Local Interconnect Network  LSB Least Significant Bit  LTI Lead Tip Inspection  LV Low Voltage  MCU Microcontroller Unit  MF Measurement Functions  MPU Memory Protection Unit  MRST Master Receive / Slave Transmit, corresponds to MISO in SPI  MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit  PD Pull Down  PGU Power Management Unit  PD Power Management Unit | CLKMU    | Clock Management Unit                                       |  |  |  |  |  |

| ECC Error Correction Code  EEPROM Electrically Erasable Programmable Read Only Memory  GPIO General Purpose Input Output  HV High Voltage  ICU Interrupt Control Unit  LDO Low DropOut voltage regulator  LIN Local Interconnect Network  LSB Least Significant Bit  LTI Lead Tip Inspection  LV Low Voltage  MCU Microcontroller Unit  MF Measurement Functions  MPU Memory Protection Unit  MRST Master Receive / Slave Transmit, corresponds to MISO in SPI  MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit  PD Power Management Unit                                                                                                                        | CMU      | Cyclic Management Unit                                      |  |  |  |  |  |

| EEPROM Electrically Erasable Programmable Read Only Memory GPIO General Purpose Input Output HV High Voltage ICU Interrupt Control Unit LDO Low DropOut voltage regulator LIN Local Interconnect Network LSB Least Significant Bit LTI Lead Tip Inspection LV Low Voltage MCU Microcontroller Unit MF Measurement Functions MPU Memory Protection Unit MRST Master Receive / Slave Transmit, corresponds to MISO in SPI MSB Most Significant Bit MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI MU Measurement Unit NMI Non Maskable Interrupt NVIC Nested Vector Interrupt Controller OSC Oscillator OTP One Time Programmable PBA Peripheral Bridge PC Program Counter PCU Power Supply Generation Unit PD Pull Down PGU Power Management Unit PMU Power Management Unit PD Pusse Locked Loop PMU Power Management Unit PD Power Management Unit PD Power Management Unit PD Power Management Unit PD Power Management Unit                                                                                                                                                                                                                                                             | DPP      | Data Post Processing                                        |  |  |  |  |  |

| GPIO General Purpose Input Output  HV High Voltage  ICU Interrupt Control Unit  LDO Low DropOut voltage regulator  LIN Local Interconnect Network  LSB Least Significant Bit  LTI Lead Tip Inspection  LV Low Voltage  MCU Microcontroller Unit  MF Measurement Functions  MPU Memory Protection Unit  MRST Master Receive / Slave Transmit, corresponds to MISO in SPI  MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                   | ECC      | Error Correction Code                                       |  |  |  |  |  |

| HV High Voltage ICU Interrupt Control Unit LDO Low DropOut voltage regulator LIN Local Interconnect Network LSB Least Significant Bit LTI Lead Tip Inspection LV Low Voltage MCU Microcontroller Unit MF Measurement Functions MPU Memory Protection Unit MRST Master Receive / Slave Transmit, corresponds to MISO in SPI MSB Most Significant Bit MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI MU Measurement Unit NMI Non Maskable Interrupt NVIC Nested Vector Interrupt Controller OSC Oscillator OTP One Time Programmable PBA Peripheral Bridge PC Program Counter PCU Power Control Unit PD Pull Down PGU Power Management Unit PLL Phase Locked Loop PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EEPROM   | Electrically Erasable Programmable Read Only Memory         |  |  |  |  |  |

| ICU Interrupt Control Unit  LDO Low DropOut voltage regulator  LIN Local Interconnect Network  LSB Least Significant Bit  LTI Lead Tip Inspection  LV Low Voltage  MCU Microcontroller Unit  MF Measurement Functions  MPU Memory Protection Unit  MRST Master Receive / Slave Transmit, corresponds to MISO in SPI  MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PLL Phase Locked Loop  PMU Power Management Unit  PD Pull Down  PGU Power Management Unit  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GPIO     | General Purpose Input Output                                |  |  |  |  |  |

| LDO Low DropOut voltage regulator  LIN Local Interconnect Network  LSB Least Significant Bit  LTI Lead Tip Inspection  LV Low Voltage  MCU Microcontroller Unit  MF Measurement Functions  MPU Memory Protection Unit  MRST Master Receive / Slave Transmit, corresponds to MISO in SPI  MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | HV       | High Voltage                                                |  |  |  |  |  |

| LIN Local Interconnect Network  LSB Least Significant Bit  LTI Lead Tip Inspection  LV Low Voltage  MCU Microcontroller Unit  MF Measurement Functions  MPU Memory Protection Unit  MRST Master Receive / Slave Transmit, corresponds to MISO in SPI  MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ICU      | Interrupt Control Unit                                      |  |  |  |  |  |

| LSB Least Significant Bit  LTI Lead Tip Inspection  LV Low Voltage  MCU Microcontroller Unit  MF Measurement Functions  MPU Memory Protection Unit  MRST Master Receive / Slave Transmit, corresponds to MISO in SPI  MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LDO      | Low DropOut voltage regulator                               |  |  |  |  |  |

| LTI Lead Tip Inspection  LV Low Voltage  MCU Microcontroller Unit  MF Measurement Functions  MPU Memory Protection Unit  MRST Master Receive / Slave Transmit, corresponds to MISO in SPI  MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | LIN      | Local Interconnect Network                                  |  |  |  |  |  |

| LV Low Voltage  MCU Microcontroller Unit  MF Measurement Functions  MPU Memory Protection Unit  MRST Master Receive / Slave Transmit, corresponds to MISO in SPI  MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LSB      | Least Significant Bit                                       |  |  |  |  |  |

| MCU Microcontroller Unit  MF Measurement Functions  MPU Memory Protection Unit  MRST Master Receive / Slave Transmit, corresponds to MISO in SPI  MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LTI      | Lead Tip Inspection                                         |  |  |  |  |  |

| MF Measurement Functions MPU Memory Protection Unit MRST Master Receive / Slave Transmit, corresponds to MISO in SPI MSB Most Significant Bit MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI MU Measurement Unit NMI Non Maskable Interrupt NVIC Nested Vector Interrupt Controller OSC Oscillator OTP One Time Programmable PBA Peripheral Bridge PC Program Counter PCU Power Control Unit PD Pull Down PGU Power supply Generation Unit PLL Phase Locked Loop PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LV       | Low Voltage                                                 |  |  |  |  |  |

| MPU Memory Protection Unit  MRST Master Receive / Slave Transmit, corresponds to MISO in SPI  MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MCU      | Microcontroller Unit                                        |  |  |  |  |  |

| MRST Master Receive / Slave Transmit, corresponds to MISO in SPI MSB Most Significant Bit MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI MU Measurement Unit NMI Non Maskable Interrupt NVIC Nested Vector Interrupt Controller OSC Oscillator OTP One Time Programmable PBA Peripheral Bridge PC Program Counter PCU Power Control Unit PD Pull Down PGU Power supply Generation Unit PLL Phase Locked Loop PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MF       | Measurement Functions                                       |  |  |  |  |  |

| MSB Most Significant Bit  MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MPU      | Memory Protection Unit                                      |  |  |  |  |  |

| MTSR Master Transmit / Slave Receive, corresponds to MOSI in SPI  MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MRST     | Master Receive / Slave Transmit, corresponds to MISO in SPI |  |  |  |  |  |

| MU Measurement Unit  NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MSB      | Most Significant Bit                                        |  |  |  |  |  |

| NMI Non Maskable Interrupt  NVIC Nested Vector Interrupt Controller  OSC Oscillator  OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MTSR     | Master Transmit / Slave Receive, corresponds to MOSI in SPI |  |  |  |  |  |

| NVIC  Nested Vector Interrupt Controller  OSC  Oscillator  OTP  One Time Programmable  PBA  Peripheral Bridge  PC  Program Counter  PCU  Power Control Unit  PD  Pull Down  PGU  Power supply Generation Unit  PLL  Phase Locked Loop  PMU  Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MU       | Measurement Unit                                            |  |  |  |  |  |

| OSC OTP One Time Programmable PBA Peripheral Bridge PC Program Counter PCU Power Control Unit PD Pull Down PGU Power supply Generation Unit PLL Phase Locked Loop PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NMI      | Non Maskable Interrupt                                      |  |  |  |  |  |

| OTP One Time Programmable  PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | NVIC     | Nested Vector Interrupt Controller                          |  |  |  |  |  |

| PBA Peripheral Bridge  PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OSC      | Oscillator                                                  |  |  |  |  |  |

| PC Program Counter  PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OTP      | One Time Programmable                                       |  |  |  |  |  |

| PCU Power Control Unit  PD Pull Down  PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PBA      | Peripheral Bridge                                           |  |  |  |  |  |

| PD Pull Down PGU Power supply Generation Unit PLL Phase Locked Loop PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PC       | Program Counter                                             |  |  |  |  |  |

| PGU Power supply Generation Unit  PLL Phase Locked Loop  PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PCU      | Power Control Unit                                          |  |  |  |  |  |

| PLL Phase Locked Loop PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PD       | Pull Down                                                   |  |  |  |  |  |

| PMU Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PGU      | Power supply Generation Unit                                |  |  |  |  |  |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PLL      | Phase Locked Loop                                           |  |  |  |  |  |

| PPB Private Peripheral Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PMU      | Power Management Unit                                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PPB      | Private Peripheral Bus                                      |  |  |  |  |  |

Overview

## Table 1 Acronyms

| Acronyms | Name                                                           |

|----------|----------------------------------------------------------------|

| PSW      | Program Status Word                                            |

| PU       | Pull Up                                                        |

| PWM      | Pulse Width Modulation                                         |

| RAM      | Random Access Memory                                           |

| RCU      | Reset Control Unit                                             |

| rfu      | reserved for future use                                        |

| RMU      | Reset Management Unit                                          |

| ROM      | Read Only Memory                                               |

| SCU      | System Control Unit                                            |

| SOW      | Short Open Window (for WDT1)                                   |

| SPI      | Serial Peripheral Interface                                    |

| SSC      | Synchronous Serial Channel                                     |

| SWD      | ARM Serial Wire Debug                                          |

| TCCR     | Temperature Compensation Control Register                      |

| TMS      | Test Mode Select                                               |

| TSD      | Thermal Shut Down                                              |

| UART     | Universal Asynchronous Receiver Transmitter                    |

| VBG      | Voltage reference Band Gap                                     |

| VCO      | Voltage Controlled Oscillator                                  |

| WDT1     | Watchdog timer in SCU-PM (System Control Unit - Power Modules) |

| WMU      | Wake-up Management Unit                                        |

| 100TP    | 100 Times Programmable                                         |

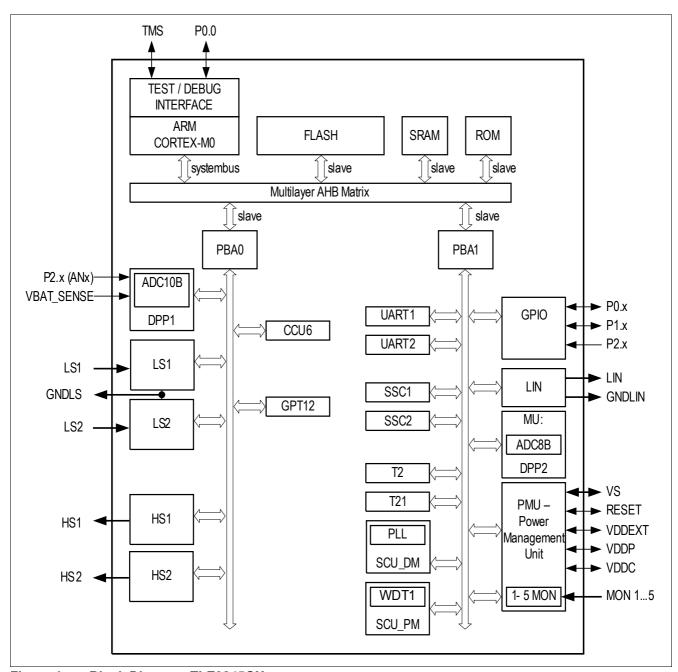

**Block Diagram**

## 2 Block Diagram

Figure 1 Block Diagram, TLE9845QX

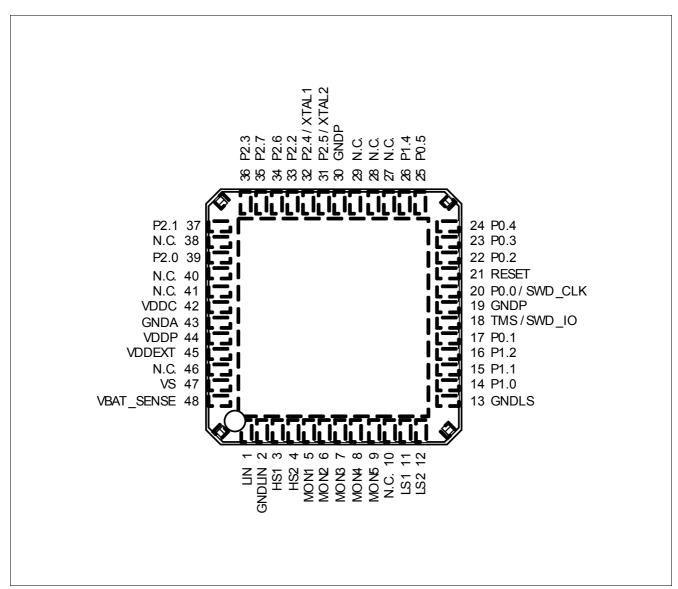

## 3 Device Pinout and Pin Configuration

#### 3.1 Device Pinout

Figure 2 Device Pinout, TLE9845QX

## 3.2 Pin Configuration

After reset, all pins are configured as input (except supply and LIN pins) with one of the following settings:

- Pull-up enabled only (PU)

- Pull-down enabled only (PD)

- Input with both pull-up and pull-down disabled (I)

- Output with output stage deactivated = high impedance state (Hi-Z)

The functions and default states of the TLE9845QX external pins are provided in the following table.

Type: indicates the pin type.

- I/O: Input or output

- I: Input only

- O: Output only

- P: Power supply

Not all alternate functions listed, see Chapter 14.

Table 2 Pin Definitions and Functions

| Symbol | Pin Number | Туре | Reset<br>State | Function        |                                                                                                                                 |

|--------|------------|------|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------|

| P0     |            |      |                | Alternate fur   | 6-Bit bidirectional general purpose I/O port. nctions can be assigned and are listed in the Port Main function is listed below. |

| P0.0   | 20         | I/O  | I/PU           | SWD_CLK<br>GPIO | Serial Wire Debug Clock General Purpose IO Alternate function mapping see <b>Table 8</b>                                        |

| P0.1   | 17         | I/O  | I/PU           | GPIO            | General Purpose IO Alternate function mapping see Table 8                                                                       |

| P0.2   | 22         | I/O  | I/PD           | GPIO            | General Purpose IO Alternate function mapping see Table 8                                                                       |

| P0.3   | 23         | I/O  | I/PU           | GPIO            | General Purpose IO Alternate function mapping see Table 8                                                                       |

| P0.4   | 24         | I/O  | I/PU           | GPIO            | General Purpose IO Alternate function mapping see Table 8                                                                       |

| P0.5   | 25         | I/O  | I/PU           | GPIO            | General Purpose IO Alternate function mapping see Table 8                                                                       |

| P1     |            |      |                | Alternate fur   | 4-Bit bidirectional general purpose I/O port. nctions can be assigned and are listed in the Port Main function is listed below. |

| P1.0   | 14         | I/O  | I              | GPIO            | General Purpose IO Alternate function mapping see Table 9                                                                       |

| P1.1   | 15         | I/O  | I              | GPIO            | General Purpose IO Alternate function mapping see Table 9                                                                       |

| P1.2   | 16         | I/O  | I              | GPIO            | General Purpose IO Alternate function mapping see Table 9                                                                       |

| P1.4   | 26         | I/O  | I              | GPIO            | General Purpose IO Alternate function mapping see Table 9                                                                       |

Table 2

Pin Definitions and Functions (cont'd)

| Table 2 P     | on Definitions a | and Fun | ctions (c      | ont'd)                                                                                                                                                                |                                                                                             |  |

|---------------|------------------|---------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| Symbol        | Pin Number       | Туре    | Reset<br>State | Function                                                                                                                                                              |                                                                                             |  |

| P2            |                  |         |                | Port 2 Port 2 is an 8-Bit general purpose input-only port. Alternate functions can be assigned and are listed in the Port description. Main function is listed below. |                                                                                             |  |

| P2.0          | 39               | I       | I              | AN0                                                                                                                                                                   | ADC1 analog input channel 12 Alternate function mapping see Table 10                        |  |

| P2.1          | 37               | I       | I              | AN1                                                                                                                                                                   | ADC1 analog input channel 7 Alternate function mapping see <b>Table 10</b>                  |  |