# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# TMC4361-LA DATASHEET

Cost-effective S-ramp motion controller with servo option for stepper motors. Optimized for high velocities. SPI and Step/Dir interfaces to motor driver and encoder interface for closed loop operation.

**FEATURES AND BENEFITS**

3.3V or 5V operation

**SPI interface** for  $\mu$ C with easy-to-use protocol

SPIinterface for SPI motor drivers

**Step/Dirinterface** forStep/Dir motor drivers

Clock frequency 4.2 MHz up to 32 MHz

Encoder interface: incremental ABN and serial SSI/SPI

2x ref.-switch input

Servo drive option

S-shaped or linear velocity ramps, optimally calculated On-the-fly change of target motion parameters Low power operation using clock gating technology

**Different current levels** related to the motion profile status **Programmable microstep table**

Read-out option for all important motion parameters Compact Size 6x6 mm<sup>2</sup> QFN40 package

Directly controls TMC23x, TMC24x, and TMC26x motor driver

#### DESCRIPTION

The TMC4361 is intended for applications where a fast and jerk-limited motion profile is desired. This motion controller adds to any microcontroller with SPI interface. It supports S-shaped, trapezoid, and rectangle ramps. With encoder, the TMC4361 allows for an extremely quick and precise positioning. Its servo features provide steploss protection, energy efficiency, and target positioning with stepper typical stability. Standard SPI and STEP/DIR interfaces to the motor driver simplify communication.

High end features, no software effort and the small form factor of the TMC4361 enable miniaturized designs with low external component count for cost-effective and highly competitive solutions.

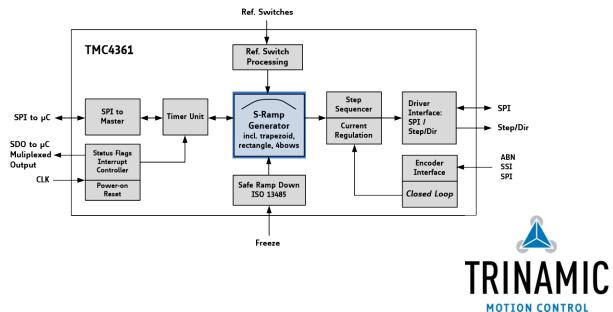

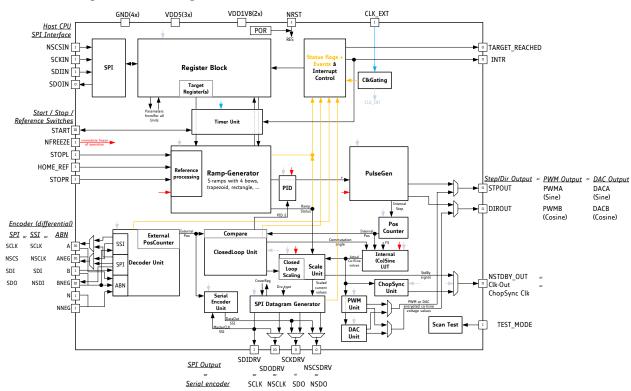

#### BLOCK DIAGRAM

### HIGH-END SOLUTION: VELOCITY MEETS PRECISION

The TMC4361 is a miniaturized high performance stepper motor controller with an outstanding costperformance ratio. It is designed for high volume as well as for demanding industrial motion control applications. The TMC4361 is equipped with an SPI<sup>™</sup> host interface (SPI is trademark of Motorola) with easy-to-use protocol and three driver interfaces (SPI, Step/Dir, and PWM) for addressing various stepper motor driver types. The TMC4361 scores with its unique servo drive features, high integration and a versatility that covers a wide spectrum of applications, motor sizes, and encoder types.

For a comfortable handling, the chip works with real world units. Extensive support at the chip, board, and software levels enables rapid design cycles and fast time-to-market with competitive products. High energy efficiency delivers further cost savings.

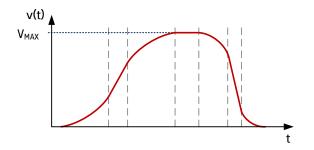

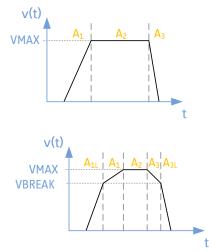

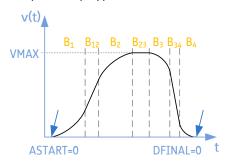

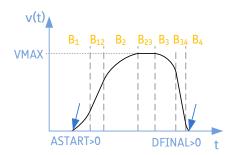

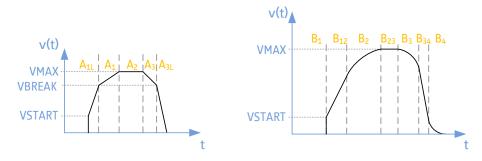

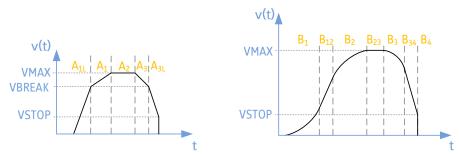

#### S-SHAPED VELOCITY PROFILE

This outstanding ramp profile minimizes jerk. Seven segments of the ramp allow for an optimum adaption of the velocity profile to the customer specific application requirements. High torque with high velocities can be reached by calibrating the bows of the ramp in a way that the acceleration value near  $V_{MAX}$  is reduced in parallel to the available motor torque.

#### COMPACT DESIGN FOR RELIABLE CLOSED LOOP OPERATION

#### **BENEFIT FROM HIGH VELOCITIES COMBINED WITH EXTREMELY HIGH PRECISION!**

Closed loop operation is an optimum choice in case a dynamic and reliable drive without step-loss or motor stall is desired. The controller IC monitors the encoder values nonstop and uses them for a sophisticated motor field control.

#### COMPACT DESIGN FOR RELIABLE OPERATION USING STOP SWITCHES

The TMC4361 offers a left and a right stop switch in hardware as well as a home switch. Further, it provides two virtual stop switches which can trigger stop slopes in case the related virtual stop switch microstep position is reached.

#### **ORDER CODES**

| Order code | Description                                             | Size      |

|------------|---------------------------------------------------------|-----------|

| TMC4361-LA | Motion controller with servo and dcStep features, QFN40 | 6 x 6 mm² |

# **Table of Contents**

| 1  |                              | PRINCIPLES OF OPERATION                                                                                                                          | 4                                |

|----|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|    | 1.3<br>1.4                   | Step Frequencies<br>Moving the Motor                                                                                                             | 4<br>5<br>6<br>7                 |

| 2  |                              | PIN ASSIGNMENTS                                                                                                                                  | 8                                |

|    |                              | Package Outline<br>Signal Description                                                                                                            | 8<br>8                           |

| 3  |                              | SAMPLE CIRCUITS                                                                                                                                  | 10                               |

| 4  |                              | NOTES                                                                                                                                            | 11                               |

| 5  |                              | SPI CONTROL INTERFACE                                                                                                                            | 12                               |

|    | 5.1<br>5.2<br>5.3            | SPI DATAGRAM STRUCTURE<br>SPI SIGNALS<br>TIMING                                                                                                  | 12<br>13<br>14                   |

| 6  |                              | INPUT FILTERING                                                                                                                                  | 15                               |

|    | 6.1                          | INPUT FILTER CONFIGURATION                                                                                                                       | 15                               |

| 7  |                              | STATUS FLAGS & EVENTS                                                                                                                            | 17                               |

|    | 7.1<br>7.2                   | STATUS FLAGS<br>STATUS EVENTS & SPI STATUS & INTERRUPTS                                                                                          | 17<br>17                         |

| 8  |                              | RAMP GENERATOR                                                                                                                                   | 19                               |

|    | 8.1<br>8.2                   | STEP/DIR OUTPUT CONFIGURATION<br>RAMP MODES AND TYPES                                                                                            | 19<br>20                         |

| 9  |                              | REFERENCE SWITCHES                                                                                                                               | 25                               |

|    | 9.2<br>9.3                   | STOPL AND STOPR<br>Virtual Stop Switches<br>HOME Reference<br>Cyclic Movement to <i>XTARGET</i><br>Target Reached / Position Comparison          | 25<br>26<br>27<br>28<br>28       |

| 10 | )                            | RAMP TIMING & SYNCHRONIZATION                                                                                                                    | 29                               |

|    |                              | Start Signal Generation<br>Target Pipeline                                                                                                       | 29<br>33                         |

| 11 | L                            | SERIAL DATA OUTPUT                                                                                                                               | 34                               |

|    | 11.2<br>11.3<br>11.4<br>11.5 | SINE WAVE LOOK-UP TABLE<br>SPI OUTPUT PARAMETERS<br>CURRENT DATAGRAMS<br>TMC MOTOR DRIVER<br>OTHER DRIVER CHIPS<br>CURRENT SCALING & RAMP STATUS | 35<br>38<br>39<br>40<br>43<br>44 |

| 12 | 2                            | NFREEZE: EMERGENCY-STOP                                                                                                                          | 47                               |

|    | 12.1                         | FREEZE FUNCTION CONFIGURATION                                                                                                                    | 47                               |

| 13 | 3                            | CONTROLLED PWM OUTPUT                                                                                                                            | 48                               |

|    | 13.1                         | PWM OUTPUT GENERATION                                                                                                                            | 48                               |

| 14 | F                            | DECODER UNIT & CLOSED LOOP                                                                                                                       | 49                               |

|    | 14.1                         | GENERAL ENCODER INTERFACE                                                                                                                        | 50                               |

|    |                              |                                                                                                                                                  |                                  |

| 14<br>14                                                                        | .3<br>.4                                                                                                                                                                                                                                                | INCREMENTAL ABN ENCODER<br>ABSOLUTE ENCODER<br>CONTROL VIA ENCODER FEEDBACK<br>ENCODER MISALIGNMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50<br>52<br>56<br>61                                                                                                                         |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 15                                                                              |                                                                                                                                                                                                                                                         | SERIAL ENCODER OUTPUT UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62                                                                                                                                           |

| 15                                                                              | 5.1                                                                                                                                                                                                                                                     | PROVIDING SSI OUTPUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 62                                                                                                                                           |

| 16                                                                              |                                                                                                                                                                                                                                                         | CLK GATING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63                                                                                                                                           |

| 16                                                                              | 5.1                                                                                                                                                                                                                                                     | CLOCK GATING AND WAKE-UP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 63                                                                                                                                           |

| 17                                                                              |                                                                                                                                                                                                                                                         | REGISTERS AND SWITCHES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65                                                                                                                                           |

| 17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>1 | .2         .3         .4         .5         .6         .7         .8         .9         .10         .11         .12         .13         .14         .15         .16         .17         .18         .19         .20         .21         .20         .21 | GENERAL CONFIGURATION<br>REFERENCE SWITCH CONFIGURATION<br>START SWITCH CONFIGURATION<br>INPUT FILTER CONFIGURATION<br>SPI-OUT CONFIGURATION<br>CURRENT CONFIGURATION<br>CURRENT SCALE VALUES<br>ENCODER SIGNAL CONFIGURATION<br>SERIAL ENCODER DATA IN<br>SERIAL ENCODER DATA OUT<br>MOTOR DRIVER SETTINGS<br>EVENT SELECTION REGISTERS<br>STATUS EVENT REGISTER<br>STATUS FLAG REGISTER<br>VARIOUS CONFIGURATION REGISTERS<br>RAMP GENERATOR REGISTERS<br>FREEZE REGISTER<br>CLOCK GATING ENABLE REGISTERS<br>PID AND CLOSED LOOP REGISTERS<br>MISC REGISTERS<br>TARNSFER REGISTERS<br>SINLUT REGISTERS | 65<br>67<br>69<br>70<br>71<br>73<br>73<br>74<br>76<br>76<br>76<br>76<br>76<br>77<br>78<br>80<br>82<br>83<br>83<br>84<br>85<br>86<br>87<br>87 |

| 18                                                                              |                                                                                                                                                                                                                                                         | ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 88                                                                                                                                           |

| 19                                                                              |                                                                                                                                                                                                                                                         | ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88                                                                                                                                           |

| 19                                                                              | .2                                                                                                                                                                                                                                                      | DC CHARACTERISTICS OPERATING CONDITIONS<br>POWER DISSIPATION<br>GENERAL IO TIMING PARAMETERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 88<br>88<br>89                                                                                                                               |

| 20                                                                              |                                                                                                                                                                                                                                                         | LAYOUT EXAMPLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 90                                                                                                                                           |

| 21                                                                              |                                                                                                                                                                                                                                                         | PACKAGE MECHANICAL DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 92                                                                                                                                           |

|                                                                                 |                                                                                                                                                                                                                                                         | Dimensional Drawings<br>Package Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 92<br>93                                                                                                                                     |

| 22                                                                              |                                                                                                                                                                                                                                                         | DISCLAIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 93                                                                                                                                           |

| 23                                                                              |                                                                                                                                                                                                                                                         | ESD SENSITIVE DEVICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93                                                                                                                                           |

| 24                                                                              |                                                                                                                                                                                                                                                         | TABLE OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 94                                                                                                                                           |

| 25                                                                              |                                                                                                                                                                                                                                                         | REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 95                                                                                                                                           |

| 25                                                                              | .1                                                                                                                                                                                                                                                      | DOCUMENT REVISIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 95                                                                                                                                           |

# **1** Principles of Operation

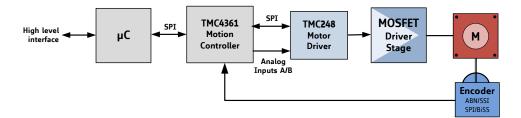

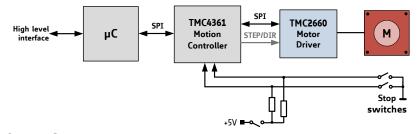

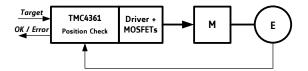

Figure 1.1 Basic application block diagram

# 1.1 Drive Concepts and Control Modes

The TMC4361 motion controller provides four different drive concepts respectivelycontrol modes. Choose the specific control mode related to the requirements of your application.

**CLASSIC STEPPER WITH OPEN LOOP**

**ENCODER FOR PRECISION AND POSITION MAINTENANCE**

**OPEN LOOP WITH ENCODER CHECK**

SERVO DRIVE: FEEDBACK CONTROL

# **1.2** Key Concepts

The TMC4361 realizes real time critical tasks autonomously and guarantees for a robust and reliable drive. The following features contribute toward greater precision, greater efficiency, higher reliability, higher velocity, and smoother motion in many stepper motor applications.

| Interfacing | The TMC4361 offers application specific interfacing via SPI,Step/Dir, and PWM interface. |

|-------------|------------------------------------------------------------------------------------------|

| T 1         |                                                                                          |

- *Initialization* Adapt the TMC4361 to the driver type and configuration and send initial configuration data to SPI drivers. Configure microstep resolution and waveform.

- PositioningThe TMC4361 operates motor based on user specified target positions and velocities.<br/>Modify all motion target parameters on-the-fly during motion.

- **Microstepping** Based on internal position counters the TMC4361 performs up to ±2<sup>31</sup> (micro)steps completely independent from the microcontroller. Microstep resolutions are individually programmable. The range goes from full stepping (1 microstep = 1 full step) and half stepping (2 microsteps per full step) up to 8 bit micro stepping (256 microsteps per full step) for precise positioning and noiseless stepper motor rotation. With Step/Dir drivers any microstep resolution is possible as supported by the driver. The internal microstep table can be adapted to specific motor characteristics to further reduce torque ripple.

- **Servo Drive** The TMC4361 provides closed loop operation for Step/Dir and SPI drivers. Using a differential or serial encoder, the closed loop unit of the TMC4361 compares the external position counter values with the internal ones and sends signals for correction.

- *chopSync™* The TMC4361 has an integratedchopSync chopper for very smooth motor movementwith TMC23x/24x.

- **Programming** Every parameter can be changed at any time. The uniform access to any TMC4361 register simplifies application programming. A read-back option for nearly all internal registers is available.

- **Synchronization** The TMC4361 provides synchronizing several TMC4361 motion controller chips if it is desired to drive motors simultaneously. In this case one TMC4361 is the master and the connected TMC4361 are slaves.

# **1.3** Overview Interfaces

# 1.3.1 SPI to CPU

From the software point of view, the TMC4361 provides a set of registers, accessed by a microcontroller via a serial interface in a uniform way. Each datagram contains address bits, a read-write selection bit, and data bits to access the registers and the on-chip memory. Each time the microcontroller sends a datagram to the TMC4361 it simultaneously receives a datagram from the TMC4361. This simplifies the communication with the TMC4361 and makes programming easy. Most microcontrollers have an SPI hardware interface, which directly connects to the serial four wire microcontroller interface of the TMC4361. For microcontrollers without SPIhardware, software doing the serial communication is sufficient and can easily be implemented. (For further information refer to chapter 5.)

### 1.3.2 SPI to Driver

The TMC4361 automatically generates the required data-stream for SPI drivers and provides user configurable microstep waves and motor ramps. The serial interface to the motor driver is configurable for all TRINAMIC drivers as well as for SPI DACs. Pre-settings for TRINAMIC driver chips are provided. (For further information refer to chapter 11.)

Third party driver chips can be configured via SPI interface using cover datagrams. During motor movement the SPI interface remains switched off and the Step/Dir interface isused for driving the motor.

### 1.3.3 Step/Dir to Driver

The TMC4361 provides a configurable Step/Dir interface to the driver. The motion controller controls the motor position by sending pulses on the STEP signal while indicating the direction on the DIR signal. Programmable step pulse length and step frequencies allow operation at high speed and high microstep resolution. The driver chip converts these signals into the coil currents which control the position of the motor. The TMC4361 perfectly fits to the TMC26x smart power Step/Dir driver family. (For further information refer to chapters 11.4 and 11.5.)

### **1.3.4 PWM Interface to Driver**

The TMC4361 allows for using PWM output values instead of Step/Dir outputs due to disabling the Step/Dir output and forwarding PWM signals via STPOUT\_PWMA and DIROUT\_PWMB. The PWM frequency is calculated with  $f_{PWM} = f_{CLK}$  / PWM\_FREQ.This mode supports noisefree and smooth microstepping with TMC23x and TMC24x stepper motor drivers. (For further information refer to chapter 13.)

### **1.3.5** Encoder Interface

The TMC4361 is equipped with a six pin encoder input interface for incremental ABN encoders (differential or single ended) or absolute encoders like SSI or SPI encoders. Motor feedback can be analyzed and closed loop behavior can be reached. All encoder input signals are filtered using anadaptable digital filter. (For further information refer to chapter 14.)

### 1.3.6 Reference Switches and Special IOs

The TMC4361 offers a left and a right stop switch in hardware as well as a home switch. Further, it provides two virtual stop switches which can trigger stop slopes in case the related virtual stop switch microstep position is reached. (Refer to chapter 9)

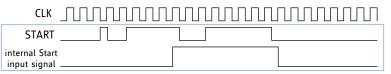

The START pin can be used as input or as output:a ramp start can be initialized viaa start input signal. The other way round, the START pin can be used as output. In this case, multiple drivers can be synchronized using an internal start signal of a TMC4361 master and forwarding it as start trigger to further TMC4361 which act as slaves then. (Refer to chapter 10.1.)

The TMC4361 provides a clock output (STDBY\_CLK). This output can be used to provide a step-synchronous chopper or application specific. (Refer to chapter 11.)

### 1.3.7 Safety Stop

The low-active safety pin NFREEZE can be used to end current operations without any delay. This way, an emergency-stop can be realized in case of dysfunctions on board level. (Refer to chapter 12.)

# 1.4 Step Frequencies

All parameter units are real physical units. Therefore, it is necessary to set the *CLK\_FREQ* register to the appropriate value in [Hz] which is given by the external clock. As operation frequency any value between 4.2 MHz and 32 MHz can be chosen. The maximum motion velocity is restricted by the clock frequency. Values higher than  $\frac{1}{2}$  pulse \*  $f_{CLK}$  are prohibited because the STPOUT output remains active for one clock cycle and inactive for one clock cycle afterwards for a Step/Dir driver. The microstep resolution can be chosen in the range from full steps up to 256 microsteps per full step when using the internal sequencer. (Refer to chapter 8.2.3.)

# **1.5** Moving the Motor

Moving the motor is simple:

To move a motor to a *new target position*, write the target position into the associated register by sending a datagram to the TMC4361.

To move a motor with a *newtarget velocity*, write the velocity into the register assigned to the stepper motor.

### **1.5.1** Motion Controller Functionality

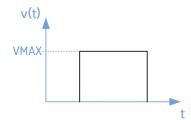

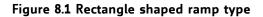

The ramp generator monitors the motion parameters stored in its registers and calculates velocity profiles. Based on the actual ramp generator velocity a pulse generator supplies step pulses to the motor driver and to the internal sequencer. Two general ramp modes can be chosen (see chapter 8.2):

*Velocity mode* The target velocity *VMAX* will be reached using the selected ramp type.

Positioning mode The maximum velocity value is used within the given ramp type as long as the target position is not exceeded. The stepping direction depends on XACTUAL, XTARGET, and the current ramp status.

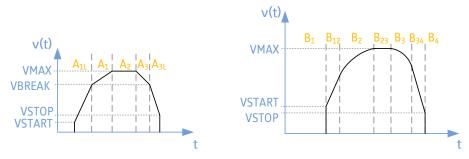

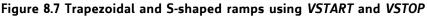

Three ramp types can be selected: rectangle shaped ramps, trapezoidal ramps, and S-shaped ramps. Sshaped ramps in positioning mode finish exactly at the target position by keeping the actual velocity at maximum value as long as possible while staying within the motion limits. The slopes to and from maximum velocity are as fast as possible without exceeding limits.

# **1.6** Status Flags, Events, and Interrupts

The microcontroller connected to the TMC4361 normally requires status information. Therefore, the TMC4361 provides 32 status flags and 32 status events. Status events can be configured customer specific and led through to the interrupt output of the TMC4361. (Refer to chapter 7.)

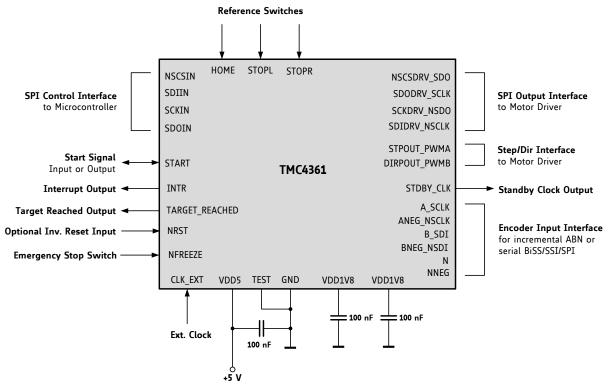

# 2 Pin Assignments

# 2.1 Package Outline

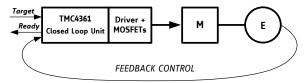

Figure 2.1Pinning (top view)

Attention: Do not connect pins without assignment!

# 2.2 Signal Description

| Pin       | Number         | Туре   | Function                                                                                         |

|-----------|----------------|--------|--------------------------------------------------------------------------------------------------|

| GND       | 6,15,<br>25,36 | GND    | Digital ground pin for IOs and digital circuitry                                                 |

| VDD5      | 5,26,37        | VDD    | Digital power supply for IOs and digital circuitry (3.3V 5V)                                     |

| VDD1V8    | 16,35          | VDD    | Connection of internal generated core voltage of 1.8V                                            |

| NSCSIN    | 2              | Ι      | Low active chip select input of the SPI interface to the $\mu C$                                 |

| SCKIN     | 3              | I      | Serial clock for the SPI interface to the $\mu$ C                                                |

| SDIIN     | 4              | Ι      | Serial data input of the SPI interface to the $\mu$ C                                            |

| SDOIN     | 7              | 0      | Serial data output of the SPI interface to the $\mu$ C (Z if NSCSIN=1)                           |

| CLK_EXT   | 38             | Ι      | Clock input to provide aclock with the frequency $f_{\text{CLK}}$ for all internal operations.   |

| NRST      | 39             | I (PU) | Low active reset. If not connected, Power-on-Reset and internal pull-up resistor will be active. |

| TEST_MODE | 34             | I      | Test mode input. Tie to low for normal operation.                                                |

| Pin                       | Number    | Туре   | Function                                                                                                                                                                                                                                                    |  |  |

|---------------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| STOPL                     | 12        | I (PD) | Left stop switch. External signal to stop a ramp.<br>If not connected, an internal pull-down resistor will be active.                                                                                                                                       |  |  |

| HOME_REF                  | 13        | I (PD) | Home reference signal input. External signal for reference search.If not connected,an internal pull-down resistor will be active.                                                                                                                           |  |  |

| STOPR                     | 14        | I (PD) | Right stop switch. External signal to stop a ramp.<br>If not connected, an internal pull-down resistor will be active.                                                                                                                                      |  |  |

| INTR                      | 33        | 0      | Interrupt output                                                                                                                                                                                                                                            |  |  |

| TARGET_REACHED            | 31        | 0      | Target reached output                                                                                                                                                                                                                                       |  |  |

| START                     | 20        | IO     | Start signal input/output                                                                                                                                                                                                                                   |  |  |

| NFREEZE                   | 19        | I (PU) | Low active safety pin to immediately freeze output operations.If not connected, an internal pull-up resistor will be active.                                                                                                                                |  |  |

| STDBY_CLK                 | 32        | 0      | StandBy signal or internal CLK output or ChopSync output                                                                                                                                                                                                    |  |  |

| Ν                         | 21        | I (PD) | N signal input of incremental encoder input interface<br>If not connected, an internal pull-down resistor will be active.                                                                                                                                   |  |  |

| NNEG                      | 22        | I (PD) | Negated N signal input of incremental encoder input interface<br>If not connected, an internal pull-down resistor will be active.                                                                                                                           |  |  |

| B<br>SDI                  | 10        | I (PD) | B signal input of incremental encoder input interface.<br>Serial data input signal of serial encoder input interface<br>(SSI/SPI).                                                                                                                          |  |  |

| BNEG<br>NSDI<br>SDO_ENC   | 11        | IO     | If not connected, an internal pull-down resistor will be active.<br>Negated B signal input of incremental encoder input interface.<br>Negated serial data input signal of SSI encoder input interface<br>Serial data output of SPI encoder input interface. |  |  |

| A<br>SCLK                 | 40        | IO     | A signal input of incremental encoder interface.<br>Serial clock output signal of serial encoder interface (SSI/SPI).                                                                                                                                       |  |  |

| ANEG<br>NSCLK<br>NSCS_ENC | 1         | IO     | Negated A signal input of incremental encoder interface.<br>Negated serial clock output signal of serial encoder interface.<br>Low active chip select output of SPI encoder input interface.                                                                |  |  |

| STPOUT<br>PWMA<br>DACA    | 24        | 0      | Step output.<br>First PWM signal (Sine).<br>First DAC output signal (Sine).                                                                                                                                                                                 |  |  |

| DIROUT<br>PWMB<br>DACB    | 23        | 0      | Direction output.<br>Second PWM signal (Cosine).<br>Second DAC output signal (Cosine).                                                                                                                                                                      |  |  |

| NSCSDRV<br>SDO            | 30        | 0      | Low active chip select output of SPI interface to motor driver.<br>Serial data output of serial encoder output interface.                                                                                                                                   |  |  |

| SCKDRV<br>NSDO            | 29        | 0      | Serial clock output of SPI interface to motor driver.<br>Negated serial data output of serial encoder output interface.                                                                                                                                     |  |  |

| SDODRV<br>SCLK            | 27        | IO     | Serial data output of SPI interface to motor driver.<br>Clock input of serial encoder output interface.                                                                                                                                                     |  |  |

| SDIDRV<br>NSCLK           | 28        | I (PD) | Serial data input of SPI interface to motor driver.<br>Negated clock input of serial encoder output interface<br>If not connected, an internal pull-down resistor will be active.                                                                           |  |  |

| n.c.                      | 8,9,17,18 | -      | Do not connect                                                                                                                                                                                                                                              |  |  |

PD: if n.c. → pull-down PU: if n.c. → pull-up

# 3 Sample Circuits

The sample circuits show the connection of external components.

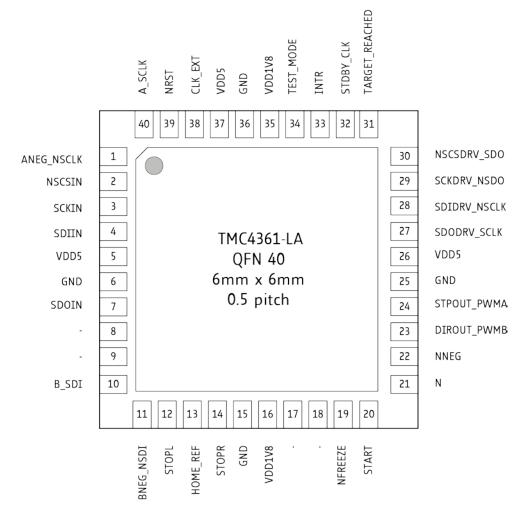

Figure 3.1 How to connect the TMC4361

#### **CHECK YOUR CONNECTIONS!**

- 1. Check, if the STDBY\_CLK output provides the pulse which is applied at the CLK\_EXT input pin. If both values fit, POR (power on reset), power supply and clk frequency are ready to be used.

- 2. The SPI communication to TMC4361 is established if the step frequency at STPOUT\_PWMA matches to the selected value of VMAX (maximum velocity value). This relationship is valid with a clock frequency of 16MHz. When using another frequency, it is necessary to convert the values appropriately.

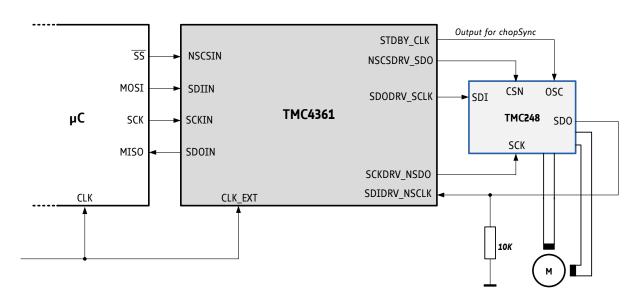

#### Figure 3.2 TMC4361 with TMC248 stepper driver in SPI mode

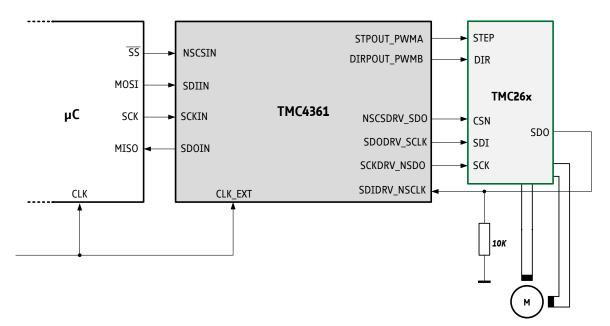

Figure 3.3 TMC4361 with TMC26x stepper driver in Step/Dir mode. The SPI interface is used for configuration.

# 4 Notes

REGISTER names are italicized with VALUE REGISTER in capital letters and switches with small letters.

PIN names are written with capital letters.

# 5 SPI Control Interface

The TMC4361 uses 40 bit SPI<sup>TM</sup> datagrams for communication with a microcontroller. The bit-serial interface is synchronous to a bus clock. For every bit sent from the bus master to the bus slave, another bit is sent simultaneously from the slave to the master. Communication between an SPI master and the TMC4361 slave always consists of sending one 40-bit command word and receiving one 40-bit status word. The SPI command rate typically comprises a few commands per complete motor motion.

#### SPI CONTROL INTERFACE

| Pin Name | Туре   | Remarks                                          |

|----------|--------|--------------------------------------------------|

| NSCSIN   | Input  | Chip Select of the SPI-µC interface (low active) |

| SCKIN    | Input  | Clock of the SPI-µC interface                    |

| SDIIN    | Input  | Data input of the SPI-µC interface               |

| SDOIN    | Output | Data output of the SPI-µC interface              |

# 5.1 SPI Datagram Structure

Microcontrollers which are equipped with hardware SPI are typically able to communicate using integer multiples of 8 bit. The NSCSINline of the TMC4361has to be handled in a way, that it stays active (low) for the complete duration of the datagram transmission.

Each datagram sent to the TMC4361 is composed of an address byte followed by four data bytes. This allows direct 32 bit data word communication with the register set of the TMC4361. Each register is accessed via 32 data bits even if it uses less than 32 data bits.

Each register is specified by a one byte address:

- For a read access the most significant bit of the address byte is 0.

- For a write access the most significant bit of the address byte is 1.

Some registers are write only registers, most can be read additionally, and there are also some read only registers.

| TMC4361 SPI DATAGRAM STRUCTURE                                                                                                                                           |                                                       |                               |                            |                            |                            |                           |               |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------|----------------------------|----------------------------|----------------------------|---------------------------|---------------|---------------|

| MSB (transmitted first                                                                                                                                                   | MSB (transmitted first) 40 bit LSB (transmitted last) |                               |                            |                            |                            |                           |               |               |

| 39                                                                                                                                                                       |                                                       |                               |                            | 0                          |                            |                           |               |               |

| <ul> <li>→ 8 bit address</li> <li>← 8 bit SPI status</li> </ul>                                                                                                          | $\leftrightarrow$ 32 bi                               | $\leftrightarrow$ 32 bit data |                            |                            |                            |                           |               |               |

| 39 32                                                                                                                                                                    | 31 0                                                  |                               |                            |                            |                            |                           |               |               |

| <ul> <li>→ to TMC4361:</li> <li>RW + 7 bit address</li> <li>← from TMC4361:</li> <li>8 bit SPI status</li> </ul>                                                         | 8 bit data                                            |                               | 8 bit data                 |                            | 8 bit data                 |                           | 8 bit data    |               |

| 39 / 38 32                                                                                                                                                               | 31 24                                                 |                               | 23 16                      |                            | 15 8                       |                           | 7 0           |               |

| w         3832           3         3         3         3         3         3         3           9         8         7         6         5         4         3         2 |                                                       | 2724<br>2 2 2 2<br>7 6 5 4    | 2320<br>2 2 2 2<br>3 2 1 0 | 1916<br>1 1 1 1<br>9 8 7 6 | 1512<br>1 1 1 1<br>5 4 3 2 | 118<br>1 1 9 8<br>1 0 9 8 | 74<br>7 6 5 4 | 30<br>3 2 1 0 |

# 5.1.1 Selection of Write / Read (WRITE\_notREAD)

The read and write selection is controlled by the MSB of the address byte (bit 39 of the SPI datagram). This bit is 0 for read access and 1 for write access. So, the bit named W is a WRITE\_notREAD control bit. The active high write bit is the MSB of the address byte. Thus, 0x80 has to be added to the address for a write access. The SPI interface always delivers data back to the master, independent of the W bit. The data transferred back is the data read from the address which was transmitted with the *previous* datagram, if the previous access was a read access. If the previous access was a write access, then the data read back mirrors the previously received write data. So, the difference between a read and a write access is that the read access does not transfer data to the addressed register but it transfers the address

only and its 32 data bits are dummies. Further, the following read or write access delivers back data read from the address transmitted in the preceding read cycle.

A read access request datagram uses dummy write data. Read data is transferred back to the master with the subsequent read or write access. Hence, reading multiple registers can be done in a pipelined fashion. Data which will be delivered are latched immediately after the prior data transfer.

Whenever data is read from or written to the TMC4361, the MSBs delivered back contain the SPI status *SPI\_STATUS*, which is a number of eight status bits. The selection of these bits will be explained in chapter 7.2.

Example:

For a read access to the register (*XACTUAL*) with the address 0x21, the address byte has to be set to 0x21 in the access preceding the read access. For a write access to the register (*VACTUAL*), the address byte has to be set to 0x80 + 0x22 = 0xA2. For read access, the data bit might have any value, e.g., 0.

| action                     | data sent to TMC           | data received from TMC          |

|----------------------------|----------------------------|---------------------------------|

| read XACTUAL               | →0x2100000000              | $\leftarrow$ 0xSS & unused data |

| read XACTUAL               | →0x2100000000              | ←0xSS & X_ACTUAL                |

| write VACTUAL:= 0x00ABCDEF | $\rightarrow$ 0xA200ABCDEF | ←0xSS & X_ACTUAL                |

| write VACTUAL:= 0x00123456 | →0xA200123456              | $\leftarrow$ 0xss00abcdef       |

\*) SS: is a placeholder for the status bits SPI\_STATUS

### 5.1.2 Data Alignment

All data are right aligned. Some registers represent unsigned (positive) values; some represent integer values (signed) as two's complement numbers. Single bits or groups of bits are represented as single bits respectively as integer groups.

# 5.2 SPI Signals

The SPI bus on the TMC4361 has four signals:

- SCKIN bus clock input

- SDIIN serial data input

- SDOIN serial data output

- NSCSIN chip select input (active low)

The slave is enabled for an SPI transaction by a transition to low level on the chip select input NSCSIN. Bit transfer is synchronous to the bus clock SCKIN, with the slave latching the data from SDIIN on the rising edge of SCKIN and driving data to SDOIN following the falling edge. The most significant bit is sent first. A minimum of 40 SCKIN clock cycles is required for a bus transaction with the TMC4361. If less than 40 clock cycles are transmitted, the transfer will not be valid, even for a read access. However, sending only eight clock cycles can be useful to obtain the SPI status because it sends the status information back first.

If more than 40 clocks are driven, the additional bits shifted into SDIIN are shifted out on SDOIN after a 40-clock delay through an internal shift register. This can be used for daisy chaining multiple chips.

NSCSIN must be low during the whole bus transaction. When NSCSIN goes high, the contents of the internal shift register are latched into the internal control register and recognized as a command from the master to the slave. If more than 40 bits are sent, only the last 40 bits received before the rising edge of NSCSIN are recognized as the command.

# 5.3 Timing

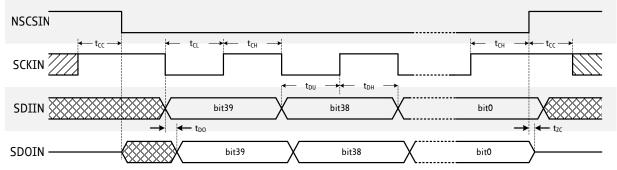

The SPI interface is synchronized to the internal system clock, which limits the SPI bus clock SCKIN to half of the system clock frequency. The signal processing of the SPI inputs are supported with internal Schmitt Trigger, but not with RC elements. To avoid glitches at the inputs of the SPI interface between  $\mu$ C and TMC4361, external RC elements have to be provided. Figure 5.1 shows the timing parameters of an SPI bus transaction and the table below specifies the parameter values.

Figure 5.1 SPI timing

| SPI interface timing                                                      | AC-Characteristics             |                                                                                                           |                     |                        |                             |      |  |  |

|---------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------|------------------------|-----------------------------|------|--|--|

|                                                                           | clock period: t <sub>CLK</sub> |                                                                                                           |                     |                        |                             |      |  |  |

| Parameter                                                                 | Symbol                         | Conditions                                                                                                | Min                 | Тур                    | Max                         | Unit |  |  |

| SCKIN valid before or after change of NSCSIN                              | tcc                            |                                                                                                           | 10                  |                        |                             | ns   |  |  |

| NSCSIN high time                                                          | t <sub>сsн</sub>               | *) Min time is for<br>synchronous CLK<br>with SCKIN high<br>one t <sub>CH</sub> before<br>SCSIN high only | t <sub>clk</sub> *) | >2t <sub>CLK</sub> +10 |                             | ns   |  |  |

| SCKIN low time                                                            | t <sub>CL</sub>                | *) Min time is for<br>synchronous CLK<br>only                                                             | t <sub>clK</sub> *) | >t <sub>CLK</sub> +10  |                             | ns   |  |  |

| SCKIN high time                                                           | t <sub>сн</sub>                | *) Min time is for<br>synchronous CLK<br>only                                                             | t <sub>clk</sub> *) | >t <sub>CLK</sub> +10  |                             | ns   |  |  |

| SCKIN frequency using external clock (Example: f <sub>CLK</sub> = 16 MHz) | f <sub>scк</sub>               | assumes<br>synchronous CLK                                                                                |                     |                        | f <sub>CLK</sub> / 2<br>(8) | MHz  |  |  |

| SDIIN setup time before rising edge of SCKIN                              | $\mathbf{t}_{DU}$              |                                                                                                           | 10                  |                        |                             | ns   |  |  |

| SDIIN hold time after rising edge of SCKIN                                | t <sub>DH</sub>                |                                                                                                           | 10                  |                        |                             | ns   |  |  |

| Data out valid time after falling SCKIN clock edge                        | t <sub>DO</sub>                | no capacitive load<br>on SDOIN                                                                            |                     |                        | t <sub>filt</sub> +5        | ns   |  |  |

$t_{CLK}$  = 1 /  $f_{CLK}$

# 6 Input Filtering

Input signals can be noisy due to long cables and circuit paths. To prevent jamming, every input pin provides a Schmitt Trigger. Additionally, several signalsare passed through a digital filter. Particular inputpins areseparated into four filtering groups. Each groupcan be programmedindividuallyaccording to its filter characteristics.

PINS AND REGISTERS: INPUT FILTERING GROUPS

| Pin names       | Ту               | pe   | Remarks                                              |

|-----------------|------------------|------|------------------------------------------------------|

| A_SCLK          |                  |      | Encoder interface input pins                         |

| B_SDI           |                  |      |                                                      |

| N               | Inc              | outs |                                                      |

| ANEG_NSCLK      | •                |      |                                                      |

| BNEG_NSDI       |                  |      |                                                      |

| NNEG            |                  |      |                                                      |

| STOPL           | _                |      | Reference input pins                                 |

| HOME_REF        | Inp              | outs |                                                      |

| STOPR           |                  |      |                                                      |

| START           | Inj              | out  | START input pin                                      |

| SDODRV_SCLK     | Tenute           |      | Master clock input interface pins for serial encoder |

| SDIDRV_NSCLK    | Inputs           |      |                                                      |

| Pin name        | Register address |      | Remarks                                              |

| INPUT_FILT_CONF | 0x03             | RW   | Filter configuration for all four input groups       |

# 6.1 Input Filter Configuration

Every filtering groupcan be configured separately with regard toinput sample rate and digital filter length.

## 6.1.1 Input Sample Rate (SR)

$f_{CLK} \cdot 1 / 2^{SR}$

where SR (extended with the particular name extension) isin [0... 7].

This means that every (2<sup>sR</sup>)<sup>th</sup> input bit will be considered for internal processing.

| Sample rate configuration |                        |  |  |  |  |

|---------------------------|------------------------|--|--|--|--|

| SR value                  | Sample rate            |  |  |  |  |

| 0                         | f <sub>clк</sub>       |  |  |  |  |

| 1                         | f <sub>CLK</sub> / 2   |  |  |  |  |

| 2                         | f <sub>CLK</sub> / 4   |  |  |  |  |

| 3                         | f <sub>CLK</sub> / 8   |  |  |  |  |

| 4                         | f <sub>CLK</sub> / 16  |  |  |  |  |

| 5                         | f <sub>CLK</sub> / 32  |  |  |  |  |

| 6                         | f <sub>clk</sub> / 64  |  |  |  |  |

| 7                         | f <sub>CLK</sub> / 128 |  |  |  |  |

# 6.1.2 Digital Filter Length (FILT\_L)

One bit is sampled within each (2<sup>SR</sup>)<sup>th</sup>input clock cycle. The filter length FILT\_L can be set within the range [0... 7]. The filter lengthFILT\_L specifies the number of sampled bits thatmust have the same voltage level toseta new input bit voltage level.

| Configuration | Configuration of digital filter length |  |  |  |  |

|---------------|----------------------------------------|--|--|--|--|

| FILT_L value  | Filter length                          |  |  |  |  |

| 0             | No filtering                           |  |  |  |  |

| 1             | 2 equal bits                           |  |  |  |  |

| 2             | 3 equal bits                           |  |  |  |  |

| 3             | 4 equal bits                           |  |  |  |  |

| 4             | 5 equal bits                           |  |  |  |  |

| 5             | 6 equal bits                           |  |  |  |  |

| 6             | 7 equal bits                           |  |  |  |  |

| 7             | 8 equal bits                           |  |  |  |  |

### 6.1.3 Examples

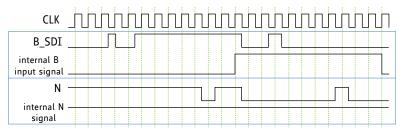

The following three examples depict the input pin filtering of three different input filtering groups. The voltage levels after passing the Schmitt Trigger are compared to the internal signals which are processed by the motion controller.

The sample points are depicted as green dashed lines.

#### **REFERENCE INPUT PINS**

Here, every second clock cycle is sampled. Two sampled input bits must be equal to be a valid input voltage.

| CLK                          | Л |   | Л | ЛЛ | hΠ | ЛЛ | ΠЛ | Л | ΠΠ | ΠЛ | пл | Π |

|------------------------------|---|---|---|----|----|----|----|---|----|----|----|---|

| HOME                         |   | Л |   |    |    |    |    |   |    |    |    | _ |

| internal<br>home signal      |   |   |   |    |    |    |    |   |    |    |    | _ |

| STOPL                        |   |   |   |    |    | Л  |    | 1 |    |    |    | _ |

| internal left<br>stop signal |   |   |   |    |    |    |    |   |    |    |    |   |

#### Figure 6.1 Reference input pins: SR\_REF = 1, FILT\_L\_REF = 1

#### START INPUT PIN

Every fourth clock cycle is sampled and the sampled input bit is valid.

#### Figure 6.2START input pin: SR\_S = 2, FILT\_L\_S = 0

#### **ENCODER INTERFACE INPUT PINS**

Every clock cycle bit is sampled. Eight sampled input bits must be equal to be a valid input voltage.

Figure 6.3 Encoder interface input pins: SR\_ENC\_IN = 0, FILT\_L\_ENC\_IN = 7

# 7 Status Flags & Events

The TMC4361 offers several possibilities for velocity ramps. It combinestarget positioning and velocity ramps without interventions in between. However, the microcontroller connected to the TMC4361 normally requiresstatus information. Therefore, TMC4361 provides 32 status flags and 32 status events. Status events can be configured customer specific and lead through using the interrupt output of the TMC4361. Further, the eight SPI status bits sent witheach SPI datagram can be read out.

| Pin names            | Туре             |     | Remarks                                                                |

|----------------------|------------------|-----|------------------------------------------------------------------------|

| INTR                 | Out              | put | Interrupt output to indicate status events                             |

| Register name        | Register address |     | Remarks                                                                |

| STATUS_FLAGS         | 0x0F             | R   | 32 status flags of the TMC4361 and the connected TMC motor driver chip |

|                      |                  |     | · · · · · · · · · · · · · · · · · · ·                                  |

| EVENTS               | 0x0E             | R+C | 32 events triggered by altered TMC4361 status bits                     |

| SPI_STATUS_SELECTION | 0x0B             | RW  | Selection of 8 out of 32 events for SPI status bits                    |

| EVENT_CLEAR_CONF     | 0x0C             | RW  | Exceptions for cleared event bits                                      |

| INTR_CONF            | 0x0D             | RW  | Selection of 32 events for INTR output                                 |

#### PINS AND REGISTERS: STATUS FLAGS AND EVENTS

# 7.1 Status Flags

Status bits of the STATUS\_FLAGS register are specified in the register chapter (see 17).

# 7.2 Status Events & SPI Status & Interrupts

#### STATUS FLAGS - STATUS EVENTS

Status eventsare triggered during the transition process of status bits from inactive to active level. Status bits and status events are associated in different ways:

- Several status eventsare associated with one status bit.

- Some status events show the status transition of one or more status bits out of a status bit group. The motor driver flags, e.g., triggeronly one motor driver event *MOTOR\_EV* in case one of the selected motor driver status flags becomes active.

- In case a flag consists of more than one bit, the number of associated events that can be triggered corresponds to the valid combinations. The *VEL\_STATE* flag, e.g., has two bit but three associated velocity state events (00/01/10). Such an eventistriggered if the associated combination switches from inactive to active.

- Furthermore, some events have no equivalence in the *STATUS\_FLAGS* register(e.g., *COVER\_DONE* which indicates new data from the motor driver chip).

The EVENTS register is automatically cleared after reading the register subsequent to an SPI datagram request.

To prevent events from being cleared, the *EVENT\_CLEAR\_CONF* register can be assigned properly. Just set the related *EVENT\_CLEAR\_CONF* register bit position to 1.

#### HOW TO AVOID A LACK OF INFORMATION

The recognition of a status event can fail in case it is triggered right before or during the *EVENTS* register becomes cleared. By setting the *EVENT\_CLEAR\_CONF* register appropriately, this can be avoided. Up to eight events can be selected for permanent SPI status report.Therefore, select up to eight events by writing 1 to the specific bit positions of the *SPI\_STATUS\_SELECTION* register.The bit positionsaresorted according to the event bit positions in the *EVENTS* register. In case more than eight events are chosen, the first eight bits (starting from index 0) are forwarded as *SPI\_STATUS*.

#### INTERRUPTS

Similar to the *EVENT\_CLEAR\_CONF* register and the *SPI\_STATUS\_SELECTION* register, events can be selected using the *INTR\_CONF* register to be forwarded to the INTR output. The active polarity of the INTR output can be set with *intr\_pol*. The selected events will be ORed to one signal. The INTR output becomes active as soon as one of the selected events triggers.

Due to the importance of events for interrupt generation and SPI status monitoring, it is recommended to clear the *EVENTS* register before starting regular operation.

# 8 Ramp Generator

Stepgeneration is one of themain tasks of a steppermotor motion controller. The internal ramp generator of the TMC4361 provides several ways of step generation in order to form different ramp types to fit for various applications.

| PINS AND REGISTERS: R | RAMP GENERATOR |

|-----------------------|----------------|

|-----------------------|----------------|

| Pin names                        | Ту       | ре      | Remarks                                                                                                                                          |  |  |

|----------------------------------|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| STPOUT_PWMA                      | Out      | put     | Step output signal                                                                                                                               |  |  |

| DIROUT_PWMB                      | Output   |         | Direction output signal                                                                                                                          |  |  |

| Register name                    | Register | address | Remarks                                                                                                                                          |  |  |

| GENERAL_CONF                     | 0x00     | RW      | Ramp generator affecting bits 1 : 5                                                                                                              |  |  |

| STP_LENGTH_ADD<br>DIR_SETUP_TIME | 0x10     | RW      | Additional step length in clock cycles; 16 bits<br>Additional time in clock cycles when no steps will occur<br>after a direction change; 16 bits |  |  |

| RAMPMODE                         | 0x20     | RW      | Requested ramp type and mode; 3 bits                                                                                                             |  |  |

| XACTUAL                          | 0x21     | RW      | Current internal microstep position;signed; 32 bits                                                                                              |  |  |

| VACTUAL                          | 0x22     | R       | Current step velocity; 24 bits; signed; no decimals                                                                                              |  |  |

| AACTUAL                          | 0x23     | R       | Current step acceleration; 24 bits; signed; no decimals                                                                                          |  |  |

| VMAX                             | 0x24     | RW      | Maximum permitted or target velocity; signed; 32 bits=<br>24+8 (24 bits integer part, 8 bits decimal places)                                     |  |  |

| VSTART                           | 0x25     | RW      | Velocity at ramp start; unsigned; 31 bits=23+8                                                                                                   |  |  |