# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **TMC5160 DATASHEET**

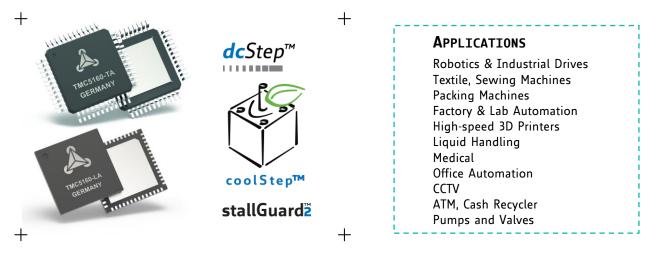

Universal high voltage controller/driver for two-phase bipolar stepper motor. stealthChop™ for quiet movement. External MOSFETs for up to 20A motor current per coil. With Step/Dir Interface and SPI.

#### **FEATURES AND BENEFITS**

2-phase stepper motors up to 20A coil current (external MOSFETs) Motion Controller with sixPoint<sup>™</sup> ramp Step/Dir Interface with microstep interpolation microPlyer™ Voltage Range 8 ... 60V DC SPI & Single Wire UART Encoder Interface and 2x Ref.-Switch Input Highest Resolution 256 microsteps per full step stealthChop2<sup>™</sup> for guiet operation and smooth motion **Resonance Dampening** for mid-range resonances **spreadCycle™** highly dynamic motor control chopper dcStep<sup>™</sup> load dependent speed control stallGuard2<sup>™</sup> high precision sensorless motor load detection coolStep<sup>™</sup> current control for energy savings up to 75% Passive Braking and freewheeling mode **Full Protection & Diagnostics** Compact Size 9x9mm<sup>2</sup> TQFP48 package / 8x8mm<sup>2</sup> QFN

#### DESCRIPTION

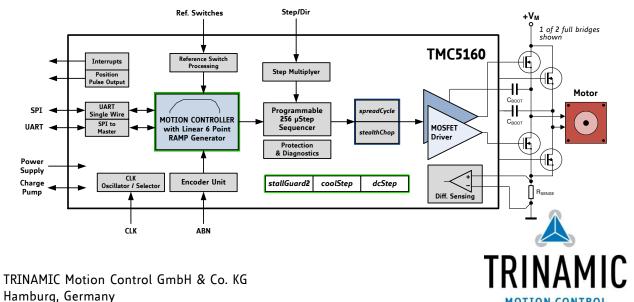

The TMC5160 is a high power stepper motor controller and driver IC with serial communication interfaces. It combines a flexible ramp generator for automatic target positioning with industries' most advanced stepper motor driver. Using external transistors, highly dynamic, high torque drives can be realized. Based on TRINAMICs sophisticated spreadCycle and stealthChop choppers, the driver ensures absolutely noiseless operation combined with maximum efficiency and best motor torque. High integration, high energy efficiency and a small form factor enable miniaturized and scalable systems for cost effective solutions. The complete solution reduces learning curve to a minimum while giving best performance in class.

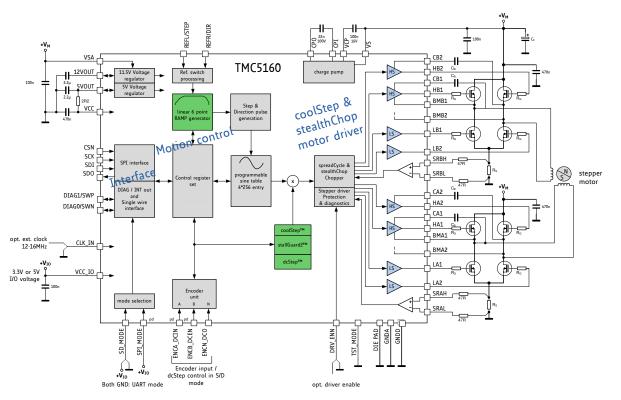

MOTION CONTROL

#### BLOCK DIAGRAM

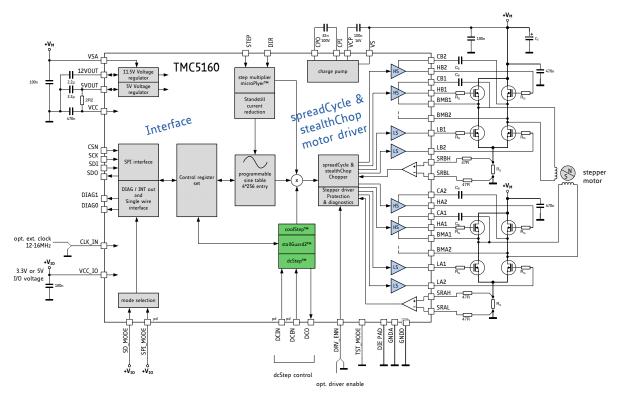

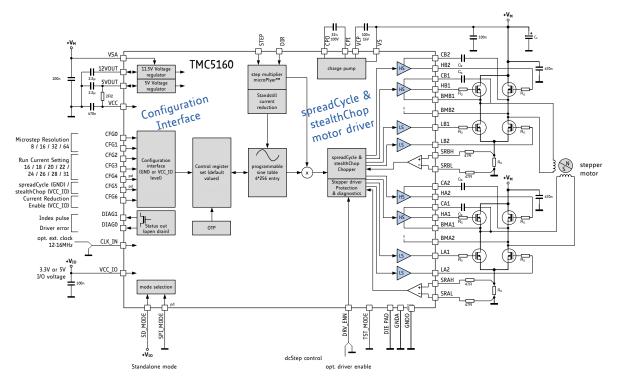

#### **APPLICATION EXAMPLES: HIGH VOLTAGE – MULTIPURPOSE USE**

The TMC5160 scores with complete motion controlling features, powerful external MOSFET driver stages, and high quality current regulation. It offers a versatility that covers a wide spectrum of applications from battery powered, high efficiency systems up to embedded applications with 20A motor current per coil. The TMC5160 contains the complete intelligence which is required to drive a motor. Receiving target positions the TMC5160 manages motor movement. Based on TRINAMICs unique features stallGuard2, coolStep, dcStep, spreadCycle, and stealthChop, the TMC5160 optimizes drive performance. It trades off velocity vs. motor torque, optimizes energy efficiency, smoothness of the drive, and noiselessness. The small form factor of the TMC5160 keeps costs down and allows for miniaturized layouts. Extensive support at the chip, board, and software levels enables rapid design cycles and fast time-to-market with competitive products. High energy efficiency and reliability deliver cost savings in related systems such as power supplies and cooling. For smaller designs, the compatible, integrated TMC5130 driver provides 1.4A of motor current.

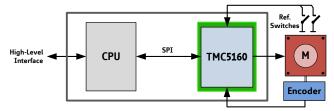

#### MINIATURIZED DESIGN FOR ONE STEPPER MOTOR

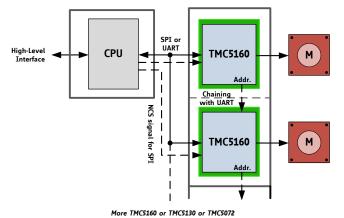

COMPACT DESIGN FOR MULTIPLE STEPPER MOTORS

An ABN encoder interface with scaler unit and two reference switch inputs are used to ensure correct motor movement. Automatic interrupt upon deviation is available.

An application with 2 stepper motors is shown. Additionally, the ABN Encoder interface and two reference switches can be used for each motor. A single CPU controls the whole system, as there are no real time tasks required to move a motor. The CPUboard and the controller / driver boards are highly economical and space saving.

The TMC5160-EVAL is part of TRINAMICs universal evaluation board system which provides a convenient handling of the hardware as well as a user-friendly software tool for evaluation. The TMC5160 evaluation board system consists three of parts: LANDUNGSBRÜCKE (base board), ESELSBRÜCKE (connector board including several test points), and TMC5160-EVAL.

#### **ORDER CODES**

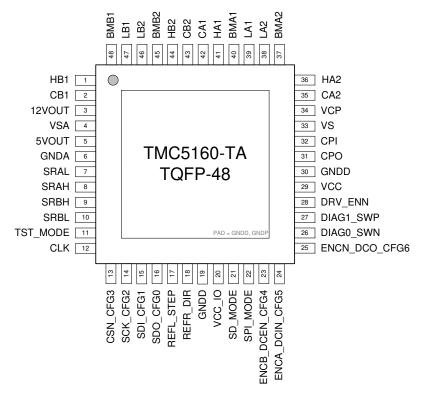

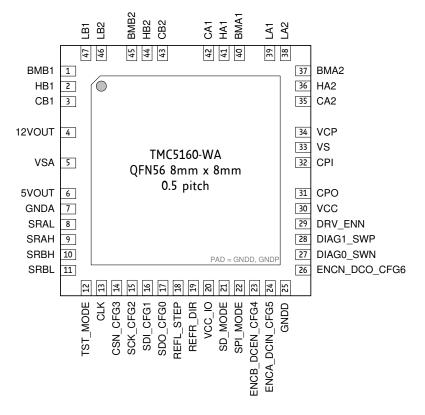

| Order code     | Description                                                            | Size [mm <sup>2</sup> ] |  |  |

|----------------|------------------------------------------------------------------------|-------------------------|--|--|

| TMC5160-TA     | stepper controller/driver for external MOSFETs; TQFP48                 | 9 x 9                   |  |  |

| TMC5160-WA     | stepper controller/driver for external MOSFETs; wett. QFN8x8           | 8 x 8                   |  |  |

| TMC5160-EVAL   | Evaluation board for TMC5160 two phase stepper motor controller/driver | 85 x 55                 |  |  |

| LANDUNGSBRÜCKE | Baseboard for TMC5160-EVAL and further evaluation boards.              | 85 x 55                 |  |  |

| ESELSBRÜCKE    | onnector board for plug-in evaluation board system. 61 x 38            |                         |  |  |

## **Table of Contents**

| 1 | PRI                                                                                                                                         | NCIPLES OF OPERATION5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1                                                                                                                                         | Key Concepts6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 1.2                                                                                                                                         | CONTROL INTERFACES7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 1.3                                                                                                                                         | SOFTWARE7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 1.4                                                                                                                                         | MOVING AND CONTROLLING THE MOTOR8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

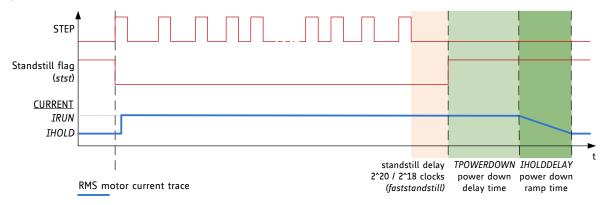

|   | 1.5                                                                                                                                         | AUTOMATIC STANDSTILL POWER DOWN8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 1.6                                                                                                                                         | STEALTHCHOP2 & SPREADCYCLE DRIVER8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 1.7                                                                                                                                         | stallGuardz – Mechanical Load Sensing9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 1.8                                                                                                                                         | coolStep – Load Adaptive Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | CONTRO                                                                                                                                      | DL9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 1.9                                                                                                                                         | DCSTEP – LOAD DEPENDENT SPEED CONTROL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | ,                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 1.10                                                                                                                                        | ENCODER INTERFACE10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2 | DTN                                                                                                                                         | ASSIGNMENTS11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2 | 1 111                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 2.1                                                                                                                                         | PACKAGE OUTLINE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 2.2                                                                                                                                         | SIGNAL DESCRIPTIONS12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3 | SAM                                                                                                                                         | 19LE CIRCUITS15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

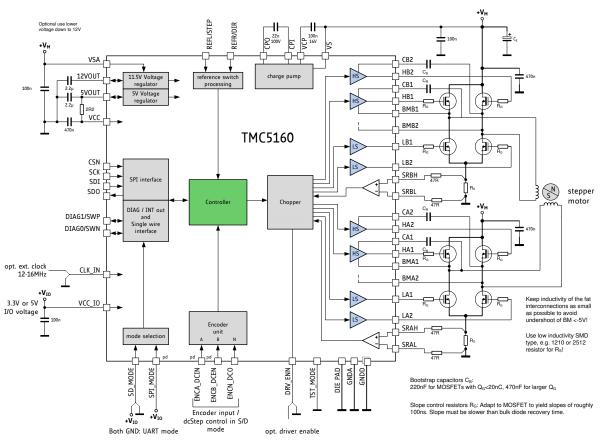

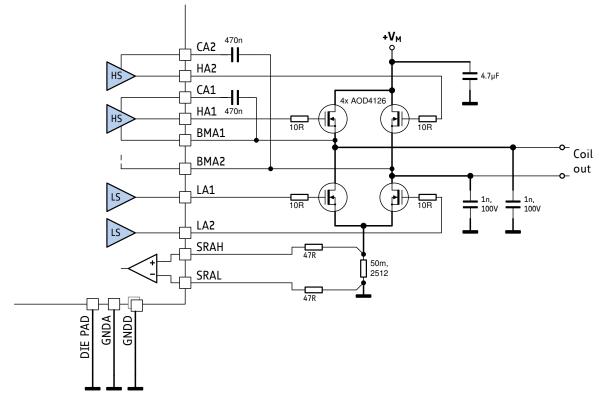

|   | 3.1                                                                                                                                         | STANDARD APPLICATION CIRCUIT15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

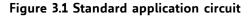

|   | 3.2                                                                                                                                         | EXTERNAL GATE VOLTAGE REGULATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

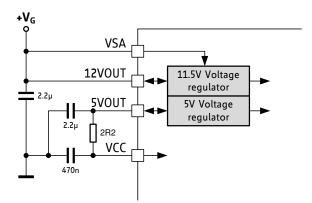

|   | 3.3                                                                                                                                         | CHOOSING MOSFETS AND SLOPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 3.4                                                                                                                                         | TUNING THE MOSFET BRIDGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| _ |                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4 | 361                                                                                                                                         | INTERFACE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

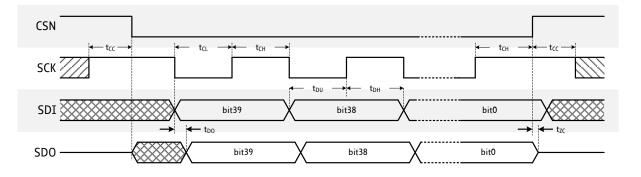

|   | 4.1                                                                                                                                         | SPI DATAGRAM STRUCTURE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 4.2                                                                                                                                         | SPI SIGNALS23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 1 2                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 4.3                                                                                                                                         | TIMING24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5 |                                                                                                                                             | RT SINGLE WIRE INTERFACE25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5 | UAR                                                                                                                                         | RT SINGLE WIRE INTERFACE25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5 | UAR<br>5.1                                                                                                                                  | RT SINGLE WIRE INTERFACE25<br>Datagram Structure25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5 | UAR<br>5.1<br>5.2                                                                                                                           | RT SINGLE WIRE INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5 | UAR<br>5.1<br>5.2<br>5.3                                                                                                                    | RT SINGLE WIRE INTERFACE25DATAGRAM STRUCTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5 | UAR<br>5.1<br>5.2<br>5.3<br>5.4                                                                                                             | RT SINGLE WIRE INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5 | UAR<br>5.1<br>5.2<br>5.3<br>5.4                                                                                                             | RT SINGLE WIRE INTERFACE25DATAGRAM STRUCTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | UAR<br>5.1<br>5.2<br>5.3<br>5.4                                                                                                             | RT SINGLE WIRE INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG                                                                                                      | RT SINGLE WIRE INTERFACE25DATAGRAM STRUCTURE25CRC CALCULATION27UART SIGNALS27ADDRESSING MULTIPLE SLAVES28ISTER MAPPING30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2                                                                                        | RT SINGLE WIRE INTERFACE25DATAGRAM STRUCTURE25CRC CALCULATION27UART SIGNALS27ADDRESSING MULTIPLE SLAVES28ISTER MAPPING30GENERAL CONFIGURATION REGISTERS31VELOCITY DEPENDENT DRIVER FEATURE31N REGISTER SET37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2                                                                                        | RT SINGLE WIRE INTERFACE25DATAGRAM STRUCTURE25CRC CALCULATION27UART SIGNALS27ADDRESSING MULTIPLE SLAVES28ISTER MAPPING30GENERAL CONFIGURATION REGISTERS31VELOCITY DEPENDENT DRIVER FEATURE37RAMP GENERATOR REGISTERS39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2<br>CONTRO                                                                              | RT SINGLE WIRE INTERFACE25DATAGRAM STRUCTURE25CRC CALCULATION27UART SIGNALS27ADDRESSING MULTIPLE SLAVES28ISTER MAPPING30GENERAL CONFIGURATION REGISTERS31VELOCITY DEPENDENT DRIVER FEATURE37RAMP GENERATOR REGISTERS39ENCODER REGISTERS44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2<br>CONTRO<br>6.3                                                                       | RT SINGLE WIRE INTERFACE25DATAGRAM STRUCTURE25CRC CALCULATION27UART SIGNALS27ADDRESSING MULTIPLE SLAVES28ISTER MAPPING30GENERAL CONFIGURATION REGISTERS31VELOCITY DEPENDENT DRIVER FEATURE37RAMP GENERATOR REGISTERS39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2<br>CONTRO<br>6.3<br>6.4<br>6.5                                                         | RT SINGLE WIRE INTERFACE25DATAGRAM STRUCTURE25CRC CALCULATION27UART SIGNALS27ADDRESSING MULTIPLE SLAVES28ISTER MAPPING30GENERAL CONFIGURATION REGISTERS31VELOCITY DEPENDENT DRIVER FEATURE37RAMP GENERATOR REGISTERS39ENCODER REGISTERS44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6 | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2<br>CONTRO<br>6.3<br>6.4<br>6.5<br>STEA                                                 | RT SINGLE WIRE INTERFACE25DATAGRAM STRUCTURE25CRC CALCULATION27UART SIGNALS27ADDRESSING MULTIPLE SLAVES28ISTER MAPPING30GENERAL CONFIGURATION REGISTERS31VELOCITY DEPENDENT DRIVER FEATURE31VELOCITY DEPENDENT DRIVER FEATURE37RAMP GENERATOR REGISTERS39ENCODER REGISTERS44MOTOR DRIVER REGISTERS46ALTHCHOP™56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6 | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2<br>CONTRC<br>6.3<br>6.4<br>6.5<br>STEA<br>7.1                                          | RT SINGLE WIRE INTERFACE       25         DATAGRAM STRUCTURE       25         CRC CALCULATION       27         UART SIGNALS       27         ADDRESSING MULTIPLE SLAVES       28         ISTER MAPPING       30         GENERAL CONFIGURATION REGISTERS       31         VELOCITY DEPENDENT DRIVER FEATURE       37         RAMP GENERATOR REGISTERS       39         ENCODER REGISTERS       44         MOTOR DRIVER REGISTERS       46         ALTHCHOP™       56         AUTOMATIC TUNING       57                                                                                                                                                                                                                                                                                                                                |

| 6 | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2<br>CONTRC<br>6.3<br>6.4<br>6.5<br>STE<br>7.1<br>7.2                                    | RT SINGLE WIRE INTERFACE       25         DATAGRAM STRUCTURE       25         CRC CALCULATION       27         UART SIGNALS       27         ADDRESSING MULTIPLE SLAVES       28         ISTER MAPPING       30         GENERAL CONFIGURATION REGISTERS       31         VELOCITY DEPENDENT DRIVER FEATURE       37         RAMP GENERATOR REGISTERS       39         ENCODER REGISTERS       44         MOTOR DRIVER REGISTERS       46         ALTHCHOP™       56         AUTOMATIC TUNING       57         STEALTHCHOP OPTIONS       59                                                                                                                                                                                                                                                                                           |

| 6 | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2<br>CONTRC<br>6.3<br>6.4<br>6.5<br>STEA<br>7.1<br>7.2<br>7.3                            | RT SINGLE WIRE INTERFACE25DATAGRAM STRUCTURE25CRC CALCULATION27UART SIGNALS27ADDRESSING MULTIPLE SLAVES28ISTER MAPPING30GENERAL CONFIGURATION REGISTERS31VELOCITY DEPENDENT DRIVER FEATURE31Negenserator Registers37RAMP GENERATOR REGISTERS39ENCODER REGISTERS44MOTOR DRIVER REGISTERS46ALTHCHOP™56AUTOMATIC TUNING57STEALTHCHOP CURRENT REGULATOR59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6 | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2<br>CONTRC<br>6.3<br>6.4<br>6.5<br>STE<br>7.1<br>7.2<br>7.3<br>7.4                      | RT SINGLE WIRE INTERFACE       25         DATAGRAM STRUCTURE       25         CRC CALCULATION       27         UART SIGNALS       27         ADDRESSING MULTIPLE SLAVES       28         ISTER MAPPING       30         GENERAL CONFIGURATION REGISTERS       31         VELOCITY DEPENDENT DRIVER FEATURE       37         RAMP GENERATOR REGISTERS       39         ENCODER REGISTERS       44         MOTOR DRIVER REGISTERS       46         ALTHCHOP™       56         AUTOMATIC TUNING       57         STEALTHCHOP OPTIONS       59         STEALTHCHOP CURRENT REGULATOR       59         VELOCITY BASED SCALING       61                                                                                                                                                                                                    |

| 6 | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2<br>CONTRC<br>6.3<br>6.4<br>6.5<br>STEA<br>7.1<br>7.2<br>7.3                            | RT SINGLE WIRE INTERFACE       25         DATAGRAM STRUCTURE       25         CRC CALCULATION       27         UART SIGNALS       27         ADDRESSING MULTIPLE SLAVES       28         ISTER MAPPING       30         GENERAL CONFIGURATION REGISTERS       31         VELOCITY DEPENDENT DRIVER FEATURE       37         RAMP GENERATOR REGISTERS       39         ENCODER REGISTERS       44         MOTOR DRIVER REGISTERS       44         MOTOR DRIVER REGISTERS       56         AUTOMATIC TUNING       57         STEALTHCHOP OPTIONS       59         STEALTHCHOP CURRENT REGULATOR       59         VELOCITY BASED SCALING       61         COMBINING STEALTHCHOP AND SPREADCYCLE.       1                                                                                                                                |

| 6 | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2<br>CONTRC<br>6.3<br>6.4<br>6.5<br>STE<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5               | RT SINGLE WIRE INTERFACE       25         DATAGRAM STRUCTURE       25         CRC CALCULATION       27         UART SIGNALS       27         ADDRESSING MULTIPLE SLAVES       28         ISTER MAPPING       30         GENERAL CONFIGURATION REGISTERS       31         VELOCITY DEPENDENT DRIVER FEATURE       37         RAMP GENERATOR REGISTERS       39         ENCODER REGISTERS       44         MOTOR DRIVER REGISTERS       46         ALTHCHOPTM       56         AUTOMATIC TUNING       57         STEALTHCHOP CURRENT REGULATOR       59         VELOCITY BASED SCALING       61         COMBINING STEALTHCHOP AND SPREADCYCLE.       63                                                                                                                                                                                |

| 6 | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2<br>CONTRC<br>6.3<br>6.4<br>6.5<br>STE<br>7.1<br>7.2<br>7.3<br>7.4                      | RT SINGLE WIRE INTERFACE       25         DATAGRAM STRUCTURE       25         CRC CALCULATION       27         UART SIGNALS       27         ADDRESSING MULTIPLE SLAVES       28         ISTER MAPPING       30         GENERAL CONFIGURATION REGISTERS       31         VELOCITY DEPENDENT DRIVER FEATURE       37         RAMP GENERATOR REGISTERS       39         ENCODER REGISTERS       44         MOTOR DRIVER REGISTERS       44         MOTOR DRIVER REGISTERS       56         AUTOMATIC TUNING       57         STEALTHCHOP OPTIONS       59         STEALTHCHOP CURRENT REGULATOR       59         VELOCITY BASED SCALING       61         COMBINING STEALTHCHOP AND SPREADCYCLE.       1                                                                                                                                |

| 6 | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2<br>CONTRO<br>6.3<br>6.4<br>6.5<br>STE<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7 | RT SINGLE WIRE INTERFACE       25         DATAGRAM STRUCTURE       25         CRC CALCULATION       27         UART SIGNALS       27         ADDRESSING MULTIPLE SLAVES       28         ISTER MAPPING       30         GENERAL CONFIGURATION REGISTERS       31         VELOCITY DEPENDENT DRIVER FEATURE       31         VELOCITY DEPENDENT DRIVER FEATURE       37         RAMP GENERATOR REGISTERS       39         ENCODER REGISTERS       44         MOTOR DRIVER REGISTERS       46         ALTHCHOP™       56         AUTOMATIC TUNING       57         STEALTHCHOP OPTIONS       59         STEALTHCHOP CURRENT REGULATOR       59         VELOCITY BASED SCALING       61         COMBINING STEALTHCHOP AND SPREADCYCLE.       63         FLAGS IN STEALTHCHOP       65         FREEWHEELING AND PASSIVE BRAKING       65 |

| 6 | UAR<br>5.1<br>5.2<br>5.3<br>5.4<br>REG<br>6.1<br>6.2<br>CONTRO<br>6.3<br>6.4<br>6.5<br>STE<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7 | RT SINGLE WIRE INTERFACE25DATAGRAM STRUCTURE25CRC CALCULATION27UART SIGNALS27ADDRESSING MULTIPLE SLAVES28ISTER MAPPING30GENERAL CONFIGURATION REGISTERS31VELOCITY DEPENDENT DRIVER FEATURE31Nederster Set37RAMP GENERATOR REGISTERS39ENCODER REGISTERS44MOTOR DRIVER REGISTERS46ALTHCHOPTM56AUTOMATIC TUNING57STEALTHCHOP CURRENT REGULATOR59VELOCITY BASED SCALING61COMBINING STEALTHCHOP AND SPREADCYCLE.63FLAGS IN STEALTHCHOP65                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9       SELECTING SENSE RESISTORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 8.2  | CLASSIC CONSTANT OFF TIME CHOPPER | 71 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|-----------------------------------|----|

| 11       DIAGNOSTICS AND PROTECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9  | SE   | ELECTING SENSE RESISTORS          | 73 |

| 11.1       TEMPERATURE SENSORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10 | )    | VELOCITY BASED MODE CONTROL       | 75 |

| 11.2       SHORT PROTECTION       77         11.3       OPEN LOAD DIAGNOSTICS       79         12       RAMP GENERATOR       80         12.1       REAL WORLD UNIT CONVERSION       80         12.2       MOTION PROFILES       81         12.3       VELOCITY THRESHOLDS       83         12.4       REFERENCE SWITCHES       84         13       STALLGUARD2 LOAD MEASUREMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11 | L    | DIAGNOSTICS AND PROTECTION        | 77 |

| 11.3       OPEN LOAD DIAGNOSTICS       79         12       RAMP GENERATOR       80         12.1       REAL WORLD UNIT CONVERSION       80         12.2       MOTION PROFILES.       81         12.3       VELOCITY THRESHOLDS       83         12.4       REFERENCE SWITCHES       84         13       STALLGUARD2 LOAD MEASUREMENT       86         13.1       TUNING STALLGUARD2 THRESHOLD SGT       87         13.2       STALLGUARD2 UPDATE RATE AND FILTER       89         13.3       DETECTING A MOTOR STALL       89         13.4       HOMING WITH STALLGUARD       89         13.5       LIMITS OF STALLGUARD2 OPERATION       89         14.4       COOLSTEP OPERATION       90         14.1       USER BENEFITS.       90         14.2       SETTING UP FOR COOLSTEP       91         15.3       TUNING COOLSTEP       92         15       STEP/DIR INTERFACE       93         15.2       CHANGING RESOLUTION       94         15.3       MICROPLYER AND STAND STILL DETECTION .95       96         16.1       STEP/DIR MODE       96         15.2       CHANGING RESOLUTION       96         15.3       MICRO          |    |      |                                   |    |

| 12       RAMP GENERATOR       80         12.1       REAL WORLD UNIT CONVERSION       80         12.2       MOTION PROFILES       81         12.3       VELOCITY THRESHOLDS       83         12.4       REFERENCE SWITCHES       84         13       STALLGUARD2 LOAD MEASUREMENT       86         13.1       TUNING STALLGUARD2 THRESHOLD SGT       87         13.2       STALLGUARD2 UPDATE RATE AND FILTER       89         13.3       DETECTING A MOTOR STALL       89         13.4       HOMING WITH STALLGUARD       89         13.5       LIMITS OF STALLGUARD2 OPERATION       89         14.4       COOLSTEP OPERATION       90         14.1       USER BENEFITS       90         14.2       SETTING UP FOR COOLSTEP       90         14.3       TUNING COOLSTEP       92         15       STEP/DIR INTERFACE       93         15.2       CHANGING RESOLUTION       94         15.3       MICROPLYER AND STAND STILL DETECTION .95       96         16.1       STEP/DIR MODE       96         15.2       CHANGING RESOLUTION       96         15.3       MICROPLYER AND STAND STILL DETECTION .95         16       DIAG OUT |    |      |                                   |    |

| 12.2       MOTION PROFILES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12 | -    |                                   |    |

| 12.2       MOTION PROFILES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 12.1 | REAL WORLD UNIT CONVERSION        | 80 |

| 12.4       REFERENCE SWITCHES       84         13       STALLGUARD2 LOAD MEASUREMENT86         13.1       TUNING STALLGUARD2 THRESHOLD SGT87         13.2       STALLGUARD2 UPDATE RATE AND FILTER89         13.3       DETECTING A MOTOR STALL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 12.2 | MOTION PROFILES                   | 81 |

| 13       STALLGUARD2 LOAD MEASUREMENT86         13.1       TUNING STALLGUARD2 THRESHOLD SGT87         13.2       STALLGUARD2 UPDATE RATE AND FILTER89         13.3       DETECTING A MOTOR STALL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | -    |                                   |    |

| 13.1       TUNING STALLGUARD2 THRESHOLD SGT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13 | •    |                                   |    |

| 13.2STALLGUARD2UPDATERATEANDFILTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |      |                                   |    |

| 13.4HOMING WITH STALLGUARD.8913.5LIMITS OF STALLGUARD2 OPERATION8914COOLSTEP OPERATION9014.1USER BENEFITS.9014.2SETTING UP FOR COOLSTEP9014.3TUNING COOLSTEP.9215STEP/DIR INTERFACE.9315.1TIMING.9315.2CHANGING RESOLUTION9415.3MICROPLYER AND STAND STILL DETECTION .9516DIAG OUTPUTS9616.1STEP/DIR MODE9616.2MOTION CONTROLLER MODE9617DCSTEP9817.1USER BENEFITS.9817.2DESIGNING-IN DCSTEP9817.3DCSTEP INTEGRATION WITH THE MOTION<br>CONTROLLER9917.4STALL DETECTION IN DCSTEP MODE9917.5MEASURING ACTUAL MOTOR VELOCITY IN<br>DCSTEP OPERATION10017.6DCSTEP WITH STEP/DIR INTERFACE10118SINE-WAVE LOOK-UP TABLE10418.1USER BENEFITS.10418.2MICROSTEP TABLE10419EMERGENCY STOP10520ABN INCREMENTAL ENCODER106                                                                                                                                                                                                                                                                                                                                                                                                                    |    | -    |                                   |    |

| 13.5LIMITS OF STALLGUARD2 OPERATION8914COOLSTEP OPERATION9014.1USER BENEFITS.9014.2SETTING UP FOR COOLSTEP9014.3TUNING COOLSTEP9215STEP/DIR INTERFACE9315.1TIMING9315.2CHANGING RESOLUTION9415.3MICROPLYER AND STAND STILL DETECTION .9516DIAG OUTPUTS9616.1STEP/DIR MODE9616.2MOTION CONTROLLER MODE9617DCSTEP9817.1USER BENEFITS.9817.2DESIGNING-IN DCSTEP9817.3DCSTEP INTEGRATION WITH THE MOTION<br>CONTROLLER9917.4STALL DETECTION IN DCSTEP MODE9917.5MEASURING ACTUAL MOTOR VELOCITY IN<br>DCSTEP OPERATION10017.6DCSTEP WITH STEP/DIR INTERFACE10118SINE-WAVE LOOK-UP TABLE10418.1USER BENEFITS.10418.2MICROSTEP TABLE10419EMERGENCY STOP10520ABN INCREMENTAL ENCODER<br>INTERFACE106                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |      |                                   |    |

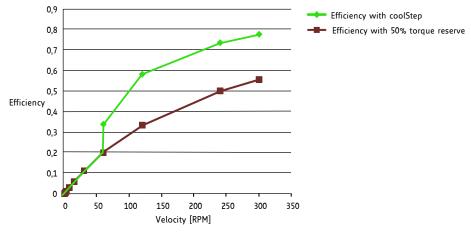

| 14COOLSTEP OPERATION9014.1USER BENEFITS.9014.2SETTING UP FOR COOLSTEP9014.3TUNING COOLSTEP9215STEP/DIR INTERFACE9315.1TIMING9315.2CHANGING RESOLUTION9415.3MICROPLYER AND STAND STILL DETECTION.9516DIAG OUTPUTS9616.1STEP/DIR MODE9616.2MOTION CONTROLLER MODE9617DCSTEP9817.1USER BENEFITS.9817.2DESIGNING-IN DCSTEP9817.3DCSTEP INTEGRATION WITH THE MOTION<br>CONTROLLER9917.4STALL DETECTION IN DCSTEP MODE9917.5MEASURING ACTUAL MOTOR VELOCITY IN<br>DCSTEP OPERATION10017.6DCSTEP WITH STEP/DIR INTERFACE10118SINE-WAVE LOOK-UP TABLE10418.1USER BENEFITS.10418.2MICROSTEP TABLE10419EMERGENCY STOP10520ABN INCREMENTAL ENCODER106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |      |                                   |    |

| 14.2       SETTING UP FOR COOLSTEP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1/ |      |                                   |    |

| 14.2       SETTING UP FOR COOLSTEP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 14.1 | User Benefits                     | 90 |

| 15       STEP/DIR INTERFACE       93         15.1       TIMING       93         15.2       CHANGING RESOLUTION       94         15.3       MICROPLYER AND STAND STILL DETECTION .95         16       DIAG OUTPUTS       96         16.1       STEP/DIR MODE       96         16.2       MOTION CONTROLLER MODE       96         17       DCSTEP       98         17.1       USER BENEFITS       98         17.2       DESIGNING-IN DCSTEP       98         17.3       DCSTEP INTEGRATION WITH THE MOTION       CONTROLLER         CONTROLLER       99       99       17.4       STALL DETECTION IN DCSTEP MODE       99         17.4       STALL DETECTION IN DCSTEP MODE       99       17.5       MEASURING ACTUAL MOTOR VELOCITY IN         DCSTEP OPERATION       IO0       17.6       DCSTEP WITH STEP/DIR INTERFACE       100         17.6       DCSTEP WITH STEP/DIR INTERFACE       104       18.1       USER BENEFITS       104         18.1       USER BENEFITS       104       104       19       EMERGENCY STOP       105         20       ABN INCREMENTAL ENCODER       106       106       106       106              |    |      | SETTING UP FOR COOLSTEP           | 90 |