Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## TMC8670 Datasheet

Hardware Version V1.0 | Document Revision V1.00 • 2018-June-11

The TMC8670 is a CANopen-over EtherCAT (CoE) field oriented control (FOC) servo controller for torque, velocity, and position control. It comes with a fully integrated EtherCAT Slave Controller (ESC), a flexible sensor engine for different position feedback and current sensing options, as well as a complete CANopen-over-EtherCAT firmware stack for the CiA DS402 device profile. TMC8670 is a building block that enables a servo controller with only a couple of components.

#### **Features**

- Field Oriented Control (FOC) Servo Controller

- Torque Control (FOC), Velocity Control, Position Control

- Sensor Engine (Hall analog/digital, Encoder analog/digital)

- Support for 3-Phase PMSM and 2-Phase Stepper Motors

- PWM Engine including SVPWM

- Integrated EtherCAT Slave Controller, CoE protocol CiA 402 drive profile

- UART interface

## **Applications**

- Robotics

- Semiconductor Handling

- Factory Automation

- Laboratory Automation

- Manufacturing

- IIoT Applications

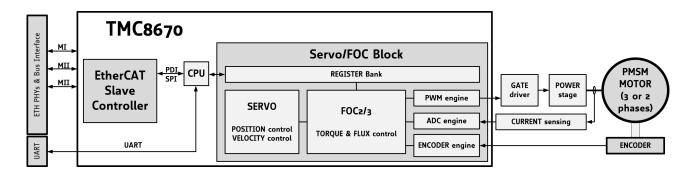

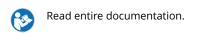

## Simplified Block Diagram

©2018 TRINAMIC Motion Control GmbH & Co. KG, Hamburg, Germany Terms of delivery and rights to technical change reserved. Download newest version at: www.trinamic.com

## **Contents**

| 1 | Product Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                                                      |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 2 | Order Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                                      |

| 3 | Principles of Operation / Key Concepts 3.1 General Device Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8                                                                                      |

| 4 | Device Pin Definitions 4.1 Pinout and Pin Coordinates of TMC8670-BA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                        |

| 5 | Device Usage and Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20                                                                                     |

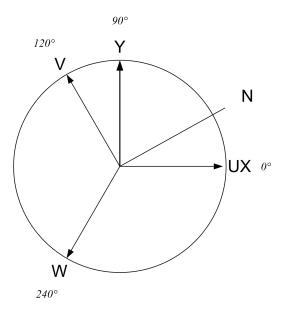

|   | <ul> <li>5.1 Reference Clock</li> <li>5.2 Ethernet PHY Connection</li> <li>5.3 External Circuitry and Applications Examples</li> <li>5.3.1 Supply and Filtering</li> <li>5.3.2 Status LED Circuit</li> <li>5.3.3 SII EEPROM Circuit</li> <li>5.4 Incremental Encoder Connection</li> <li>5.4.1 Incremental ABN Encoder</li> <li>5.4.2 Secondary Incremental ABN Encoder</li> <li>5.4.3 Open Loop Encoder</li> <li>5.4.3 Open Loop Encoder</li> <li>5.5.1 Digital Hall Sensor Interface with optional Interim Position Interpolation</li> <li>5.5.2 Digital Hall Sensor - Interim Position Interpolation</li> <li>5.5.3 Digital Hall Sensors together with Incremental Encoder</li> <li>5.6 ADC Interfaces</li> <li>5.6.1 ADC Interface - Delta Sigma Modulator</li> <li>5.6.2 ADC Interface - SPI ADC</li> <li>5.6.3 Analog Hall and Analog Encoder Interface (SinCos of 0°90° or 0°120°240°)</li> <li>5.6.4 Analog Position Decoder (SinCos of 0°90° or 0°120°240°)</li> <li>5.7 Brake Chopper Connection</li> <li>5.8 Debug UART Connections</li> <li>5.8.1 UART Hardware Debug Interface</li> </ul> | 20<br>22<br>22<br>23<br>24<br>26<br>26<br>27<br>28<br>28<br>29<br>30<br>31<br>31<br>31 |

| 6 | FOC Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34                                                                                     |

|   | <ul> <li>6.1 Why FOC?</li> <li>6.2 What is FOC?</li> <li>6.3 Why FOC as pure Hardware Solution?</li> <li>6.4 How does FOC work?</li> <li>6.5 What is required for FOC?</li> <li>6.5.1 Coordinate Transformations - Clarke, Park, iClarke iPark</li> <li>6.5.2 Measurement of Stator Coil Currents</li> <li>6.5.3 Stator Coil Currents I_U, I_V, I_W and Association to Terminal Voltages U_U, U_V, U_W</li> <li>6.5.4 Measurement of Rotor Angle</li> <li>6.5.5 Measured Rotor Angle vs. Magnetic Axis of Rotor vs. Magnetic Axis ot Stator</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 34<br>35<br>35<br>36<br>36<br>36<br>37                                                 |

|   | 6.6  | <ul> <li>6.5.6 Knowledge of Relevant Motor Parameters and Position Sensor (Encoder) Parameters</li> <li>6.5.7 Proportional Integral (PI) Controllers for Closed Loop Current Control</li> <li>6.5.8 Pulse Width Modulation (PWM) and Space Vector Pulse Width Modulation (SVPWM)</li> <li>6.5.9 Orientations, Models of Motors, and Coordinate Transformations</li> <li>FOC23 Engine</li> <li>6.6.1 PI Controllers</li> <li>6.6.2 PI Controller Calculations - Classic Structure</li> <li>6.6.3 PI Controller Calculations - Advanced Structure</li> <li>6.6.4 PI Controller - Clipping</li> <li>6.6.5 PI Flux &amp; PI Torque Controller</li> <li>6.6.6 PI Velocity Controller</li> <li>6.6.7 P Position Controller</li> <li>6.6.8 Inner FOC Control Loop - Flux &amp; Torque</li> <li>6.6.9 FOC Transformations and PI(D) for control of Flux &amp; Torque</li> <li>6.6.10 Motion Modes</li> </ul> | 38<br>39<br>39<br>40<br>40<br>41<br>42<br>43<br>43 |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 7 | Ethe | erCAT Slave Controller Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46                                                 |

|   | 7.1  | General EtherCAT Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46                                                 |

|   | 7.2  | EtherCAT Register Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    |

|   | 7.3  | EtherCAT Register Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53                                                 |

|   |      | 7.3.1 ESC Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |

|   |      | 7.3.2 Station Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |

|   |      | 7.3.3 Write Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |

|   |      | 7.3.4 Data Link Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |

|   |      | 7.3.5 Application Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |

|   |      | 7.3.7 Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |

|   |      | 7.3.8 Error Counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                    |

|   |      | 7.3.9 Watchdogs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |

|   |      | 7.3.10 SII EEPROM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    |

|   |      | 7.3.11 MII Management Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |

|   |      | 7.3.12 FMMUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |

|   |      | 7.3.13 SyncManagers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |

|   |      | 7.3.14 Distributed Clocks Receive Times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |

|   |      | 7.3.15 Distributed Clocks Time Loop Control Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |

|   |      | 7.3.16 Distributed Clocks Cyclic Unit Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

|   |      | 7.3.17 Distributed Clocks SYNC Out Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |

|   |      | 7.3.18 Distributed Clocks LATCH In Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |

|   |      | 7.3.20 ESC Specific                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |

|   |      | 7.3.21 Process Data RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |

| 8 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12                                                 |

|   | 8.1  | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    |

|   | 8.2  | Operational Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12                                                 |

|   | 8.3  | Digital I/Os                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |

|   |      | Package Thermal Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    |

|   | 0.5  | Tuckage memai behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |

| 9 | Mar  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                 |

|   | 9.1  | Package Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |

|   | 9.2  | Marking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |

|   | 9.3  | Board and Layout Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17                                                 |

**10 Abbreviations**

| 11 Figures Index       | 120 |

|------------------------|-----|

| 12 Tables Index        | 121 |

| 13 Revision History    | 123 |

| 13.1 IC Revision       | 123 |

| 13.2 Document Revision | 123 |

## 1 Product Features

TMC8670 is a highly integrated SoC providing the interface between an EtherCAT real-time field bus and the local drive application. It includes the real-time MAC layer for EtherCAT, the application software stack for the CiA DS402 CANopen device profile, and the complete servo control block in dedicated hardware with interfaces to ADCs and position feedback.

TMC8670 offers an extremely high function density in a small scale package.

#### **Advantages:**

- Fully standard compliant and proven EtherCAT Slave Controller and State Machine

- Highly integrated Servo Controller with rich feature set vs. package size

- · Robust silicon technology

- · Saves board space & reduces BOM

- Long-term availability

### **Major Features:**

- Integrated EtherCAT Slave Controller with 2 MII ports for Ethernet bus interfacing

- Complete firmware stack with EtherCAT State Machine and CANopen over EtherCAT stack based on CiA DS402 device profile

- Firmware update via EtherCAT or via UART

- Fully integrated hardware servo controller with field-oriented control and rich interface support

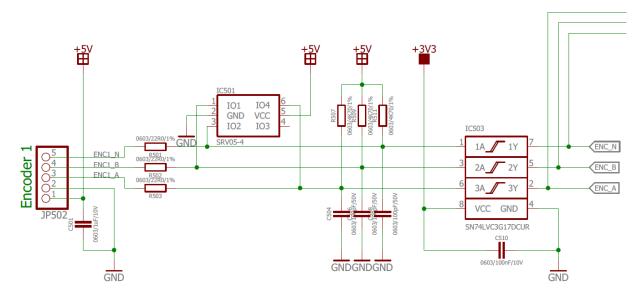

- Two digital incremental encoder interfaces

- Analog SinCos encoder interface

- · Digital hall sensor interface

- · Analog hall sensor interface

- Flexible ADC interface to connect to external SPI ADCs or delta sigma modulators

- Industrial temperature range -40°C to +125°C

- Package: 325-pin BGA chip scale package with 0.5mm pitch, 11mm x 11mm

## 2 Order Codes

| Order Code   | Description                                                                                                             | Size        |

|--------------|-------------------------------------------------------------------------------------------------------------------------|-------------|

| TMC8670-BI   | TMC8670 Advanced EtherCAT® Servo Controller in 325-pin BGA chip scale package with 0.5mm pitch                          | 11mm x 11mm |

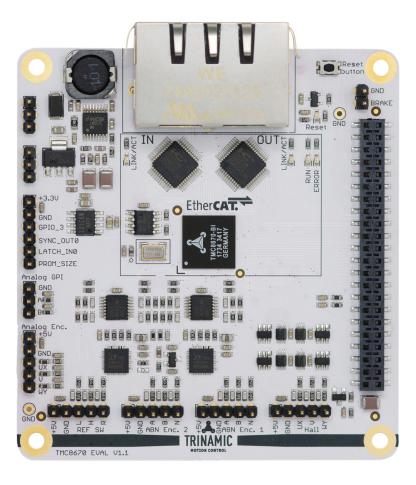

| TMC8670-EVAL | Evaluation Board for TMC8670-BI, compatible with the modular Landungsbruecke system, RJ45 twisted pair copper interface | 79mm x 85mm |

Table 1: TMC8670 order codes

### **Trademark and Patents**

EtherCAT® is a registered trademark and patented technology, licensed by Beckhoff Automation GmbH, Germany.

## 3 Principles of Operation / Key Concepts

## 3.1 General Device Architecture

Figure 1 shows the general device architecture and major connections of TMC8670.

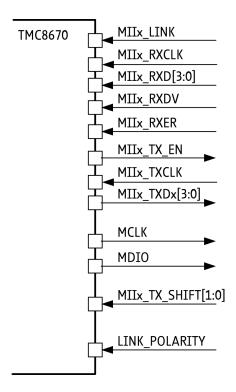

The EtherCAT Slave Controller (ESC) is realized in dedicated logic and provides two MII interfaces to external Ethernet PHYs suitable for EtherCAT.

The ESC connects to the integrated microcontroller, which executes the EtherCAT State Machine (ESM) and the CiA DS402 CANopen protocol stack. A debug UART interface connects to the MCU for debugging and firmware updates.

The firmware in the MCU controls the servo and field-oriented control (FOC) block, which is completely realized in dedicated logic. All PI-loops for position, velocity, and torque are fully configurable.

The FOC block drives external gate driver, which in turn are switching a power stage for 3-phase brushless motors or 2-phase stepper motors.

The FOC block provides a set of interfaces for different types of current sensing and position feedback. Current sensing and encoders are external components to the TMC8670.

Figure 1: General device architecture

### 3.2 EtherCAT Slave Controller

TMC8670 contains a standard-conform and proven ESC engine providing real-time EtherCAT MAC layer functionality to EtherCAT slaves. It connects via MII interface to standard Ethernet PHYs and provides a digital control interface to a local application controller

The ESC part of TMC8670 provides the following EtherCAT-related features. More information is available in Section 7.

- Two MII interfaces to external Ethernet PHYs plus management interface

- Four Fieldbus Memory Management Units (FMMU)

- Four Sync Managers (SM)

- 4 KByte of Process Data RAM (PDRAM)

- · 64 bit Distributed Clocks support

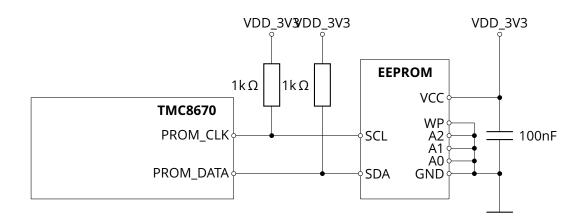

- IIC interface for an external SII-EEPROM for ESC configuration

## 3.3 Microcontroller and Firmware Stack

The integrated microcontroller system contains and controls the application layer of TMC8670. Thereby, the firmware is split up into a bootloader section and the application layer section. The bootloader allows

for future firmware updates. The application layer comprises the ESM to communicate with the ESC and the CANopen-over-EtherCAT (CoE) protocol stack. The CoE stack is based on the CiA DS402 device profile for drives. It controls the hardware servo/FOC controller block. The application layer also supports File-Transfer-over-EtherCAT (FoE), which is used for remote firmware updates via the EtherCAT master.

#### 3.4 Servo/FOC Controller

The integrated servo/FOC controller is completely realized in dedicated logic. Its control registers are directly mapped into the microcontrollers address space. It offloads the microcontroller from the repetitive and time-consuming computation tasks of control loop processing, FOC Park and Clark transformations, PWM generation, and interfacing to ADCs and position feedback. The servo/FOC controller supports PWM frequencies and current loop frequencies of up to 100kHZ. It not only supports 3-phase brushless motors but also 2-phase stepper motors and single phase motors, for example DC motors.

More information is given the FOC Basics Section.

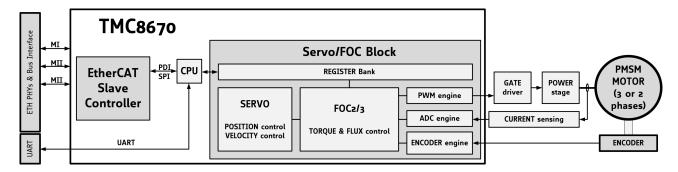

### 3.5 Flexible Sensor Engine

A versatile and flexible sensor engine is part of the servo/FOC controller block of TMC8670. The sensor engine handles digital hall sensors, digital incremental encoders, analog hall sensors, and analog sin-cossensors. Together with the relevant sensor parameters, it maps the measured sensor position to 16 bit signed values (s16) for the FOC engine.

Figure 2: TMC8670 Sensor Engine maps position sensor signals to mechanical angels and electrical angels as direct input for the FOC engine.

**ADC Interfaces** The TMC8670 is a pure digital IC with interfaces for external ADCs. As ADC one can either select LTC2351 from Linear Technology or Delta Sigma Modulators (AD7401). As an alternative to Delta Sigma Modulators, the TMC8670 supports low cost comparators (e.g. LM339) together with some passive components to form delta sigma modulators.

**Digital Encoder Interfaces** The digital encoder interface support a wide range of encoders with different resolutions, signal polarities and zero pulses.

**Analog Encoder Interfaces** The analog encoder interface is for analog hall signals - two phase SinCos or three phase - and for analog (incremental) encoders. An interpollator for SinCos encoders is integrated.

**Digital Hall Sensor Interface** The digital hall signal interface enables digital hall signals for initialization of incremental encoders. The digital hall signal interface can be used directly for the FOC. For torque ripple reduction an interpolator for the digital hall signals is integrated.

**Analog Hall Sensor Interface** The interface for analog hall signals is the same interface as available for SinCos analog encoders.

#### 3.6 Communication Interfaces

**Field Bus Interface** TMC8670 provides two MII ports to connect to 100-Mbit Ethernet PHYs that connect to the field bus. One port is the dedicated EtherCAT IN port. The second port is the dedicated EtherCAT OUT port. Depending on the physical medium (twisted pair copper or passive optical fiber) an external transformer circuit connects to the RX and TX lines.

**IIC SII EEPROM Interface** The IIC EEPROM interface is intended to be a point-to-point interface between TMC8670 and the SII EEPROM with TMC8670 being the master. Depending on the EEPROM's capacity the addressing mode must be properly set using the PROM\_SIZE configuration pin.

Configuration of the EtherCAT Slave Controller is done during boot time with configuration information read from the SII EEPROM after reset or power cycling. This information must be (pre)programmed into the SII EEPROM. This can be done via the EtherCAT master using a so-called EtherCAT Slave Information (ESI) file in standardized XML format.

**Debug UART Interfaces** TMC8670 has two UART interfaces that allow for basic local debugging. The MCU UART directly connects to the microcontroller and can also be used for local firmware updates. The HW UART directly connects to the servo/FOC controller block and allows for direct control via register read/write of this function block alone. This is usable for local tuning, monitoring of the registers, and debugging.

More details on the two debug UART interfaces are given in the Debug UARTs' section

## 3.7 Software- and Tool-Support

**Evaluation Board** An evaluation board is available for the TMC8670 with standard RJ45 connectors and transformers for interfacing twisted pair copper media.

Figure 3: TMC8670 Evaluation Board

The complete board design files are available for download and can be used as reference. All information is available for download on the specific product page on TRINAMIC's website at <a href="https://www.trinamic.com/support/eval-kits/">https://www.trinamic.com/support/eval-kits/</a>.

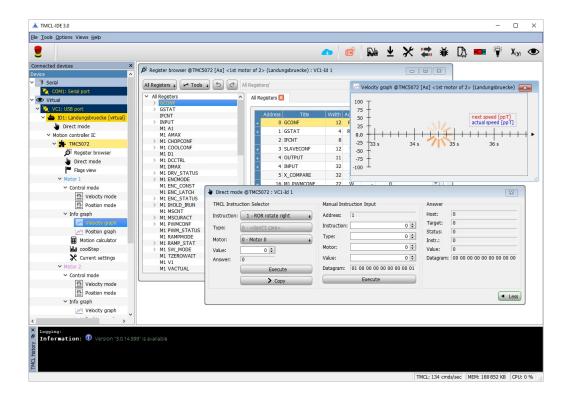

**TMCL-IDE** The TMCL-IDE is TRINAMIC's primary tool (for Windows PCs) to control TRINAMIC modules and evaluation boards. Besides, it provides feature like remote firmware updates, module monitoring options, and specific Wizard support. The TMCL-IDE can be used along with TRINAMIC's modular evaluation board system.

### 1 Info

The TMLC-IDE is not an EtherCAT master system!

The TMC8670-EVAL can be accessed via the UART interface of the evaluation board to try out the servo functions without using an EtherCAT master in the first place.

Figure 4: TMCL-IDE

The latest version and additional information is available for download from TRINAMIC's website at <a href="https://www.trinamic.com/support/software/tmcl-ide/">https://www.trinamic.com/support/software/tmcl-ide/</a>.

## 4 Device Pin Definitions

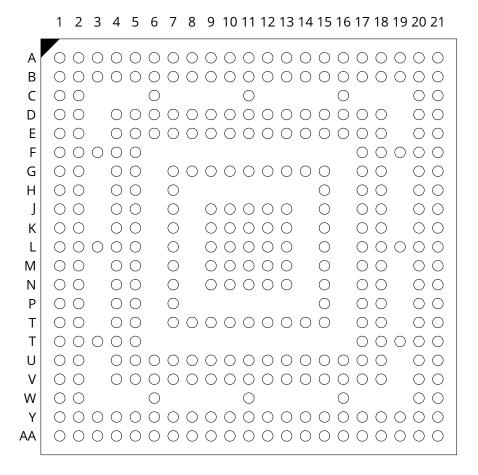

## 4.1 Pinout and Pin Coordinates of TMC8670-BA

Figure 5: TMC8670-BI Pinout top view

## 4.2 Pin Numbers and Signal Descriptions

Pins not listed in the following table are N.C. (not connected). Pin types are I = input, O = output, PU = has pull-up, PD = has pull-down.

| Name            | Pin | Туре | Function                                                                                                                          |

|-----------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------|

| General Signals |     |      |                                                                                                                                   |

| NRESET          | M9  | I    | Low active system reset, pull up to VDD_3V3 with 10K                                                                              |

| CLK_25MHZ       | P1  | I    | 25MHz Reference Clock Input, connect to clock source with <25ppm or better, typically same clock source as used for the ETH PHYs. |

| CLKOUT_25MHZ    | H17 | 0    |                                                                                                                                   |

| Name                   | Pin | Туре  | Function                                                                                                                                                                                                                                                         |

|------------------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EtherCAT SII EEPROM IC | )s  |       |                                                                                                                                                                                                                                                                  |

| PROM_CLK               | F1  | 0     | External IIC SII EEPROM clock signal, use 1K pull up resistor to VDD_3V3                                                                                                                                                                                         |

| PROM_DATA              | F2  | 1/0   | External IIC SII EEPROM data signal, <b>use 1k pull up</b> resistor to VDD_3V3                                                                                                                                                                                   |

| PROM_SIZE              | K1  | I, PU | Selects between two different EEPROM sizes since the communication protocol for SII EEPROM access changes if a size > 16kBit is used (an additional address byte is required then). 0 = up to 16kBit EEPROM, 1 = 32 kBit-4Mbit EEPROM, has weak internal pull-up |

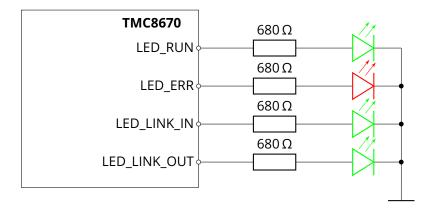

| EtherCAT Status LEDs | EtherCAT Status LEDs |   |                                                                                             |  |  |

|----------------------|----------------------|---|---------------------------------------------------------------------------------------------|--|--|

| LED_RUN              | D1                   | 0 | ESM Run Status LED, connect to green LED (Anode) 0 = LED off, 1 = LED on                    |  |  |

| LED_ERR              | D2                   | 0 | ESM Error Status LED, connect to red LED (Anode) 0 = LED off, 1 = LED on                    |  |  |

| LED_LINK_IN          | E1                   | 0 | ETH Link In Port Status and Activity, connect to green LED (Anode) 0 = LED off, 1 = LED on  |  |  |

| LED_LINK_OUT         | F3                   | 0 | ETH Link Out Port Status and Activity, connect to green LED (Anode) 0 = LED off, 1 = LED on |  |  |

| Distributed Clocks Synchronization |    |       |                                                             |  |

|------------------------------------|----|-------|-------------------------------------------------------------|--|

| LATCH_IN0                          | K2 | I, PD | Distributed Clocks Latch Input, has weak internal pull-down |  |

| SYNC_OUT0                          | K4 | 0     | Distributed Clocks Synchronization Output                   |  |

| Name Pin Type | Function |  |

|---------------|----------|--|

|---------------|----------|--|

| MII Interface to external ETH PHY (EtherCAT IN Port) |     |   |                           |  |  |

|------------------------------------------------------|-----|---|---------------------------|--|--|

| MII1_LINK                                            | F18 | I | Link indication input     |  |  |

| MII1_RXCLK                                           | G18 | I | Receive clock             |  |  |

| MII1_RXD[0]                                          | F19 | I | Receive data bit 0        |  |  |

| MII1_RXD[1]                                          | F20 | I | Receive data bit 1        |  |  |

| MII1_RXD[2]                                          | E21 | I | Receive data bit 2        |  |  |

| MII1_RXD[3]                                          | E20 | I | Receive data bit 3        |  |  |

| MII1_RXDV                                            | G21 | I | Receive data valid signal |  |  |

| MII1_RXER                                            | G20 | I | Receive error signal      |  |  |

| MII1_TXCLK                                           | E18 | I | Transmit clock            |  |  |

| MII1_TXD[0]                                          | D21 | 0 | Transmit data bit 0       |  |  |

| MII1_TXD[1]                                          | C21 | 0 | Transmit data bit 1       |  |  |

| MII1_TXD[2]                                          | C20 | 0 | Transmit data bit 2       |  |  |

| MII1_TXD[3]                                          | B21 | 0 | Transmit data bit 3       |  |  |

| MII1_TX_EN                                           | E17 | 0 | Transmit enable           |  |  |

| MII Interface to external ETH PHY (EtherCAT OUT Port) |     |   |                           |  |  |

|-------------------------------------------------------|-----|---|---------------------------|--|--|

| MII2_LINK                                             | K18 | I | Link indication input     |  |  |

| MII2_RXCLK                                            | L18 | I | Receive clock             |  |  |

| MII2_RXD[0]                                           | N21 | I | Receive data bit 0        |  |  |

| MII2_RXD[1]                                           | M20 | I | Receive data bit 1        |  |  |

| MII2_RXD[2]                                           | L20 | I | Receive data bit 2        |  |  |

| MII2_RXD[3]                                           | L21 | I | Receive data bit 3        |  |  |

| MII2_RXDV                                             | N20 | 1 | Receive data valid signal |  |  |

| MII2_RXER                                             | M18 | I | Receive error signal      |  |  |

| MII2_TXCLK                                            | J17 | I | Transmit clock            |  |  |

| MII2_TXD[0]                                           | L19 | 0 | Transmit data bit 0       |  |  |

| MII2_TXD[1]                                           | K21 | 0 | Transmit data bit 1       |  |  |

| MII2_TXD[2]                                           | J20 | 0 | Transmit data bit 2       |  |  |

| MII2_TXD[3]                                           | J21 | 0 | Transmit data bit 3       |  |  |

| MII2_TX_EN                                            | J18 | 0 | Transmit enable           |  |  |

| Name                                                          | Pin      | Туре  | Function                                                                                                      |  |  |  |

|---------------------------------------------------------------|----------|-------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| ETH PHY Interface Configuration Pins and Management Interface |          |       |                                                                                                               |  |  |  |

| LINK_POLARITY                                                 | R9       | I, PD | selects polarity of the ETH PHYs link signal: 0 = low active, 1 = high active                                 |  |  |  |

| MII1_TX_SHIFT[0]                                              | K15      | 1     | Used for clock shift compensation on TX port                                                                  |  |  |  |

| MII1_TX_SHIFT[1]                                              | K17      | 1     | Used for clock shift compensation on TX port                                                                  |  |  |  |

| MII2_TX_SHIFT[0]                                              | L15      | I     | Used for clock shift compensation on TX port                                                                  |  |  |  |

| MII2_TX_SHIFT[1]                                              | L17      | I     | Used for clock shift compensation on TX port                                                                  |  |  |  |

| MCLK                                                          | H20      | 0     | PHY management clock, connect all ETH PHYs to this bus                                                        |  |  |  |

| MDIO                                                          | H21      | 1/0   | PHY management data, connect all ETH PHYs to this bus if required, <b>use 4K7 pull up resistor to VDD_3V3</b> |  |  |  |

| Motor Position Feedba                                         | ck Signa | ıls   |                                                                                                               |  |  |  |

| ENC_A                                                         | N1       | I, PU | incremental encoder signal A                                                                                  |  |  |  |

| ENC_B                                                         | N2       | I, PU | incremental encoder signal B                                                                                  |  |  |  |

| ENC_N                                                         | P2       | I, PU | incremental encoder null pulse N                                                                              |  |  |  |

| ENC_2_A                                                       | V6       | I, PU | 2nd incremental encoder signal A                                                                              |  |  |  |

| ENC_2_B                                                       | V7       | I, PU | 2nd incremental encoder signal B                                                                              |  |  |  |

| ENC_2_N                                                       | W6       | I, PU | 2nd incremental encoder null pulse N                                                                          |  |  |  |

| HALL_UX                                                       | M4       | I, PU | digital Hall signal associated to U (H1)                                                                      |  |  |  |

| HALL_V                                                        | N4       | I, PU | digital Hall signal associated to V (H2)                                                                      |  |  |  |

| HALL_WY                                                       | P4       | I, PU | digital Hall signal associated to W (H1)                                                                      |  |  |  |

| ENC_ADC_CSN                                                   | L3       | 0     | analog encoder SPI ADC LTC2351 CONV                                                                           |  |  |  |

| ENC_ADC_MISO                                                  | L1       | I     | analog encoder SPI ADC LTC2351 SDO                                                                            |  |  |  |

| ENC_ADC_SCK                                                   | L2       | 0     | analog encoder SPI ADC LTC2351 SCK                                                                            |  |  |  |

| Reference Switch Signals |    |       |                        |

|--------------------------|----|-------|------------------------|

| REF_SW_H                 | H5 | I, PU | Home Reference Switch  |

| REF_SW_L                 | H4 | I, PU | Left Reference Switch  |

| REF_SW_R                 | J4 | I, PU | Right Reference Switch |

| Name                   | Pin     | Туре            | Function                                                          |

|------------------------|---------|-----------------|-------------------------------------------------------------------|

| Motor and Supply Curre | ent Mea | asurement Signa | ls                                                                |

| SPI_ADC_CSN            | U8      | 0               | analog current measurement SPI ADC LTC2351 CONV                   |

| SPI_ADC_SCK            | U9      | 0               | analog current measurement SPI ADC LTC2351 SCK                    |

| SPI_ADC_MISO           | U10     | I, PU           | analog current measurement SPI ADC LTC2351 SDO                    |

| ADC_PHASE_MISO_2ND     | U11     | I, PU           | analog current measurement SPI ADC LTC2351 SDO                    |

| MCLK_AENC_UX           | P5      | Ю               | DS-Mod Clock analog encoder/analog Hall U or X                    |

| MCLK_AENC_VN           | R4      | 10              | DS-Mod Clock analog encoder/analog Hall V or N                    |

| MCLK_AENC_WY           | U4      | 10              | DS-Mod Clock analog encoder/analog Hall W or Y                    |

| MCLK_AGPI_A            | T2      | Ю               | DS-Mod Clock for Analog General Purpose Input AGPI_A              |

| MCLK_AGPI_B            | U2      | IO              | DS-Mod Clock for Analog General Purpose Input AGPI_B              |

| MCLK_I_UX              | V1      | Ю               | DS-Mod Clock for Analog Current Sense Voltage of I_U or I_X       |

| MCLK_I_WY              | AA2     | 10              | DS-Mod Clock for Analog Current Sense Voltage of I_W or I_Y       |

| MCLK_VM                | ТЗ      | 10              | DS-Mod Clock for (down-divided) motor supply voltage of V_M       |

| MDAT_AENC_UX           | R5      | I               | DS-Mod Data Stream for analog encoder/analog Hall U or X          |

| MDAT_AENC_VN           | T5      | I               | DS-Mod Data Stream for analog encoder/analog Hall V or N          |

| MDAT_AENC_WY           | U5      | I               | DS-Mod Data Stream for analog encoder/analog Hall W or Y          |

| MDAT_AGPI_A            | T1      | 1               | DS-Mod Data Stream for Analog General Purpose Input AGPI_A        |

| MDAT_AGPI_B            | U1      | 1               | DS-Mod Data Stream for Analog General Purpose Input AGPI_B        |

| MDAT_I_UX              | W1      | I               | DS-Mod Data Stream for Analog Current Sense Voltage of I_U or I_X |

| MDAT_I_WY              | W2      | 1               | DS-Mod Clock for Analog Current Sense Voltage of I_W or I_Y       |

| MDAT_I_UX_2ND          | Y1      | I, PU           | DS-Mod Data stream for Analog Current Sense Voltage of I_U or I_X |

| MDAT_I_WY_2ND          | Y2      | I, PU           | DS-Mod Data stream for Analog Current Sense Voltage of I_W or I_Y |

| MDAT_VM                | R2      | I               | DS-Mod Data stream for (down-divided) motor supply voltage of V_M |

| Name        | Pin  | Туре | Function                                                                 |

|-------------|------|------|--------------------------------------------------------------------------|

| PWM Signals |      |      |                                                                          |

| PWM_UX1_H   | Y7   | 0    | Digital gate control signal for High Side of Phase U (FOC3) or X1 (FOC2) |

| PWM_UX1_L   | AA7  | 0    | Digital gate control signal for Low Side of Phase U (FOC3) or X1 (FOC2)  |

| PWM_VX2_H   | Y8   | 0    | Digital gate control signal for High Side of Phase V (FOC3) or X2 (FOC2) |

| PWM_VX2_L   | AA8  | 0    | Digital gate control signal for Low Side of Phase V (FOC3) or X2 (FOC2)  |

| PWM_WY1_H   | Y10  | 0    | Digital gate control signal for High Side of Phase W (FOC3) or Y1 (FOC2) |

| PWM_WY1_L   | AA10 | 0    | Digital gate control signal for Low Side of Phase W (FOC3) or Y1 (FOC2)  |

| PWM_Y2_H    | AA11 | 0    | Digital gate control signal for High Side of Phase Y2 (FOC2)             |

| PWM_Y2_L    | Y11  | 0    | Digital gate control signal for Low Side of Phase Y2 (FOC2)              |

| Additional Control Signals |     |   |                              |

|----------------------------|-----|---|------------------------------|

| ENABLE_OUT                 | W11 | 0 | enable output                |

| BRAKE_CHOPPER              | Y9  | 0 | brake chopper control signal |

| Debug UART Interfaces and Debug I/Os |     |       |                                                    |

|--------------------------------------|-----|-------|----------------------------------------------------|

| STATUS_OUT                           | M5  | 0     | status signal output                               |

| RXD_HWI                              | G5  | I, PU | HW debug UART, RxD input                           |

| TXD_HWO                              | G4  | 0     | HW debug UART, TxD output                          |

| RXD_MCU                              | G2  | I, PU | MCU debug UART, RxD input                          |

| TXD_MCU                              | G1  | 0     | MCU debug UART, TxD output                         |

| MCU_GPO_15                           | V8  | 0     | reserved, keep open                                |

| MCU_GPO_16                           | V10 | 0     | reserved, keep open                                |

| MCU_GPO_17                           | V11 | 0     | reserved, keep open                                |

| MCU_GPO_18                           | U12 | 0     | reserved, keep open                                |

| PDI_IRQ                              | K5  | 0     | reserved, keep open (GPIO_3 on TMC8670 EVAL V.1.1) |

| Name                   | Pin Type                 | Function                                    |  |  |  |

|------------------------|--------------------------|---------------------------------------------|--|--|--|

| Device Supply and Grou | Device Supply and Ground |                                             |  |  |  |

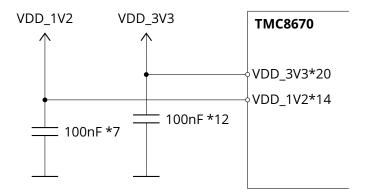

| VDD_1V2                | K10, K11, L10, L11,      | 1.2V DC Core supply voltage,                |  |  |  |

|                        | M12, M13, N12, N13,      | use 100nF filter capacitors                 |  |  |  |

|                        | R12, R13, U14, V14,      |                                             |  |  |  |

|                        | V16, W16                 |                                             |  |  |  |

| VDD_3V3                | M7, U15, V12, K9,        | 3.3V supply voltage for I/Os, PLL, and NVM, |  |  |  |

|                        | H7, G15, R14, E2,        | use 100nF filter capacitors                 |  |  |  |

|                        | J5, M2, N5, V2,          |                                             |  |  |  |

|                        | V5, AA9, R10, V9,        |                                             |  |  |  |

|                        | D20, F17, J15, K20       |                                             |  |  |  |

| GND                    | G7, H15, R15, A1,        | Supply Ground                               |  |  |  |

|                        | A11, A16, A21,           |                                             |  |  |  |

|                        | A6, AA1, AA12,           |                                             |  |  |  |

|                        | AA14, AA15, AA16,        |                                             |  |  |  |

|                        | AA18, AA19, AA20,        |                                             |  |  |  |

|                        | D12, D17, D7, F21,       |                                             |  |  |  |

|                        | F4, G14, H1, H18,        |                                             |  |  |  |

|                        | J10, J11, J7, K12,       |                                             |  |  |  |

|                        | K13, L12, L13, L4,       |                                             |  |  |  |

|                        | M10, M11, M17, M21,      |                                             |  |  |  |

|                        | N10, N11, P15, P7,       |                                             |  |  |  |

|                        | R1, T21, T4, U13,        |                                             |  |  |  |

|                        | U16, U17, U6, U7,        |                                             |  |  |  |