# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **TMD3782** Color Light-to-Digital Converter with Proximity Sensing

#### **General Description**

The TMD3782x device will perform color temperature measurement, ambient light sensing (ALS) and proximity detection with background light rejection. The device detects light intensity under a variety of lighting conditions and through a variety of attenuation materials, including dark glass. The proximity detection feature allows a large dynamic range of operation for accurate distance detection, such as in a cell phone when the user positions the phone close to their ear. IR LED sink current is factory trimmed to provide consistent proximity response without requiring customer calibrations. An internal state machine provides the ability to put the device into a low power state between proximity and RGBC measurements providing very low average power consumption.

The color sensing feature is useful in applications such as backlight control, solid state lighting, reflected LED color sampler, or fluorescent light color temperature detection. The integrated IR blocking filter makes this device an excellent ambient light sensor, color temperature monitor, and general purpose color sensor.

Ordering Information and Content Guide appear at end of datasheet.

### **Key Benefits & Features**

The benefits and features of TMD3782, Color Light-to-Digital Converter with Proximity Sensing are listed below:

Figure 1: Added Value of Using TMD3782

| Benefit                                     | Feature                                                                                                                                                                                                                           |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • Single Device Integrated Optical Solution | <ul> <li>RGB, Ambient Light Sensor (ALS) and Proximity Support</li> <li>Power Management Features</li> <li>I<sup>2</sup>C Fast Mode Interface Compatible</li> <li>Integral IR LED</li> <li>Small 8 lead optical module</li> </ul> |

| Color Temperature and Ambient Light Sensing | <ul> <li>UV / IR blocking filters</li> <li>Programmable Gain &amp; Integration Time</li> <li>1,000,000:1 Dynamic Range</li> </ul>                                                                                                 |

| Equal Response to 360° Incident Light       | Circular Segmented RGBC Photodiode                                                                                                                                                                                                |

| Ideal for Operation Behind Dark Glass       | Very High Sensitivity                                                                                                                                                                                                             |

| Benefit                                                            | Feature                                                                                                                                                  |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Proximity Detection with Integrated IR<br/>LED</li> </ul> | <ul> <li>Background Ambient Light Rejection</li> <li>Factory Trimmed, Consistent Response</li> <li>Programmable Current Sink for IR LED Drive</li> </ul> |

### Applications

The TMD3782 applications include:

- Ambient Light Sensing

- Color Temperature Sensing

- Cell Phone Touch Screen Disable

- Mechanical Switch Replacement

- Industrial Process Control

- Medical Diagnostics

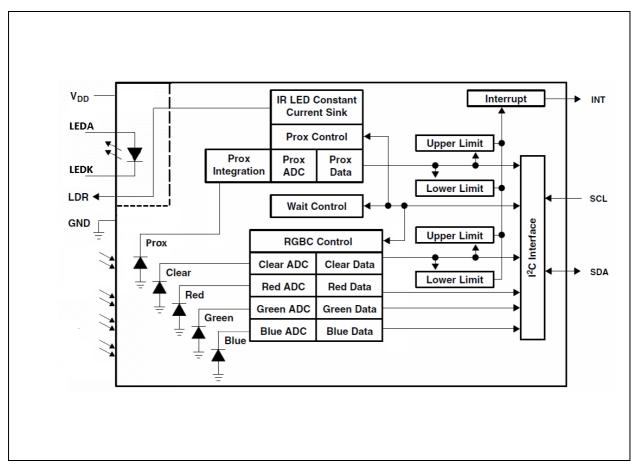

#### **Block Diagram**

The functional blocks of this device are shown below:

## **Detailed Description**

The TMD3782 is a digital color light sensor device containing four analog-to-digital converters (ADCs) that integrate currents from photodiodes. Multiple photodiode segments for red, green, blue, and clear are geometrically arranged to reduce the reading variance as a function of the incident light angle. Integration of all color sensing channels occurs simultaneously. Upon completion of the conversion cycle, the result is transferred to the corresponding data registers. The transfers are double-buffered to ensure that the integrity of the data is maintained. Communication with the device is accomplished through a fast (up to 400 kHz), two-wire I<sup>2</sup>C serial bus for easy connection to a microcontroller or embedded controller.

The TMD3782 provides a separate pin for level-style interrupts. When interrupts are enabled and a pre-set value is exceeded, the interrupt pin is asserted and remains asserted until cleared by the controlling firmware. The interrupt feature simplifies and improves system efficiency by eliminating the need to poll a sensor for a light intensity or proximity value. An interrupt is generated when the value of a clear channel or proximity conversion equals or exceeds either an upper or lower threshold. In addition, a programmable interrupt persistence feature allows the user to determine how many consecutive samples must equal or exceed the threshold to trigger an interrupt. Interrupt thresholds and persistence settings are configured independently for both the clear channel and proximitysensors.

Proximity detection is done using a dedicated proximity photodiode centrally located beneath an internal lens, an internal LED, and a driver circuit. The driver circuit requires no external components and is trimmed to provide a calibrated proximity response. Customer calibrations are usually not required. The number of proximity LED pulses can be programmed from 1 to 255 pulses, providing a 2000:1 contiguous dynamic range. Background ambient light is subtracted from the proximity reading to improve accuracy in all lighting conditions.

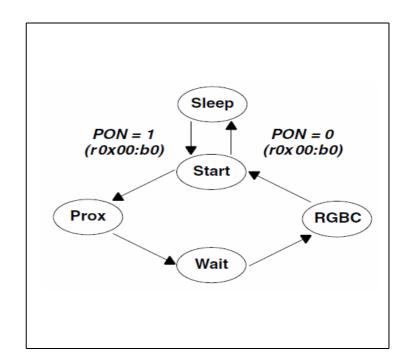

A state machine controls the functionality. Enabling bits independently determine whether the Proximity, Wait or RGBC / ALS functions are performed. Average power consumption is managed via control of variable endurance low power wait cycles. Once initiated the state machine will run continuously until disabled.

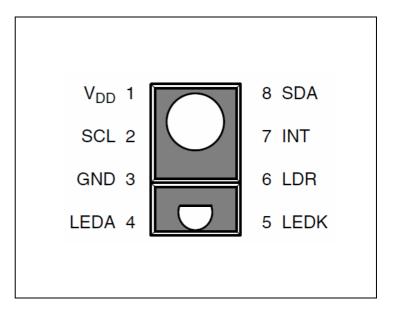

### **Pin Assignment**

#### The TMD3782 pin assignments are described below.

Figure 3: Pin Diagram

Package Module - 8 (Top View) Package drawing is not to scale.

Figure 4: Pin Description

| Pin Number | Pin Name        | Тур | Description                                                                                   |

|------------|-----------------|-----|-----------------------------------------------------------------------------------------------|

| 1          | V <sub>DD</sub> | PWR | Supply voltage                                                                                |

| 2          | SCL             | I   | I <sup>2</sup> C serial clock input terminal - clock signal for I <sup>2</sup> C serial data. |

| 3          | GND             | GND | Power supply ground. All voltages are referenced to GND.                                      |

| 4          | LEDA            | PWR | LED anode.                                                                                    |

| 5          | LEDK            | -   | LED cathode. Connect to LDR pin when using internal driver circuit.                           |

| 6          | LDR             | -   | Proximity IR LED controlled current sink driver.                                              |

| 7          | INT             | 0   | Interrupt — open drain (active low)                                                           |

| 8          | SDA             | I/O | I <sup>2</sup> C serial data I/O terminal - serial data I/O for I <sup>2</sup> C.             |

## Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5: Absolute Maximum Ratings

| Parameter                                   | Min   | Max | Units | Comments                             |

|---------------------------------------------|-------|-----|-------|--------------------------------------|

| Supply Voltage, V <sub>DD</sub>             |       | 3.8 | V     | All voltages are with respect to GND |

| Digital I/O Voltage (except LDR)            | -0.5  | 3.8 | V     |                                      |

| Max LEDA Voltage <sup>(2)</sup>             |       | 4.8 | V     |                                      |

| Max LDR Voltage <sup>(3)</sup>              |       | 4.4 | V     |                                      |

| Output Terminal Current (except LDR)        | -1    | 20  | mA    |                                      |

| Storage Temperature Range, T <sub>stg</sub> | -40   | 85  | °C    |                                      |

| ESD Tolerance, JEDEC Specification          | ±2000 |     | V     | JESD22-A11 Class 1C                  |

#### Note(s) and/or Footnote(s):

1. All voltages are with respect to GND.

Maximum 4.8V DC over 7 years lifetime Maximum 5.0V spikes with up to 250s cumulative duration over 7 years lifetime Maximum 5.5V spikes with up to 10s (=1000\*10ms) cumulative duration over 7 years lifetime

3. Maximum voltage with LDR = off

## **Electrical Characteristics**

All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

#### Figure 6:

**Recommended Operating Conditions**

| Symbol          | Parameter                                     | Min | Тур | Мах | Units |

|-----------------|-----------------------------------------------|-----|-----|-----|-------|

| V <sub>DD</sub> | Supply voltage                                | 2.7 | 3   | 3.3 | V     |

| T <sub>A</sub>  | Operating free-air temperature <sup>(1)</sup> | -30 |     | 85  | °C    |

#### Note(s) and/or Footnote(s):

1. While the device is operational across the temperature range, functionality will vary with temperature. Specifications are stated only at 25°C unless otherwise noted.

Figure 7:

Operating Characteristics, V<sub>DD</sub>=3V, T<sub>A</sub>=25°C (unless otherwise noted)

| Symbol            | Parameter                              | Conditions                                    | Min                         | Тур | Max                         | Units |

|-------------------|----------------------------------------|-----------------------------------------------|-----------------------------|-----|-----------------------------|-------|

|                   |                                        | Active - LDR pulses off                       |                             | 235 | 330                         | μA    |

| I <sub>DD</sub>   | Supply current                         | Wait state                                    |                             | 65  |                             |       |

|                   |                                        | Sleep state — no I <sup>2</sup> C<br>activity |                             | 2.5 | 10                          |       |

| V <sub>OL</sub>   | INT, SDA output low voltage            | 3 mA sink current<br>6 mA sink current        | 0<br>0                      |     | 0.4<br>0.6                  | V     |

| I <sub>LEAK</sub> | Leakage current, SDA, SCL,<br>INT pins |                                               | -5                          |     | 5                           | μΑ    |

| I <sub>LEAK</sub> | Leakage current, LDR pin               |                                               | -10                         |     | 10                          | μA    |

| V <sub>IH</sub>   | SCL, SDA input high voltage            | TMD37821<br>TMD37823                          | 0.7 V <sub>DD</sub><br>1.25 |     |                             | V     |

| V <sub>IL</sub>   | SCL, SDA input low voltage             | TMD37821<br>TMD37823                          |                             |     | 0.3 V <sub>DD</sub><br>0.54 | V     |

#### Figure 8:

Optical Characteristics (Clear Channel),  $V_{DD} = 3V$ ,  $T_A = 25$ °C, AGAIN = 16x, ATIME = 0xF6

| Parameter | Test Conditions                     | C    | Unit |      |                                 |  |

|-----------|-------------------------------------|------|------|------|---------------------------------|--|

| Farameter |                                     | Min  | Тур  | Мах  | Unit                            |  |

| D         | $\lambda_D = 465 \text{ nm}^{(1)}$  | 9.4  | 11.8 | 14.2 |                                 |  |

|           | $\lambda_D = 525 \text{ nm}^{(2)}$  | 12.5 | 15.6 | 18.7 | count/<br>(µW/cm <sup>2</sup> ) |  |

|           | $\lambda_D = 615$ nm <sup>(3)</sup> | 14.6 | 18.2 | 21.8 |                                 |  |

Figure 9:

Optical Characteristics (RGBC), V<sub>DD</sub> = 3V, T<sub>A</sub> = 25°C

|                                                |                                      | Clear Channel  |      |                  |     |                 |     |  |

|------------------------------------------------|--------------------------------------|----------------|------|------------------|-----|-----------------|-----|--|

| Parameter                                      | Test<br>Conditions                   | Red<br>Channel |      | Green<br>Channel |     | Blue<br>Channel |     |  |

|                                                |                                      | Min            | Max  | Min              | Мах | Min             | Мах |  |

| Color ADC count value<br>ratio:<br>Color/Clear | $\lambda_{D} = 465 \text{ nm}^{(1)}$ | 0%             | 15%  | 10%              | 42% | 70%             | 90% |  |

|                                                | $\lambda_{D} = 525 \text{ nm}^{(2)}$ | 4%             | 25%  | 60%              | 85% | 10%             | 45% |  |

|                                                | $\lambda_D = 615$ nm <sup>(3)</sup>  | 80%            | 110% | 0%               | 14% | 5%              | 24% |  |

#### Note(s) and/or Footnote(s):

- 1. The 465 nm input irradiance is supplied by an InGaN light-emitting diode with the following characteristics: dominant wavelength  $\lambda_D = 465$  nm, spectral halfwidth  $\Delta \lambda_2 = 22$  nm.

- 2. The 525 nm input irradiance is supplied by an InGaN light-emitting diode with the following characteristics: dominant wavelength  $\lambda_D$  = 525 nm, spectral halfwidth  $\Delta\lambda_2$  = 35 nm.

- 3. The 615 nm input irradiance is supplied by a AlInGaP light-emitting diode with the following characteristics: dominant wavelength  $\lambda_D = 615$  nm, spectral halfwidth  $\Delta\lambda_2 = 15$  nm.

#### Figure 10:

RGBC Characteristics, V<sub>DD</sub> = 3 V, T<sub>A</sub> = 25°C, AGAIN = 16x, AEN = 1 (unless otherwise noted)

| Parameter                                                        | Conditions                               | Channel | Min             | Тур             | Max             | Units                 |

|------------------------------------------------------------------|------------------------------------------|---------|-----------------|-----------------|-----------------|-----------------------|

| Dark ADC count value                                             | $E_e = 0$ , AGAIN = 60x,                 |         | 0               | 1               | 3               | counts                |

| Dark ADC Count value                                             | ATIME=0xD6 (100ms)                       |         | 0               |                 | 1               | counts <sup>(1)</sup> |

| ADC integration time step size                                   | ATIME = 0xFF                             |         | 2.25            | 2.38            | 2.53            | ms                    |

| ADC number of integration steps                                  |                                          |         | 1               |                 | 256             | steps                 |

| ADC counts per step                                              |                                          |         | 0               |                 | 1023            | counts                |

| ADC count value                                                  | ATIME = 0xC0 (152.3 ms)                  |         | 0               |                 | 65535           | counts                |

| Gain scaling, relative to $1 \times$ gain setting <sup>(2)</sup> | AGAIN = 4x<br>AGAIN = 16x<br>AGAIN = 60x |         | 3.8<br>15<br>58 | 4.0<br>16<br>60 | 4.2<br>17<br>63 | ×                     |

#### Note(s) and/or Footnote(s):

1. Based on typical 3-sigma distribution. Not 100% tested.

2. Clear channel response to a red LED light source with a dominant wavelength ( $\lambda_D$ ) of 615 nm and a spectral halfwidth ( $\Delta\lambda_2$ ) of 20 nm.

Figure 11:

Proximity Characteristics,  $V_{DD} = 3 V$ ,  $T_A = 25^{\circ}C$ , PEN = 1 (unless otherwise noted)

| Parameter                                                          | Conditions                                                                                      | Min  | Тур                     | Max  | Units  |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|-------------------------|------|--------|

| I <sub>DD</sub> Supply current                                     | LDR pulse on                                                                                    |      | 3                       |      | mA     |

| ADC conversion time step size                                      |                                                                                                 | 2.25 | 2.38                    | 2.53 | ms     |

| LED pulse period                                                   |                                                                                                 |      | 14                      |      | us     |

| LED pulse width                                                    | LED on time                                                                                     |      | 6.3                     |      | us     |

| Nominal LED drive current<br>(measured at LDR=0.6V) <sup>(1)</sup> | PDRIVE = 0 (100%)<br>PDRIVE = 1 (50%)<br>PDRIVE = 2 (25%)<br>PDRIVE = 3 (12.5%)                 |      | 100<br>50<br>25<br>12.5 |      | mA     |

| Proximity offset, no target <sup>(2), (3)</sup>                    | Pulses: 8<br>PDRIVE = 0 (100%)                                                                  | 100  | 165                     | 230  | counts |

| Proximity response,<br>100-mm target <sup>(3)</sup>                | 73 mm × 83 mm, 90% reflective Kodak<br>Gray Card, 8 pulses,<br>PDRIVE = 0 (100%) <sup>(3)</sup> | 415  | 510                     | 605  | counts |

#### Note(s) and/or Footnote(s):

- 1. Value is factory adjusted to meet the Prox count specification. Considerable variation (relative to the typical value) is possible after adjustment.

- 2. Proximity offset is the sum of optical and electrical offsets, and will change from one design implementation (or test system) to another. 100% tested.

- 3. Application design must use correct electrical schematic to ensure proper offset results. Refer to application guide and guidance for proper circuit.

#### Figure 12: IR LED Characteristics, V<sub>DD</sub> = 3 V, T<sub>A</sub> = 25°C

| Symbol                          | Parameter                       | Conditions                                                        | Min | Тур | Max | Units |

|---------------------------------|---------------------------------|-------------------------------------------------------------------|-----|-----|-----|-------|

| V <sub>F</sub>                  | Forward Voltage                 | I <sub>F</sub> = 20 mA                                            |     | 1.4 | 1.5 | V     |

| V <sub>R</sub>                  | Reverse Voltage                 | I <sub>R</sub> = 10 μA                                            | 5   |     |     | V     |

| P <sub>O</sub>                  | Radiant Power                   | I <sub>F</sub> = 20 mA                                            | 4.5 |     |     | mW    |

| λ <sub>p</sub>                  | Peak Wavelength                 | I <sub>F</sub> = 20 mA                                            |     | 850 |     | nm    |

| Δ <sub>λ</sub>                  | Spectral Radiation<br>Bandwidth | I <sub>F</sub> = 20 mA                                            |     | 40  |     | nm    |

| T <sub>R</sub> , T <sub>F</sub> | Optical Rise, r<br>Fall Time    | $I_F = 100 \text{ mA}, T_W = 125 \text{ ns},$<br>duty cycle = 25% |     | 20  | 40  | ns    |

Figure 13:

Wait Characteristics,  $V_{DD} = 3 V$ ,  $T_A = 25$ °C, WEN = 1 (unless otherwise noted)

| Parameter      | Conditions   | Channel | Min  | Тур  | Max  | Units |

|----------------|--------------|---------|------|------|------|-------|

| Wait step size | WTIME = 0xFF |         | 2.25 | 2.38 | 2.53 | ms    |

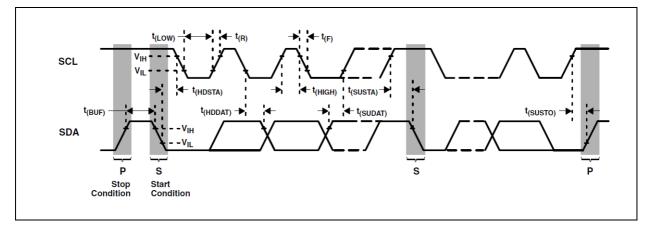

## **Timing Characteristics**

The timing characteristics of TMD3782 are given below.

Figure 14: AC Electrical Characteristics, V<sub>DD</sub> = 3 V, T<sub>A</sub> = 25°C (unless otherwise noted)

| Parameter <sup>(1)</sup> | Description                                                                                        | Min | Тур | Max | Units |

|--------------------------|----------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| f <sub>(SCL)</sub>       | Clock frequency (I <sup>2</sup> C only)                                                            | 0   |     | 400 | kHz   |

| t <sub>(BUF)</sub>       | Bus free time between start and stop condition                                                     | 1.3 |     |     | μs    |

| t <sub>(HDSTA)</sub>     | Hold time after (repeated) start<br>condition. After this period, the first<br>clock is generated. | 0.6 |     |     | μs    |

| t <sub>(SUSTA)</sub>     | Repeated start condition setup time                                                                | 0.6 |     |     | μs    |

| t <sub>(SUSTO)</sub>     | Stop condition setup time                                                                          | 0.6 |     |     | μs    |

| t <sub>(HDDAT)</sub>     | Data hold time                                                                                     | 0   |     |     | μs    |

| t <sub>(SUDAT)</sub>     | Data setup time                                                                                    | 100 |     |     | ns    |

| t <sub>(LOW)</sub>       | SCL clock low period                                                                               | 1.3 |     |     | μs    |

| t <sub>(HIGH)</sub>      | SCL clock high period                                                                              | 0.6 |     |     | μs    |

| t <sub>F</sub>           | Clock/data fall time                                                                               |     |     | 300 | ns    |

| t <sub>R</sub>           | Clock/data rise time                                                                               |     |     | 300 | ns    |

| C <sub>i</sub>           | Input pin capacitance                                                                              |     |     | 10  | pF    |

#### Note(s) and/or Footnote(s):

1. Specified by design and characterization; not production tested.

### **Timing Diagrams**

Figure 15: Parameter Measurement Information

## Typical Operating Characteristics

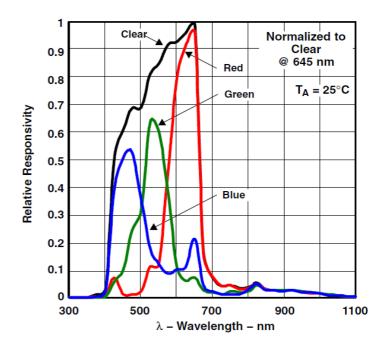

Figure 16: Spectral Responsivity

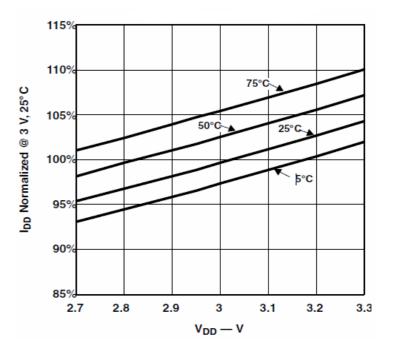

Figure 17: Normalized I<sub>DD</sub> vs. V<sub>DD</sub> and Temperature

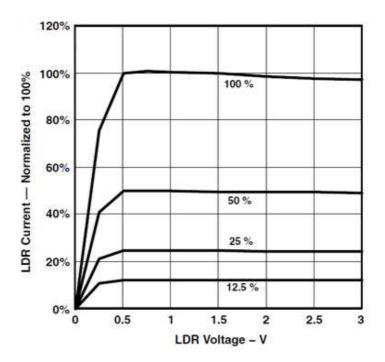

Figure 18: Typical LDR Current vs. Voltage

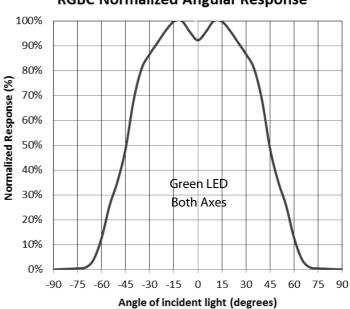

Figure 19: RGBC Responsivity vs. Angular Displacement

**RGBC Normalized Angular Response**

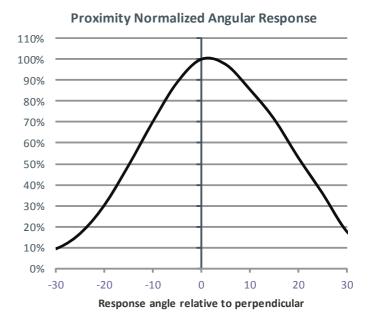

#### Figure 20: Proximity Responsivity vs. Angular Displacement

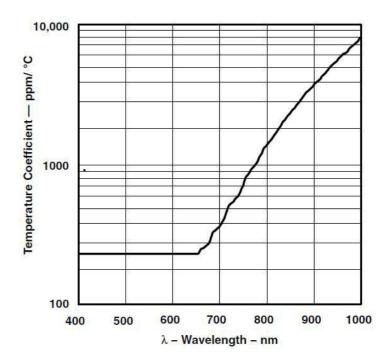

Figure 21: Responsivity Temperature Coefficient

## I<sup>2</sup>C Protocol

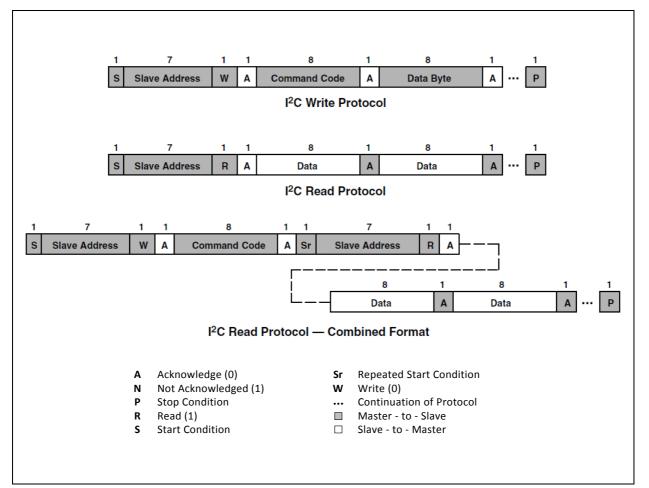

Interface and control are accomplished through an  $l^2C$  serial compatible interface (standard or fast mode) to a set of registers that provide access to device control functions and output data. The devices support the 7-bit  $l^2C$  addressing protocol.

The I<sup>2</sup>C standard provides for three types of bus transaction: read, write, and a combined protocol (Figure 22). During a write operation, the first byte written is a command byte followed by data. In a combined protocol, the first byte written is the command byte followed by reading a series of bytes. If a read command is issued, the register address from the previous command will be used for data access. Likewise, if the MSB of the command is not set, the device will write a series of bytes at the address stored in the last valid command with a register address. The command byte contains either control information or a 5-bit register address. The control commands can also be used to clear interrupts.

The l<sup>2</sup>C bus protocol was developed by Philips (now NXP). For a complete description of the l<sup>2</sup>C protocol, please review the NXP l<sup>2</sup>C design specification at

http://www.l<sup>2</sup>C-bus.org/references/.

Figure 22: I<sup>2</sup>C Write, Read and Combined Protocols

## **Register Description**

The TMD3782 is controlled and monitored by data registers and a command register accessed through the serial interface. These registers provide for a variety of control functions and can be read to determine results of the ADC conversions. The register set is summarized in Figure 23.

| Figure 23:          |  |

|---------------------|--|

| <b>Register Map</b> |  |

| Address | Register Name | R/W | Register Function                            | Reset<br>Value |

|---------|---------------|-----|----------------------------------------------|----------------|

| -       | COMMAND       | W   | Specified register address                   | 0x00           |

| 0x00    | ENABLE        | R/W | Enables states and interrupts                | 0x00           |

| 0x01    | ATIME         | R/W | RGBC time                                    | 0xFF           |

| 0x03    | WTIME         | R/W | Wait time                                    | 0xFF           |

| 0x04    | AILTL         | R/W | Clear interrupt low threshold low byte       | 0x00           |

| 0x05    | AILTH         | R/W | Clear interrupt low threshold high byte      | 0x00           |

| 0x06    | AIHTL         | R/W | Clear interrupt high threshold low byte      | 0x00           |

| 0x07    | AIHTH         | R/W | Clear interrupt high threshold high byte     | 0x00           |

| 0x08    | PILTL         | R/W | Proximity interrupt low threshold low byte   | 0x00           |

| 0x09    | PILTH         | R/W | Proximity interrupt low threshold high byte  | 0x00           |

| 0x0A    | PIHTL         | R/W | Proximity interrupt high threshold low byte  | 0x00           |

| 0x0B    | PIHTH         | R/W | Proximity interrupt high threshold high byte | 0x00           |

| 0x0C    | PERS          | R/W | Interrupt persistence filters                | 0x00           |

| 0x0D    | CONFIG        | R/W | Configuration                                | 0x00           |

| 0x0E    | PPULSE        | R/W | Proximity pulse count                        | 0x00           |

| 0x0F    | CONTROL       | R/W | Gain control register                        | 0x00           |

| 0x11    | REVISION      | R   | Die revision number                          | Rev.           |

| 0x12    | ID            | R   | Device ID                                    | ID             |

| 0x13    | STATUS        | R   | Device status                                | 0x00           |

| 0x14    | CDATA         | R   | Clear ADC low data register                  | 0x00           |

| 0x15    | CDATAH        | R   | Clear ADC high data register                 | 0x00           |

| 0x16    | RDATA         | R   | Red ADC low data register                    |                |

| 0x17    | RDATAH        | R   | Red ADC high data register                   | 0x00           |

| 0x18    | GDATA         | R   | Green ADC low data register                  | 0x00           |

| Address | Register Name | R/W | R/W Register Function            |      |

|---------|---------------|-----|----------------------------------|------|

| 0x19    | GDATAH        | R   | Green ADC high data register     | 0x00 |

| 0x1A    | BDATA         | R   | Blue ADC low data register       | 0x00 |

| 0x1B    | BDATAH        | R   | Blue ADC high data register      | 0x00 |

| 0x1C    | PDATA         | R   | Proximity ADC low data register  | 0x00 |

| 0x1D    | PDATAH        | R   | Proximity ADC high data register | 0x00 |

The mechanics of accessing a specific register depends on the specific protocol used. In general, the COMMAND register is written first to specify the specific control/status register for following read/write operations.

### **Command Register**

The Command Register specifies the address of the target register for future write and read operations, and is used to clear interrupt sources.

Figure 24: Command Register

| 7       | 6    | 5 | 4 | 3   | 2 | 1 | 0 |

|---------|------|---|---|-----|---|---|---|

| COMMAND | ТҮРЕ |   |   | ADD |   |   |   |

| Fields  | Bits | Description                                                         |                                                                                                                         |                                     |  |

|---------|------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|

| COMMAND | 7    | Select Command                                                      | Select Command Register. Must write as 1 when addressing COMMAND register.                                              |                                     |  |

|         |      | Selects type of transaction to follow in subsequent data transfers: |                                                                                                                         |                                     |  |

|         |      | FIELD VALUE                                                         | TRANSACTION TYPE                                                                                                        |                                     |  |

|         | 6:5  | 00                                                                  | Repeated byte protocol transaction                                                                                      |                                     |  |

| TYPE    |      | 6:5                                                                 | 01                                                                                                                      | Auto-increment protocol transaction |  |

|         |      | 10                                                                  | Reserved — Do not use                                                                                                   |                                     |  |

|         |      | 11                                                                  | Special function — See description below                                                                                |                                     |  |

|         |      |                                                                     | repeatedly read the same register with each data access. Block<br>ide auto-increment function to read successive bytes. |                                     |  |

| Fields | Bits | Description                                                                                                                                                                                                                                                                                                         |                                     |  |  |

|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|

|        |      | Address field/special function field. Depending on the transaction type, see about<br>this field either specifies a special function command or selects the specific<br>control–status–register for following write and read transactions. The field value<br>listed below apply only to special function commands: |                                     |  |  |

|        |      | FIELD VALUE                                                                                                                                                                                                                                                                                                         | SPECIAL FUNCTION                    |  |  |

|        |      | 00000                                                                                                                                                                                                                                                                                                               | Normal —no action                   |  |  |

| ADD    | 4:0  | 00101                                                                                                                                                                                                                                                                                                               | Proximity interrupt clear           |  |  |

|        |      | 00110                                                                                                                                                                                                                                                                                                               | Clear channel interrupt clear       |  |  |

|        |      | 00111                                                                                                                                                                                                                                                                                                               | Proximity and Clear interrupt clear |  |  |

|        |      | other                                                                                                                                                                                                                                                                                                               | Reserved — Do not write             |  |  |

|        |      | Clear channel/Proximity Interrupt Clear. Clears any pending Clear/Proximity interrupt. This special function is self clearing.                                                                                                                                                                                      |                                     |  |  |

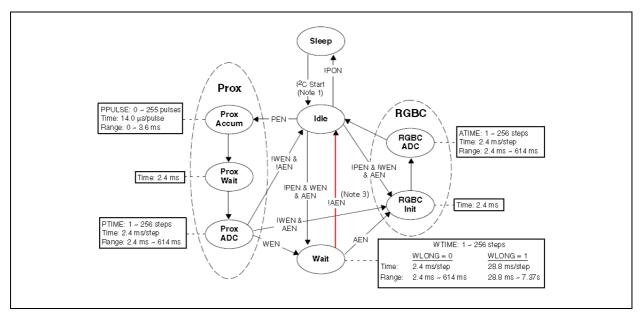

#### System Timing

The system state machine shown in Figure 25 provides an overview of the states and state transitions that provide system control of the device. This section highlights the programmable features, which affect the state machine cycle time, and provides details to determine system level timing.

When the proximity detection feature is enabled (PEN), the state machine transitions through the Prox Accum, Prox Wait, and Prox ADC states. The Prox Wait time is a fixed 2.4 ms, whereas the Prox Accum time is determined by the number of proximity LED pulses (PPULSE) and the Prox ADC time is determined by the integration time (PTIME). The formulas to determine the Prox Accum and Prox ADC times are given in the associated boxes in Figure 25. If an interrupt is generated as a result of the proximity cycle, it will be asserted at the end of the Prox ADC state.

When the power management feature is enabled (WEN), the state machine will transition in turn to the Wait state. The wait time is determined by WLONG, which extends normal operation by 12× when asserted, and WTIME. The formula to determine the wait time is given in the box associated with the Wait state in Figure 25.

When the RGBC feature is enabled (AEN), the state machine will transition through the RGBC Init and RGBC ADC states. The RGBC Init state takes 2.4 ms, while the RGBC ADC time is dependent on the integration time (ATIME). The formula to determine RGBC ADC time is given in the associated box in Figure 25. If an interrupt is generated as a result of the RGBC cycle, it will be asserted at the end of the RGBC ADC.

#### Figure 25: Enhanced State Machine Diagram

#### Note(s) and/or Footnote(s):

1. There is a 2.4 ms warm-up delay if PON is enabled. If PON is not enabled, the device will return to the Sleep state as shown.

2. PON, PEN, WEN and AEN are fields in the Enable register (0x00).

3. PON=1, PEN-1, WEN-1, AEN=0 is unsupported and will lead to erroneous proximity readings.

### Enable Register (0 x 00)

The Enable Register is used primarily to power the device on and off, and enable functions and interrupts.

Figure 26: Enable Register

| 7     | 6   | 5    | 4    | 3   | 2   | 1   | 0   |

|-------|-----|------|------|-----|-----|-----|-----|

| Reser | ved | PIEN | AIEN | WEN | PEN | AEN | PON |

| Field                   | Bits | Description (Reset value = 0x00)                                                                                                                                                                                                                                                                                                                  |

|-------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved                | 7:6  | Reserved. Write as 0.                                                                                                                                                                                                                                                                                                                             |

| PIEN                    | 5    | Proximity Interrupt Enable. When asserted permits proximity interrupts to be generated, subject to the persist filter.                                                                                                                                                                                                                            |

| AIEN                    | 4    | Ambient Light Sensing (ALS) Interrupt Enable. When asserted permits ALS interrupts to be generated, subject to the persist filter.                                                                                                                                                                                                                |

| WEN <sup>(1), (2)</sup> | 3    | Wait Enable. This bit activates the wait feature. Writing a 1 activates the wait timer. Writing a 0 disables the wait timer.                                                                                                                                                                                                                      |

| PEN <sup>(1), (2)</sup> | 2    | Proximity enable. This bit activates the proximity function. Writing a 1 enables proximity. Writing a 0 disables proximity.                                                                                                                                                                                                                       |

| AEN <sup>(1), (2)</sup> | 1    | ADC enable. This bit activates the four-channel (RGBC) ADC. Writing a 1 enables the ADC. Writing a 0 disables the ADC.                                                                                                                                                                                                                            |

| PON                     | 0    | Power ON. This bit activates the internal oscillator to permit the timers and ADC channels to operate. Writing a 1 activates the oscillator. Writing a 0 disables the oscillator. During reads and writes over the l <sup>2</sup> C interface, this bit is temporarily overridden and the oscillator is enabled, independent of the state of PON. |

#### Note(s) and/or Footnote(s):

1. The PON bit must also be set=1 for these functions to operate.

2. WEN=1, PEN=1, AEN=0 is unsupported and will lead to erroneous proximity readings.

#### **RGBC Integration Time Register (0x01)**

The RGBC Timing Register controls the internal integration time of the RGBC channel ADCs. Upon power up, the RGBC time register is set to 0xFF.

The maximum (or saturation) count value can be calculated based upon the integration time cycles as follows:

min [CYCLES \* 1024, 65535]

Figure 27: RGBC Integration Time Register

| Field  | Bits      | Description (Reset value = 0xFF) |        |         |           |  |

|--------|-----------|----------------------------------|--------|---------|-----------|--|

|        |           | REGISTER VALUE                   | CYCLES | TIME    | Max Count |  |

|        |           | 0xFF                             | 1      | 2.38 ms | 1024      |  |

| ΛΤΙΛΛΕ | ATIME 7:0 | 0xF6                             | 10     | 24 ms   | 10240     |  |

| ATIME  |           | 0xD6                             | 42     | 100 ms  | 43008     |  |

|        |           | 0xC0                             | 64     | 152 ms  | 65535     |  |

|        |           | 0x00                             | 256    | 609 ms  | 65535     |  |

#### Wait Time Register (0x03)

Wait time is set in 2.38 ms increments unless the WLONG bit is asserted in which case the wait times are  $12 \times$  longer. WTIME is programmed as a 2's complement number.

Figure 28: Wait Time Register

| Field | Bits      | Description (Reset value = 0xFF) |           |                   |                   |

|-------|-----------|----------------------------------|-----------|-------------------|-------------------|

|       | WTIME 7:0 | REGISTER<br>VALUE                | WAIT TIME | TIME<br>(WLONG=0) | TIME<br>(WLONG=1) |

| WTIME |           | 0xFF                             | 1         | 2.38 ms           | 0.03 s            |

|       |           | 0xAB                             | 85        | 202 ms            | 2.43 s            |

|       |           | 0x00                             | 256       | 609 ms            | 7.31 s            |

#### Note(s) and/or Footnote(s):

1. The wait time register should be configured before AEN and/or PEN is asserted.

### Clear Channel Interrupt Threshold Registers (0x04 - 0x0b)

The Clear Channel Interrupt Threshold Registers provide 16 bit values to be used as the high and low thresholds for comparison to the 16 bit CDATA values. If AIEN (r0x00:b4) is enabled and CDATA is not between AILT and AIHT for the number of consecutive samples specified in APERS (r0x0C) an interrupt is asserted on the interrupt pin.

Figure 29: Clear Channel Interrupt Threshold Registers

| Registers | Address | Bits | Description (Reset value = 0x00) |

|-----------|---------|------|----------------------------------|

| AILTL     | 0x04    | 7:0  | ALS low threshold lower byte     |

| AILTH     | 0x05    | 7:0  | ALS low threshold upper byte     |

| AIHTL     | 0x06    | 7:0  | ALS high threshold lower byte    |

| AIHTH     | 0x07    | 7:0  | ALS high threshold upper byte    |

#### Proximity Interrupt Threshold Registers (0x04 - 0x0b)

The Proximity Interrupt Threshold Registers provide 16 bit values to be used as the high and low thresholds for comparison to the 16 bit PDATA values. If PIEN (r0x00:b5) is enabled and PDATA is not between PILT and PIHT for the number of consecutive samples specified in PPERS (r0x0C) an interrupt is asserted on the interrupt pin.

Figure 30: Proximity Interrupt Threshold Registers

| Registers | Address | Bits | Description (Reset value = 0x00)    |

|-----------|---------|------|-------------------------------------|

| PILTL     | 0x08    | 7:0  | Proximity low threshold lower byte  |

| PILTH     | 0x09    | 7:0  | Proximity low threshold upper byte  |

| PIHTL     | 0x0a    | 7:0  | Proximity high threshold lower byte |

| PIHTH     | 0x0b    | 7:0  | Proximity high threshold upper byte |

## Interrupt Persistence Register (0x0C)

The Interrupt Register controls the interrupt capabilities of the device.

Figure 31: Interrupt Persistence Register

| 7 | 6   | 5   | 4 | 3 | 2  | 1   | 0 |

|---|-----|-----|---|---|----|-----|---|

|   | PPE | ERS |   |   | AP | ERS |   |

| Field | Bits | Description (Reset value = 0x00)                                                            |                                              |                                    |                                   |  |

|-------|------|---------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------|-----------------------------------|--|

|       |      | Proximity interrupt persistence. Controls rate of proximity interrupts to the host processo |                                              |                                    |                                   |  |

|       |      | FIELD VALUES                                                                                | PERSISTENCE                                  |                                    |                                   |  |

|       |      | 0000                                                                                        | Every proximity cycle generates an interrupt |                                    |                                   |  |

| PPERS | 7:4  | 0001                                                                                        | Any value outside of threshold range         |                                    |                                   |  |

|       |      |                                                                                             |                                              | 0010                               | 2 consecutive values out of range |  |

|       |      |                                                                                             |                                              |                                    |                                   |  |

|       |      |                                                                                             | 1111                                         | 15 consecutive values out of range |                                   |  |

| Field | Bits | Description (Reset value = 0x00)                                                                    |                                         |  |  |  |

|-------|------|-----------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|

|       |      | Clear channel interrupt persistence. Controls rate of Clear channel interrupts to the hosprocessor. |                                         |  |  |  |

|       |      | FIELD VALUE                                                                                         | PERSISTENCE                             |  |  |  |

|       |      | 0000                                                                                                | Every RGBC cycle generates an interrupt |  |  |  |

|       |      | 0001                                                                                                | Any value outside of threshold range    |  |  |  |

|       |      | 0010                                                                                                | 2 consecutive values out of range       |  |  |  |

|       |      | 0011                                                                                                | 3 consecutive values out of range       |  |  |  |

|       |      | 0100                                                                                                | 5 consecutive values out of range       |  |  |  |

|       |      | 0101                                                                                                | 10 consecutive values out of range      |  |  |  |

| APERS | 3:0  | 0110                                                                                                | 15 consecutive values out of range      |  |  |  |

|       |      | 0111                                                                                                | 20 consecutive values out of range      |  |  |  |

|       |      | 1000                                                                                                | 25 consecutive values out of range      |  |  |  |

|       |      | 1001                                                                                                | 30 consecutive values out of range      |  |  |  |

|       |      | 1010                                                                                                | 35 consecutive values out of range      |  |  |  |

|       |      | 1011                                                                                                | 40 consecutive values out of range      |  |  |  |

|       |      | 1100                                                                                                | 45 consecutive values out of range      |  |  |  |

|       |      | 1101                                                                                                | 50 consecutive values out of range      |  |  |  |

|       |      | 1110                                                                                                | 55 consecutive values out of range      |  |  |  |

|       |      | 1111                                                                                                | 60 consecutive values out of range      |  |  |  |

## Configuration Register (0x0D)

The Configuration Register sets the wait long time.

Figure 32: Configuration Register

| 7 | 6        | 5 | 4 | 3 | 2 | 1     | 0        |

|---|----------|---|---|---|---|-------|----------|

|   | Reserved |   |   |   |   | WLONG | Reserved |

| Field    | Bits | Description (Reset value = 0x00)                                                                                    |

|----------|------|---------------------------------------------------------------------------------------------------------------------|

| Reserved | 7:2  | Reserved. Write as 0.                                                                                               |

| WLONG    | 1    | Wait Long. When asserted, the wait cycles are increased by a factor 12× from that programmed in the WTIME register. |

| Reserved | 0    | Reserved. Write as 0.                                                                                               |

### Proximity Pulse Count Register (0x0E)

The Proximity Pulse Count Register sets the number of proximity pulses that will be transmitted.

#### Figure 33: Proximity Pulse Count Register

| Field  | Bits | Description (Reset value = 0x00)                                                 |

|--------|------|----------------------------------------------------------------------------------|

| PPULSE | 7:0  | Proximity Pulse Count. Specifies the number of proximity pulses to be generated. |

### **Control Register (0x0F)**

The Control Register provides RGBC gain settings and a control for managing the proximity reading in the event the analog circuitry becomes saturated. Bit 5 must be set =1 for proper device operation.

Figure 34: Control Register

| 7    | 6  | 5        | 4    | 3    | 2    | 1  | 0    |

|------|----|----------|------|------|------|----|------|

| PDRI | VE | Reserved | PSAT | Rese | rved | AC | SAIN |

| Field    | Bits | Desc                                                                                                            | Description (Reset value = 0x00) |  |  |

|----------|------|-----------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| PDRIVE   | 7:6  | 00 = 100%<br>01 = 50%<br>10 = 25%<br>11 = 12.5%                                                                 |                                  |  |  |

| Reserved | 5    | Reserved. Must be writte                                                                                        | n = 1                            |  |  |

| PSAT     | 4    | 0 = PDATA output regardless of ambient light level<br>1 = PDATA output equal to dark current value if saturated |                                  |  |  |

| Reserved | 3:2  | Reserved. Write as 00                                                                                           |                                  |  |  |

|          | 1:0  | RGBC Gain Control.                                                                                              |                                  |  |  |

|          |      | FIELD VALUE                                                                                                     | RGBC GAIN VALUE                  |  |  |

| AGAIN    |      | 00                                                                                                              | 1X Gain                          |  |  |

|          |      | 01                                                                                                              | 4X Gain                          |  |  |

|          |      | 10                                                                                                              | 16X Gain                         |  |  |

|          |      | 11                                                                                                              | 60X Gain                         |  |  |