# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Tri-Rate Serial Digital Interface Physical Layer IP Core User's Guide

## **Table of Contents**

| Chapter 1. Introduction                     | 5  |

|---------------------------------------------|----|

| Quick Facts                                 |    |

| Features                                    | 6  |

| Video Interface and Source Format Support   | 6  |

| Chapter 2. Functional Description           | 8  |

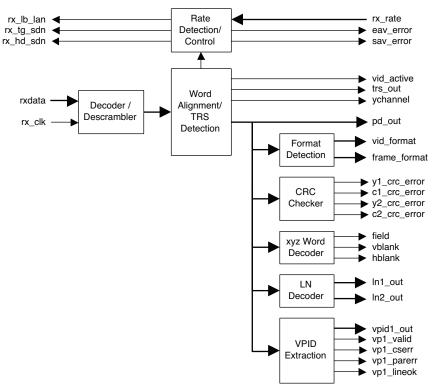

| Receiver                                    |    |

| Decoder/Descrambler                         | 9  |

| Word Alignment/TRS Detection                |    |

| Rate Detection and Control                  |    |

| Format Detection                            |    |

| CRC Checker                                 | 10 |

| XYZ Word Decoder                            | 10 |

| LN Decoder                                  |    |

| VPID Extraction                             | 11 |

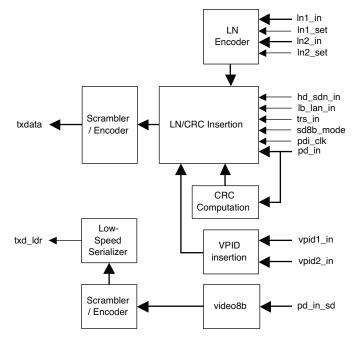

| Transmitter                                 | 11 |

| LN Encoder                                  | 11 |

| CRC Computation                             |    |

| VPID Insertion                              |    |

| LN/CRC Insertion                            |    |

| Scrambler/ Encoder                          |    |

| Low-Speed Serializer                        |    |

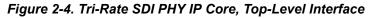

| Signal Descriptions                         |    |

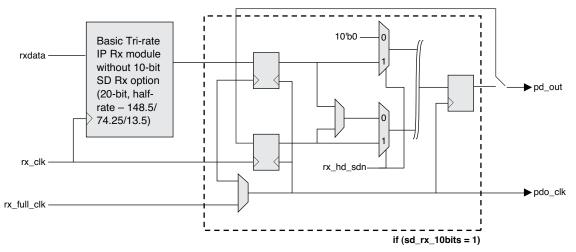

| Interfacing with Tri-Rate SDI PHY IP Core   |    |

| SERDES/Board Tx Interface                   |    |

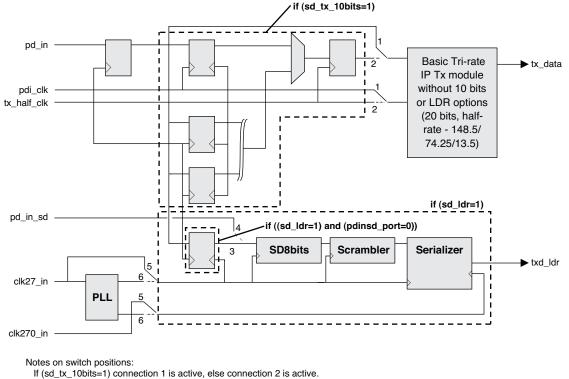

| SD 10-bit Mode for Tx                       |    |

| SD LDR Mode                                 | 18 |

| VPID Extraction                             | 19 |

| FPGA Tx Interface                           |    |

| Custom Format                               | 19 |

| Advanced Settings                           | 19 |

| SERDES/Board Rx Interface                   |    |

| FPGA Rx Interface                           |    |

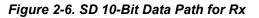

| SD 10-Bit Mode for Rx                       | 20 |

| Video Payload Identification and Extraction | 20 |

| Integer Frame-Rate Applications             |    |

| Fractional Frame-Rate Applications          |    |

| Timing Specifications                       |    |

| Chapter 3. Parameter Settings               |    |

| PHY Tab                                     |    |

| PHY Function                                |    |

| Enable 3G Level-B                           |    |

| LN Insertion                                |    |

| CRC Insertion                               |    |

| VPID Insertion                              |    |

| LDR Path for SD                             |    |

| Include PLL for LDR.                        |    |

| 10-bit Mode for SD Tx                       |    |

| Separate Data Input for SD                  |    |

| SD Data Width                               | 29 |

|                                             |    |

© 2011 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| VPID Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10-bit Mode for SD Rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Clock Enable Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Custom Format Tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Custom Format Support for HD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Custom Format Support for 3G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Value or Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EAV2SAV cycles- Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EAV2SAV Cycles- Minimum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EAV2SAV Cycles- Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SAV2EAV Cycles- Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SAV2EAV Cycles- Minimum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SAV2EAV Cycles- Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Advanced Tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3G/HD/SDProgram Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Lock Match Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Unlock Error Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Chapter 4. IP Core Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Licensing the IP Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Getting Started                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| IPexpress-Created Files and Top Level Directory Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Running Functional Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Synthesizing and Implementing the Core in a Top-Level Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Hardware Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Enabling Hardware Evaluation in Diamond                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Enabling Hardware Evaluation in ispLEVER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Updating/Regenerating the IP Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Regenerating an IP Core in Diamond                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Regenerating an IP Core in Diamond<br>Regenerating an IP Core in ispLEVER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Regenerating an IP Core in ispLEVER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Regenerating an IP Core in ispLEVER<br>Chapter 5. Application Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Regenerating an IP Core in ispLEVER<br>Chapter 5. Application Support<br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design<br>Simulating the Sample Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39<br>40<br>40<br>40<br>40<br>41<br>42                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design<br>Simulating the Sample Design<br>Testbench and Configuration File                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39<br>40<br>40<br>40<br>40<br>41<br>41<br>42<br>43                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design<br>Simulating the Sample Design<br>Testbench and Configuration File<br>Implementing and Testing the Sample Design                                                                                                                                                                                                                                                                                                                                                                                                       | 39<br>40<br>40<br>40<br>40<br>41<br>41<br>42<br>43<br>43<br>45                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design<br>Simulating the Sample Design<br>Testbench and Configuration File<br>Implementing and Testing the Sample Design<br>Board Switch Assignments for Sample Designs                                                                                                                                                                                                                                                                                                                                                        | 39<br>40<br>40<br>40<br>41<br>42<br>43<br>43<br>45<br>45                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design<br>Simulating the Sample Design<br>Testbench and Configuration File<br>Implementing and Testing the Sample Design<br>Board Switch Assignments for Sample Designs<br>Transmitter Testing                                                                                                                                                                                                                                                                                                                                 | 39<br>40<br>40<br>40<br>41<br>41<br>42<br>43<br>43<br>45<br>45<br>46                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design<br>Simulating the Sample Design<br>Testbench and Configuration File<br>Implementing and Testing the Sample Design<br>Board Switch Assignments for Sample Designs<br>Transmitter Testing<br>Receiver Testing                                                                                                                                                                                                                                                                                                             | 39<br>40<br>40<br>40<br>41<br>41<br>42<br>43<br>43<br>45<br>45<br>45<br>46<br>46                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design<br>Simulating the Sample Design<br>Testbench and Configuration File<br>Implementing and Testing the Sample Design<br>Board Switch Assignments for Sample Designs<br>Transmitter Testing<br>Receiver Testing<br>LCD Display                                                                                                                                                                                                                                                                                              | 39       40       40       40       40       41       42       43       45       45       46       47                                                                                                                                                                                                                                                                                                                                                                                                    |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design<br>Simulating the Sample Design<br>Testbench and Configuration File<br>Implementing and Testing the Sample Design<br>Board Switch Assignments for Sample Designs<br>Transmitter Testing<br>Receiver Testing<br>LOD Display<br>Loopback Testing                                                                                                                                                                                                                                                                          | 39       40       40       40       40       40       41       42       43       45       45       46       47       47                                                                                                                                                                                                                                                                                                                                                                                  |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design<br>Simulating the Sample Design<br>Testbench and Configuration File<br>Implementing and Testing the Sample Design<br>Board Switch Assignments for Sample Designs<br>Transmitter Testing<br>Receiver Testing<br>LOD Display<br>Loopback Testing<br>Passthrough Testing                                                                                                                                                                                                                                                   | 39       40       40       40       40       41       42       43       45       45       46       46       47       47       47       47                                                                                                                                                                                                                                                                                                                                                                |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design<br>Simulating the Sample Design<br>Testbench and Configuration File<br>Implementing and Testing the Sample Design<br>Board Switch Assignments for Sample Designs<br>Transmitter Testing<br>Receiver Testing<br>LCD Display<br>Loopback Testing<br>Passthrough Testing<br>Passthrough Testing                                                                                                                                                                                                                            | 39       40       40       40       41       42       43       45       45       46       47       47       48                                                                                                                                                                                                                                                                                                                                                                                           |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design<br>Simulating the Sample Design<br>Testbench and Configuration File<br>Implementing and Testing the Sample Design<br>Board Switch Assignments for Sample Designs<br>Transmitter Testing<br>Receiver Testing<br>LOD Display<br>Loopback Testing<br>Passthrough Testing<br>Passthrough Testing<br>Chapter 6. Core Verification                                                                                                                                                                                            | 39       40       40       40       40       41       42       43       45       45       46       46       47       47       48       49                                                                                                                                                                                                                                                                                                                                                                |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b><br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design<br>Simulating the Sample Design<br>Testbench and Configuration File<br>Implementing and Testing the Sample Design<br>Board Switch Assignments for Sample Designs<br>Transmitter Testing<br>Receiver Testing<br>LCD Display<br>Loopback Testing<br>Passthrough Testing<br>Chapter 6. Core Verification<br>Lattice Technical Support                                                                                                                                                                                      | 39       40       40       40       40       41       42       43       45       45       46       46       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       49                                                                                                             |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39       40       40       40       40       41       42       43       45       45       45       46       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       49       49       49       49       49        49                                                                                                                                                                                                      |

| Regenerating an IP Core in ispLEVER<br><b>Chapter 5. Application Support</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39       40       40       40       40       41       42       43       45       45       45       46       47       47       47       47       47       47       49       49       49       49       49       49       49       49                                                                                                                                                                                                                                                                      |

| Regenerating an IP Core in ispLEVER<br>Chapter 5. Application Support<br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design<br>Passthrough Design<br>Simulating the Sample Design<br>Testbench and Configuration File<br>Implementing and Testing the Sample Design<br>Board Switch Assignments for Sample Designs<br>Transmitter Testing<br>LCD Display<br>LOD Display<br>Loopback Testing<br>Passthrough Testing<br>Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support                                                                                                  | 39       40       40       40       40       41       42       43       45       45       46       47       47       47       47       47       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49 |

| Regenerating an IP Core in ispLEVER.<br>Chapter 5. Application Support<br>Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs<br>Loopback Design.<br>Passthrough Design.<br>Testbench and Configuration File.<br>Implementing and Testing the Sample Design<br>Board Switch Assignments for Sample Designs<br>Transmitter Testing<br>Receiver Testing<br>LCD Display<br>LCD Display<br>Passthrough Testing.<br>Passthrough Testing.<br>Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support.<br>Online Forums                                                                                                                                                   | 39       40       40       40       40       41       42       43       45       45       46       46       47       47       47       47       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49 |

| Regenerating an IP Core in ispLEVER.       Chapter 5. Application Support.       Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs       Loopback Design       Passthrough Design       Simulating the Sample Design       Testbench and Configuration File       Implementing and Testing the Sample Design       Board Switch Assignments for Sample Designs       Transmitter Testing       Receiver Testing       LCD Display       Loopback Testing       Passthrough Testing       Chapter 6. Core Verification       Chapter 7. Support Resources       Lattice Technical Support       Online Forums       Telephone Support Hotline       E-mail Support       Local Support              | 39       40       40       40       40       41       42       43       45       45       46       47       47       47       47       47       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49 |

| Regenerating an IP Core in ispLEVER       Chapter 5. Application Support       Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs       Loopback Design       Passthrough Design       Simulating the Sample Design       Testbench and Configuration File       Implementing and Testing the Sample Design       Board Switch Assignments for Sample Designs       Transmitter Testing       Receiver Testing       LCD Display       Loopback Testing       Passthrough Testing       Chapter 6. Core Verification       Chapter 7. Support Resources       Lattice Technical Support       Online Forums       Telephone Support Hotline       E-mail Support       Local Support       Internet | 39       40       40       40       40       41       42       43       45       45       46       46       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49       49 |

| Regenerating an IP Core in ispLEVER.       Chapter 5. Application Support.       Tri-Rate SDI PHY IP Loopback and Passthrough Sample Designs       Loopback Design       Passthrough Design       Simulating the Sample Design       Testbench and Configuration File       Implementing and Testing the Sample Design       Board Switch Assignments for Sample Designs       Transmitter Testing       Receiver Testing       LCD Display       Loopback Testing       Passthrough Testing       Chapter 6. Core Verification       Chapter 7. Support Resources       Lattice Technical Support       Online Forums       Telephone Support Hotline       E-mail Support       Local Support              | 39       40       40       40       40       41       42       43       45       45       46       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       47       49       49       49       49       49       49       49       49       49       49       49       49       49       49 |

| 50 |

|----|

|    |

|    |

|    |

|    |

## Chapter 1: Introduction

Serial Digital Interface (SDI) is the most popular raw video connectivity standard used in television broadcast studios and video production facilities. The availability of high-speed serial inputs/outputs and general purpose programmable logic makes FPGAs (field programmable gate arrays) ideal devices to be used for acquisition, mixing, storage, editing, processing and format conversion applications. Simpler applications use FPGAs to acquire SDI data from one or more SD (standard definition), HD (high definition) or 3G (3-Gigabit HD) sources, perform simple processing and re-transmit the video data in SDI format. Such applications require an SDI PHY (physical layer) interface and some basic processing blocks like a color space converter. In more complex applications, the acquired video is taken through multiple processing phases, like de-interlacing, video format conversion, filtering, scaling, graphics mixing and picture-in-picture display. FPGA devices can also be used as a bridge between SDI video sources and backplane protocols such as PCI Express or ethernet, with or without any additional video processing.

In an FPGA-based SDI solution, the physical interface portion is often the most challenging part of the solution. This is because the PHY layer includes several device-dependent components like the high-speed I/Os (inputs/outputs), serializer/de-serializer, clock/data recovery, word alignment and timing signal detection logic. Video processing, on the other hand, is algorithmic and is usually achieved using proprietary algorithms developed by the user's in-house design engineering teams.

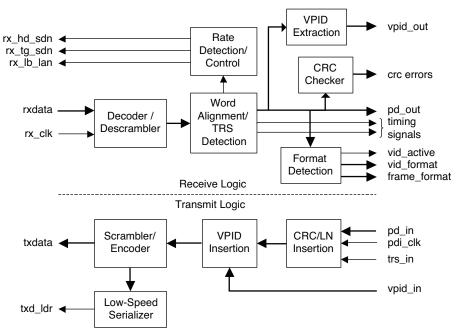

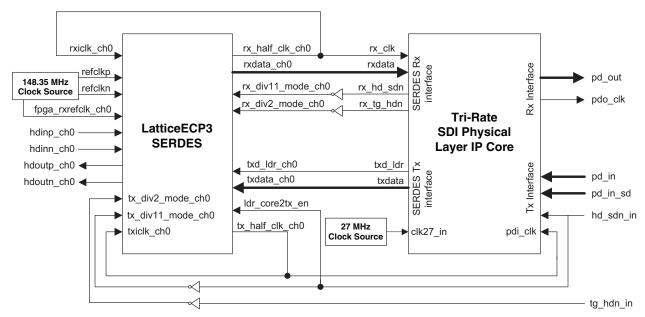

The Lattice Tri-Rate SDI PHY intellectual property (IP) core is a complete SDI PHY interface that connects to the high-speed SDI serial data on one side (through LatticeECP3<sup>™</sup> SERDES) and the formatted parallel video data on the other side. It enables faster development of applications for processing, storing, and bridging SDI video data. It is comprised of the following major functional blocks: SDI encoder/decoder, word alignment, CRC detection and checking, VPID (video payload identifier) insertion and extraction, and rate detection logic. The IP core supports the following interface standards and source formats for SDI as specified in standards published by the Society for Motion Picture and Television Engineers (SMPTE).

| Interface:         | SMPTE 259M-2006 [1] (SD), SMPTE 292M-1998 [2] (HD) and SMPTE 424 M [3] (3G) |

|--------------------|-----------------------------------------------------------------------------|

| SD source formats: | SMPTE 125M [4] and SMPTE 267M [5] (13.5 MHz only)                           |

| HD source formats: | SMPTE 260M [6], SMPTE 274M [7], SMPTE 295M [8] and SMPTE 296M [9]           |

| 3G source formats: | SMPTE 425M [10]                                                             |

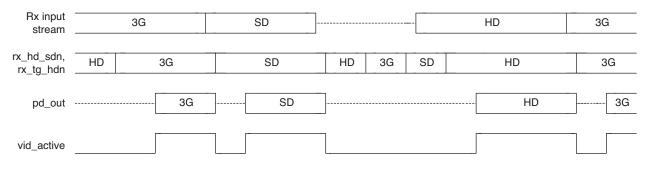

The Tri-Rate SDI PHY IP core, when connected with the LatticeECP3 SERDES, can transmit and/or receive any of the supported video standards and formats through a common physical serial interface. The Tri-Rate SDI PHY IP core can automatically scan and lock on to any of the supported video streams. Receiving multiple standards requires appropriate external clocks to be supplied by the application in response to commands from the Tri-Rate SDI PHY IP core.

## **Quick Facts**

Table 1-1 gives quick facts about the Tri-Rate SDI PHY IP core for LatticeECP3 devices.

#### Table 1-1. Tri-Rate SDI PHY IP Core Quick Facts

|                                  |                         | Tri-Rate SDI PHY IP Core                                                    |                                                                |                        |  |  |  |

|----------------------------------|-------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|------------------------|--|--|--|

|                                  |                         | Tx Only                                                                     | Rx Only                                                        | Both Tx and Rx         |  |  |  |

| Core Requirements                | FPGA Families Supported |                                                                             | LatticeECP3                                                    | ·                      |  |  |  |

| Core Requirements                | Minimal Devices Needed  | L                                                                           | FE3-17EA-6FTN2                                                 | 56C                    |  |  |  |

|                                  | Targeted Device         | L                                                                           | FE3-95EA-7FN11                                                 | 56C                    |  |  |  |

|                                  | Data Path Width         |                                                                             | 20                                                             |                        |  |  |  |

| Typical Resource Utilization     | LUTs                    | 850                                                                         | 1700                                                           | 2500                   |  |  |  |

|                                  | sysMEM EBRs             | 0                                                                           |                                                                |                        |  |  |  |

|                                  | Registers               | 500                                                                         | 1300                                                           | 1800                   |  |  |  |

|                                  | Lattice Implementation  | Lattice Di                                                                  | amond <sup>®</sup> 1.3 or isp                                  | LEVER <sup>®</sup> 8.1 |  |  |  |

|                                  |                         | Synopsys <sup>®</sup> Synplify <sup>™</sup> Pro for Lattice E-2011.03L      |                                                                |                        |  |  |  |

| Design Tool Support <sup>1</sup> | Synthesis               | Mentor Graphics <sup>®</sup> Precision™ RTL Synthesis<br>2010a_Update 2.254 |                                                                |                        |  |  |  |

|                                  | Simulation              | Aldec <sup>®</sup> Ac                                                       | Aldec <sup>®</sup> Active-HDL <sup>™</sup> 8.2 Lattice Edition |                        |  |  |  |

|                                  | Simulation              | Mentor (                                                                    | Graphics ModelSir                                              | m™ SE 6.5              |  |  |  |

1. Design tool support for IP core version 1.3.

## Features

- Dynamic reception of multiple interface standards over the same physical cable: SD-SDI, HD-SDI and 3G-SDI interfaces

- Automatic Rx (receive) rate detection and dynamic Tx (transmit) rate selection

- Multiple SD source formats support: SMPTE 125M [4] and SMPTE 267M [5] (13.5 MHz only)

- Multiple HD source formats support: SMPTE 260M [6], SMPTE 274M [7], SMPTE 295M [8] and SMPTE 296M [9]

- Support for 3G source formats, including 3G Level-B format: SMPTE 425M [10]

- Word alignment and timing reference sequence (TRS) detection

- Field, vertical blanking (vblank) and horizontal blanking (hblank) timing signals generation

- CRC computation, error checking and insertion for HD/3G

- Line number (LN) decoding and encoding for HD/3G

- Custom source format support for HD/3G

- Video Payload Identifier (VPID) insertion and extraction for HD/3G

- 10-bit parallel input/output support for SD

- Soft-logic based low data-rate (LDR) serializer for SD transmission

## Video Interface and Source Format Support

This Tri-Rate SDI PHY IP core supports SMPTE 259, SMPTE 292 and SMPTE 424 interface standards.

## Lattice Semiconductor

SMPTE 259 standard is applicable to 4:2:2 video streams defined by SMPTE 125M and SMPTE 267M. These source formats are briefly described below.

- SMPTE 125M: System M 525 lines and 60 fields based on ITU-R BT.601. The video is transmitted in the form of one luminance (Y) and two color-difference components (scaled versions of R-Y and B-Y). It follows a 4:2:2 family level of ITU-R BT.601 with a nominal luminance sampling at 13.5 MHz allowing for both 8-bit and 10-bit data types.

- SMPTE 267M: System M 525 lines and 59.94 fields, wide screen, 16x9 aspect ratio, based on ITU-R BT.601. The video is transmitted in the form of one luminance (Y) and two color-difference components (scaled versions of R-Y and B-Y). It follows a 4:2:2 family level of ITU-R BT.601 with a nominal luminance sampling at 13.5 MHz or 18 MHz, allowing for both 8-bit and 10-bit data types.

This IP core supports all of SMPTE 125M and only the 13.5 MHz version of SMPTE 267M.