# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **Features**

- CPU32+ Processor (4.5 MIPS at 25 MHz)

- 32-bit Version of the CPU32 Core (Fully Compatible with the CPU32)

- Background Debug Mode

- Byte-misaligned Addressing

- Up to 32-bit Data Bus (Dynamic Bus Sizing for 8 and 16 Bits)

- Up to 32 Address Lines (At Least 28 Always Available)

- Complete Static Design (0 25 MHz Operation)

- Slave Mode to Disable CPU32+ (Allows Use with External Processors)

- Multiple QUICCs Can Share One System Bus (One Master)

- TS68040 Companion Mode Allows QUICC to be a TS68040 Companion Chip and Intelligent Peripheral (22 MIPS at 25 MHz)

- Peripheral Device of TSPC603e (see DC415/D note)

- Four General-purpose Timers

- Superset of MC68302 Timers

- Four 16-bit Timers or Two 32-bit Timers

- Gate Mode Can Enable/Disable Counting

- Two Independent DMAs (IDMAs)

- System Integration Module (SIM60)

- Communications Processor Module (CPM)

- Four Baud Rate Generators

- · Four SCCs (Ethernet/IEEE 802.3 Optional on SCC1-Full 10 Mbps Support)

- Two SMC

- V<sub>cc</sub> = +5V ± 5%

- f<sub>max</sub> = 25 MHz and 33 MHz

- Military Temperature Range: -55°C < T<sub>c</sub> < +125°C

- P<sub>D</sub> = 1.4 W at 25 MHz; 5.25V

2 W at 33 MHz; 5.25V

# Description

The TS68EN360 QUad Integrated Communication Controller (QUICC<sup>™</sup>) is a versatile one-chip integrated microprocessor and peripheral combination that can be used in a variety of controller applications. It particularly excels in communications activities. The QUICC (pronounced "quick") can be described as a next-generation TS68302 with higher performance in all areas of device operation, increased flexibility, major extensions in capability, and higher integration. The term "quad" comes from the fact that there are four serial communications controllers (SCCs) on the device; however, there are actually seven serial channels: four SCCs, two serial management controllers (SMCs), and one serial peripheral interface (SPI).

# Screening/Quality

This product is manufactured in full compliance with:

- MIL-STD-883 (class B)

- QML (class Q)

- · or according to Atmel standards

32-bit Quad Integrated Communication Controller

# **TS68EN360**

Rev. 2113A-HIREL-03/02

R suffix PGA 241 Ceramic Pin Grid Array Cavity Up Ceramic Leaded Chip Carrier Cavity Down

# Introduction

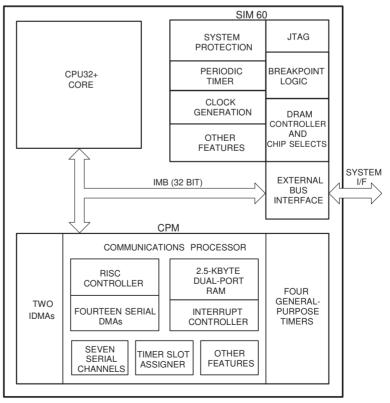

#### QUICC Architecture Overview

The QUICC is 32-bit controller that is an extension of other members of the TS68300 family. Like other members of the TS68300 family, the QUICC incorporates the intermodule bus (IMB). The TS68302 is an exception, having an 68000 bus on chip. The IMB provides a common interface for all modules of the TS68300 family, which allows the development of new devices more quickly by using the library of existing modules. Although the IMB definition always included an option for an on-chip 32-bit bus, the QUICC is the first device to implement this option.

The QUICC is comprised of three modules: the CPU32+ core, the SIM60, and the CPM. Each module utilizes the 32-bit IMB.

The TS68EN360 QUICC block diagram is shown in Figure 1.

# **Pin Assignments**

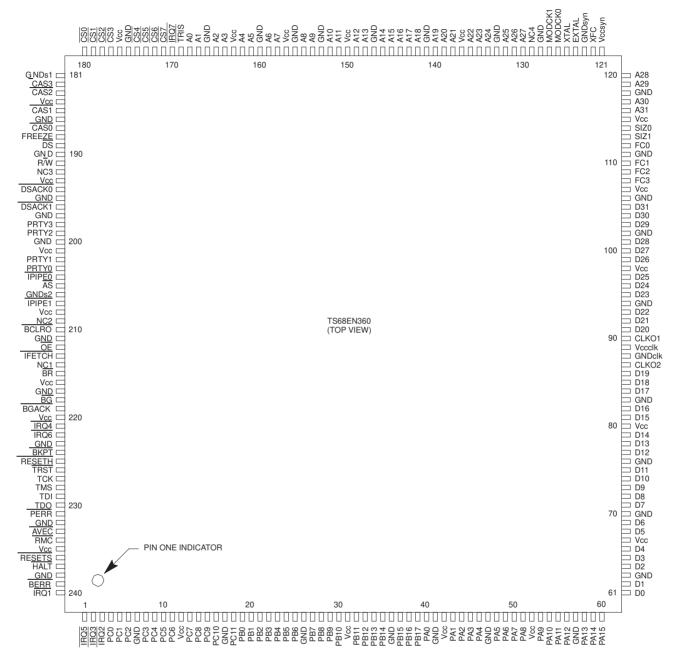

Figure 2. 241-lead Pin Grid Array (PGA)

| [ |            |             |           |             |             |           |            |           |           |            |          |          |                |                |                        |                |                |              |

|---|------------|-------------|-----------|-------------|-------------|-----------|------------|-----------|-----------|------------|----------|----------|----------------|----------------|------------------------|----------------|----------------|--------------|

| т | 〇<br>PA15  | 〇<br>PA12   | O<br>PA9  | O<br>PA6    | O<br>PA3    | O<br>PA2  | ()<br>PB17 | O<br>PB15 | )<br>PB12 | ()<br>PB11 | O<br>PB8 | O<br>PB5 | O<br>PB2       | O<br>PC11      | O<br>PC9               | O<br>PC6       | O<br>PC5       | O<br>PC2     |

| S | ()<br>D2   | ()<br>D0    | O<br>PA13 | )<br>PA10   | O<br>PA7    | O<br>PA5  | O<br>PA1   | 〇<br>PB16 | О<br>РВ13 | O<br>PB10  | O<br>PB7 | O<br>PB4 | O<br>PB1       | O<br>PC10      | O<br>PC7               | O<br>PC3       | O<br>PC1       |              |

| R | ()<br>D4   | ()<br>D3    | ()<br>D1  | O<br>PA14   | O<br>PA11   | ()<br>PA8 | O<br>PA4   | O<br>PA0  | O<br>PB14 | O<br>PB9   | O<br>PB6 | O<br>PB3 | O<br>PB0       | O<br>PC8       | O<br>PC4               | O<br>PC0       |                |              |

| Q | ()<br>D7   | ()<br>D6    | O<br>D5   | )<br>GND    | )<br>GND    | )<br>GND  | ⊖<br>Vcc   | ⊖<br>Vcc  | O<br>GND  | )<br>GND   | ⊖<br>Vcc | ⊖<br>Vcc | )<br>GND       | O<br>GND       | )<br>GND               |                |                |              |

| Р | ()<br>D10  | ()<br>D9    | ()<br>D8  | )<br>GND    | ⊖<br>Vcc    | ()<br>GND |            |           | O<br>NC   |            |          |          | ⊖<br>Vcc       | O<br>GND       | )<br>GND               |                |                |              |

| N | ()<br>D13  | ()<br>D12   | ()<br>D11 | )<br>GND    | )<br>GND    |           |            |           |           |            |          |          |                | O<br>GND       | )<br>GND               |                | O<br>TDO       | ⊖<br>™S      |

| М | ()<br>D16  | ()<br>D15   | ()<br>D14 | )<br>GND    |             |           |            |           |           |            |          |          |                |                | ⊖<br>Vcc               | O<br>TD1       | О<br>тск і     | RESETH       |

| L | ()<br>D19  | ()<br>D18   | ()<br>D17 | ⊖<br>Vcc    |             |           |            |           |           |            |          |          |                |                | )<br>GND               |                |                |              |

| к | O<br>CLKO2 | ⊖<br>Vcc    | )<br>GND  | O<br>Vccclk |             | clk       |            |           |           | EN360      |          |          |                | ⊖<br>Vcc       | ⊖<br>Vcc               |                | BGACH          |              |

| J | CLKO1      | ()<br>D20   | ()<br>D22 | O<br>GND    | ⊖<br>Vcc    |           |            |           | (BOTTC    | OM VIEV    | N)       |          |                | O<br>GND       | )<br>GND               |                |                |              |

| н | ()<br>D21  | ()<br>D23   | ()<br>D25 | )<br>GND    |             |           |            |           |           |            |          |          |                |                | O<br>GNDs2             | 0<br>2 NC2     |                |              |

| G | ()<br>D24  | ()<br>D26   | ()<br>D28 | ⊖<br>Vcc    |             |           |            |           |           |            |          |          |                |                | ⊖<br>Vcc               |                | $\bigcirc$ AS  | O<br>IPIPE1  |

| F | ()<br>D27  | ()<br>D29   | ()<br>D31 | )<br>GND    | )<br>GND    |           |            |           |           |            |          |          |                | ⊖<br>Vcc       | )<br>GND               | O<br>PRTY2     | O<br>PRTY1     | O<br>PRTY0   |

| E | )<br>D30   | O<br>FC3    | O<br>FC0  | ()<br>A31   | O<br>Vccsyn | ()<br>GND | syn        |           | )<br>GND  |            |          |          | ⊖<br>Vcc       | O<br>GNDs1     | ⊖<br>Vcc               | О<br>NC3 і     |                | O<br>1 PRTY3 |

| D | O<br>FC2   | O<br>FC1    | ()<br>A30 | )<br>XFC    | ⊖<br>Vcc    | )<br>GND  | )<br>GND   | ⊖<br>Vcc  | ⊖<br>Vcc  | )<br>GND   | )<br>GND | )<br>GND | )<br>GND       | ⊖<br>Vcc       | ()<br>GND              |                | O<br>R/W       | O<br>DSACK0  |

| С | O<br>SIZ1  | ()<br>A29 e |           |             | O<br>1 A27  | ()<br>A23 | ()<br>A20  | ()<br>A17 | ()<br>A14 | ()<br>A8   | ()<br>A4 | ()<br>A0 | $\bigcirc$ CS7 | $\bigcirc$ CS4 | $\frac{\bigcirc}{CS1}$ |                |                |              |

| В | )<br>SIZ0  | ()<br>A28 M |           |             | ()<br>A25   | ()<br>A22 | ()<br>A19  | ()<br>A16 | ()<br>A13 | ()<br>A10  | ()<br>A7 | ()<br>A5 | ()<br>A1       |                | $\frac{\bigcirc}{CS5}$ | $\bigcirc$ CS2 |                | O<br>CAS1    |

| A |            | ⊖<br>xtal   | O<br>NC4  | ()<br>A26   | ()<br>A24   | ()<br>A21 | ()<br>A18  | ()<br>A15 | ()<br>A12 | ()<br>A11  | ()<br>A9 | ()<br>A6 | O<br>A3        | ()<br>A2       |                        | $\bigcirc$ CS6 | $\bigcirc$ CS3 |              |

| l | 1          | 2           | 3         | 4           | 5           | 6         | 7          | 8         | 9         | 10         | 11       | 12       | 13             | 14             | 15                     | 16             | 17             | 18           |

Note: Pin P9 "NC" is for guide purposes only.

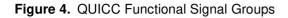

#### Figure 3. 240-lead Cerquad

# **Signal Description**

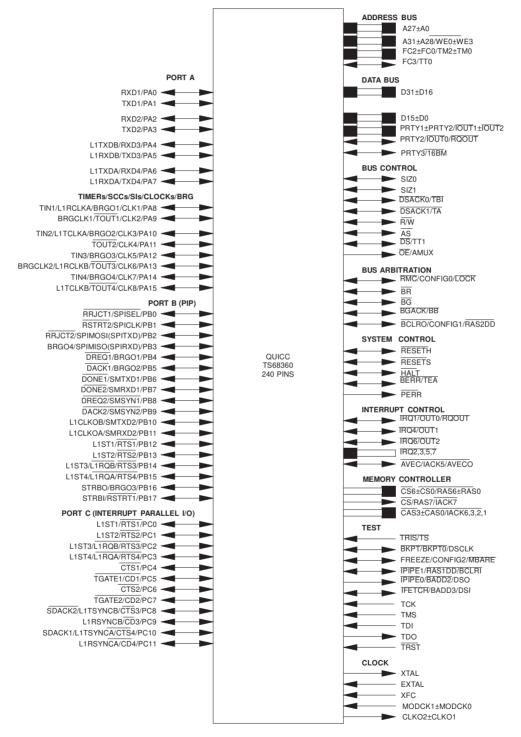

# **Functional Signal Group**

# Signal Index

| Table 1. | System | n Bus | Signal | Index | (Norma | al Operation) |

|----------|--------|-------|--------|-------|--------|---------------|

|          |        |       |        |       |        |               |

| Group                | Signal Name                                                                      | Mnemonic                  | Function                                                                                                                                                                    |

|----------------------|----------------------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address              | Address Bus                                                                      | A27-A0                    | Lower 27 bits of address bus. (I/O)                                                                                                                                         |

|                      | Address Bus/Byte Write<br>Enables                                                | A31-A28<br>WE3-WE0        | Upper four bits of address bus (I/O), or byte write enable signals (O) for accesses to external memory or peripherals.                                                      |

|                      | Function Codes                                                                   | FC3-FC0                   | Identifies the processor state and the address space of the current bus cycle. (I/O)                                                                                        |

| Data                 | Data Bus 31 - 16                                                                 | D31-D16                   | Upper 16-bit data bus used to transfer byte or word data.<br>Used in 16-bit bus mode. (I/O)                                                                                 |

|                      | Data Bus 15 - 0                                                                  | D15-D0                    | Lower 16-bit data bus used to transfer 3-byte or long-word data. (I/O)<br>Not used in 16-bit bus mode.                                                                      |

| Parity               | Parity 2 - 0                                                                     | PRTY2-PRTY0               | Parity signals for byte writes/reads from/to external memory module. (I/O)                                                                                                  |

|                      | Parity 3/16BM                                                                    | PRTY3/16BM                | Parity signals for byte writes/reads from/to external memory module or defines 16-bit bus mode. (I/O)                                                                       |

|                      | Parity Error                                                                     | PERR                      | Indicates a parity error during a read cycle. (O)                                                                                                                           |

| Memory<br>Controller | Chip Select<br>Row Address Select 7<br>Interrupt Acknowledge 7                   | CS<br>RAS7<br>IACK7       | Enables peripherals or DRAMs at programmed addresses (O) or interrupt level 7 acknowledge line. (O)                                                                         |

|                      | Chip Select 6-0<br>Row Address Select 6-0                                        | CS6-CS0<br>RAS6-RAS0      | Enables peripherals or DRAMs at programmed addresses.<br>(O)                                                                                                                |

|                      | Column Address Select<br>3 - 0/Interrupt<br>Acknowledge 1, 2, 3, 6               | CAS3-CAS0/<br>IACK6,3,2,1 | DRAM column address select or interrupt level acknowledge lines. (O)                                                                                                        |

| Bus Arbitration      | Bus Request                                                                      | BR                        | Indicates that an external device requires bus mastership. (I)                                                                                                              |

|                      | Bus Grant                                                                        | BG                        | Indicates that the current bus cycle is complete and the QUICC has relinquished the bus. (O)                                                                                |

|                      | Bus Grand Acknowledge                                                            | BGACK                     | Indicates that an external device has assumed bus mastership. (I)                                                                                                           |

|                      | Read-Modify-Write Cycle<br>Initial Configuration 0                               | RMC<br>CONFIG0            | Identifies the bus cycle as part of an indivisible<br>read-modify-write operation (I/O) or initial QUICC<br>configuration select. (I)                                       |

|                      | Bus Clear Out/Initial<br>Configuration 1/Row<br>Address Select 2<br>Double-Drive | BCLRO/CONFIG1/<br>RAS2DD  | Indicates that an internal device requires the external bus<br>(Open-Drain O) or initial QUICC configuration select (I) or<br>row address select 2 double-drive output. (O) |

| Group                | Signal Name                                                | Mnemonic            | Function                                                                                                                                                                                                                            |

|----------------------|------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus Control          | Data and Size<br>Acknowledge                               | DSACKT - DSACKO     | Provides asynchronous data transfer acknowledgement and dynamic bus sizing (open-drain I/O but driven high before three-stated).                                                                                                    |

|                      | Address Strobe                                             | AS                  | Indicates that a valid address is on the address bus. (I/O)                                                                                                                                                                         |

|                      | Data Strobe                                                | DS                  | During a read cycle, DS indicates that an external device should place valid data on the data bus. During a write cycle, DS indicates that valid data is on the data bus. (I/O)                                                     |

|                      | Size                                                       | SIZ1-SIZ0           | Indicates the number of bytes remaining to be transferred for this cycle. (I/O) $% \left( 1/O\right) =0$                                                                                                                            |

|                      | Read/Write                                                 | R/₩                 | Indicates the direction of data transfer on the bus. (I/O)                                                                                                                                                                          |

|                      | Output Enable Address<br>Multiplex                         | <del>oe</del> /amux | Active during a read cycle indicates that an external device<br>should place valid data on the data bus (O) or provides a<br>strobe for external address multiplexing in DRAM accesses<br>if internal multiplexing is not used. (O) |

| Interrupt<br>Control | Interrupt Request<br>Level 7-1                             | IRQ7-IRQ1           | Provides external interrupt requests to the CPU32+ at priority levels 7-1. (I)                                                                                                                                                      |

|                      | Autovector/Interrupt<br>Acknowledge 5                      | AVEC/IACK5          | Autovector request during an interrupt acknowledge cycle<br>(open-drain I/O) or interrupt level 5 acknowledge line. (O)                                                                                                             |

| System               | Soft Reset                                                 | RESETS              | Soft system reset. (open-drain I/O)                                                                                                                                                                                                 |

| Control              | Hard Reset                                                 | RESETH              | Hard system reset. (open-drain I/O)                                                                                                                                                                                                 |

|                      | Halt                                                       | HALT                | Suspends external bus activity. (open-drain I/O)                                                                                                                                                                                    |

|                      | Bus Error                                                  | BERR                | Indicates an erroneous bus operation is being attempted.<br>(open-drain I/O)                                                                                                                                                        |

| Clock and Test       | System Clock Out 1                                         | CLKO1               | Internal system clock output 1. (O)                                                                                                                                                                                                 |

|                      | System Clock Out 2                                         | CLKO2               | Internal system clock output 2 - normally 2x CLKO1. (O)                                                                                                                                                                             |

|                      | Crystal Oscillator                                         | EXTAL, XTAL         | Connections for an external crystal to the internal oscillator circuit. EXTAL (I), XTAL (O).                                                                                                                                        |

|                      | External Filter Capacitor                                  | XFC                 | Connection pin for an external capacitor to filter the circuit of the PLL. (I)                                                                                                                                                      |

|                      | Clock Mode Select 1-0                                      | MODCK1-MODCK0       | Selects the source of the internal system clock. (I) THESE PINS SHOULD NOT BE SET TO 00                                                                                                                                             |

|                      | Instruction Fetch/<br>Development Serial Input             | IFETCH/DSI          | Indicates when the CPU32+ is performing an instruction word prefetch (O) or input to the CPU32+ background debug mode. (I)                                                                                                          |

|                      | Instruction Pipe 0/<br>Development Serial<br>Output        | IPIPE0/DSO          | Used to track movement of words through the instruction pipeline (O) or output from the CPU32+ background debug mode. (O)                                                                                                           |

|                      | Instruction Pipe 1/Row<br>Address Select 1<br>Double-Drive | IPIPE1/RAS1DD       | Used to track movement of words through the instruction pipeline (O), or a row address select 1 "double-drive" output (O).                                                                                                          |

|                      | Breakpoint/Development<br>Serial Clock                     | BKPT/DSCLK          | Signals a hardware breakpoint to the QUICC (open-drain I/O), or clock signal for CPU32+ background debug mode (I).                                                                                                                  |

|                      | Freeze/Initial<br>Configuration 2                          | FREEZE/CONFIG2      | Indicates that the CPU32+ has acknowledged a breakpoint (O), or initial QUICC configuration select (I).                                                                                                                             |

|                      |                                                            |                     |                                                                                                                                                                                                                                     |

Table 1. System Bus Signal Index (Normal Operation) (Continued)

| Group                      | Signal Name                    | Mnemonic | Function                                                                                                        |  |

|----------------------------|--------------------------------|----------|-----------------------------------------------------------------------------------------------------------------|--|

| Clock and Test<br>(Cont'd) | Three-State                    | TRIS     | Used to three-state all pins if QUICC is configured as a master. Always Sampled except during system reset. (I) |  |

|                            | Test Clock                     | ТСК      | Provides a clock for Scan test logic. (I)                                                                       |  |

|                            | Test Mode Select               | TMS      | Controls test mode operations. (I)                                                                              |  |

|                            | Test Data In                   | TDI      | Serial test instructions and test data signal. (I)                                                              |  |

|                            | Test Data Out                  | TDO      | Serial test instructions and test data signal. (O)                                                              |  |

|                            | Test Reset                     | TRST     | Provides an asynchronous reset to the test controller. (I)                                                      |  |

| Power                      | Clock Synthesizer Power        | VCCSYN   | Power supply to the PLL of the clock synthesizer.                                                               |  |

|                            | Clock Synthesizer Ground       | GNDSYN   | Ground supply to the PLL of the clock synthesizer.                                                              |  |

|                            | Clock Out Power                | VCCCLK   | Power supply to clock out pins.                                                                                 |  |

|                            | Clock Out Ground               | GNDCLK   | Ground supply to clock out pins.                                                                                |  |

|                            | Special Ground 1               | GNDS1    | Special ground for fast AC timing on certain system bus signals.                                                |  |

|                            | Special Ground 2               | GNDS2    | Special ground for fast AC timing on certain system bus signals.                                                |  |

|                            | System Power Supply and Return | VCC, GND | Power supply and return to the QUICC.                                                                           |  |

|                            | No Connect                     | NC4-NC1  | Four no-connect pins.                                                                                           |  |

**Table 1.** System Bus Signal Index (Normal Operation) (Continued)

Note: 1. I denotes input, O denotes output and I/O is input/output.

#### Table 2. Peripherals Signal Index

| Group | Signal Name             | Mnemonic      | Function                                                                                                                             |

|-------|-------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------|

| SCC   | Receive Data            | RXD4-RXD1     | Serial receive data input to the SCCs. (I)                                                                                           |

|       | Transmit Data           | TXD4-TXD1     | Serial transmit data output from the SCCs. (O)                                                                                       |

|       | Request to Send         | RTS4-RTS1     | Request to send outputs indicate that the SCC is ready to transmit data. (O)                                                         |

|       | Clear to Send           | CTS4-CTS1     | Clear to send inputs indicate to the SCC that data transmission may begin. (I)                                                       |

|       | Carrier Detect          | CD4-CD1       | Carrier detect inputs indicate that the SCC should begin reception of data. (I)                                                      |

|       | Receive Start           | RSTRTT        | This output from SCC1 identifies the start of a receive frame.<br>Can be used by an Ethernet CAM to perform address<br>matching. (O) |

|       | Receive Reject          | RRJCT1        | This input to SCC1 allows a CAM to reject the current<br>Ethernet frame after it determines the frame address did not<br>match. (I)  |

|       | Clocks                  | CLK8-CLK1     | Input clocks to the SCCs, SCMs, SI, and the baud rate generators. (I)                                                                |

| IDMA  | DMA Request             | DREQ2-DREQ1   | A request (input) to an IDMA channel to start an IDMA transfer. (I)                                                                  |

|       | DMA Acknowledge         | DACK2-DACK1   | An acknowledgement (output) by the IDMA that an IDMA transfer is in progress. (O)                                                    |

|       | DMA Done                | DONE2-DONE1   | A bidirectional signal that indicates the last IDMA transfer in a block of data. (I/O)                                               |

| TIMER | Timer Gate              | TGATE2-TGATE1 | An input to a timer that enables/disables the counting function. (I)                                                                 |

|       | Timer Input             | TIN4-TIN1     | Time reference input to the timer that allows it to function as a counter. (I)                                                       |

|       | Timer Output            | TOUT4-TOUT1   | Output waveform (pulse or toggle) from the timer as a result of a reference value being reached. (O)                                 |

| SPI   | SPI Master In Slave Out | SPIMISO       | Serial data input to the SPI master (I); serial data output from an SPI slave. (O)                                                   |

|       | SPI Master Out Slave In | SPIMOSI       | Serial data output from the SPI master (O); serial data input to an SPI slave. (I)                                                   |

|       | SPI Clock               | SPICLK        | Output clock from the SPI master (O); input clock to the SPI slave. (I)                                                              |

|       | SPI Select              | SPISEL        | SPI slave select input. (I)                                                                                                          |

| SMC   | SMC Receive Data        | SMRXD2-SMRXD1 | Serial data input to the SMCs. (I)                                                                                                   |

|       | SMC Transmit Data       | SMTXD2-SMTXD1 | Serial data output from the SMCs. (O)                                                                                                |

|       | SMC Sync                | SMSYN2-SMSYN1 | SMC synchronization signal. (I)                                                                                                      |

#### Table 2. Peripherals Signal Index (Continued)

| Group | Signal Name                    | Mnemonic              | Function                                                                                                                        |

|-------|--------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| SI    | SI Receive Data                | L1RXDA, L1RXDB        | Serial input to the time division multiplexed (TDM) channel A or channel B.                                                     |

|       | SI Transmit Data               | L1TXDA, L1TXDB        | Serial output from the TDM channel A or channel B.                                                                              |

|       | SI Receive Clock               | L1RCLKA, L1RCLKB      | Input receive clock to TDM channel A or channel B.                                                                              |

|       | SI Transmit Clock              | L1TCLKA, L1TCLKB      | Input transmit clock to TDM channel A or channel B.                                                                             |

|       | SI Transmit Sync Signals       | L1TSYNCA,<br>L1TSYNCB | Input transmit data sync signal to TDM channel A or channel B.                                                                  |

|       | SI Receive Sync Signals        | L1RSYNCA,<br>L1RSYNCB | Input receive data sync signal to TDM channel A or channel B.                                                                   |

|       | IDL Interface Request          | L1RQA, L1RQB          | IDL interface request to transmit on the D channel. Output from the SI.                                                         |

|       | SI Output Clock                | L1CLKOA, L1CLKOB      | Output serial data rate clock. Can output a data rate clock when the input clock is 2x the data rate.                           |

|       | SI Data Strobes                | L1ST4-L1ST1           | Serial data strobe outputs can be used to gate clocks to external devices that do not have a built-in time slot assigner (TSA). |

| BRG   | Baud Rate Generator<br>Out 4-1 | BRGO4-BRGO1           | Baud rate generator output clock allows baud rate generator to be used externally.                                              |

|       | BRG Input Clock                | CLK2, CLK6            | Baud rate generator input clock from which BRG will derive the baud rates.                                                      |

| PIP   | Port B 15-0                    | PB15-BP0              | PIP Data I/O Pins.                                                                                                              |

|       | Strobe Out                     | STRBO                 | This input causes the PIP output data to be placed on the PIP data pins.                                                        |

|       | Strobe In                      | STRBI                 | This input causes data on the PIP data pins to be latched by the PIP as input data.                                             |

| SDMA  | SDMA Acknowledge 2-1           | SDACK2-SDACK1         | SDMA output signals used in RISC receiver to mark fields in the Ethernet receive frame.                                         |

# Scope

This drawing describes the specific requirements for the microcontroller TS68EN360 - 25 MHz and 33 MHz in compliance with MIL-STD-883 class B or Atmel standard screening.

# Applicable Documents

MIL-STD-883

1

- 1. MIL-STD-883: test methods and procedures for electronics.

- 2. MIL-PRF-38535: general specifications for microcircuits.

- 3. DESC 5962-SMD-97607

# TS68EN360

# **Requirements**

| General                  | This microcircuits are in accordance with the applicable document and as specified herein.                                                                                                                                   |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design and Construction  |                                                                                                                                                                                                                              |

| Terminal Connections     | Depending on the package, the terminal connections shall be as shown in Figure 2 and Figure 3.                                                                                                                               |

| Lead Material and Finish | Lead material and finish shall be as specified in MIL-STD-883 (see enclosed "Ordering Information" on page 79).                                                                                                              |

| Package                  | <ul> <li>The macrocircuits are packaged in hermetically sealed ceramic packages which are conform to case outlines of MIL-STD-1835 or as follow:</li> <li>PGA but see "241-pin – PGA" on page 77</li> <li>CERQUAD</li> </ul> |

|                          | The precise case outlines are described at the end of the specification ("Package Mechanical Data" on page 77) and into MIL-STD-1835.                                                                                        |

# Electrical Characteristics

#### Table 3. Absolute Maximum Ratings

| Rating                           | Symbol           | Value        | Unit |

|----------------------------------|------------------|--------------|------|

| Supply Voltage <sup>(1)(2)</sup> | V <sub>cc</sub>  | -0.3 to +6.5 | V    |

| Input Voltage <sup>(1)(2)</sup>  | V <sub>IN</sub>  | -0.3 to +6.5 | V    |

| Storage Temperature Range        | T <sub>STG</sub> | -55 to +150  | °C   |

Note: This device contains protective circuitry against damage due to high static voltages or electrical fields; however, it iadvised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., eitheGND or  $V_{DD}$ ).

Notes: 1. Permanent damage can occur if maximum ratings are exceeded. Exposure to voltages or currents in excess of recommended values affects device reliability. Device modules may not operate normally while being exposed to electrical extremes.

2. Although sections of the device contain circuitry to protect against damage from high static voltages or electrical fieldsake normal precautions to avoid exposure to voltages higher than maximum-rated voltages.

The supply voltage V<sub>CC</sub> must start and restart from 0.0V; otherwise, the 360 will not come out of reset properly.Unless otherwise stated, all voltages are referenced to the reference terminal.

#### Table 4. Recommended Conditions Of Use

Unless otherwise stated, all voltages are referenced to the reference terminal.

| Symbol            | Parameter                            |                      | Min. | Тур.            | Max. | Unit |

|-------------------|--------------------------------------|----------------------|------|-----------------|------|------|

| V <sub>CC</sub>   | Supply Voltage Range                 | +4.75                |      | +5.25           | V    |      |

| V <sub>IL</sub>   | Logic Low Level Input Voltage Range  | GND                  |      | +0.8            | V    |      |

| V <sub>IH</sub>   | Logic High Level Input Voltage Range | +2.0                 |      | V <sub>cc</sub> | V    |      |

| T <sub>case</sub> | Operating Temperature                | -55                  |      | +125            | °C   |      |

| V <sub>OH</sub>   | High Level Output Voltage            | +2.4                 |      |                 | V    |      |

| f <sub>sys</sub>  | System Frequency                     | (For 25 MHz version) |      | 25              |      | MHz  |

|                   |                                      | (For 33 MHz version) |      | 33              |      | MHz  |

#### Table 5. Thermal Characteristics

| Symbol | Parameter                                | Value           | Unit |      |

|--------|------------------------------------------|-----------------|------|------|

| JC     | Thermal Resistance - Junction to Case    | 240-pin Cerquad | 2    | °C/W |

|        |                                          | 241-pin PGA     | 7    | °C/W |

| JA     | Thermal Resistance - Junction to Ambient | 240-pin Cerquad | 27.4 | 0000 |

|        |                                          | 241-pin PGA     | 22.8 | °C/W |

$\mathsf{T}_{\mathsf{I}} = \mathsf{T}_{\mathsf{\Delta}} + (\mathsf{P}_{\mathsf{D}} \cdot \theta_{\mathsf{I}})$  $\mathsf{P}_{\mathsf{D}} = (\mathsf{V}_{\mathsf{D}\mathsf{D}} \cdot \mathsf{I}_{\mathsf{D}\mathsf{D}}) + \mathsf{P}_{\mathsf{I}/\mathsf{O}}$ Where P<sub>I/O</sub> is the power dissipation on pins. **Power Considerations** The average chip-junction temperature,  $T_J$ , in °C can be obtained from:  $\mathsf{T}_{\mathsf{J}} = \mathsf{T}_{\mathsf{A}} \div (\mathsf{P}_{\mathsf{D}} \cdot \Theta_{\mathsf{J}})$ (1) where: T<sub>A</sub> = Ambient Temperature, °C  $\Theta_{JA}$  = Package Thermal Resistance, Junction-to-Ambient, C/W  $P_D = P_{INT} + P_{I/O}$  $P_{INT} = I_{CC} \cdot V_{CC}$ , Watts-chip Internal Power P<sub>I/O</sub> = Power Dissipation on Input and Output Pins-User Determined For most applications,  $P_{I/O} < 0.3 \cdot P_{INT}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:  $\mathsf{P}_{\mathsf{D}} = \mathsf{K} \div (\mathsf{T}_{\mathsf{J}} + 273^{\circ}\mathsf{C})$ (2)Solving Equations (1) and (2) for K gives:  $K = P_D \cdot (T_A + 273^{\circ}C) + \Theta_{JA} \cdot P_D^{-2}$ (3)where K is a constant pertaining to the particular part. K can be determined from Equation (3) by measuring  $P_D$  (at thermal equilibrium) for a know  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving Equations (1) and (2) iteratively for any value of  $T_A$ .

| Mechanical and<br>Environment     | The microcircuits shall meet all mechanical environmental requirements of either MIL-STD-883 for class B devices or for Atmel standard screening.                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Marking                           | <ul> <li>The document where are defined the marking are identified in the related reference documents. Each microcircuit are legible and permanently marked with the following information as minimum:</li> <li>Atmel logo</li> <li>Manufacturer's part number</li> <li>Class B identification</li> <li>Date-code of inspection lot</li> <li>ESD identifier if available</li> <li>Country of manufacturing</li> </ul>                                                                                                                                |

| Quality Conformance<br>Inspection |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DESC/MIL-STD-883                  | Is in accordance with MIL-M-38535 and method 5005 of MIL-STD-883. Group A and B inspections are performed on each production lot. Group C and D inspections are performed on a periodical basis.                                                                                                                                                                                                                                                                                                                                                     |

| Electrical<br>Characteristics     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| General Requirements              | <ul> <li>All static and dynamic electrical characteristics specified for inspection purposes and the relevant measurement conditions are given below:</li> <li>Static electrical characteristics for the electrical variants</li> <li>Dynamic electrical characteristics for TS68EN360 (25 MHz, 33 MHz)</li> <li>For static characteristics, test methods refer to IEC 748-2 method number, where existing.</li> <li>For dynamic characteristics, test methods refer to clause "Static Characteristics" on page 14 of this specification.</li> </ul> |

#### **Static Characteristics**

GND = 0  $V_{dc}$ ,  $T_{C}$  = -55 to +125°C. The electrical specifications in this document are preliminary. (See numbered notes).

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Symbol           | Min.                   | Max.                                   | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------|----------------------------------------|------|

| Input High Voltage (except EXTAL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>IH</sub>  | 2.0                    | V <sub>cc</sub>                        | V    |

| Input Low Voltage (5V Part)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>IL</sub>  | GND                    | 0.8                                    | V    |

| Input Low Voltage (Part Only; PA8-15, PB1, PC5, PC7, TCK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | YL.              | GND                    | 0.5                                    | V    |

| Input Low Voltage (Part Only; All Other Pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | YL               | GND                    | 0.8                                    | V    |

| EXTAL Input High Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>IHC</sub> | 0.8*(V <sub>CC</sub> ) | V <sub>CC</sub> + 0.3                  | V    |

| Undershoot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                | -                      | -0.8                                   | V    |

| Input Leakage Current (All Input Only Pins except for TMS, TDI and TRST) Vin = $0/5V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | lin              | -2.5                   | 2.5                                    | αA   |

| Hi-Z (Off-State) Leakage Current (All Noncrystal Outputs and I/O Pins except TMS,TDI and TRST) Vin = $0/5V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I <sub>oz</sub>  | -2.5                   | -2.5                                   | αA   |

| Signal Low Input Current $V_{IL} = 0.8V$ (TMS, TDI and TRST Pins Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Ι <sub>L</sub>   | -0.5                   | 0.5                                    | mA   |

| Signal High Input Current $V_{IH}$ = 2.0V (TMS, TDI and TRST Pins Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I <sub>H</sub>   | -0.5                   | 0.5                                    | mA   |

| Output High Voltage<br>$I_{OH} = -0.8 \text{ mA}, V_{CC} = 4.75 \text{V}$<br>All Noncrystal Outputs Except Open Drain Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>OH</sub>  | 2.4                    | -                                      | V    |

| Output Low Voltage<br>$I_{OL} = 2.0 \text{ mA}, \text{CLKO1-2}, \text{FREEZE}, \text{1PIPE0T}, \text{1FETCH}, \text{BKPTO}$<br>$I_{OL} = 3.2 \text{ mA}, \text{A31-A0}, \text{D31-D0}, \text{FC3-0}, \text{SIZ0-1}, \text{PA0}, 2, 4, 6, 8-15, \text{PB0-5}, \text{PB8-17}, \text{PC0-11}, \text{TDO}, \text{PERR}, \text{PRTY0-3}, \text{TOUT0-2}, \text{AVECO}, \text{AS}, \text{CAS3-0}, \text{BLCRO}, \text{RAS0-7}$<br>$I_{OL} = 5.3 \text{ mA}, \text{DSACK0-T}, \text{R/W}, \text{DS}, \text{OE}, \text{RMC}, \text{BG}, \text{BGACK}, \text{BERR}$<br>$I_{OL} = 7 \text{ mA}, \text{TXD1-4}$<br>$I_{OL} = 8.9 \text{ mA}, \text{PB6}, \text{PB7}, \text{HALT}, \text{RESET}, \text{BR} (\text{Output})$ | V <sub>OL</sub>  | -                      | 0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5 | V    |

| Input Capacitance<br>All I/O Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Cin              | -                      | 20                                     | pF   |

| Load Capacitance (except CLKO1-2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CL               | -                      | 100                                    | pF   |

| Load Capacitance (CLKO1-2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLC              |                        | 50                                     | pF   |

| Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>CC</sub>  | 4.75                   | 5.25                                   | V    |

#### **Dynamic Characteristics**

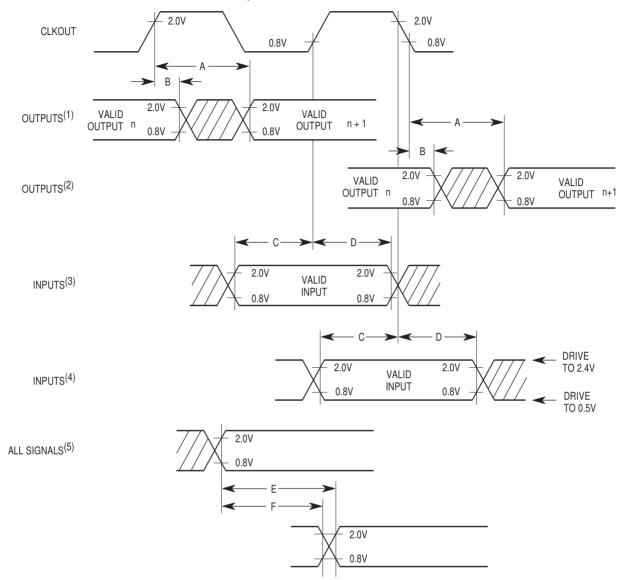

The AC specifications presented consist of output delays, input setup and hold times, and signal skew times. All signals are specified relative to an appropriate edge of the clock and possibly to one or more other signals.

The measurement of the AC specifications is defined by the waveforms shown in Figure 5. To test the parameters guaranteed by Atmel inputs must be driven to the voltage levels specified in the figure. Outputs are specified with minimum and/or maximum limits, as appropriate, and are measured as shown. Inputs are specified with minimum setup and hold times and are measured as shown. Finally, the measurement for signal-to-signal specifications are shown.

Note that the testing levels used to verifyconformance to the AC specifications do not affect the guaranteed DC operation of the device as specified in the DC electrical characteristics.

#### Figure 5. Drive Levels and Test Points For AC Specifications

Notes: 1. This output timing is applicable to all parameters specified relative to the rising edge of the clock.

- 2. This output timing is applicable to all parameters specified relative to the falling edge of the clock.

- 3. This input timing is applicable to all parameters specified relative to the rising edge of the clock.

- 4. This input timing is applicable to all parameters specified relative to the falling edge of the clock.

- 5. This timing is applicable to all parameters specified relative to the assertion/negation of another signal.

Legend:

- a) Maximum output delay specification.

- b) Minimum output hold time.

- c) Minimum input setup time specification.

- d) Minimum input hold time specification.

- e) Signal valid to signal valid specification (maximum or minimum).

- f) Signal valid to signal invalid specification (maximum or minimum).

# <u>AIME</u>

### **AC Power Dissipation**

#### Table 6. Typical Current Drain

| Mode of Operation                                 | Symbol                                 | System Clock<br>Frequency | BRGCLK Clock<br>Frequency | SyncCLK Clock<br>Frequency | Тур        | Unit |

|---------------------------------------------------|----------------------------------------|---------------------------|---------------------------|----------------------------|------------|------|

| Normal mode (Rev $A^{(1)}$ and Rev $B^{(2)}$ )    | I <sub>DD</sub>                        | 25 MHz                    | 25 MHz                    | 25 MHz                     | 250        | mA   |

| Normal Mode (Rev C <sup>3)</sup> and Newer)       | I <sub>DD</sub>                        | 25 MHz                    | 25 MHz                    | 25 MHz                     | 237        | mA   |

| Normal Mode                                       | I <sub>DD</sub>                        | 33 MHz                    | 33 MHz                    | 33 MHz                     | 327        | mA   |

| Low Power Mode                                    | I <sub>DDSB</sub>                      | Divide by 2<br>12.5 MHz   | Divide by 16<br>1.56 MHz  | Divide by 2<br>12.5 MHz    | 150        | mA   |

| Low Power Mode                                    | I <sub>DDSB</sub>                      | Divide by 4<br>6.25 MHz   | Divide by 16<br>1.56 MHz  | Divide by 4<br>6.25 MHz    | 85         | mA   |

| Low Power Mode                                    | I <sub>DDSB</sub>                      | Divide by 16<br>1.56 MHz  | Divide by 16<br>1.56 MHz  | Divide by 4<br>6.25 MHz    | 35         | mA   |

| Low Power Mode                                    | I <sub>DDSB</sub>                      | Divide by 256<br>97.6 kHz | Divide by 16<br>1.56 MHz  | Divide by 4<br>6.25 MHz    | 20         | mA   |

| Low Power Mode                                    | I <sub>DDSB</sub>                      | Divide by 256<br>97.6 kHz | Divide by 64<br>390 kHz   | Divide by 64<br>390 kHz    | 13         | mA   |

| Low Power Stop VCO Off <sup>4)</sup>              | I <sub>DDSP</sub>                      |                           |                           |                            | 0.5        | mA   |

| PLL Supply Current<br>PLL Disabled<br>PLL Enabled | I <sub>ddpd</sub><br>I <sub>ddpe</sub> |                           |                           |                            | TBD<br>TBD |      |

Notes: 1. Rev A mask is C63T

2. Rev B masks are C69T and F35G

3. Current Rev C masks are E63C, E68C and F15W

4. EXTAL frequency is 32 kHz

All measurements were taken with only CLKO1 enabled,  $V_{CC}$  = 5.0V,  $V_{IL}$  = 0V and  $V_{IH}$  =  $V_{CC}$

#### Table 7. Maximum Power Dissipation

| System Frequency | V <sub>cc</sub> | Max P <sub>D</sub> | Unit | Mask                                          |

|------------------|-----------------|--------------------|------|-----------------------------------------------|

| 25 MHz           | 5.25V           | 1.80               | W    | REV A <sup>(1)</sup> and REV B <sup>(2)</sup> |

| 25 MHz           | 5.25V           | 1.45               | W    | REV C <sup>(3)</sup> and Newer                |

| 25 MHz           | 3.6V            | 0.65               | W    | REV C <sup>(3)</sup> and Newer                |

| 33 MHz           | 5.25V           | 2.00               | W    | REV C <sup>(3)</sup> and Newer                |

Notes: 1. Rev A mask is C63T

2. Rev B masks are C69T and F35G

3. Current Rev C masks are E63C, E68C and F15W

### **AC Electrical Specifications Control Timing**

GND = 0 Vdc,  $T_c = -55$  to +125°C. The electrical specifications in this document are preliminary (See Figure 6).

|        | Characteristic                                                                                               |                     | 25 MHz            |       | 33.34 MHz |       |      |

|--------|--------------------------------------------------------------------------------------------------------------|---------------------|-------------------|-------|-----------|-------|------|

| Number |                                                                                                              | Symbol              | Min               | Max   | Min       | Max   | Unit |

|        | System Frequency                                                                                             | f <sub>sys</sub>    | dc <sup>(1)</sup> | 25.00 |           | 33.34 | MHz  |

|        | Crystal Frequency                                                                                            | f <sub>XTAL</sub>   | 25                | 6000  | 25        | 6000  | kHz  |

|        | On-Chip VCO System Frequency                                                                                 | f <sub>sys</sub>    | 20                | 50    | 20        | 67    | MHz  |

|        | Start-up Time<br>With external clock (oscillator disabled) or after<br>changing the multiplication factor MF | t <sub>pll</sub>    |                   | 2500  |           |       | clks |

|        | CLKO1-2 stability                                                                                            | Ц <sub>LK</sub>     | TBD               | TBD   |           |       | %    |

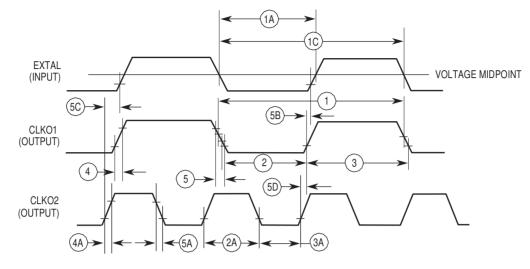

| 1      | CLKO1 Period                                                                                                 | t <sub>cyc</sub>    | 40                | -     | 30        | -     | ns   |

| 1A     | EXTAL Duty Cycle, MF                                                                                         | t <sub>dcyc</sub>   | 40                | 60    | 40        | 60    | %    |

| 1C     | External Clock Input Period                                                                                  | t <sub>EXTcyc</sub> | 40                | -     | 30        | -     | ns   |

| 2, 3   | CLKO1 Pulse Width (Measured at 1.5V)                                                                         | ŧw1                 | 19                | -     | 14        | -     | ns   |

| 2A, 3A | CLKO2 Pulse Width (Measured at 1.5V)                                                                         | Łw2                 | 9.5               | -     | 7         | -     | ns   |

| 4, 5   | CLKO1 Rise and Fall Times (Full drive)                                                                       | ¢rf1                | -                 | 2     | -         | 2     | ns   |

| 4A, 5A | CLKO2 Rise and Fall Times (Full drive)                                                                       | ŧrf2                | -                 | 2     | -         | 1.6   | ns   |

| 5B     | EXTAL to CLKO1 Skew-PLL enabled (MF< 5)                                                                      | ĖXTP1               |                   | а     |           | а     | ns   |

| 5C     | EXTAL to CLKO2 Skew-PLL enabled (MF< 5)                                                                      | Ėxtp2               |                   | а     |           | а     | ns   |

| 5D     | CLKO1 to CLKO2 Skew                                                                                          | Atmel <sub>kw</sub> |                   | а     |           | а     | ns   |

Note: 1. Note that the minimum VCO frequency and the PLL default values put some restrictions on the minimum system frequency. The following calculation should be used to determine the actual value for specifications 5B, 5C and 5D.

5B: 25 MHz  $\pm (0.9 \text{ ns} + 0.25 \text{ x} \text{ (rise time)}) (1.4 \text{ ns} @ \text{ rise} = 2 \text{ ns}; 1.9 \text{ ns} @ \text{ rise} = 4 \text{ ns})$

33 MHz  $\pm (0.5 \text{ ns} + 0.25 \text{ x} \text{ (rise time)}) (1 \text{ ns} @ \text{ rise} = 2 \text{ ns}; 1.5 \text{ ns} @ \text{ rise} = 4 \text{ ns})$

5C: 25/33 MHz ±(2 ns + 0.25 x (rise time)) (2.5 ns @ rise = 2 ns; 3 ns @ rise = 4 ns)

5D: 25 MHz  $\pm$  (3 ns + 0.5 x (rise time)) (4 ns @ rise = 2 ns; 5 ns @ rise = 4 ns)

33 MHz ±(2.5 ns + 0.5 x (rise time)) (3.5 ns @ rise = 2 ns; 4.5 ns @ rise = 4 ns)

#### Figure 6. Clock Timing

#### **External Capacitor For PLL**

GND = 0 Vdc,  $T_{C} = -55$  to  $+125^{\circ}C$ . The electrical specifications in this document are preliminary.

| Characteristic                                       | Symbol                  | Min      | Max      | Unit |

|------------------------------------------------------|-------------------------|----------|----------|------|

| PLL External Capacitor (XFC to VCCSYN)               | <b>C</b> <sub>XFC</sub> |          |          |      |

| MF< 5 (Recommended value MF x 400 pF) <sup>(1)</sup> |                         | MF x 340 | MF x 480 | pF   |

| MF> 4 (Recommended value MF x 540 pF) <sup>(1)</sup> |                         | MF x 380 | MF x 970 | pF   |

Note: 1. MF - multiplication factor.

#### Examples:

- Notes: 1. MODCK1 pin = 0, MF =  $1 \Rightarrow CxFC = 400 \text{ pF}$

- MODCK1 pin = 1, crystal is 32.768 kHz (or 4.192 MHz), initial MF = 401, initial frequency = 13.14 MHz, later on MF is changed to 762 to support a frequency of 25 MHz. Minimum &FC is: 762 x 380 = 289 nF, Maximum C<sub>FC</sub> is: 401 x 970 = 390 nF. The recommended CxFC for 25 MHz is: 762 x 540 = 414 nF. 289 nF < &FC < 390 nF and closer to 414 nF. The proper available value for CxFC is 390 nF.</li>

- MODCK1 pin = 1, crystal is 32.768 kHz (or 4.192 MHz), initial MF = 401, initial frequency = 13.14 MHz, later on MF is changed to 1017 to support a frequency of 33.34 MHz. Minimum &Fc is: 1017 x 380 = 386 nF, Maximum &Fc is: 401 x 970 = 390 nF ⇒ 386 nF < CxFc < 390 nF. The proper available value for &Fc is 390 nF.</li>

- In order to get higher range, higher crystal frequency can be used (i.e. 50 kHz), in this case: Minimum CXFC is: 667 x 380 = 253 nF, Maximum QFC is: 401 x 970 = 390 nF⇒ 386 nF < CXFC < 390 nF.</li>

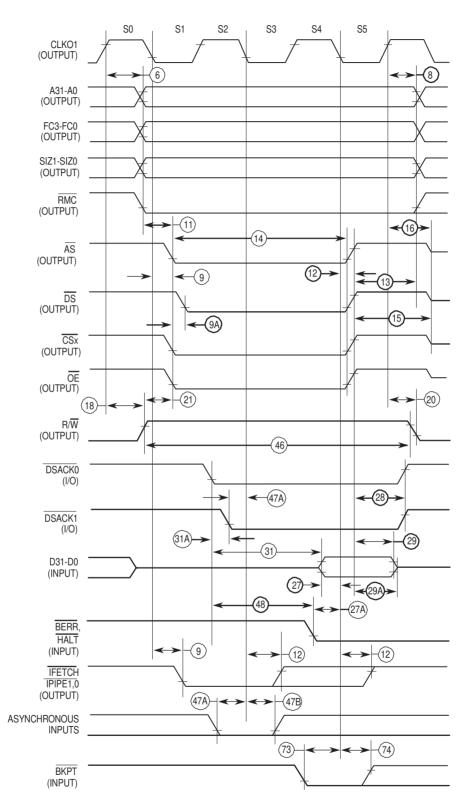

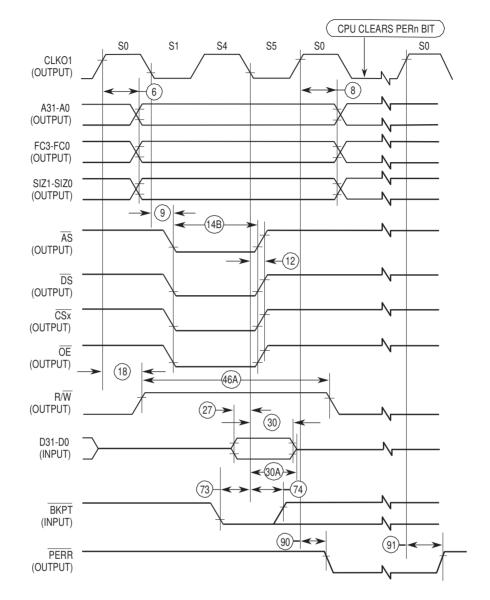

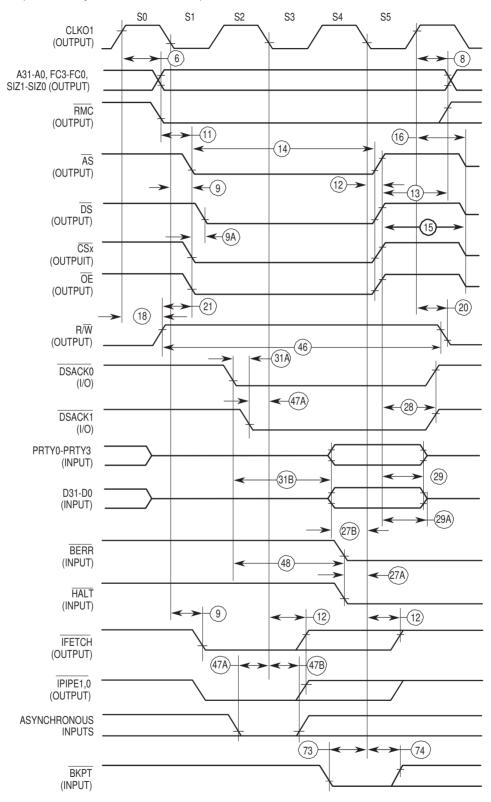

# **Bus Operation AC Timing Specifications**

GND = 0 Vdc,  $T_c$  = -55 to +125°C. The electrical specifications in this document are preliminary (See Figure 7 to Figure 23).

|                               | Characteristic                                                                   |                    | 25 MHz |     | 33.34 MHz |       |      |

|-------------------------------|----------------------------------------------------------------------------------|--------------------|--------|-----|-----------|-------|------|

| Number                        |                                                                                  | Symbol             | Min    | Max | Min       | Max   | Unit |

| 6                             | CLKO1 High to Address, FC, SIZ, RMCValid                                         | t <sub>chav</sub>  | 0      | 15  | 0         | 12    | ns   |

| 6A                            | CLKO1 High to Address Valid (GAMX = 1)                                           | <b>E</b> HAV       | 0      | 20  | 0         | 15    | ns   |

| 7                             | CLKO1 High to Address, Data, FC, SIZ, RMCHigh<br>Impedance                       | t <sub>CHAZx</sub> | 0      | 40  | 0         | 30    | ns   |

| 8                             | CLKO1 High to Address, Data, FC, SIZ, RMC Invalid                                | t <sub>CHAZn</sub> | -2     | -   | -2        | -     | ns   |

| 9                             | CLKO1 Low to AS, DS, OE, WE, IFETCH, IPIPE, IACKX Asserted                       | t <sub>CLSA</sub>  | 3      | 20  | 3         | 15    | ns   |

| 9 <sup>(10)</sup>             | CLKO1 Low to CSTRAST Asserted                                                    | t <sub>CLSA</sub>  | 4      | 16  | 4         | 12    | ns   |

| 9B <sup>(11)</sup>            | CLKO1 High to CST/RAST Asserted                                                  | t <sub>CHCA</sub>  | 4      | 16  | 4         | 12    | ns   |

| 9A <sup>(2)(10)</sup>         | AS to DS or CSX/RASX or OE Asserted (Read)                                       | t <sub>stsa</sub>  | -6     | 6   | -5.625    | 5.625 | ns   |

| 9C <sup>(2)(11)</sup>         | AS to CSX/RASX Asserted                                                          | t <sub>stca</sub>  | 14     | 26  | 9         | 21    | ns   |

| 11 <sup>(10)</sup>            | Address, FC, SIZ, RMC, valid to AS, CSX/RASX,<br>OE, WE, (and DS Read) Asserted  | t <sub>AVSA</sub>  | 10     | -   | 8         | -     | ns   |

| 11A <sup>(11)</sup>           | Address, FC, SIZ, RMC, Valid to CSX/RASX<br>Asserted                             | t <sub>AVCA</sub>  | 30     | -   | 22.5      | -     | ns   |

| 12                            | CLKO1 Low to AS, DS, OE, WE, IFETCH, IPIPE, IACKX Negated                        | t <sub>CLSN</sub>  | 3      | 20  | 3         | 15    | ns   |

| 12 <sup>(16)</sup>            | CLKO1 Low to CSXRASX Negated                                                     | t <sub>CLSN</sub>  | 4      | 16  | 4         | 12    | ns   |

| 12A <sup>(13)(16)</sup>       | CLKO1 High to CST/RAST Negated                                                   | t <sub>CHCN</sub>  | 4      | 16  | 4         | 12    | ns   |

| 12B                           | CS negate to WE negate (CSNTQ = 1)                                               | Atmeļ <sub>w</sub> | 15     | -   | 12        | -     | ns   |

| 13 <sup>(12)</sup>            | AS, DS, CSx, OE, WE, IACKx Negated to Address,<br>FC, SIZ Invalid (Address Hold) | t <sub>snai</sub>  | 10     | -   | 7.5       | -     | ns   |

| 13A <sup>(13)</sup>           | CSx Negated to Address, FC, SIZ, Invalid (Address Hold)                          | t <sub>cnai</sub>  | 30     | -   | 22.5      | -     | ns   |

| <b>14</b> <sup>(10)(12)</sup> | AS, CSx, OE, WE (and DS Read) Width Asserted                                     | t <sub>swa</sub>   | 75     | -   | 56.25     | -     | ns   |

| 14C <sup>(11)(13)</sup>       | CSx Width Asserted                                                               | t <sub>cwa</sub>   | 35     | -   | 26.25     | -     | ns   |

| 14A                           | DS Width Asserted (Write)                                                        | t <sub>swaw</sub>  | 35     | -   | 26.25     | -     | ns   |

| 14B                           | AS, CSx, OE, WE, IACKx, (and DS Read) Width<br>Asserted (Fast Termination Cycle) | t <sub>swow</sub>  | 35     | -   | 26.25     | -     | ns   |

| 14D <sup>(13)</sup>           | CSx Width Asserted (Fast Termination Cycle)                                      | ŧwdw               | 15     | -   | 10        | -     | ns   |

| 15 <sup>(3)(10)(12)</sup>     | AS, DS, CSx, OE, WE Width Negated                                                | t <sub>sn</sub>    | 35     | -   | 26.25     | -     | ns   |

| 16                            | CLKO1 High to AS, DS, R/₩ High Impedance                                         | t <sub>chsz</sub>  | -      | 40  | -         | 30    | ns   |

| 17 <sup>(12)</sup>            | AS, DS, CSx, WE Negated to R/W High                                              | t <sub>snrn</sub>  | 10     | -   | 7.5       | -     | ns   |

| 17A <sup>(13)</sup>           | CSx Negated to R/W High                                                          | t <sub>CNRN</sub>  | 30     | -   | 22.5      | -     | ns   |

| 18                            | CLKO1 High to R/W High                                                           | t <sub>chrh</sub>  | 0      | 20  | 0         | 15    | ns   |