Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# IDT Tsi340™ PCI-to-PCI Bridge User Manual

80E3000\_MA001\_05

September 2009

6024 Silver Creek Valley Road, San Jose, California 95138

Telephone: (800) 345-7015 • (408) 284-8200 • FAX: (408) 284-2775

Printed in U.S.A.

©2009 Integrated Device Technology, Inc.

#### GENERAL DISCLAIMER

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

#### CODE DISCLAIMER

Code examples provided by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of the code examples below is completely at your own risk. IDT MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND CONCERNING THE NONINFRINGEMENT, QUALITY, SAFETY OR SUITABILITY OF THE CODE, EITHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. FURTHER, IDT MAKES NO REPRESENTATIONS OR WARRANTIES AS TO THE TRUTH, ACCURACY OR COMPLETENESS OF ANY STATEMENTS, INFORMATION OR MATERIALS CONCERNING CODE EXAMPLES CONTAINED IN ANY IDT PUBLICATION OR PUBLIC DISCLOSURE OR THAT IS CONTAINED ON ANY IDT INTERNET SITE. IN NO EVENT WILL IDT BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, INCIDENTAL, INDIRECT, PUNITIVE OR SPECIAL DAMAGES, HOWEVER THEY MAY ARISE, AND EVEN IF IDT HAS BEEN PREVIOUSLY ADVISED ABOUT THE POSSIBILITY OF SUCH DAMAGES. The code examples also may be subject to United States export control laws and may be subject to the export or import laws of other countries and it is your responsibility to comply with any applicable laws or regulations.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- 1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

IDT, the IDT logo, and Integrated Device Technology are trademarks or registered trademarks of Integrated Device Technology, Inc.

| Ab | out tl | his Doo    | cument                                     | . 13 |

|----|--------|------------|--------------------------------------------|------|

|    | Scop   | e          |                                            | 13   |

|    | Docu   | ment Con   | nventions                                  | 13   |

|    | Revis  | sion Histo | ory                                        | 14   |

| 1. | Fur    | octiona    | Il Overview                                | 15   |

| "  | 1.1    |            | ew                                         |      |

|    | 1.1    |            | ewes                                       |      |

|    | 1.2    |            | onal Overview                              |      |

|    | 1.3    |            | Posted Write Buffer                        |      |

|    |        | 1.3.1      | Posted Write Queue                         |      |

|    |        | 1.3.2      |                                            |      |

|    |        | 1.3.3      | Non-Posted Buffer                          |      |

|    |        | 1.3.4      | Non-Posted Queue                           |      |

|    |        | 1.3.5      | Configuration Space                        |      |

|    |        | 1.3.6      | Address Decoding Logic                     |      |

|    |        | 1.3.7      | Secondary Bus Arbiter                      |      |

|    | 1.4    | 1.3.8      | Hot Swap Interface                         |      |

|    | 1.4    |            | low                                        |      |

|    |        | 1.4.1      | Memory Read Transactions                   |      |

|    |        | 1.4.2      | Posted Write Transaction Flow              | 21   |

| 2. | PCI    | Interfa    | ace                                        | . 23 |

|    | 2.1    | Overvie    | ew                                         | 23   |

|    | 2.2    |            | ction Types                                |      |

|    |        | 2.2.1      | Transaction Types Not Supported            |      |

|    |        | 2.2.2      | Address Phase                              |      |

|    |        | 2.2.3      | Device Select (DEVSEL#) Generation         |      |

|    |        | 2.2.4      | Data Phase Transactions                    |      |

|    | 2.3    | Configu    | uration Transactions                       |      |

|    |        | 2.3.1      | Type 0 Access to Tsi340                    |      |

|    |        | 2.3.2      | Type 1 to Type 0 Translation               |      |

|    |        | 2.3.3      | Type 1 to Type 1 Forwarding                |      |

|    |        | 2.3.4      | Special Cycles                             |      |

|    | 2.4    | Transac    | ction Termination                          |      |

|    |        | 2.4.1      | Master Termination Initiated by Tsi340     |      |

|    |        | 2.4.2      | Master Abort Received by Tsi340            |      |

|    |        | 2.4.3      | Target Termination Received by Tsi340      |      |

|    |        | 2.4.4      | Delayed Write Target Termination Response. |      |

|    |        | 2.4.5      | Posted Write Target Termination Response   |      |

|    |        | 2.4.6      | Delayed Read Target Termination Response   |      |

|    |        | 2.4.7      | Target Termination Initiated by Tsi340     |      |

|    | 2.5    |            | ctPCI Hot-swap Support                     |      |

|    |        | I          | A A A A A A A A A A A A A A A A A A A      |      |

| 3. | Add | Iress Decoding                                                       | 45 |

|----|-----|----------------------------------------------------------------------|----|

|    | 3.1 | Overview of Address Decoding.                                        | 45 |

|    | 3.2 | Address Ranges                                                       |    |

|    | 3.3 | I/O Address Decoding                                                 | 45 |

|    |     | 3.3.1 Base and Limit Address Registers                               | 46 |

|    |     | 3.3.2 ISA Mode                                                       | 48 |

|    | 3.4 | Memory Address Decoding                                              | 49 |

|    |     | 3.4.1 Memory-Mapped I/O Base and Limit Address Registers             | 49 |

|    |     | 3.4.2 Prefetchable Memory Base and Limit Address Registers           | 50 |

|    |     | 3.4.3 Prefetchable Memory 64-Bit Addressing Registers                | 52 |

|    | 3.5 | VGA Support                                                          | 53 |

|    |     | 3.5.1 VGA Mode                                                       | 53 |

|    |     | 3.5.2 VGA Snoop Mode                                                 | 54 |

| 4. | Tra | nsaction Ordering                                                    | 55 |

|    | 4.1 | Overview of Transaction Ordering                                     |    |

|    | 4.2 | Transaction Governed by Ordering Rules                               |    |

|    | 2   | 4.2.1 Combining or Merging Transactions                              |    |

|    | 4.3 | General Ordering Guidelines.                                         |    |

|    |     | 4.3.1 Ordering Rules                                                 |    |

| 5. | PCI | Bus Arbitration                                                      | 50 |

| 0. | 5.2 | Primary PCI Bus Arbitration                                          |    |

|    | 3.2 | 5.2.1 Transactions                                                   |    |

|    | 5.3 | Secondary PCI Bus Arbitration                                        |    |

|    | 3.3 | 5.3.1 Secondary Bus Arbitration Using the Internal Arbiter           |    |

|    | 5.4 | Bus Parking                                                          |    |

| c  |     |                                                                      |    |

| 6. |     | or Handling                                                          |    |

|    | 6.1 | Overview                                                             |    |

|    | 6.2 | Address Parity Errors                                                |    |

|    | 6.3 | Data Parity Errors                                                   |    |

|    |     | 6.3.1 Configuration Write Transactions to Tsi340 Configuration Space |    |

|    |     | 6.3.2 Read Transactions                                              |    |

|    |     | 6.3.3 Delayed Write Transactions.                                    |    |

|    | 6.1 | 6.3.4 Posted Write Transactions                                      |    |

|    | 6.4 | System Error (SERR#) Reporting                                       |    |

|    |     | 6.4.1 Assertion of P_SERR_b                                          |    |

|    |     |                                                                      |    |

| 7. |     | Power Management                                                     |    |

|    | 7.1 | PCI Power Management                                                 | 73 |

| 8. | Res | et, Clock, and Initialization                                        | 75 |

|    | 8.1 | Clocking.                                                            | 75 |

|    |     | 8.1.1 Primary Input                                                  | 75 |

|     |      | 8.1.2     | Secondary Clock Outputs                    | 75    |

|-----|------|-----------|--------------------------------------------|-------|

|     |      | 8.1.3     | Clock Run                                  | 75    |

|     | 8.2  | Reset     |                                            | 76    |

|     |      | 8.2.1     | Primary Interface Reset                    | 76    |

|     |      | 8.2.2     | Secondary Interface Reset                  | 76    |

|     |      | 8.2.3     | Chip Reset                                 | 77    |

| 0   | Ciar | aala an   | d Dinout                                   | 70    |

| 9.  | _    |           | d Pinout                                   |       |

|     | 9.1  |           | N                                          |       |

|     | 9.2  | •         |                                            |       |

|     |      | 9.2.1     | Primary Bus Interface Signals              |       |

|     |      | 9.2.2     | Secondary Bus Interface Signals            |       |

|     |      | 9.2.3     | Clocks and Resets                          |       |

|     |      | 9.2.4     | Miscellaneous Signals                      |       |

|     | 9.3  | Pinout .  |                                            | 87    |

| 10. | Elec | ctrical ( | Characteristics                            | . 93  |

|     | 10.1 | Absolute  | Maximum Ratings                            | 93    |

|     | 10.2 |           | nended Operating Conditions                |       |

|     | 10.3 |           | Current                                    |       |

|     | 10.4 |           | upply Sequencing                           |       |

|     | 10.5 |           | rating Characteristics                     |       |

|     | 10.6 |           | ing Specifications                         |       |

|     | 10.0 | 10.6.1    | PCI Interface AC Timing                    |       |

|     |      | 10.6.1    | PCI Clock (PCI_CLK) Specification.         |       |

|     | 10.7 |           | ing Waveforms                              |       |

|     |      |           |                                            |       |

| 11. | Reg  | ister D   | escriptions                                | 101   |

|     | 11.1 | Overvie   | w                                          | . 101 |

|     | 11.2 | PCI Con   | figuration Space                           | . 102 |

|     |      | 11.2.1    | Accessing Configuration Space Registers    | . 102 |

|     | 11.3 | Register  | Map                                        | . 103 |

|     | 11.4 | PCI-to-F  | CI Bridge Standard Register Descriptions   | . 107 |

|     |      | 11.4.1    | Vendor ID Register—Offset 0x00             | . 107 |

|     |      | 11.4.2    | Device ID Register—Offset 0x00             | . 107 |

|     |      | 11.4.3    | Primary Command Register—Offset 0x04       | . 108 |

|     |      | 11.4.4    | Primary Status Register—Offset 0x04        |       |

|     |      | 11.4.5    | Revision ID Register—Offset 0x08           |       |

|     |      | 11.4.6    | Programming Interface Register—Offset 08   |       |

|     |      | 11.4.7    | Subclass Code Register—Offset 0x08         |       |

|     |      | 11.4.8    | Base Class Code Register—Offset 0x08       |       |

|     |      | 11.4.9    | Cache Line Size Register—Offset 0x0C       |       |

|     |      | 11.4.10   | Primary Latency Timer Register—Offset 0x0C |       |

|     |      | 11.4.11   | Header Type Register—Offset 0x0C           |       |

|     |      | 11.4.12   | Primary Bus Number Register—Offset 0x18    |       |

|     |      | 11.4.13   | Secondary Bus Number Register—Offset 0x18  |       |

|     |      |           |                                            |       |

|      | 11.4.14                                                                                                                                                  | Subordinate Bus Number Register—Offset 0x18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 113                                                                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|      | 11.4.15                                                                                                                                                  | Secondary Latency Timer Register—Offset 0x18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 114                                                                                                                      |

|      | 11.4.16                                                                                                                                                  | I/O Base Address Register—Offset 0x1C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 115                                                                                                                      |

|      | 11.4.17                                                                                                                                                  | I/O Limit Address Register—Offset 0x1C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 115                                                                                                                      |

|      | 11.4.18                                                                                                                                                  | Secondary Status Register—Offset 0x1C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 116                                                                                                                      |

|      | 11.4.19                                                                                                                                                  | Memory Base Address Register—Offset 0x20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 117                                                                                                                      |

|      | 11.4.20                                                                                                                                                  | Memory Limit Address Register—Offset 0x20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 117                                                                                                                      |

|      | 11.4.21                                                                                                                                                  | Prefetchable Memory Base Address Register—Offset 0x24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 118                                                                                                                      |

|      | 11.4.22                                                                                                                                                  | Prefetchable Memory Limit Address Register—Offset 0x24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 118                                                                                                                      |

|      | 11.4.23                                                                                                                                                  | Prefetchable Memory Base Address Upper 32 Bits Register—Offset 0x28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 119                                                                                                                      |

|      | 11.4.24                                                                                                                                                  | Prefetchable Memory Limit Address Upper 32 Bits Register—Offset 0x2C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 119                                                                                                                      |

|      | 11.4.25                                                                                                                                                  | I/O Base Address Upper 16 Bits Register—Offset 0x30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 120                                                                                                                      |

|      | 11.4.26                                                                                                                                                  | I/O Limit Address Upper 16 Bits Register—Offset 0x30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 120                                                                                                                      |

|      | 11.4.27                                                                                                                                                  | ECP Pointer Register—Offset 0x34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 121                                                                                                                      |

|      | 11.4.28                                                                                                                                                  | Interrupt Line Register – Offset 0x3C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 121                                                                                                                      |

|      | 11.4.29                                                                                                                                                  | Interrupt Pin Register—Offset 0x3C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 121                                                                                                                      |

|      | 11.4.30                                                                                                                                                  | Bridge Control Register—Offset 0x3C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 122                                                                                                                      |

| 11.5 | Device S                                                                                                                                                 | Specific Register Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 125                                                                                                                      |

|      | 11.5.1                                                                                                                                                   | Subsystem Vendor ID Register — Offset 0x40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 125                                                                                                                      |

|      | 11.5.2                                                                                                                                                   | Subsystem ID Register — Offset 0x40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 125                                                                                                                      |

|      | 11.5.3                                                                                                                                                   | Chip Control Register/Diagnostic Control — Offset 0x44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 126                                                                                                                      |

|      | 11.5.4                                                                                                                                                   | Arbiter Control Register—Offset 0x44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 127                                                                                                                      |

|      | 11.5.5                                                                                                                                                   | Memory Read Control Register — Offset 0x48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 128                                                                                                                      |

|      | 11.5.6                                                                                                                                                   | Secondary Bus Arbiter Preemption Control Register — Offset 0x4C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 129                                                                                                                      |

|      | 11.5.7                                                                                                                                                   | P_SERR_b Event Disable Register—Offset 0x64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 130                                                                                                                      |

|      |                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

|      | 11.5.8                                                                                                                                                   | Secondary Clock Control Register—Offset 0x68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 131                                                                                                                      |

|      | 11.5.8<br>11.5.9                                                                                                                                         | Secondary Clock Control Register—Offset 0x68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

|      |                                                                                                                                                          | P_SERR_b Status Register — Offset 0x68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 132                                                                                                                      |

|      | 11.5.9                                                                                                                                                   | P_SERR_b Status Register — Offset 0x68.  CLKRUN Register — Offset 0x6C.  Port Option Register — Offset 0x74.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul><li>. 132</li><li>. 133</li><li>. 134</li></ul>                                                                        |

|      | 11.5.9<br>11.5.10                                                                                                                                        | P_SERR_b Status Register — Offset 0x68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul><li>. 132</li><li>. 133</li><li>. 134</li></ul>                                                                        |

|      | 11.5.9<br>11.5.10<br>11.5.11                                                                                                                             | P_SERR_b Status Register — Offset 0x68.  CLKRUN Register — Offset 0x6C.  Port Option Register — Offset 0x74.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul><li>. 132</li><li>. 133</li><li>. 134</li><li>. 135</li></ul>                                                          |

|      | 11.5.9<br>11.5.10<br>11.5.11<br>11.5.12                                                                                                                  | P_SERR_b Status Register — Offset 0x68  CLKRUN Register — Offset 0x6C  Port Option Register — Offset 0x74  Capability ID Register—Offset 0x80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul><li>. 132</li><li>. 133</li><li>. 134</li><li>. 135</li><li>. 136</li></ul>                                            |

|      | 11.5.9<br>11.5.10<br>11.5.11<br>11.5.12<br>11.5.13<br>11.5.14                                                                                            | P_SERR_b Status Register — Offset 0x68  CLKRUN Register — Offset 0x6C  Port Option Register — Offset 0x74  Capability ID Register—Offset 0x80  Next Item Pointer Register—Offset 0x80                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <ul><li>. 132</li><li>. 133</li><li>. 134</li><li>. 135</li><li>. 136</li><li>. 136</li></ul>                              |

|      | 11.5.9<br>11.5.10<br>11.5.11<br>11.5.12<br>11.5.13<br>11.5.14                                                                                            | P_SERR_b Status Register — Offset 0x68  CLKRUN Register — Offset 0x6C  Port Option Register — Offset 0x74  Capability ID Register—Offset 0x80  Next Item Pointer Register—Offset 0x80  Power Management Capabilities Register—Offset 0x80  Power Management Data Register—Offset 0x84  PMCSR_BSE Register — Offset 0x84                                                                                                                                                                                                                                                                                                                | <ul><li>. 132</li><li>. 133</li><li>. 134</li><li>. 135</li><li>. 136</li><li>. 136</li><li>. 137</li><li>. 138</li></ul>  |

|      | 11.5.9<br>11.5.10<br>11.5.11<br>11.5.12<br>11.5.13<br>11.5.14<br>11.5.15                                                                                 | P_SERR_b Status Register — Offset 0x68  CLKRUN Register — Offset 0x6C  Port Option Register — Offset 0x74  Capability ID Register—Offset 0x80  Next Item Pointer Register—Offset 0x80  Power Management Capabilities Register—Offset 0x80  Power Management Data Register—Offset 0x84  PMCSR_BSE Register — Offset 0x84  HS Capability ID Register — Offset 0x90                                                                                                                                                                                                                                                                       | <ul><li>. 132</li><li>. 133</li><li>. 134</li><li>. 135</li><li>. 136</li><li>. 137</li><li>. 138</li></ul>                |

|      | 11.5.9<br>11.5.10<br>11.5.11<br>11.5.12<br>11.5.13<br>11.5.14<br>11.5.15<br>11.5.16                                                                      | P_SERR_b Status Register — Offset 0x68  CLKRUN Register — Offset 0x6C  Port Option Register — Offset 0x74  Capability ID Register—Offset 0x80  Next Item Pointer Register—Offset 0x80  Power Management Capabilities Register—Offset 0x80  Power Management Data Register—Offset 0x84  PMCSR_BSE Register — Offset 0x84                                                                                                                                                                                                                                                                                                                | <ul><li>. 132</li><li>. 133</li><li>. 134</li><li>. 135</li><li>. 136</li><li>. 137</li><li>. 138</li></ul>                |

|      | 11.5.9<br>11.5.10<br>11.5.11<br>11.5.12<br>11.5.13<br>11.5.14<br>11.5.15<br>11.5.16<br>11.5.17                                                           | P_SERR_b Status Register — Offset 0x68  CLKRUN Register — Offset 0x6C  Port Option Register — Offset 0x74  Capability ID Register—Offset 0x80  Next Item Pointer Register—Offset 0x80  Power Management Capabilities Register—Offset 0x80  Power Management Data Register—Offset 0x84  PMCSR_BSE Register — Offset 0x84  HS Capability ID Register — Offset 0x90                                                                                                                                                                                                                                                                       | . 132<br>. 133<br>. 134<br>. 135<br>. 136<br>. 137<br>. 138<br>. 138                                                       |

|      | 11.5.9<br>11.5.10<br>11.5.11<br>11.5.12<br>11.5.13<br>11.5.14<br>11.5.15<br>11.5.16<br>11.5.17                                                           | P_SERR_b Status Register — Offset 0x68  CLKRUN Register — Offset 0x6C  Port Option Register — Offset 0x74  Capability ID Register—Offset 0x80  Next Item Pointer Register—Offset 0x80  Power Management Capabilities Register—Offset 0x80  Power Management Data Register—Offset 0x84  PMCSR_BSE Register — Offset 0x84  HS Capability ID Register — Offset 0x90  HS Next Item Pointer Register — Offset 0x90                                                                                                                                                                                                                          | . 132<br>. 133<br>. 134<br>. 135<br>. 136<br>. 137<br>. 138<br>. 138<br>. 138                                              |

| Paci | 11.5.9<br>11.5.10<br>11.5.11<br>11.5.12<br>11.5.13<br>11.5.14<br>11.5.15<br>11.5.16<br>11.5.17<br>11.5.18<br>11.5.19<br>11.5.20                          | P_SERR_b Status Register — Offset 0x68  CLKRUN Register — Offset 0x6C  Port Option Register — Offset 0x74  Capability ID Register—Offset 0x80  Next Item Pointer Register—Offset 0x80  Power Management Capabilities Register—Offset 0x80  Power Management Data Register—Offset 0x84  PMCSR_BSE Register — Offset 0x84  HS Capability ID Register — Offset 0x90  HS Next Item Pointer Register — Offset 0x90  HS Control Status Register — Offset 0x90  Miscellaneous Control Register — Offset 0xC0                                                                                                                                  | . 132<br>. 133<br>. 134<br>. 135<br>. 136<br>. 137<br>. 138<br>. 138<br>. 138                                              |

|      | 11.5.9<br>11.5.10<br>11.5.11<br>11.5.12<br>11.5.13<br>11.5.14<br>11.5.15<br>11.5.16<br>11.5.17<br>11.5.18<br>11.5.19<br>11.5.20<br><b>kaging</b>         | P_SERR_b Status Register — Offset 0x68  CLKRUN Register — Offset 0x6C  Port Option Register — Offset 0x74  Capability ID Register—Offset 0x80  Next Item Pointer Register—Offset 0x80  Power Management Capabilities Register—Offset 0x80  Power Management Data Register—Offset 0x84  PMCSR_BSE Register — Offset 0x84  HS Capability ID Register — Offset 0x90  HS Next Item Pointer Register — Offset 0x90  HS Control Status Register — Offset 0x90  Miscellaneous Control Register — Offset 0xC0                                                                                                                                  | . 132<br>. 133<br>. 134<br>. 135<br>. 136<br>. 137<br>. 138<br>. 138<br>. 138<br>. 140                                     |

| 12.1 | 11.5.9 11.5.10 11.5.11 11.5.12 11.5.13 11.5.14 11.5.15 11.5.16 11.5.17 11.5.18 11.5.19 11.5.20  kaging Mechani                                           | P_SERR_b Status Register — Offset 0x68  CLKRUN Register — Offset 0x6C  Port Option Register — Offset 0x74  Capability ID Register—Offset 0x80  Next Item Pointer Register—Offset 0x80  Power Management Capabilities Register—Offset 0x80  Power Management Data Register—Offset 0x84  PMCSR_BSE Register — Offset 0x84  HS Capability ID Register — Offset 0x90  HS Next Item Pointer Register — Offset 0x90  HS Control Status Register — Offset 0x90  Miscellaneous Control Register — Offset 0xC0                                                                                                                                  | . 132<br>. 133<br>. 134<br>. 135<br>. 136<br>. 137<br>. 138<br>. 138<br>. 138<br>. 140                                     |

|      | 11.5.9<br>11.5.10<br>11.5.11<br>11.5.12<br>11.5.13<br>11.5.14<br>11.5.15<br>11.5.16<br>11.5.17<br>11.5.18<br>11.5.19<br>11.5.20<br><b>kaging</b> Mechani | P_SERR_b Status Register — Offset 0x68.  CLKRUN Register — Offset 0x6C.  Port Option Register — Offset 0x74.  Capability ID Register—Offset 0x80  Next Item Pointer Register—Offset 0x80.  Power Management Capabilities Register—Offset 0x80  Power Management Data Register—Offset 0x84  PMCSR_BSE Register — Offset 0x84  HS Capability ID Register — Offset 0x90  HS Next Item Pointer Register — Offset 0x90  HS Control Status Register — Offset 0x90.  Miscellaneous Control Register — Offset 0xC0.                                                                                                                            | . 132<br>. 133<br>. 134<br>. 135<br>. 136<br>. 137<br>. 138<br>. 138<br>. 138<br>. 140<br>. 141<br>. 141                   |

| 12.1 | 11.5.9 11.5.10 11.5.11 11.5.12 11.5.13 11.5.14 11.5.15 11.5.16 11.5.17 11.5.18 11.5.19 11.5.20  kaging  Mechani Thermal 12.2.1                           | P_SERR_b Status Register — Offset 0x68.  CLKRUN Register — Offset 0x6C.  Port Option Register — Offset 0x74.  Capability ID Register—Offset 0x80  Next Item Pointer Register—Offset 0x80.  Power Management Capabilities Register—Offset 0x80  Power Management Data Register—Offset 0x84.  PMCSR_BSE Register — Offset 0x84  HS Capability ID Register — Offset 0x90.  HS Next Item Pointer Register — Offset 0x90.  HS Control Status Register — Offset 0x90.  Miscellaneous Control Register — Offset 0xC0.                                                                                                                         | . 132<br>. 133<br>. 134<br>. 135<br>. 136<br>. 137<br>. 138<br>. 138<br>. 138<br>. 140<br>. 141<br>. 144                   |

| 12.1 | 11.5.9 11.5.10 11.5.11 11.5.12 11.5.13 11.5.14 11.5.15 11.5.16 11.5.17 11.5.18 11.5.19 11.5.20  kaging  Mechani Thermal 12.2.1 12.2.2                    | P_SERR_b Status Register — Offset 0x68.  CLKRUN Register — Offset 0x6C.  Port Option Register — Offset 0x74.  Capability ID Register—Offset 0x80.  Next Item Pointer Register—Offset 0x80.  Power Management Capabilities Register—Offset 0x80.  Power Management Data Register—Offset 0x84.  PMCSR_BSE Register — Offset 0x84.  HS Capability ID Register — Offset 0x90.  HS Next Item Pointer Register — Offset 0x90.  HS Control Status Register — Offset 0x90.  Miscellaneous Control Register — Offset 0xC0.  Ical Diagram  Characteristics  Junction-to-Ambient Thermal Characteristics (Theta ja)  System-level Characteristics | . 132<br>. 133<br>. 134<br>. 135<br>. 136<br>. 137<br>. 138<br>. 138<br>. 138<br>. 140<br>. 141<br>. 144<br>. 144          |

| 12.1 | 11.5.9 11.5.10 11.5.11 11.5.12 11.5.13 11.5.14 11.5.15 11.5.16 11.5.17 11.5.18 11.5.19 11.5.20  kaging  Mechani Thermal 12.2.1 12.2.2 0.0.1              | P_SERR_b Status Register — Offset 0x68.  CLKRUN Register — Offset 0x6C.  Port Option Register — Offset 0x74.  Capability ID Register—Offset 0x80  Next Item Pointer Register—Offset 0x80.  Power Management Capabilities Register—Offset 0x80  Power Management Data Register—Offset 0x84.  PMCSR_BSE Register — Offset 0x84  HS Capability ID Register — Offset 0x90.  HS Next Item Pointer Register — Offset 0x90.  HS Control Status Register — Offset 0x90.  Miscellaneous Control Register — Offset 0xC0.                                                                                                                         | . 132<br>. 133<br>. 134<br>. 135<br>. 136<br>. 137<br>. 138<br>. 138<br>. 140<br>. 141<br>. 144<br>. 144<br>. 145<br>. 145 |

**12.**

| 13. | Ordering Information |                            |     |  |

|-----|----------------------|----------------------------|-----|--|

|     | 13.1                 | Part Numbers               | 147 |  |

|     | 13.2                 | Part Numbering Information | 147 |  |

# **Figures**

| Figure 1:  | Tsi340 Block Diagram                            | 16  |

|------------|-------------------------------------------------|-----|

| Figure 2:  | Application Diagram - Digital Video Recorder    | 17  |

| Figure 3:  | Memory Read Flow                                | 20  |

| Figure 4:  | Memory Write Flow                               | 22  |

| Figure 5:  | Type 0 Configuration Transaction Address Format | 33  |

| Figure 6:  | Type 1 Configuration Transaction Address Format | 33  |

| Figure 7:  | Input Timing Measurement Waveforms              | 98  |

| Figure 8:  | Output Timing Measurement Waveforms             | 99  |

| Figure 9:  | AC Test Load for All Signals Except PCI         | 99  |

| Figure 10: | PCI TOV (max) Rising Edge AC Test Load          | 99  |

| Figure 11: | PCI TOV (max) Falling Edge AC Test Load         | 100 |

| Figure 12: | PCI TOV (min) AC Test Load                      | 100 |

| Figure 13: | Tsi340 PQFP Package - Top View                  | 142 |

| Figure 14: | Tsi340 PQFP Package - Side View                 | 143 |

| Figure 15: | Tsi340 PQFP Package - Side View                 | 143 |

| Figure 16: | Tsi340 POEP Package - Side View                 | 143 |

10 Figures

# **Tables**

| Table 1:  | Type of Transactions                                |

|-----------|-----------------------------------------------------|

| Table 2:  | Posted Write Address Boundaries                     |

| Table 3:  | Read Behavior         29                            |

| Table 4:  | Prefetch Address Boundaries                         |

| Table 5:  | Device Number to IDSEL S_AD Mapping                 |

| Table 6:  | Tsi340 Response to Delayed Write Target Termination |

| Table 7:  | Tsi340 Response to Posted Write Target Termination  |

| Table 8:  | Tsi340 Response to Delayed Read Target Termination  |

| Table 9:  | Summary of Transaction Ordering                     |

| Table 10: | Power Management Transitions                        |

| Table 11: | Signal Types                                        |

| Table 12: | Primary PCI Interface Signals                       |

| Table 13: | Secondary PCI Interface Signals                     |

| Table 14: | Clocks and Resets                                   |

| Table 15: | Miscellaneous Signals                               |

| Table 16: | 128 PQFP Pinlist                                    |

| Table 17: | Absolute Maximum Ratings93                          |

| Table 18: | Absolute Maximum Ratings - ESD                      |

| Table 19: | Recommended Operating Conditions                    |

| Table 20: | Supply Current Characteristics at 3.6V              |

| Table 21: | DC Operating Characteristics                        |

| Table 22: | AC Specifications for PCI Interface                 |

| Table 23: | PCI Clock (PCI_CLK) Specification                   |

| Table 24: | Register Map                                        |

| Table 25: | PQFP Symbol Values                                  |

| Table 26: | Thermal Characteristics of the Tsi340               |

| Table 27: | Simulated Junction to Ambient Characteristics       |

| Table 28: | Part Numbers                                        |

12 Tables

# **About this Document**

This section discusses the following topics:

- "Scope" on page 13

- "Document Conventions" on page 13

- "Revision History" on page 14

# Scope

The *Tsi340 PCI-to-PCI Bridge User Manual* discusses the features, capabilities, and configuration requirements for the *Tsi340*. It is intended for hardware and software engineers who are designing system interconnect applications with the device.

# **Document Conventions**

This document uses the following conventions.

## **Non-differential Signal Notation**

Non-differential signals are either active-low or active-high. An active-low signal has an active state of logic 0 (or the lower voltage level), and is denoted by a lowercase "\_b". An active-high signal has an active state of logic 1 (or the higher voltage level), and is not denoted by a special character. The following table illustrates the non-differential signal naming convention.

| State       | Single-line signal | Multi-line signal |  |

|-------------|--------------------|-------------------|--|

| Active low  | NAME_b             | NAME_b[3]         |  |

| Active high | NAME               | NAME[3]           |  |

# **Object Size Notation**

- A *byte* is an 8-bit object.

- A word is a 16-bit object.

- A doubleword (Dword) is a 32-bit object.

#### **Numeric Notation**

• Hexadecimal numbers are denoted by the prefix 0x (for example, 0x04).

- Binary numbers are denoted by the prefix *0b* (for example, 0b010).

- Registers that have multiple iterations are denoted by {x..y} in their names; where x is first register and address, and y is the last register and address. For example, REG{0..1} indicates there are two versions of the register at different addresses: REG0 and REG1.

#### **Symbols**

This symbol indicates a basic design concept or information considered helpful.

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or damage to the device.

#### **Document Status Information**

- Advance Contains information that is subject to change, and is available once prototypes are released to customers.

- Preliminary Contains information about a product that is near production-ready, and is revised as required.

- Formal Contains information about a final, customer-ready product, and is available once the product is released to production.

# **Revision History**

#### 80E3000 MA001 05, Formal, September 2009

This version of the document was rebranded as IDT. It does not contain any technical changes.

## 80E3000 MA001 02, Advance, October 2006

This version includes numerous minor changes.

#### 80E3000\_MA001\_01, Draft, July 2006

This is the first version of the *Tsi384 User Manual*.

# 1. Functional Overview

This chapter discusses the following topics about the Tsi340:

- "Overview" on page 15

- "Features" on page 17

- "Functional Overview" on page 18

- "Data Flow" on page 20

# 1.1 Overview

The IDT Tsi340 is a PCI-to-PCI bridge that is fully compliant with the *PCI Local Bus Specification*, *Revision 2.3*.

The Tsi340 has two identical PCI interfaces that support PCI transactions for each bus. The interfaces can act as either a bus master or a bus slave, depending on the type of transaction.

The Tsi340 enables two PCI buses to operate concurrently. This means that a master and a target on the same PCI bus can communicate while the other PCI bus is busy. This traffic isolation can increase system performance in applications such as multimedia.

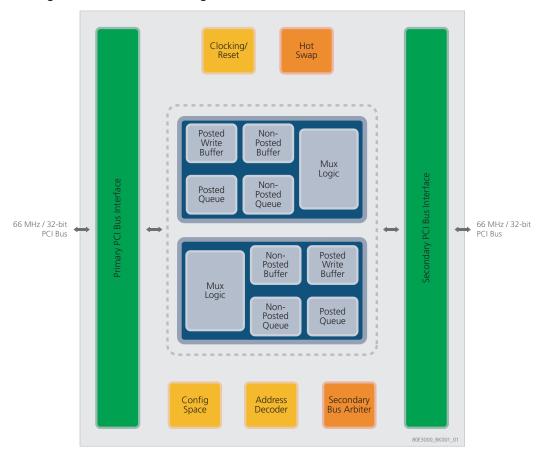

The block diagram for Tsi340 is shown Figure 1 on page 16.

16 1. Functional Overview

Figure 1: Tsi340 Block Diagram

#### **Typical Applications**

The Tsi340 is suited to applications that need to bridge from PCI to other downstream PCI devices. Its flexibility, and small footprint, make it ideal for a wide range of applications, including:

- Video capture cards

- Digital video recorders

- Industrial PC (IPC) backplanes

- Multi-function printers

- Storage host bus adapters (HBAs)

- Network interface cards (NICs)

- Firewall and security gateways

- Printers, graphics and imaging systems

1. Functional Overview 17

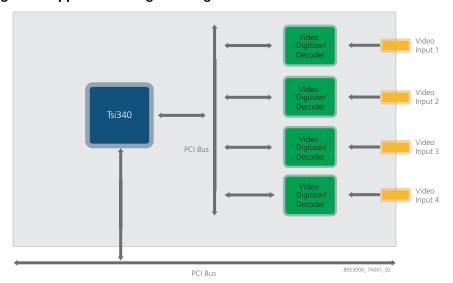

Option card designers can use the Tsi340 to implement multiple-device PCI option cards. The *PCI Local Bus Specification* loading rules limit PCI option cards to a single connection per PCI signal in the option card connector. Without a PCI-to-PCI bridge, PCI loading rules limit option cards to one device. The Tsi340 overcomes this restriction by providing an independent PCI bus that can support up to four devices.

The application diagram below shows how the Tsi340 enables the design of a multi-component option card and expands the PCI architecture.

Figure 2: Application Diagram - Digital Video Recorder

# 1.2 Features

The following section describe the features of Tsi340:

- Industry-standard PCI-to-PCI bridge

- 66 MHz, 32-bit operation on the primary and secondary interfaces

- Up to four PCI bus masters supported on the secondary interface

- Concurrent operation of primary and secondary interfaces

- Compliant with the following specifications:

- PCI-to-PCI Bridge Architecture Specification (Revision 1.1)

- PCI Local Bus Specification (Revision 2.3)

- PCI bus Power Management Interface Specification (Revision 1.1)

- Advanced Configuration Power Interface (ACPI)

- Posted write buffers in both directions

- 1-KB transaction buffer (total)

18 1. Functional Overview

- Enhanced address decoding

- Compatible with existing PCI bridging devices from PLX and Pericom

- Physical

- 128-pin PQFP

- RoHS compliant

- 3.3 V I/O, 5 V tolerant

- Compliance

- PCI-to-PCI Bridge Architecture Specification (Revision 1.1)

- PCI Local Bus Specification (Revision 2.3)

- PCI bus Power Management Interface Specification (Revision 1.1)

- Advanced Configuration Power Interface (ACPI)

- PICMG CompactPCI Hot-Swap Specification (Revision 2.0)

# 1.3 Functional Overview

Tsi340 has two PCI interfaces: a primary interface and a secondary interface. Each interface controls the PCI protocol for its respective bus. These interfaces transfer data/control information to and from the Buffer Logic Unit (BLU). The BLU consists of a posted write buffer, posted write queue, non-posted buffer, and non-posted queue.

#### 1.3.1 Posted Write Buffer

The Tsi340 handles the conventional PCI transactions of Memory Write, and Memory Write and Invalidate as posted transactions.

The posted write buffer is used for temporary storage of data flowing from the primary interface to the secondary interface and from the secondary interface to the primary interface. Each posted buffer has a capacity of 256 bytes. The amount of space assigned to each transaction is dynamic. A single transaction can use sizes ranging from one memory location (4 bytes) to 64-memory location (64 bytes).

When the Tsi340 determines that a memory write transaction must be forwarded across the bridge, it first checks for empty space in the posted write buffer. If space is available, the posted write buffer accepts data until the buffer is full or the transaction is terminated. If there is no space in the posted write buffer, the transaction is terminated with retry.

#### 1.3.2 Posted Write Queue

The posted write queue is used to store the control information related to the transaction flowing from the primary interface to secondary interface or from the secondary interface to the primary interface. Each posted write queue has a four entry FIFO, which provides four active posted write transactions in each direction. Data related to each entry is stored in the posted write buffer.

1. Functional Overview 19

The posted write queue accepts an entry from an external master as long as at least one entry is free and at least one Dword of space is available in the posted write buffer.

#### 1.3.3 Non-Posted Buffer

The non-posted buffer is used for storing the data related to delayed transactions. The following list of transactions use the non-posted buffer:

- Memory Read

- Memory Read Line

- Memory Read Multiple

- I/O Read

- I/O Write

- Type-1 Configuration Read

- Type-1 Configuration Write

All the non-posted transactions are processed through the non-posted queues and non-posted buffers. Each non-posted buffer has a storage capacity of up to 256 bytes for storing data related to delayed transactions.

#### 1.3.4 Non-Posted Queue

The non-posted queue is used to store the control information related to the all non-posted transactions. Each non-posted queue has a four entry FIFO, which provides four active non-posted transactions in each direction. Data related to each entry is stored in the non-posted buffer.

The non-posted queue accepts an entry from an external master if at least one entry is available. If all four entries are full the Tsi340 retries the external master until an entry becomes available.

## 1.3.5 Configuration Space

Tsi340 is a PCI-to-PCI bridge, and complies with the *PCI to PCI Bridge Architecture Specification*, *Revision 1.1*. The Tsi340's configuration space can only be accessed from the primary interface. The Tsi340 uses additional device specific configuration registers to support optional, device specific features.

Refer to "Configuration Transactions" on page 33 for more information.

## 1.3.6 Address Decoding Logic

The Tsi340 is a transparent bridge. In transparent mode, the I/O, Memory, pre-fetchable memory base and limit, and optional base address registers 0 and 1 define address ranges residing on the secondary bus. All other addresses are assumed to reside on the primary bus. Inverse address decoding determines when to forward the transaction up-stream.

Refer to "Address Decoding" on page 45 for more information.

20 1. Functional Overview

#### 1.3.7 Secondary Bus Arbiter

The Tsi340 has an internal secondary bus arbiter. It provides bus arbitration for up to four additional masters. Each external master is assigned to either high or low priority, or may be masked off.

The internal arbiter provides a two level arbitration scheme in which arbitration is divided into the following two groups: a high priority group and low priority group. Each master can be assigned to either high priority group or low priority group through the configuration register.

Refer to "PCI Bus Arbitration" on page 59 for more information.

## 1.3.8 Hot Swap Interface

Tsi340 is designed with an interface for Hot Swap support. This allows the user to insert or extract the bridge card without powering down the system. During insertion and extraction process, the bridge indicates to system software about the Hot Swap event by driving HS\_ENUM\_b. It also provides a visual indication through the HS\_LED\_OUT signal.

## 1.4 Data Flow

The following sections describe the data flow through the Tsi340 device.

## 1.4.1 Memory Read Transactions

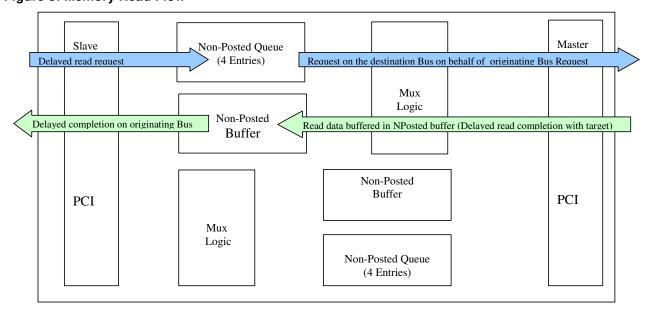

The conventional PCI memory read, memory read line, and memory read multiple commands are used to transfer memory read data. Tsi340 completes all memory read transactions as delayed transactions. Figure 3 shows the Tsi340 memory read flow.

Figure 3: Memory Read Flow

1. Functional Overview 21

The following steps detail the memory read flow through the Tsi340:

- The read request from the initiator is posted/entered into the Non-Posted Queue,

- The transaction is terminated by signaling target retry to the initiator

- When the target retry is received, the initiator is required to continue to repeat the same read transaction until at least one data transfer is completed or until a master/target abort is received

- The Tsi340 then arbitrates for the destination bus and initiates a read transaction using the exact read address and read command

- If Tsi340 receives retry on the target bus, it continues to repeat the read transaction until at least one data transfer is completed, or until an error condition is encountered.

When a memory read transaction targets non-prefetchable address space the Tsi340 will pre-fetch a single DWORD of data when the memory read command is used. For all other read transactions the Tsi340 will pre-fetch data according to the pre-fetch algorithm, see "Read Transactions" on page 29.

• When the transaction is completed on the target bus, the Tsi340 transfers the data to the initiator when the initiator repeats the transaction

#### 1.4.2 Posted Write Transaction Flow

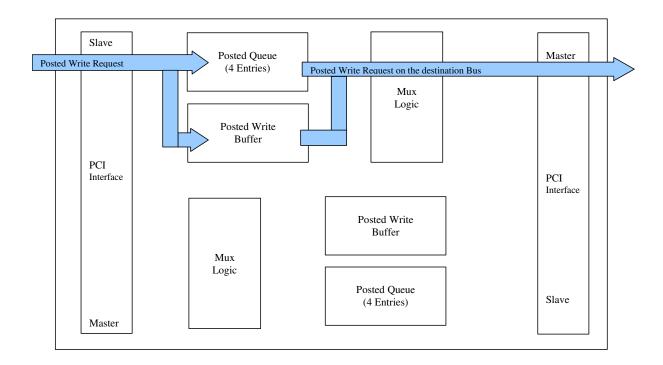

The conventional PCI memory write and memory write and invalidate are posted transactions. Unlike non-posted transactions these transactions are first completed on the originating bus and then completed on the destination bus. Figure 4 shows the Tsi340 posted write flow.

22 1. Functional Overview

**Figure 4: Memory Write Flow**

The following steps detail the posted write flow through the Tsi340:

- When Tsi340 determines that a memory write transaction is to be forwarded across the bridge, it first checks for empty space in the posted write buffer

- If space is available, Tsi340 accepts data until the buffer is full or the transaction is terminated.

- If there is no space in the posted write buffer, the transaction is terminated with retry.

- After buffering data into the posted buffer the Tsi340 arbitrates for the destination bus and writes the data to the destination.

# 2. PCI Interface

This chapter discusses the following topics about the Tsi340:

- "Overview" on page 23

- "Transaction Types" on page 23

- "Configuration Transactions" on page 33

- "Transaction Termination" on page 38

- "CompactPCI Hot-swap Support" on page 44

## 2.1 Overview

Tsi340 has two PCI interfaces: a primary interface and a secondary interface. Each interface controls the PCI protocol for its respective bus. These interfaces transfer data/control information to and from the Buffer Logic Unit (BLU). The BLU consists of a posted write buffer, posted write queue, non-posted buffer, and non-posted queue.

The following sections describe the how the Tsi340 handles PCI transactions, transaction forwarding across Tsi340, and transaction termination.

# 2.2 Transaction Types

This section provides a summary of PCI transactions performed by Tsi340. Table 1 lists the command code and name of each PCI transaction. The Master and Target columns indicate Tsi340 support for each transaction when Tsi340 initiates transactions as a master, on the primary bus and on the secondary bus, and when Tsi340 responds to transactions as a target, on the primary bus and on the secondary bus.

**Table 1: Type of Transactions**

|                            | Initiates a | s a Master | Responds as a Target |           |

|----------------------------|-------------|------------|----------------------|-----------|

| Type of Transaction        | Primary     | Secondary  | Primary              | Secondary |

| 0000-Interrupt Acknowledge | No          | No         | No                   | No        |

| 0001-Special Cycle         | Yes         | Yes        | No                   | No        |

| 0010-I/O Read              | Yes         | Yes        | Yes                  | Yes       |

| 0011-I/O Write             | Yes         | Yes        | Yes                  | Yes       |

| 0100-Reserved              | No          | No         | No                   | No        |

24 2. PCI Interface

**Table 1: Type of Transactions**

|                                  | Initiates a | s a Master | Responds as a Target |           |

|----------------------------------|-------------|------------|----------------------|-----------|

| Type of Transaction              | Primary     | Secondary  | Primary              | Secondary |

| 0101-Reserved                    | No          | No         | No                   | No        |

| 0110-Memory Read                 | Yes         | Yes        | Yes                  | Yes       |

| 0111-Memory Write                | Yes         | Yes        | Yes                  | Yes       |

| 1000-Reserved                    | No          | No         | No                   | No        |

| 1001-Reserved                    | No          | No         | No                   | No        |