# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# IDT<sub>®</sub> Tsi577 Serial RapidIO Switch

# **Hardware Manual**

May 18, 2012

#### GENERAL DISCLAIMER

Integrated Device Technology, Inc. ("IDT") reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance. IDT does not assume responsibility for use of any circuitry described herein other than the circuitry embodied in an IDT product. Disclosure of the information herein does not convey a license or any other right, by implication or otherwise, in any patent, trademark, or other intellectual property right of IDT. IDT products may contain errata which can affect product performance to a minor or immaterial degree. Current characterized errata will be made available upon request. Items identified herein as "reserved" or "undefined" are reserved for future definition. IDT does not assume responsibility for conflicts or incompatibilities arising from the future definition of such items. IDT products have not been designed, tested, or manufactured for use in, and thus are not warranted for, applications where the failure, malfunction, or any inaccuracy in the application carries a risk of death, serious bodily injury, or damage to tangible property. Code examples provided herein by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of such code examples shall be at the user's sole risk.

Copyright © 2012 Integrated Device Technology, Inc. All Rights Reserved.

The IDT logo is registered to Integrated Device Technology, Inc. IDT and CPS are trademarks of Integrated Device Technology, Inc.

# Contents

| 1. | Sigr              | nals and Package                     |  |  |  |  |

|----|-------------------|--------------------------------------|--|--|--|--|

|    | 1.1               | Signals 11                           |  |  |  |  |

|    | 1.2               | Pinlist and Ballmap                  |  |  |  |  |

|    | 1.3               | Package Characteristics              |  |  |  |  |

|    | 1.4               | Thermal Characteristics              |  |  |  |  |

| 2. | Elec              | Electrical Characteristics           |  |  |  |  |

|    | 2.1               | Absolute Maximum Ratings             |  |  |  |  |

|    | 2.2               | Recommended Operating Conditions     |  |  |  |  |

|    | 2.3               | Power                                |  |  |  |  |

|    | 2.4               | Electrical Characteristics           |  |  |  |  |

| 3. | Layout Guidelines |                                      |  |  |  |  |

|    | 3.1               | Overview                             |  |  |  |  |

|    | 3.2               | Impedance Requirements               |  |  |  |  |

|    | 3.3               | Tracking Topologies                  |  |  |  |  |

|    | 3.4               | Power Distribution                   |  |  |  |  |

|    | 3.5               | Decoupling Requirements 59           |  |  |  |  |

|    | 3.6               | Clocking and Reset                   |  |  |  |  |

|    | 3.7               | Modeling and Simulation              |  |  |  |  |

|    | 3.8               | Testing and Debugging Considerations |  |  |  |  |

|    | 3.9               | Reflow Profile.   69                 |  |  |  |  |

| Α. | Ord               | ering Information                    |  |  |  |  |

|    | A.1               | Ordering Information                 |  |  |  |  |

|    | A.2               | Part Numbering Information           |  |  |  |  |

# **About this Document**

This section discusses general document information about the *Serial RapidIO Switch*. The following topics are described:

- "Scope" on page 5

- "Document Conventions" on page 5

- "Revision History" on page 7

### Scope

The *Tsi577 Hardware Manual* discusses electrical, physical, and board layout information for the Tsi577. It is intended for hardware engineers who are designing system interconnect applications with these devices.

### **Document Conventions**

This document uses a variety of conventions to establish consistency and to help you quickly locate information of interest. These conventions are briefly discussed in the following sections.

#### **Non-differential Signal Notation**

Non-differential signals are either active-low or active-high. An active-low signal has an active state of logic 0 (or the lower voltage level), and is denoted by a lowercase "b". An active-high signal has an active state of logic 1 (or the higher voltage level), and is not denoted by a special character. The following table illustrates the non-differential signal naming convention.

| State       | Single-line signal | Multi-line signal |

|-------------|--------------------|-------------------|

| Active low  | NAME_b             | NAMEn[3]          |

| Active high | NAME               | NAME[3]           |

### **Differential Signal Notation**

Differential signals consist of pairs of complement positive and negative signals that are measured at the same time to determine a signal's active or inactive state (they are denoted by "\_p" and "\_n", respectively). The following table illustrates the differential signal naming convention.

| State    | Single-line signal       | Multi-line signal                |

|----------|--------------------------|----------------------------------|

| Inactive | NAME_p = 0<br>NAME_n = 1 | NAME_p[3] = 0<br>NAME_n[3] =1    |

| Active   | NAME_p = 1<br>NAME_n = 0 | NAME_p[3] is 1<br>NAME_n[3] is 0 |

#### **Symbols**

This symbol indicates a basic design concept or information considered helpful.

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or damage to the device.

## **Revision History**

#### May 18, 2012, Formal

- Updated the first paragraph in "Power Sequencing" on page 35

- Added Figure 38 (Analyzer Probe Footprint)

#### November 18, 2010, Formal

Added a note to Table 13

#### August 2009, Formal

There have been no technical changes to this document. The formatting has been updated to reflect IDT.

#### June 2009, Formal

There have been changes throughout the document.

#### September 2008, Advance

• Updated Table 8 on page 32 with new Tsi577 operating conditions

#### August 2008, Advance

- Updated Table 5 on page 29 with new Tsi577 thermal characteristics

- Updated Table 6 on page 29 with new simulated junction to ambient characteristics

#### August 2008, Advance

Although changes occurred throughout this document, the majority of changes were in "Signals and Package" on page 11.

#### June 2008, Advance

This was the first version of this document.

## **Bibliography**

1 RapidIO Interconnect Specification This specification explains RapidIO's logical layer, (Revision 1.3) common transport layer, and physical layer protocol and packet formats. It also describes overall inter-operability requirements for the RapidIO protocol. For more information, see www.rapidio.org. 2 Enhancements to the RapidIO AC This document contains the AC specifications for the RapidIO physical layer. Specification 3 ANSI/TIA/EIA-644-1995, This documents the LVDS electrical characteristics. Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits, March 1996. 4 I<sup>2</sup>C Specification This specification defines the standard I2C bus interface, including specifications for all the enhancements. For more information, see www.semiconductors.philips.com document number: 9398 393 40011 5 High-Speed Digital System Hall, Stephen H., Garret W. Hall & James A. McCall, Design ©2000 John Wiley & Sons inc. ISBN 0-471-36090-2 6 High-Speed Digital Design Johnson, Howard, Martin Graham ©1993 Prentice-Hall inc. ISBN 0-13-395724-1 7 High Performance Printed Harper, Charles A. Circuit Boards ©1999 McGraw-Hill ISBN 0-07-026713-8 8 Transmission Line Application Note 905 **RAPIDESIGNER**© ©1996 National Semiconductor Corp. Lit # 100905-002 & 633201-001 9 High Speed PCB Design Ritchey, Lee W., James C. Blankenhorn ©1993 SMT Plus Inc., and Ritch Tech 10 **Design Guidelines for Electronic** The Institute for Interconnecting and Packaging **Electronic Circuits** Packaging Utilizing High Speed Techniques ©1999 IPC Document # IPC-D-317A

| 11 | High Speed Signal Propagation                          | Johnson, Howard, Martin Graham<br>©2003 Prentice-Hall inc.<br>ISBN 0-13-084408-X |

|----|--------------------------------------------------------|----------------------------------------------------------------------------------|

| 12 | High Speed Digital Design and PCB<br>Layout            | Hanson, Robert J.<br>©AmeriCom Test & SMT Technology Inc.                        |

| 13 | 1-10 GBps Serial Interconnect<br>Requirements          | Solving High Speed Serial Design Challenges<br>©2004Xilinx                       |

| 14 | 10GBps Serial Backplanes Using<br>Virtex-II Pro X      | Solving High Speed Serial Design Challenges<br>©2004Xilinx                       |

| 15 | Designing Controlled-impedance Vias                    | Thomas Neu, EDN magazine, October 2 2003                                         |

| 16 | Computer Circuits Electrical Design,<br>First Edition, | Ron K. Poon<br>Prentice-Hall, Inc., 1995                                         |

# 1. Signals and Package

This chapter describes the packaging (mechanical) features for the Tsi577. It includes the following information:

- "Signals" on page 11

- "Pinlist and Ballmap" on page 25

- "Package Characteristics" on page 26

- "Thermal Characteristics" on page 29

## 1.1 Signals

The following conventions are used in the signal description table:

- Signals with the suffix "\_p" are the positive half of a differential pair.

- Signals with the suffix "\_n" are the negative half of a differential pair.

- Signals with the suffix "\_b" are active low.

Signals are classified according to the types defined in Table 1.

| Table | 1: | Signal | Types |

|-------|----|--------|-------|

|-------|----|--------|-------|

| Pin Type | Definition                                                                                   |  |

|----------|----------------------------------------------------------------------------------------------|--|

| I        | Input                                                                                        |  |

| 0        | Output                                                                                       |  |

| I/O      | Input/Output                                                                                 |  |

| OD       | Open Drain                                                                                   |  |

| SRIO     | Differential driver/receiver defined by RapidIO<br>Interconnect Specification (Revision 1.3) |  |

| PU       | Pulled Up internal to the Tsi577                                                             |  |

| PD       | Pulled Down internal to the Tsi577                                                           |  |

| LVTTL    | CMOS I/O with LVTTL thresholds                                                               |  |

| CML      | Current Mode Logic - Defined by RapidIO Interconnect<br>Specification (Revision 1.3)         |  |

| Pin Type    | Definition                                            |

|-------------|-------------------------------------------------------|

| Hyst        | Hysteresis                                            |

| Core Power  | Core supply                                           |

| Core Ground | Ground for core logic                                 |

| I/O Power   | I/O supply                                            |

| N/C         | No connect<br>These signals must be left unconnected. |

#### 1.1.1 Endian Ordering

This document follows the bit-numbering convention adopted by *RapidIO Interconnect Specification (Revision 1.3)*, where [0:7] is used to represent an 8 bit bus with bit 0 as the most-significant bit.

#### 1.1.2 Signal Grouping

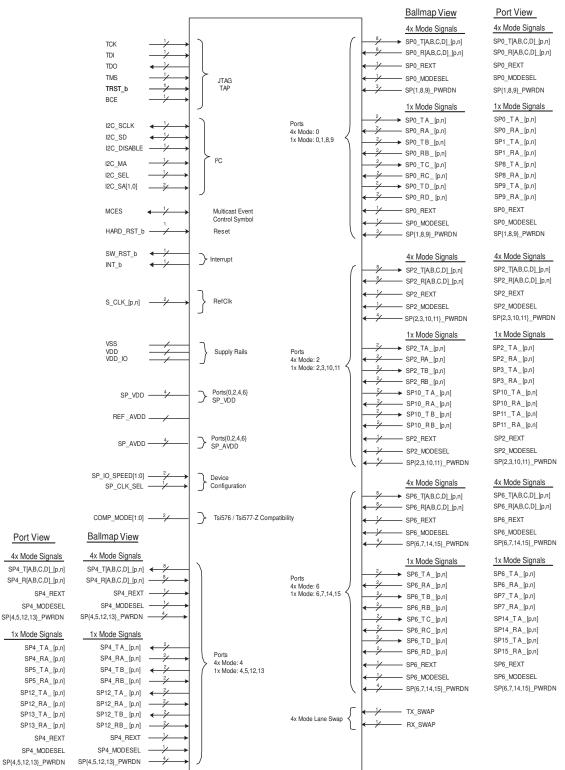

Figure 1 shows two views of the signals: the ball map view and the port view. The ball map view shows the pins as they are named in the Tsi577 ball map. The port view shows the signals on the same balls that are configuration dependent.

#### Figure 1: Signal Groupings

The signals shown in Table 2 are described using the port view information (4x mode) in Figure 1. The ball map view in the figure is to show compatibility with the Tsi576 and Tsi577-Z devices.

| Pin Name                                                                                      | Туре       | Description                                                                                                                                              | Recommended<br>Termination <sup>a</sup> |

|-----------------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| PORT n = 1x/4x Mode Se<br>PORT m = 1x Mode Seri<br>n = 0, 2, 4, 6<br>m = n+1, n+8, n+9 for ea | al RapidIO |                                                                                                                                                          |                                         |

| Serial Port Transmit                                                                          |            |                                                                                                                                                          |                                         |

| SP{n}_TA_p                                                                                    | O, SRIO    | Port n Lane A Differential Non-inverting Transmit<br>Data output (4x mode)<br>Port n Differential Non-inverting Transmit Data<br>output (1x mode)        | No termination required.                |

| SP{n}_TA_n                                                                                    | O, SRIO    | Port n Lane A Differential Inverting Transmit Data<br>output (4x mode)<br>Port n Differential Inverting Transmit Data output<br>(1x mode)                | No termination required.                |

| SP{n}_TB_p                                                                                    | O, SRIO    | Port n Lane B Differential Non-inverting Transmit<br>Data output (4x mode)<br>Port m (=n+1) Differential Non-inverting Transmit<br>Data output (1x mode) | No termination required.                |

| SP{n}_TB_n                                                                                    | O, SRIO    | Port n Lane B Differential Inverting Transmit Data<br>output (4x mode)<br>Port m (=n+1) Differential Inverting Transmit Data<br>output (1x mode)         | No termination required.                |

| SP{n}_TC_p                                                                                    | O, SRIO    | Port n Lane C Differential Non-inverting Transmit<br>Data output (4x mode)<br>Port m (=n+8) Differential Non-inverting Transmit<br>Data output (1x mode) | No termination required.                |

| SP{n}_TC_n                                                                                    | O, SRIO    | Port n Lane C Differential Inverting Transmit Data<br>output (4x mode)<br>Port m (=n+8) Differential Inverting Transmit Data<br>output (1x mode)         | No termination required.                |

| SP{n}_TD_p                                                                                    | O, SRIO    | Port n Lane D Differential Non-inverting Transmit<br>Data output (4x mode)<br>Port m (=n+9) Differential Non-inverting Transmit<br>Data output (1x mode) | No termination required.                |

| Pin Name            | Туре    | Description                                                                                                                                          | Recommended<br>Termination <sup>a</sup>  |

|---------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| SP{n}_TD_n          | O, SRIO | Port n Lane D Differential Inverting Transmit Data<br>output (4x mode)<br>Port m (=n+9) Differential Inverting Transmit Data<br>output (1x mode)     | No termination required.                 |

| Serial Port Receive |         |                                                                                                                                                      |                                          |

| SP{n}_RA_p          | I, SRIO | Port n Lane A Differential Non-inverting Receive<br>Data input (4x node)<br>Port n Differential Non-inverting Receive Data<br>input (1x mode)        | DC blocking capacitor of 0.1uF in series |

| SP{n}_RA_n          | I, SRIO | Port n Lane A Differential Inverting Receive Data<br>input (4x mode)<br>Port n Differential Inverting Receive Data input (1x<br>mode)                | DC blocking capacitor of 0.1uF in series |

| SP{n}_RB_p          | I, SRIO | Port n Lane B Differential Non-inverting Receive<br>Data input (4x mode)<br>Port m (=n+1) Differential Non-inverting Receive<br>Data input (1x mode) | DC blocking capacitor of 0.1uF in series |

| SP{n}_RB_n          | I, SRIO | Port n Lane B Differential Inverting Receive Data<br>input (4x mode)<br>Port m (=n+1) Differential Inverting Receive Data<br>input (1x mode)         | DC blocking capacitor of 0.1uF in series |

| SP{n}_RC_p          | I, SRIO | Port n Lane C Differential Non-inverting Receive<br>Data input (4x mode)<br>Port m (=n+8) Differential Non-inverting Receive<br>Data input (1x mode) | DC blocking capacitor of 0.1uF in series |

| SP{n}_RC_n          | I, SRIO | Port n Lane C Differential Inverting Receive Data<br>input (4x mode)<br>Port m (=n+8) Differential Inverting Receive Data<br>input (1x mode)         | DC blocking capacitor of 0.1uF in series |

| SP{n}_RD_p          | I, SRIO | Port n Lane D Differential Non-inverting Receive<br>Data input (4x mode)<br>Port m (=n+9) Differential Non-inverting Receive<br>Data input (1x mode) | DC blocking capacitor of 0.1uF in series |

| SP{n}_RD_n          | I, SRIO | Port n Lane D Differential Inverting Receive Data<br>input (4x mode)<br>Port m (=n+9) Differential Inverting Receive Data<br>input (1x mode)         | DC blocking capacitor of 0.1uF in series |

| Pin Name                  | Туре                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Recommended<br>Termination <sup>a</sup>                                                                                                                                               |

|---------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial Port Configuration | -                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                       |

| SP{n}_REXT                | 1                    | Used to connect a resistor to VSS to provide a reference current for the driver and equalization circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Series resistor of 191Ω<br>(1%) connected to VSS.                                                                                                                                     |

| SPn_MODESEL<br>(PWRUP)    | I/O,<br>LVTTL,<br>PD | Selects the operating mode for all four serial ports<br>within a given MAC n (n = {0,2,4,6})<br>0 = MAC n operating in 4x+0x+0x+0x mode as<br>described in section "4x + 0x + 0x + 0x<br>Configuration" on page 77<br>1 = MAC n operating in 1x+1x+1x+1x mode as<br>described in section "1x + 1x + 1x + 1x<br>Configuration" on page 77<br>Note: The MAC_MODE in the "SRIO MAC x<br>Digital Loopback and Clock Selection Register" on<br>page 407 overrides and determine the operating<br>mode for the corresponding ports.<br>Output capability of this pin is only used in test<br>mode. | Pin must be tied off<br>according to the required<br>configuration. Either a 10K<br>pull up to VDD_IO or a<br>10K pull-down to VSS.<br>Internal pull-down may be<br>used for logic 0. |

| able 2: Signal Descriptions and Recommended Termination |

|---------------------------------------------------------|

|---------------------------------------------------------|

| Pin Name               | Туре                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Recommended<br>Termination <sup>a</sup>                                                                                                                                             |

|------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SP{n}_PWRDN<br>(PWRUP) | I/O,<br>LVTTL,<br>PU | Port n Transmit and Receive Power Down Control<br>(where n = {2, 4, 6})<br>This signal controls the state of Port n inside a<br>given MAC n.<br>If Port n is in 4X mode, then the SPn_PWRDN<br>controls the state of all four lanes (A/B/C/D) of<br>SerDes Macro.<br>If Port n is in 1X mode, related port m are<br>controlled by SPm_PWRDN. If SPn_PWRDN is<br>set and all three other ports in the same given<br>MACn have their SPm_PWRDN set, then the<br>given MACn SERDES is also powered down.<br>When n=x, the related m ports are (x+1, x+8,<br>x+9).<br>0 = Port n Powered Up<br>1 = Port n Powered Down<br>Override SP{n}_PWRDN using PWDN_X4 field in<br>the "SRIO MAC x Digital Loopback and Clock<br>Selection Register" on page 407.<br>Output capability of this pin is only used in test<br>mode. | Pin must be tied off<br>according to the required<br>configuration. Either a 10K<br>pull up to VDD_IO or a<br>10K pull-down to VSS.<br>Internal pull-up may be<br>used for logic 1. |

| SP{m}_PWRDN<br>(PWRUP) | I/O,<br>LVTTL,<br>PU | Port m Transmit and Receive Power Down<br>Control (where m= {1, 3, 5,<br>7,8,9,10,11,12,13,14,15})<br>This signal controls the state of Port m. Note that<br>Port m is never used when 4x mode is selected<br>for a Serial Rapid I/O MAC, and it can be powered<br>down.<br>0 = Port m Powered Up<br>1 = Port m Powered Down<br>If SPn is in 1X mode and SPn_PWRDN is set and<br>all three other ports in the same given MACn have<br>their SPm_PWRDN set, then the given MACn<br>SERDES is also powered down.<br>Override SP{m}_PWRDN using PWDN_X1/X4<br>field in the "SRIO MAC x Digital Loopback and<br>Clock Selection Register" on page 407.<br>Output capability of this pin is only used in test<br>mode.                                                                                                  | Pin must be tied off<br>according to the required<br>configuration. Either a 10K<br>pull up to VDD_IO or a<br>10K pull-down to VSS.<br>Internal pull-up may be<br>used for logic 1. |

| Pin Name                  | Туре                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Recommended<br>Termination <sup>a</sup>                                                                                                                                                                          |

|---------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMP_MODE[1:0]<br>(PWRUP) | I, LVTTL,<br>{PU, PD} | Tsi577 Compatibility Modes<br>These signals are for backward compatibility with<br>existing devices<br>00 = Tsi577-Z Replacement (16*1X ports)<br>01 = Tsi576 Replacement (2*4X + 8*1X)<br>10 = Tsi577 (default)<br>11 = Reserved<br>For further detail refer to "Tsi577 Compatibility<br>Modes" on page 25.                                                                                                                                                                    | Pin must be tied off<br>according to the required<br>configuration. Either a 10K<br>pull up to VDD_IO or a<br>10K pull-down to VSS.<br>Internal pull-up/pull-down<br>may be used for default<br>setting of 2'b10 |

| Serial Port Speed Select  |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                  |

| SP_IO_SPEED[1]<br>(PWRUP) | I/O,<br>LVTTL,<br>PU  | Serial Port Transmit and Receive operating<br>frequency select. SP_IO_SPEED[1:0], these pin<br>select the power-up serial port frequency for <i>all</i><br>ports.<br>00 = 1.25Gbit/s<br>01 = 2.5Gbit/s<br>10 = 3.125Gbit/s (default)<br>11 = Illegal<br>Note; The SP_IO_SPEED[1:0] setting is equal to<br>theIO_SPEED field in the "SRIO MAC x Digital<br>Loopback and Clock Selection Register" on<br>page 407.<br>Output capability of this pin is only used in test<br>mode. | Pin must be tied off<br>according to the required<br>configuration. Either a 10K<br>pull-up to VDD_IO or a<br>10K pull-down to VSS.<br>Internal pull-up may be<br>used for logic 1.                              |

| SP_IO_SPEED[0]<br>(PWRUP) | I/O,<br>LVTTL,<br>PD  | See SP_IO_SPEED[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pin must be tied off<br>according to the required<br>configuration. Either a 10K<br>pull-up to VDD_IO or a<br>10K pull-down to VSS.<br>Internal pull-down may be<br>used for logic 0.                            |

Table 2: Signal Descriptions and Recommended Termination

| Pin Name                  | Туре                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Recommended<br>Termination <sup>a</sup>                                                                                                                                                                                                 |

|---------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SP_CLK_SEL<br>(PWRUP)     | I/O,<br>LVTTL,<br>PD | Reference clock speed<br>1 = 125-MHz Reference clock<br>0 = 156.25-MHz Reference clock<br>This signal configures the MPLL settings for the<br>RapidIO SerDes.<br>Output capability of this pin is only used in test<br>mode.                                                                                                                                                                                                                                                                                                                        | Pin must be tied off<br>according to the required<br>configuration. Either a 10K<br>pull-up to VDD_IO or a<br>10K pull-down to VSS.<br>Internal pull-down may be<br>used for logic 0.                                                   |

| Serial Port Lane Ordering | g Select             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                         |

| SP_RX_SWAP<br>(PWRUP)     | I, LVTTL,<br>PD      | Configures the order of 4X receive/transmit lanes<br>on serial ports.<br>0 = A, B, C, D<br>1 = D, C, B, A<br>Override SP_RX(TX)_SWAP<br>usingSWAP_RX(TX) field in the "SRIO MAC x<br>Digital Loopback and Clock Selection Register" on<br>page 407.<br>This signal is ignored in 1X mode.<br>Note: Ports that require the use of lane swapping<br>for ease of routing will only function as 4x mode<br>ports. The re-configuration of a swapped port to<br>dual 1x mode operation results in the inability to<br>connect to a 1x mode link partner. | No termination required.<br>Internal pull-down can be<br>used for logic 0. Pull up to<br>VDD_IO through 10K if<br>external pull-up is desired.<br>Pull down to VSS through<br>a 10K resistor if an<br>external pull-down is<br>desired. |

| SP_TX_SWAP<br>(PWRUP)     | I, LVTTL,<br>PD      | See SP_RX_SWAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | No termination required.<br>Internal pull-down can be<br>used for logic 0. Pull up to<br>VDD_IO through 10K if<br>external pull-up is desired.<br>Pull down to VSS through<br>10K resistor if an external<br>pull-down is desired.      |

| Table 2: Signal Descriptions and | Recommended Termination |

|----------------------------------|-------------------------|

|----------------------------------|-------------------------|

| Pin Name        | Туре                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Recommended<br>Termination <sup>a</sup>                                                           |  |  |  |

|-----------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|

| Clock and Reset | Clock and Reset            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                   |  |  |  |

| S_CLK_p         | I,<br>CML                  | Differential non-inverting reference clock. The<br>clock is used for following purposes: SERDES<br>reference clock, serial port system clock, ISF                                                                                                                                                                                                                                                                                                                                                                                                                                   | AC coupling capacitor of 0.1uF required.                                                          |  |  |  |

| S_CLK_n         | I,<br>CML                  | clock and test clock. The clock frequency is<br>defined in the Minimum Clock Frequency<br>Requirements section.<br>The maximum frequency of this input clock is<br>156.25 MHz.                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                   |  |  |  |

| HARD_RST_b      | l<br>LVTTL,<br>Hyst,<br>PU | Schmidt-triggered hard reset. Asynchronous<br>active low reset for the entire device.<br>The Tsi577 does not contain a voltage detector to<br>generate internal reset.                                                                                                                                                                                                                                                                                                                                                                                                              | Connect to a power-up<br>reset source. See "Reset<br>Requirements" on page 66<br>for more detail. |  |  |  |

| Interrupts      |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                   |  |  |  |

| INT_b           | O, OD,<br>LVTTL,<br>2mA    | Interrupt signal (open drain output)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | External pull-up required.<br>Pull up to VDD_IO through<br>a 10K resistor.                        |  |  |  |

| SW_RST_b        | O, OD,<br>LVTTL,<br>2mA    | Software reset (open drain output): This signal is<br>asserted when a RapidIO port receives a valid<br>reset request on a RapidIO link. If self-reset is not<br>selected, this pin remains asserted until the reset<br>request is cleared from the status registers. If<br>self-reset is selected, this pin remains asserted<br>until the self reset is complete. If the Tsi577 is<br>reset from the HARD_RST_b pin, this pin is<br>de-asserted and remains de-asserted after<br>HARD_RST_b is released.<br>For more information, refer to "Resets" in the<br>Tsi577 User's Manual. | External pull-up required.<br>Pull up to VDD_IO through<br>a 10K resistor.                        |  |  |  |

Table 2: Signal Descriptions and Recommended Termination

|                        |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                           | Recommended                                                                                                                                                                 |  |  |

|------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name               | Туре                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                               | Termination <sup>a</sup>                                                                                                                                                    |  |  |

| Miscellaneous          |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                             |  |  |

| Multicast              |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                             |  |  |

| MCES                   | I/O,<br>LVTTL,<br>PD            | Multicast Event Symbol pin.<br>As an input, an edge (rising or falling) will trigger a<br>Multicast Event Control Symbol to be sent to all<br>enabled ports.<br>As an output, this pin will toggle its value every<br>time an Multicast Event Control Symbol is<br>received by any port which is enabled for<br>Multicast event control symbols.<br>Refer to section "Multicast-Event Control<br>Symbols" on page 58 for further details. | No termination required.<br>This pin must not be driven<br>by an external source until<br>all power supply rails are<br>stable.                                             |  |  |

| l <sup>2</sup> C       |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                             |  |  |

| I2C_SCLK               | I/O, OD,<br>LVTTL,<br>PU<br>8mA | I <sup>2</sup> C clock, up to 100 kHz.<br>This clock signal must be connected to the clock<br>of the serial EEPROM on the I <sup>2</sup> C bus.                                                                                                                                                                                                                                                                                           | No termination required.<br>Internal pull-up may be<br>used for logic 1.<br>Pull up to VDD_IO through<br>a minimum 470 ohms<br>resistor if higher edge rate<br>is required. |  |  |

| I2C_SD                 | I/O, OD,<br>LVTTL,<br>PU<br>8mA | I <sup>2</sup> C input and output data bus (bidirectional open drain)                                                                                                                                                                                                                                                                                                                                                                     | No termination required.<br>Internal pull-up may be<br>used for logic 1.<br>Pull up to VDD_IO through<br>a minimum 470 ohms<br>resistor if higher edge rate<br>required.    |  |  |

| I2C_DISABLE<br>(PWRUP) | I, LVTTL,<br>PD                 | Disable I <sup>2</sup> C register loading after reset. When asserted, the Tsi577 will not attempt to load register values from I <sup>2</sup> C.                                                                                                                                                                                                                                                                                          | No termination<br>required.Pull up to<br>VDD_IO through a 10K<br>resistor if I <sup>2</sup> C loading is not<br>required.                                                   |  |  |

| Pin Name               | Туре                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Recommended<br>Termination <sup>a</sup>                                                                                                                                                                       |  |

|------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| I2C_MA<br>(PWRUP)      | I, LVTTL,<br>PU       | I <sup>2</sup> C Multibyte Address<br>When driven high, I <sup>2</sup> C module expects multi-byte<br>peripheral addressing; otherwise, when driven<br>low, single-byte peripheral address is assumed.<br>The value on this pin, sets the PA_SIZE field in<br>"I2C Master Configuration Register" on page 476<br>and PSIZE field in "I2C Boot Control Register" on<br>page 496.                                                                                                                                                                                                       | No termination required.<br>Internal pull-up may be<br>used for logic 1.<br>Pull up to VDD_IO through<br>10K resistor if an external<br>pull-up is desired. Pull<br>down to VSS to change<br>the logic state. |  |

| I2C_SA[1:0]<br>(PWRUP) | I, LVTTL,<br>{PU, PU} | I <sup>2</sup> C Slave Address pins<br>The values on these two pins represent the<br>values for the lower 2 bits of the 7-bit address of<br>Tsi577 when acting as an I <sup>2</sup> C slave (field<br>SLV_ADDR in "I2C Slave Configuration Register"<br>on page 493).<br>These pins with I2C_SEL is also used to update<br>the lower 2 bits of the 7-bit address of the<br>EEPROM address it boots from (field<br>BOOT_ADDR in "I2C Boot Control Register" on<br>page 496) and to access an external slave (field<br>DEV_ADDR in "I2C Master Configuration<br>Register" on page 476). | No termination required.<br>Internal pull-up may be<br>used for logic 1.<br>Pull up to VDD_IO through<br>10K resistor if an external<br>pull-up is desired. Pull<br>down to VSS to change<br>the logic state. |  |

| I2C_SEL<br>(PWRUP)     | I, LVTTL,<br>PU       | I <sup>2</sup> C Pin Select<br>Together with the I2C_SA[1:0] pins, Tsi577<br>determines the lower 2 bits of the 7-bit address of<br>the EEPROM address it boots from.<br>When asserted, the I2C_SA[1:0] values are also<br>used as the lower 2 bits of the EEPROM address.<br>When de-asserted, the I2C_SA[1:0] pins are<br>ignored and the lower 2 bits of the EEPROM<br>address default to 00.                                                                                                                                                                                      | No termination required.<br>Internal pull-up may be<br>used for logic 1.<br>Pull up to VDD_IO through<br>10K resistor if an external<br>pull-up is desired. Pull<br>down to VSS to change<br>the logic state. |  |

| JTAG TAP Controller    |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                               |  |

| ТСК                    | I, LVTTL,<br>PD       | IEEE 1149.1 Test Access Port<br>Clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Pull up to VDD_IO through 10K resistor if not used.                                                                                                                                                           |  |

Table 2: Signal Descriptions and Recommended Termination

| Pin Name       | Туре                | Description                                                                                                                                                                                                                                                                                                                       | Recommended<br>Termination <sup>a</sup>                                                                                                                                                                                                                                                                          |  |  |

|----------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TDI            | I, LVTTL,<br>PU     | IEEE 1149.1 Test Access Port<br>Serial Data Input                                                                                                                                                                                                                                                                                 | Pull up to VDD_IO through<br>a 10K resistor if the signal<br>is not used or a if higher<br>edge rate is required.                                                                                                                                                                                                |  |  |

| TDO            | O,<br>LVTTL,<br>8mA | IEEE 1149.1 Test Access Port<br>Serial Data Output                                                                                                                                                                                                                                                                                | No connect if JTAG is not<br>used.<br>Pull up to VDD_IO through<br>a 10K resistor if used.                                                                                                                                                                                                                       |  |  |

| TMS            | I, LVTTL,<br>PU     | IEEE 1149.1 Test Access Port<br>Test Mode Select                                                                                                                                                                                                                                                                                  | Pull up to VDD_IO through a 10K resistor if not used.                                                                                                                                                                                                                                                            |  |  |

| TRST_b         | I, LVTTL,<br>PU     | IEEE 1149.1 Test Access Port TAP Reset Input<br>This input must be asserted during the assertion<br>of HARD-RST_b. Afterwards, it may be left in<br>either state.<br>Combine the HARD_RST_b and TRST_b signals<br>with an AND gate and use the output to drive the<br>TRST_b pin.                                                 | Tie to VSS through a 10K resistor if not used.                                                                                                                                                                                                                                                                   |  |  |

| BCE            | I, LVTTL,<br>PU     | Boundary Scan compatibility enabled pin. This<br>input is used to aid 1149.6 testing.<br>This signal also enables system level diagnostic<br>capability using features built into the SerDes.<br>This signal must be tied to VDD_IO during normal<br>operation of the device, and during JTAG<br>accesses of the device registers | <ul> <li>This signal should have<br/>the capability to be<br/>pulled-up or pulled-low.</li> <li>The default setting is to<br/>be pulled-up.</li> <li>Pulling the signal low<br/>enables the signal<br/>analyzer functionality on<br/>the SerDes</li> <li>A 10K resistor to<br/>VDD_IO should be used.</li> </ul> |  |  |

| Power Supplies |                     |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                  |  |  |

| SP_AVDD        | -                   | 3.3V supply for bias generator circuitry. This is<br>required to be a low-noise supply.Refer to "Decouplin<br>Requirements" on<br>page 59.                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                  |  |  |

| REF_AVDD       | -                   | Analog 1.2V for Reference Clock (S_CLK_P/N).       Refer to "Deco         Clock distribution network power supply.       Requirements"         page 59.       Page 59.                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                  |  |  |

| Pin Name      | Туре | Description                                                         | Recommended<br>Termination <sup>a</sup>              |

|---------------|------|---------------------------------------------------------------------|------------------------------------------------------|

| Common Supply | -    |                                                                     |                                                      |

| VDD_IO        | -    | Common 3.3V supply for LVTTL I/O                                    | Refer to "Decoupling<br>Requirements" on<br>page 59. |

| VSS           | -    | Common ground supply for digital logic                              | Refer to "Decoupling<br>Requirements" on<br>page 59. |

| VDD           | -    | Common 1.2V supply for digital logic                                | Refer to "Decoupling<br>Requirements" on<br>page 59. |

| SP_VDD        | -    | 1.2V supply for CDR, Tx/Rx, and digital logic for all RapidIO ports | Refer to "Decoupling<br>Requirements" on<br>page 59. |

a. Signals for unused serial ports do not require termination and can be left as N/Cs.

#### 1.1.3 Tsi577 Compatibility Modes

Table 3 lists the different COMP\_MODE[1:0] pin configurations which allow backward pin and software compatibility with the Tsi576 and Tsi577-Z devices.

- When Tsi577 is placed in a Tsi577-Z socket, COMP\_MODE is automatically set to 00. The device powers up with all ports (0..15) in x1.

- When Tsi577 is placed in a Tsi576 socket, COMP\_MODE is automatically set to 01

- The Tsi577 powers up with ports 0 and 6 in 4x mode and ports 2 -> 5, 10 -> 13 in 1x mode (2\*x4 + 8\*x1). In this case, the maximum 1x mode ports is 12.

- The default mode for Tsi577 is 10.

- Ports 0, 2, 4, 6 can be 4x mode or all 16 ports (0..15) can be 1x mode.

Table 3: Tsi577 Compatibility Modes

| Device ID | COMP_MODE[1:0] | Max Number of Ports |    | Port Total | Description           |

|-----------|----------------|---------------------|----|------------|-----------------------|

| 0x577     | 00             | 4x mode             | 0  | 16         | Tsi577-Z Replacement  |

|           |                | 1x mode             | 16 |            |                       |

| 0x577     | 01             | 4x mode             | 2  | 16         | Tsi576 Replacement    |

|           |                | 1x mode             | 12 |            |                       |

| 0x577     | 10             | 4x mode             | 4  | 16         | Tsi577 Mode (default) |

|           |                | 1x mode             | 16 |            |                       |

| 0x577     | 11             | Reserved            |    | •          |                       |

## 1.2 Pinlist and Ballmap

The pinlist and ballmap information for the Tsi577 are available by visiting www.IDT.com and registering. For more information, see the following documents:

- Tsi577 Pinlist

- Tsi577 Ballmap