# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

UNIT

V

Ω

nC

Taiwan Semiconductor

**KEY PERFORMANCE PARAMETERS**

VALUE

500

1.38

15

HALOGEN

## **N-Channel Power MOSFET**

$500V, 5A, 1.38\Omega$

#### FEATURES

- 100% UIS and R<sub>g</sub> tested

- Advanced planar process

- Compliant to RoHS Directive 2011/65/EU and in accordance to WEEE 2002/96/EC

- Halogen-free according to IEC 61249-2-21

#### APPLICATIONS

- AC/DC LED Lighting

- Power Supply

- Charger

TO-252 (DPAK)

PARAMETER

$V_{\text{DS}}$

$R_{DS(on)}\left(max

ight)$

$\mathbf{Q}_{g}$

Notes: MSL 3 (Moisture Sensitivity Level) per J-STD-020

| ABSOLUTE MAXIMUM RATINGS (T <sub>A</sub> = 25°C unless otherwise noted) |                                      |              |      |  |  |

|-------------------------------------------------------------------------|--------------------------------------|--------------|------|--|--|

| PARAMETER                                                               | SYMBOL                               | Limit        | UNIT |  |  |

| Drain-Source Voltage                                                    | V <sub>DS</sub>                      | 500          | V    |  |  |

| Gate-Source Voltage                                                     | V <sub>GS</sub>                      | ±30          | V    |  |  |

| $T_{\rm C} = 25^{\circ}$                                                | C L                                  | 5            | •    |  |  |

| Continuous Drain Current (Note 1) $T_c = 100$                           | P°C                                  | 2.2          | A    |  |  |

| Pulsed Drain Current (Note 2)                                           | I <sub>DM</sub>                      | 20           | A    |  |  |

| Total Power Dissipation @ $T_{C} = 25^{\circ}C$                         | P <sub>DTOT</sub>                    | 83           | W    |  |  |

| Single Pulse Avalanche Energy (Note 3)                                  | E <sub>AS</sub>                      | 122.5        | mJ   |  |  |

| Single Pulse Avalanche Current (Note 3)                                 | I <sub>AS</sub>                      | 3.5          | А    |  |  |

| Operating Junction and Storage Temperature Range                        | ge T <sub>J</sub> , T <sub>STG</sub> | - 55 to +150 | °C   |  |  |

| THERMAL PERFORMANCE                    |                  |       |      |  |  |

|----------------------------------------|------------------|-------|------|--|--|

| PARAMETER                              | SYMBOL           | Limit | UNIT |  |  |

| Junction to Case Thermal Resistance    | R <sub>eJC</sub> | 1.5   | °C/W |  |  |

| Junction to Ambient Thermal Resistance | R <sub>eja</sub> | 62    | °C/W |  |  |

**Thermal Performance Note:**  $R_{\Theta JA}$  is the sum of the junction-to-case and case-to-ambient thermal resistances. The case-thermal reference is defined at the solder mounting surface of the drain pins.  $R_{\Theta JA}$  is guaranteed by design while  $R_{\Theta CA}$  is determined by the user's board design.  $R_{\Theta JA}$  shown below for single device operation on FR-4 PCB in still air.

## TSM5NC50CP

Taiwan Semiconductor

| ELECTRICAL SPECIFICATIONS (T <sub>A</sub> = 25°C unless otherwise noted) |                                                                                                                                        |                     |     |      |          |      |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|------|----------|------|

| PARAMETER                                                                | CONDITIONS                                                                                                                             | SYMBOL              | MIN | ТҮР  | MAX      | UNIT |

| Static                                                                   |                                                                                                                                        |                     |     |      |          |      |

| Drain-Source Breakdown Voltage                                           | $V_{GS} = 0V, I_D = 250 \mu A$                                                                                                         | BV <sub>DSS</sub>   | 500 |      |          | V    |

| Gate Threshold Voltage                                                   | $V_{DS} = V_{GS}, I_D = 250 \mu A$                                                                                                     | V <sub>GS(TH)</sub> | 2.5 | 3.3  | 4.5      | V    |

| Gate Body Leakage                                                        | $V_{GS} = \pm 30 V, \ V_{DS} = 0 V$                                                                                                    | I <sub>GSS</sub>    |     |      | ±100     | nA   |

| Zero Gate Voltage Drain Current                                          | $V_{\text{DS}} = 500 V, \ V_{\text{GS}} = 0 V$                                                                                         | I <sub>DSS</sub>    |     |      | 1        | μA   |

| Drain-Source On-State Resistance<br>(Note 4)                             | $V_{GS} = 10V, I_D = 2.4A$                                                                                                             | R <sub>DS(on)</sub> |     | 1.2  | 1.38     | Ω    |

| Dynamic (Note 5)                                                         | L                                                                                                                                      |                     |     | I    | <u> </u> |      |

| Total Gate Charge                                                        |                                                                                                                                        | Qg                  |     | 15   |          |      |

| Gate-Source Charge                                                       | $V_{DS} = 400V, I_D = 4.8A,$                                                                                                           | Q <sub>gs</sub>     |     | 4    |          | nC   |

| Gate-Drain Charge                                                        | V <sub>GS</sub> = 10V                                                                                                                  | Q <sub>gd</sub>     |     | 7    |          |      |

| Input Capacitance                                                        |                                                                                                                                        | C <sub>iss</sub>    |     | 586  |          |      |

| Output Capacitance                                                       | $V_{\rm DS} = 50 V, V_{\rm GS} = 0 V,$                                                                                                 | C <sub>oss</sub>    |     | 45   |          | pF   |

| Reverse Transfer Capacitance                                             | f = 1.0MHz                                                                                                                             | C <sub>rss</sub>    |     | 1    |          | 1    |

| Gate Resistance                                                          | f = 1.0MHz                                                                                                                             | R <sub>g</sub>      |     | 2.9  | 5.8      | Ω    |

| Switching (Note 6)                                                       |                                                                                                                                        |                     |     |      |          |      |

| Turn-On Delay Time                                                       |                                                                                                                                        | t <sub>d(on)</sub>  |     | 8.2  |          |      |

| Turn-On Rise Time                                                        | $\begin{split} V_{\text{DD}} &= 250 V, \ R_{\text{G}} = 5 \Omega, \\ I_{\text{D}} &= 4.8 \text{A}, \ V_{\text{GS}} = 10 V \end{split}$ | t <sub>r</sub>      |     | 20.4 |          |      |

| Turn-Off Delay Time                                                      |                                                                                                                                        | t <sub>d(off)</sub> |     | 15.4 |          | ns   |

| Turn-Off Fall Time                                                       |                                                                                                                                        | t <sub>f</sub>      |     | 20   |          | ]    |

| Source-Drain Diode                                                       |                                                                                                                                        |                     |     |      |          |      |

| Forward Voltage (Note 4)                                                 | $I_{\rm S} = 4.8 A, V_{\rm GS} = 0 V$                                                                                                  | V <sub>SD</sub>     |     |      | 1.3      | V    |

| Reverse Recovery Time                                                    | I <sub>S</sub> = 4.8A                                                                                                                  | t <sub>rr</sub>     |     | 205  |          | ns   |

| Reverse Recovery Charge                                                  | dl <sub>F</sub> /dt = 100A/µs                                                                                                          | Q <sub>rr</sub>     |     | 1.5  |          | μC   |

Notes:

1. Current limited by package

- 2. Pulse width limited by the maximum junction temperature

- 3. L = 20mH, I\_{AS} = 3.5A, V\_{DD} = 50V, R\_G = 25\Omega, Starting T\_J =  $25^{\circ}C$

- 4. Pulse test: PW  $\leq$  300µs, duty cycle  $\leq$  2%

- 5. For DESIGN AID ONLY, not subject to production testing.

- 6. Switching time is essentially independent of operating temperature.

#### **ORDERING INFORMATION**

| PART NO.       | PACKAGE       | PACKING             |

|----------------|---------------|---------------------|

| TSM5NC50CP ROG | TO-252 (DPAK) | 2,500pcs / 13" Reel |

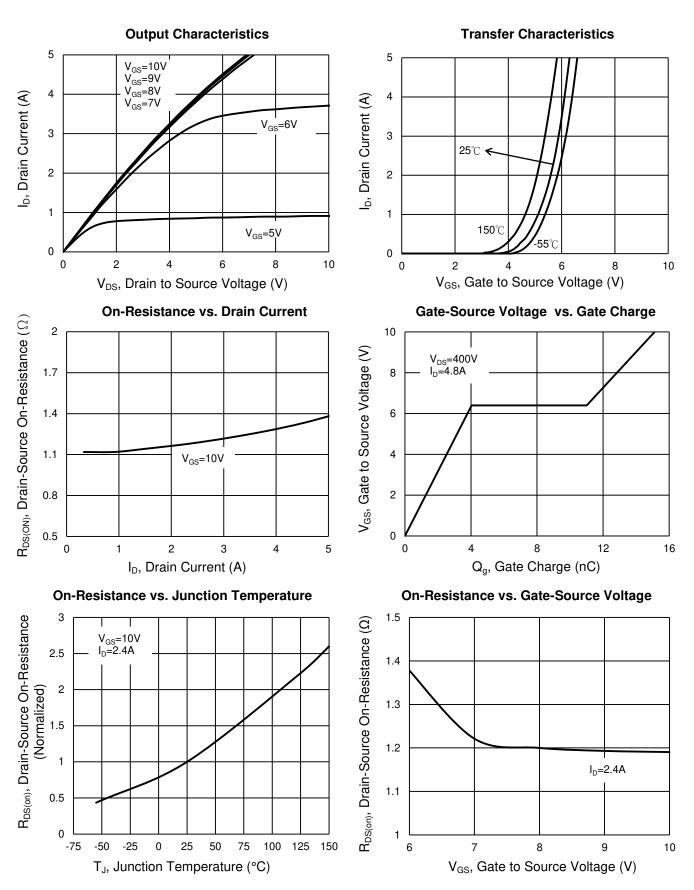

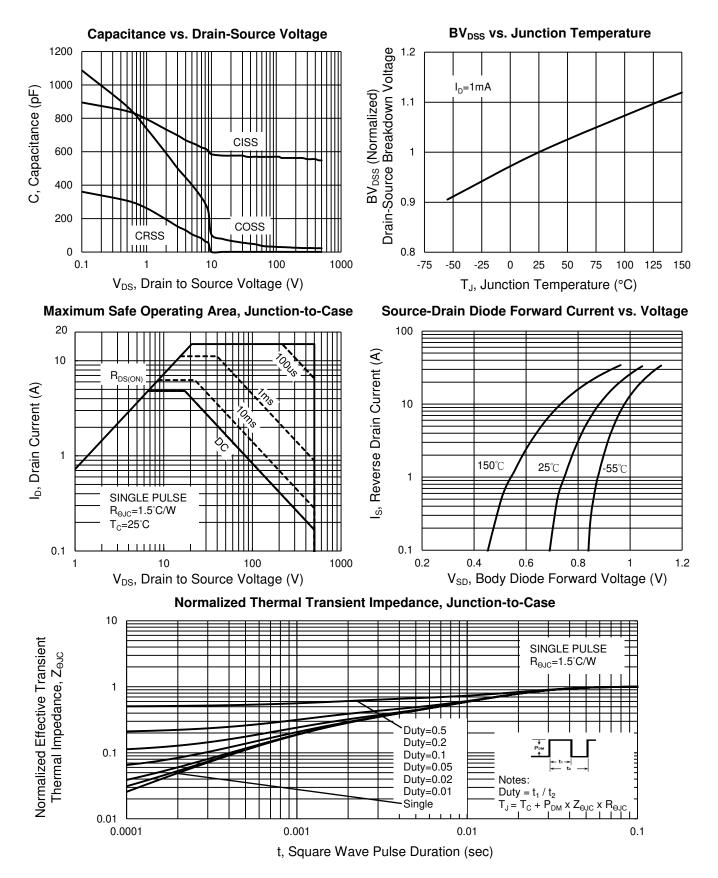

#### **CHARACTERISTICS CURVES**

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

#### **CHARACTERISTICS CURVES**

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

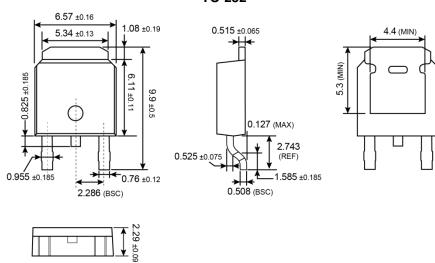

#### PACKAGE OUTLINE DIMENSIONS (Unit: Millimeters)

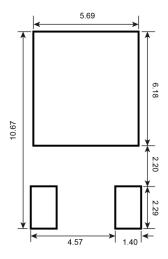

#### SUGGESTED PAD LAYOUT (Unit: Millimeters)

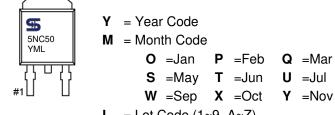

R =Apr

V =Aug Z =Dec

#### **MARKING DIAGRAM**

**L** = Lot Code  $(1 \sim 9, A \sim Z)$

Taiwan Semiconductor

#### Notice

Specifications of the products displayed herein are subject to change without notice. TSC or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.

Information contained herein is intended to provide a product description only. No license, express or implied, to any intellectual property rights is granted by this document. Except as provided in TSC's terms and conditions of sale for such products, TSC assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of TSC products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify TSC for any damages resulting from such improper use or sale.