Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Communication Solutions

Edition 2006-12-19

Published by

Infineon Technologies AG

81726 München, Germany

© Infineon Technologies AG 2006.

All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# TUA 6045-2

Low Power 3-Band Digital TV / Portable Tuner IC

TAIFUN 3

Communication Solutions

#### TUA 6045-2 'TAIFUN 3'

| Revision History:      |                                                                                            | 2006-12-19       | Data Sheet, Revision 3.1                |

|------------------------|--------------------------------------------------------------------------------------------|------------------|-----------------------------------------|

| Previous Vo            | ersion:                                                                                    | 2006-09-12       | Preliminary Specification, Revision 3.0 |

| Page Subjects (majo    |                                                                                            | ajor changes sin | ce last revision)                       |

| 9 - 11, 28,<br>30 - 41 | B, L-Band application added. Operating range and AC/DC Characteristic extended for L-Band. |                  |                                         |

| 31 - 41 Table Footnote |                                                                                            | ote added with d | lescription for impedance measurement.  |

|                        |                                                                                            |                  |                                         |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

horst.klein@infineon.com

| Table of                                                                                              | Contents                                                                                                                                                                                                                                                                                                 | Page                                                                 |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|                                                                                                       | List of Tables                                                                                                                                                                                                                                                                                           | 7                                                                    |

|                                                                                                       | List of Figures                                                                                                                                                                                                                                                                                          | 8                                                                    |

| 1                                                                                                     | Product Info                                                                                                                                                                                                                                                                                             | 9                                                                    |

| 2<br>2.1<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.2<br>2.2.1                        | Product Description Features General Mixer/Oscillator SAW Filter Driver IF AGC Amplifier PLL IF switch and Loop through for tuner alignment Application Recommended band limits in MHz                                                                                                                   | . 10<br>. 10<br>. 11<br>. 11<br>. 11                                 |

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8 | Functional Description Pin Configuration Pin Definition and Functions Functional Block Diagram Circuit Description Mixer-Oscillator-block, SAW filter driver RF AGC IF AGC amplifier PLL block, XTAL oscillator Bus Interface DC/DC clock output Power-on Reset, Stand-by Condition IF switch, Loop thru | . 13<br>. 14<br>. 21<br>. 22<br>. 22<br>. 22<br>. 23<br>. 23<br>. 24 |

| <b>4</b><br>4.1<br>4.2<br>4.3                                                                         | Applications Tuner application block diagram Application circuit for hybrid application Application circuit for L-Band application                                                                                                                                                                       | . 26<br>. 27                                                         |

| 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.2<br>5.3<br>5.4<br>5.5                                       | Reference Electrical Data Absolute Maximum Ratings Operating Range AC/DC Characteristics Bus Interface Bus Data Format Bus Timing Data Byte Specification, Function and Defaults                                                                                                                         | . 29<br>. 29<br>. 30<br>. 31<br>. 41<br>. 43                         |

| 6     | Package PG-VQFN-48                                    | 63 |

|-------|-------------------------------------------------------|----|

| 5.6.8 | Ripple susceptibility measurement                     | 62 |

| 5.6.7 | Cross modulation measurement in MID and HIGH bands    | 62 |

| 5.6.6 | Cross modulation measurement in LOW band              | 61 |

| 5.6.5 | Noise figure (NF) measurement in MID and HIGH bands   | 61 |

| 5.6.4 | Noise figure (NF) measurement in LOW band             | 60 |

| 5.6.3 | Matching circuit for optimum noise figure in LOW band | 60 |

| 5.6.2 | Gain (GV) measurement in MID and HIGH bands           | 59 |

| 5.6.1 | Gain (GV) measurement in LOW band                     | 59 |

| 5.6   | Measurement Circuits                                  | 59 |

| 5.5.2 | Read Data Registers                                   | 56 |

| 5.5.1 | Write Data Registers                                  | 48 |

## **List of Tables**

| Table 1  | ATSC tuners                                                        | 12 |

|----------|--------------------------------------------------------------------|----|

| Table 2  | DVB-T and analog tuners                                            | 12 |

| Table 3  | ISDB-T tuners                                                      | 12 |

| Table 4  | Absolute Maximum Ratings                                           | 29 |

| Table 5  | Operating Range                                                    | 30 |

| Table 6  | AC/DC Characteristics, $T_A = 25$ °C, $V_{CC} = 3.3$ V             | 31 |

| Table 7  | Pin Function                                                       | 41 |

| Table 8  | Chip Address Organization in I2C Mode                              | 42 |

| Table 9  | Address selection in I2C Mode                                      | 42 |

| Table 10 | Sub Addresses of Write Data Registers                              | 42 |

| Table 11 | Sub Addresses of Read Data Registers                               | 43 |

| Table 12 | Bus Data Format                                                    | 43 |

| Table 13 | Bus Timing                                                         | 46 |

| Table 14 | Subaddress 00H, Main Divider                                       | 48 |

| Table 15 | Subaddress 01H, Control Bytes                                      | 49 |

| Table 16 | Subaddress 02H, Reference Divider R and Crystal Oscillator Control | 50 |

| Table 17 | Subaddress 03H, AGC control and IF Signal Processing Control       | 52 |

| Table 18 | Subaddress 04H, DC-DC Converter                                    | 54 |

| Table 19 | Subaddress 06H, Mode Bytes, Test Mode and Standby Control          | 55 |

| Table 20 | Subaddress 80H, Status                                             | 56 |

| Table 21 | Subaddress 8EH, Chip Code "6045"                                   | 57 |

| Table 22 | Subaddress 8FH, Revision Code, advanced with design steps          | 58 |

# **List of Figures**

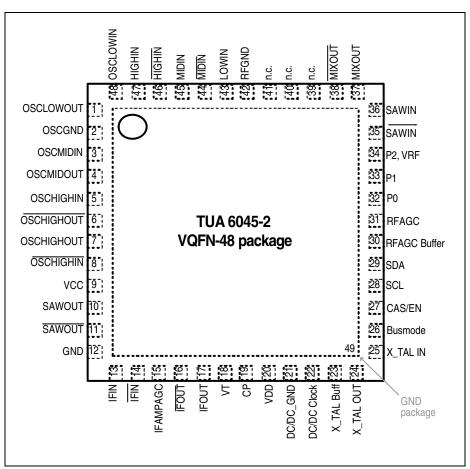

| Figure 1  | Pin Configuration TUA 6045-2 in VQFN-48 Package          |

|-----------|----------------------------------------------------------|

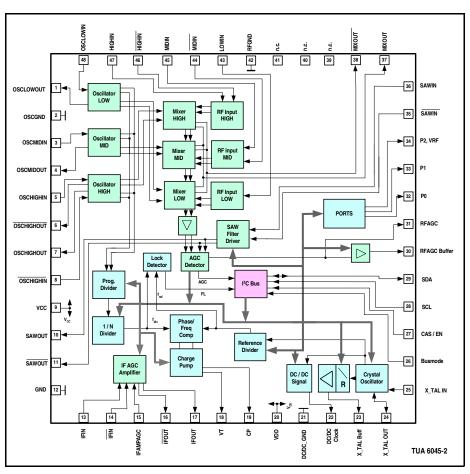

| Figure 2  | Block Diagram TUA 6045-2 in VQFN-48 package              |

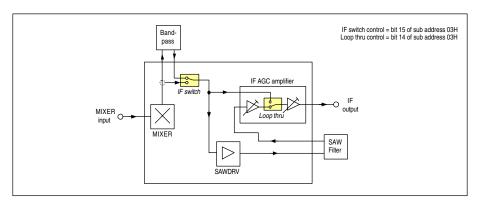

| Figure 3  | Functional Block Diagram of IF switch and Loop thru      |

| Figure 4  | Tuner application block diagram                          |

| Figure 5  | Circuit diagram for hybrid application (DVB-T / PAL)     |

| Figure 6  | Circuit diagram for L-Band application                   |

| Figure 7  | I2C Bus                                                  |

| Figure 8  | 3-Wire Bus                                               |

| Figure 9  | Gain (GV) measurement in LOW band                        |

| Figure 10 | Gain (GV) measurement in MID and HIGH bands 59           |

| Figure 11 | Matching circuit for optimum noise figure in LOW band 60 |

| Figure 12 | Noise figure (NF) measurement in LOW band 60             |

| Figure 13 | Noise figure (NF) measurement in MID and HIGH bands 61   |

| Figure 14 | Cross modulation measurement in LOW band                 |

| Figure 15 | Cross modulation measurement in MID and HIGH bands 62    |

| Figure 16 | Ripple susceptibility measurement                        |

| Figure 17 | PG-VQFN-48 Vignette 63                                   |

| Figure 18 | PG-VQFN-48 Outline Drawing 63                            |

**Product Info**

## 1 Product Info

## **General Description**

The **TUA 6045-2** integrates the mixer-oscillator, AGC amplifier and a digitally programmable phase lock loop (PLL). This makes the **TUA 6045-2** an ideal product for applications where size and low power consumption are required design key factors. Typical applications include TV's, VCR's, Set Top Boxes (STB) and also a range of portable products.

#### **Features**

#### General

- Suitable for PAL, NTSC, SECAM, DVB, DMB, DAB, ISDB-T and ATSC

- High band covers frequency range for L-Band up to 1.5 GHz

- Supply voltage range from 3 to 5.5 V

- Combined small wide AGC detection

- AGC + AGC buffer output

- · Low phase noise

- Full ESD protection

- Qualified according to JEDEC for consumer applications

#### Mixer/Oscillator

- Three band tuner

- Unbalanced highohmic LOW band input

- Balanced lowohmic MID band input

- · Balanced lowohmic HIGH band input

- Two pin oscillators for LOW/MID band

- Four pin oscillator for HIGH band

#### IF-Amplifier

- 4 IF pins to connect a 2 pole bandpass

- Symmetrical SAW driver

- · Fully balanced IF AGC amplifier

#### PLL

- I<sup>2</sup>C / three wire combi bus

- 4 independent I<sup>2</sup>C addresses

- · High voltage VCO tuning output

- Two PMOS ports

- One voltage referred port

- Internal LOW/MID/HIGH band switch

- Xtal oscillator, range from 4 to 16 MHz

- Xtal buffer output with programmable level and output divider

- Clock generator for DC/DC converter with programmable low and high time

#### Power management

Bus controlled stand by mode

## Application

The IC is suitable for PAL, NTSC, SECAM, DVB-C, DVB-T, DVB-H, DMB-T, DAB, ISDB-T, ATSC and L-Band tuners.

## Ordering Information

| Туре       | Ordering Code | Package    |  |  |

|------------|---------------|------------|--|--|

| TUA 6045-2 | SP000250164   | PG-VQFN-48 |  |  |

### **Product Description**

## 2 Product Description

The **TUA 6045-2** integrates the mixer-oscillator, variable AGC output amplifier and a digitally programmable phase lock loop (PLL) not requiring an external high voltage buffer. Furthermore, the **TUA 6045-2** integrates a buffered RF AGC and programmable clock signals for an external DC-DC up converter.

The integrated mixer oscillator function comprises of three balanced mixers. The first mixer has an unbalanced high impedance input while the other two have balance low impedance inputs. The tuner also has firstly, 2-pin asymmetric oscillators for both Low and Mid bands and secondly a 4-pin symmetrical oscillator for High band operations including a band selector switch.

The output signal from the mixer is amplified via a SAW filter driver followed by variable gain amplifier stage in order to achieve a constant output level used for A/D conversion. All functions can be programmed with up to four different IC addresses. Also, the PLL connected to a 4-16 MHz reference crystal which is buffered on-chip, allows the setting of the tuner oscillator with a minimum step size of 20 kHz. A Lock flag will be set once the PLL is locked and communicated via the I2C/3-Wire bus.

The complete control setting of the IC is done by a microprocessor via the I2C/3-Wire bus. The device also has three output ports of which P2 can be configured as a programmable output voltage port.

#### 2.1 Features

#### 2.1.1 General

- Supply voltage range 3 to 5.5 V.

- Suitable for PAL, NTSC, SECAM, DVB-T/H/C, DAB, ISDB-T, ATSC and L-Band.

- Wideband and Narrow AGC detectors for tuner RF AGC

- 5 programmable take-over points

- 2 programmable time constants.

- Low phase noise.

- Full ESD protection.

#### 2.1.2 Mixer/Oscillator

- High impedance mixer input (common emitter) for LOW band.

- Low impedance mixer input (common base) for MID band.

- Low impedance mixer input (common base) for HIGH band.

- 2 pin oscillator for LOW band.

- 2 pin oscillator for MID band.

- · 4 pin oscillator for HIGH band.

- Oscillator for HIGH band divided by 3 available for MID band mixer.

### **Product Description**

#### 2.1.3 SAW Filter Driver

Symmetrical IF preamplifier with low output impedance able to drive a compensated SAW filter (500 Ω//40 pF).

## 2.1.4 IF AGC Amplifier

Symmetrical variable gain IF output amplifier with low noise, high linearity, high dynamic range.

#### 2.1.5 PLL

- 4 independent I<sup>2</sup>C addresses, or 3-Wire bus mode.

- I<sup>2</sup>C bus protocol compatible with 3.3 V and 5V micro-controllers up to 400 kHz.

- · High voltage VCO tuning output.

- 3 PNP ports, one of them realized as programmable voltage output.

- 1 clock output for external DC/DC upconversion to generate the tuning supply voltage, may be used as NPN port.

- · Stand-by programmable for functional blocks allows customized ramping.

- · Internal LOW/MID/HIGH band switch.

- Lock-in flag.

- 4 to 16 MHz crystal oscillator with programmable output buffer.

- · programmable reference divider ratios.

- 4 charge pump currents, programmable in 15 steps.

## 2.1.6 IF switch and Loop through for tuner alignment

2 programmable switches to bypass the bandpass/SAW filter to facilitate the tuner pre-stage alignment.

## 2.2 Application

- The IC is suitable for PAL, NTSC, SECAM, DVB-T/H/C, DAB, ISDB-T, ATSC and L-Band tuners.

- The integrated RF AGC control has wide band detectors at the mixer inputs and a narrowband detector at the saw filter driver output.

## **Product Description**

## 2.2.1 Recommended band limits in MHz

Table 1 ATSC tuners

|      | RF i   | nput   | Oscillator |      |  |

|------|--------|--------|------------|------|--|

| Band | min.   | max.   | min.       | max. |  |

| LOW  | 55.25  | 157.25 | 101        | 203  |  |

| MID  | 163.25 | 451.25 | 201        | 479  |  |

| HIGH | 457.25 | 861.25 | 503        | 907  |  |

Table 2 DVB-T and analog tuners

|      | RF i   | nput   | Oscillator |        |  |

|------|--------|--------|------------|--------|--|

| Band | min.   | max.   | min.       | max.   |  |

| LOW  | 48.25  | 154.25 | 87.15      | 193.15 |  |

| MID  | 161.25 | 439.25 | 200.15     | 478.15 |  |

| HIGH | 447.25 | 863.25 | 486.15     | 902.15 |  |

Table 3 ISDB-T tuners

|      | RF i | nput | Oscillator |      |  |

|------|------|------|------------|------|--|

| Band | min. | max. | min.       | max. |  |

| LOW  | 93   | 167  | 150        | 224  |  |

| MID  | 173  | 467  | 230        | 524  |  |

| HIGH | 473  | 767  | 530        | 824  |  |

12

Note: Tuning margin of 3 MHz not included.

## 3 Functional Description

## 3.1 Pin Configuration

Figure 1 Pin Configuration TUA 6045-2 in VQFN-48 Package

## 3.2 Pin Definition and Functions

· Pin Definition and Functions

| Pin<br>No. | Symbol    | Equivalent I/O Schematic | Average DC voltage at V <sub>CC</sub> = 3.3V |       |       |

|------------|-----------|--------------------------|----------------------------------------------|-------|-------|

|            |           |                          | LOW                                          | MID   | HIGH  |

| 48         | OSCLOWIN  |                          | 2.3 V                                        |       |       |

| 1          | OSCLOWOUT | 48                       | 1.8 V                                        |       |       |

| 2          | OSCGND    | Oscillator ground        | 0.0 V                                        | 0.0 V | 0.0 V |

| 3          | OSCMIDIN  |                          |                                              | 2.3 V |       |

| 4          | OSCMIDOUT | 3                        |                                              | 1.8 V |       |

| Pin<br>No. | Symbol    | Equivalent I/O Schematic |        | Average DC voltage at V <sub>CC</sub> = 3.3V |        |  |

|------------|-----------|--------------------------|--------|----------------------------------------------|--------|--|

|            |           |                          | LOW    | MID                                          | HIGH   |  |

| 5          | OSCHIGHIN |                          |        |                                              | 2.3 V  |  |

| 6          | OSCHIGOUT |                          |        |                                              | 2.25 V |  |

| 7          | OSCHIGOUT | 6 1 7                    |        |                                              | 2.25 V |  |

| 8          | OSCHIGHIN | 5 8                      |        |                                              | 2.3 V  |  |

| 9          | VCC       | Supply voltage           | 3.3 V  | 3.3 V                                        | 3.3 V  |  |

| 10         | SAWOUT    |                          | 1.65 V | 1.65 V                                       | 1.65 V |  |

| 11         | SAWOUT    | 10, 11                   | 1.65 V | 1.65 V                                       | 1.65 V |  |

| 12         | GND       |                          | 0.0 V  | 0.0 V                                        | 0.0 V  |  |

| 13         | IFIN      |                          | 2.64 V | 2.64 V                                       | 2.64 V |  |

| 14         | IFIN      | 13 14                    | 2.64 V | 2.64 V                                       | 2.64 V |  |

| Pin<br>No. | Symbol      | Equivalent I/O Schematic | Averag | oltage<br>.3V |       |

|------------|-------------|--------------------------|--------|---------------|-------|

|            |             |                          | LOW    | MID           | HIGH  |

| 15         | IFAMPAGC    | 15                       | n.a.   | n.a.          | n.a.  |

| 16         | IFOUT       |                          | 1.6 V  | 1.6 V         | 1.6 V |

| 17         | IFOUT       | 16                       | 1.6 V  | 1.6 V         | 1.6 V |

| 18         | VT          |                          | VT     | VT            | VT    |

| 19         | CP          | 18                       | 1.7 V  | 1.7 V         | 1.7 V |

| 20         | VDD         | Supply voltage           | 3.3 V  | 3.3 V         | 3.3 V |

| 21         | DC/DC_GND   |                          | 0.0 V  | 0.0 V         | 0.0 V |

| 22         | DC/DC Clock | 22                       | n.a.   | n.a.          | n.a.  |

| Pin<br>No. | Symbol      | Equivalent I/O Schematic | Average DC voltage at V <sub>CC</sub> = 3.3V |       |       |

|------------|-------------|--------------------------|----------------------------------------------|-------|-------|

|            |             |                          | LOW                                          | MID   | HIGH  |

| 23         | XTAL Buffer | 23                       |                                              |       |       |

| 24         | XTAL Out    |                          | 0.9 V                                        | 0.9 V | 0.9 V |

| 25         | XTAL In     | 25                       | 0.9 V                                        | 0.9 V | 0.9 V |

| 26         | Busmode     | 26                       | n.a.                                         | n.a.  | n.a.  |

| 27         | CAS/EN      | 27 V <sub>ref</sub>      | n.a.                                         | n.a.  | n.a.  |

| Pin<br>No. | Symbol       | Equivalent I/O Schematic | Avera<br>at                                    | Average DC voltage at V <sub>CC</sub> = 3.3V   |                                                |  |

|------------|--------------|--------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|--|

|            |              |                          | LOW                                            | MID                                            | HIGH                                           |  |

| 28         | SCL          | 28                       | n.a.                                           | n.a.                                           | n.a.                                           |  |

| 29         | SDA          | 29                       | n.a.                                           | n.a.                                           | n.a.                                           |  |

| 30         | RFAGC Buffer |                          | 3.2 V                                          | 3.2 V                                          | 3.2 V                                          |  |

| 31         | RFAGC        | 31<br>disable            | 3.2 V                                          | 3.2 V                                          | 3.2 V                                          |  |

| 32         | P0           | -AL                      | 0 V or<br>V <sub>CC</sub> -<br>V <sub>CE</sub> | 0 V or<br>V <sub>CC</sub> -<br>V <sub>CE</sub> | 0 V or<br>V <sub>CC</sub> -<br>V <sub>CE</sub> |  |

| 33         | P1           | 32, 33                   | 0 V or<br>V <sub>CC</sub> -<br>V <sub>CE</sub> |                                                | 0 V or<br>V <sub>CC</sub> -<br>V <sub>CE</sub> |  |

| Pin<br>No. | Symbol  | Equivalent I/O Schematic | Average DC voltage at V <sub>CC</sub> = 3.3V |                 |                 |

|------------|---------|--------------------------|----------------------------------------------|-----------------|-----------------|

|            |         |                          | LOW                                          | MID             | HIGH            |

| 34         | P2, VRF | 34                       | VRF                                          | VRF             | VRF             |

| 35         | SAWIN   |                          | V <sub>cc</sub>                              | $V_{CC}$        | V <sub>CC</sub> |

| 36         | SAWIN   | 35                       | V <sub>CC</sub>                              | V <sub>CC</sub> | V <sub>CC</sub> |

| 37         | MIXOUT  |                          | V <sub>CC</sub>                              | $V_{CC}$        | V <sub>CC</sub> |

| 38         | MIXOUT  | 37 38 Oscillator         | V <sub>CC</sub>                              | V <sub>CC</sub> | V <sub>CC</sub> |

| 39         | n. c.   |                          |                                              |                 |                 |

| 40         | n. c.   |                          |                                              |                 |                 |

| 41         | n. c.   |                          |                                              |                 |                 |

| 42         | RFGND   | IF ground                | 0.0 V                                        | 0.0 V           | 0.0 V           |

| Pin<br>No. | Symbol      | Equivalent I/O Schematic     | Average DC voltage at V <sub>CC</sub> = 3.3V |       |       |

|------------|-------------|------------------------------|----------------------------------------------|-------|-------|

|            |             |                              | LOW                                          | MID   | HIGH  |

| 43         | LOWIN       | 43                           | 2                                            |       |       |

| 44         | MIDIN       |                              |                                              | 1     |       |

| 45         | MIDIN       | 44 - 45                      |                                              | 1     |       |

| 46         | HIGHIN      |                              |                                              |       | 1     |

| 47         | HIGHIN      | 46 47                        |                                              |       | 1     |

| 49         | GND package | Exposed pad ground (Die pad) | 0.0 V                                        | 0.0 V | 0.0 V |

## 3.3 Functional Block Diagram

Figure 2 Block Diagram TUA 6045-2 in VQFN-48 package

## 3.4 Circuit Description

#### 3.4.1 Mixer-Oscillator-block, SAW filter driver

The mixer-oscillator block includes three balanced mixers (one mixer with an unbalanced high-impedance input and two mixers with a balanced low-impedance input), two 2-pin asymmetrical oscillators for the LOW and the MID band, one 4-pin symmetrical oscillator for the HIGH band, a reference voltage, and a band switch.

Filters between tuner input and IC separate the TV frequency signals into three bands. The band switching in the tuner front-end is done by using three PNP port outputs. In the selected band, the signal passes through a tuner input stage with a MOSFET amplifier, a double-tuned bandpass filter and is finally fed to the mixer input of the IC. The impedance of the mixer at LOW band has high ohmic, while MID or HIGH band has a low ohmic input. The input signal is mixed there with the signal from the activated on chip oscillator to the IF frequency.

The IF is filtered by means of an external SAW filter (Surface Acoustic Waves filter) in between the 2 mixer output pins and the 2 input pins of the following SAW filter driver. The SAW filter driver has a low output impedance to drive the SAW filter directly.

#### 3.4.2 RF AGC

The RF AGC stage combines a wide band and a narrow band detection. The wide band detector (WB) detects the input signal directly at the RF input for each band. The narrow band detector (NB) detects the level of the SAW filter driver output signal. If both detected levels are below the RF AGC take-over points, a external capacity will be charged with the source current of 300 nA or 9  $\mu\text{A}$  (release current). If one of the detected levels is above the RF AGC take-over points, the external capacity will be discharged with the sink current of 100  $\mu\text{A}$  (attack current). The integrated current generates an AGC voltage for gain control of the tuners input transistors. The AGC take-over and the time constant are selectable by the  $l^2\text{C}$  bus as shown in Table 17 "Subaddress 03H, AGC control and IF Signal Processing Control" on Page 52.

An integrated RF AGC buffer allows to monitor the AGC voltage without any influence on the tuner gain control. This buffer can be disabled as shown in **Table 16**"Subaddress 02H, Reference Divider R and Crystal Oscillator Control" on Page 50

## 3.4.3 IF AGC amplifier

Coming out of the SAW filter the IF signal is sent through a VGA (Variable Gain Amplifier) which will set the differential IF output signal to the desired level (preferably 1 Vpp). The gain of the VGA is determined by the DC-voltage at pin IFAMPAGC

### 3.4.4 PLL block, XTAL oscillator

The VCO frequency  $f_{OSC}$  is stabilized by a digital CMOS PLL (Phase Locked Loop, Frequency Synthesizer). The oscillator signal is internally DC-coupled as a differential signal to the programmable divider input. The signal subsequently passes through a programmable divider (N) and then the divided VCO signal:

$$f_{div} = \frac{f_{OSC}}{N}, (N = 240...65535)$$

is compared in a digital frequency/phase detector (PD, frequency detector) with a programmable reference frequency:

$$f_{ref} = \frac{f_{XTAL}}{R}, (R = 2...1023)$$

which is derived from a quartz reference  $f_{XTAL}$  divided by a programmable reference divider (R).

The phase detector has a linear operating range without a dead zone for very small phase deviations. A programmable ABL pulse width (Anti BackLash) works against the delay of the charge pump cell. The selectable ABL pulse width values have been implemented for test purpose only and have no performance effects.

The phase detector has two outputs (up & down) that drive two current sources of opposite polarity as charge pump (CP). If the negative edge of the divided VCO signal appears prior to the negative edge of the reference signal, the positive current source ( $I_{source}$ ) pulses for the duration of the phase difference. In the reverse case the negative current source ( $I_{sink}$ ) pulses. If the two signals are in phase (PLL is locked), the integrated charge pump current is approximately zero. In case of active closed loop control the charge pump provides programmable output current drive capability to optimize the loop requirements. The charge pump currents are programmable from 0 to 1.125 mA in steps of 75  $\mu$ A.

The PLL contains an integrated lock detector. A lock-in flag is set when the loop is locked. It can be read by the processor via the common I<sup>2</sup>C/3-Wire bus.

The crystal oscillator (XTAL) is an unbalanced Pierce oscillator which operates in parallel resonance with quartz crystals from 4...16 MHz. By programming it's possible to pass the oscillator frequency  $f_{\text{XTAL}}$  through a divider stage to a buffered output pin or to use an external quartz clock for the reference oscillator via a switchable preamplifier for test purpose only.

#### 3.4.5 Bus Interface

The programming of the CMOS frequency synthesizer is done via a combined serial  $l^2C/3$ -Wire bus interface. The choice of the desired bus is made by a bus mode select signal at pin BUSMODE.

In  $I^2$ C-bus mode four different chip addresses can be set by appropriate DC levels at pin CAS (Chip Address Select), while in 3-Wire mode the chip is addressed by a low active enable signal at pin EN.

The content of the bus telegram (serial data format) is controlled by software programming and assigned to the registers of the functional units according to the several sub addresses. The most significant bit (MSB) of the data protocol is shifted in first.

The clock is generated by the processor (input pin SCL/Clock), while pin SDA/Data functions as an input or an output (open drain, external pull-up resistor) depending on the direction of the data (write or read mode). Both inputs have schmitt-trigger circuits with hysteresis and furthermore a low-pass characteristic, which suppress a certain noise level on the bus lines and enhance so the noise immunity of the combi-bus.

A detailed description of the chip address organization in I<sup>2</sup>C-mode as well as the used sub addresses of the data registers is given in **chapter 5.2 "Bus Interface" on page 41** - and the programmable I<sup>2</sup>C/3-Wire bus data format is shown in **chapter 5.3 "Bus Data Format" on page 43**.

## 3.4.6 DC/DC clock output

To drive a bipolar NPN switching transistor of an external DC/DC converter directly, a programmable DC/DC clock generator is integrated. The clock frequency and the duty cycle of the DC/DC clock generator can be set over the I<sup>2</sup>C/3-Wire bus as shown in **Table 18 "Subaddress 04H, DC-DC Converter" on Page 54**.

## 3.4.7 Power-on Reset, Stand-by Condition

While applying the supply voltage, integrated power-on reset circuits ensure a defined state after initial power-up. The required programming data will be set to default values.

When  $V_{CC}$  fall below approximately 1.2 V (typ.) the power-on resets go active and tie all write data registers to their power-on defaults (= power-down reset). While power-on reset is active no programming is possible.

The power-on flags (POFx) are set at power-on and when  $V_{VCCx}$  falls below appr. 1.2 V (typ.). They will be reset at the end of a READ operation of the status register.

By programmable stand-by control bits it's possible to reduce the current consumption of the IC up to 99%. In the full stand-by mode only bus interface is staying active and the current consumption is reduced below 200  $\mu$ A. After power-on reset only bus interface and XTAL-oscillator with bandgap are active and the current consumption is about 2.6 mA (typ.).

## 3.4.8 IF switch, Loop thru

For the alignment procedure of the tuner module two programmable switches are integrated to bypass the bandpass, the SAW driver and the SAW filter. The first switch called "IF switch" can switch between the mixer output signal and the bandpass output signal. The second switch called "Loop thru" can switch between the signal after the first stage of the IF AGC amplifier and the SAW filter output signal.

Figure 3 Functional Block Diagram of IF switch and Loop thru