Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

| Document Title | TVL-55682D101U-LW-I-AAN F | Page No.   | 1/33       |          |    |

|----------------|---------------------------|------------|------------|----------|----|

| Document No.   |                           | Issue Date | 2013/02/21 | Revision | 00 |

# **Product Information**

To:

Product Name: TVL-55682D101U-LW-I-AAN

Document Issue Date: 2013/02/21

Note: 1. Please contact Kyocera Display before designing your product based on this product.

2. The information contained herein is presented merely to indicate the characteristics and performance of our products. No responsibility is assumed by KYOCERA DISPLAY for any intellectual property claims or other problems that may result from application based on the module described herein.

KYOCERA DISPLAY CORPORATION 5-7-18, Higashi Nippori, Arakawa-ku, Tokyo, Japan 116-0014

| Document Title | TVL-55682D101U-LW-I-AAN F | Page No.   | 2/33       |          |    |

|----------------|---------------------------|------------|------------|----------|----|

| Document No.   |                           | Issue Date | 2013/02/21 | Revision | 00 |

#### FQ-7-30-0-009-02C

| Revision | Date       | Page | Old Description | New Description | Remark |

|----------|------------|------|-----------------|-----------------|--------|

| 00       | 2011/05/10 | All  |                 | First issued    |        |

|          |            |      |                 |                 |        |

|          |            |      |                 | C               |        |

|          |            |      |                 |                 |        |

|          |            |      |                 |                 |        |

|          |            |      |                 |                 |        |

|          |            |      |                 |                 |        |

|          |            |      |                 |                 |        |

|          |            |      |                 |                 |        |

| Document Title | TVL-55682D101U-LW-I-AAN F | Page No.   | 3/33       |          |    |

|----------------|---------------------------|------------|------------|----------|----|

| Document No.   |                           | Issue Date | 2013/02/21 | Revision | 00 |

### **Contents**

| 1 | GENERAL DESCRIPTIONS       | Δ            |

|---|----------------------------|--------------|

|   |                            |              |

| 2 | ABSOLUTE MAXIMUM RATINGS   | <del>7</del> |

| 3 | ELECTRICAL SPECIFICATION   | 8            |

| 4 | OPTICAL CHARACTERISTICS    | 17           |

| 5 | MECHANICAL CHARACTERISTICS | 21           |

| 6 | PACKAGE SPECIFICATION      | 24           |

| 7 | LOT MARK                   | 25           |

| 8 | GENERAL PRECAUTION         | 26           |

| 9 | EDID DATA STRUCTURE        | 29           |

| Document Title | TVL-55682D101U-LW-I-AAN F | Page No.   | 4/33       |          |    |

|----------------|---------------------------|------------|------------|----------|----|

| Document No.   |                           | Issue Date | 2013/02/21 | Revision | 00 |

### 1 General Descriptions

#### 1.1 Introduction

The TVL-55682AAN is a Color Active Matrix Thin Film Transistor (TFT) Liquid Crystal Display (LCD) module, which uses amorphous Silicon TFT as a switching device. It is composed of a TFT LCD panel, a timing controller, voltage reference, common voltage, column driver, and row driver circuit. This TFT LCD has a 10.1-inch (diagonally measured) active display area with WSVGA resolution (1,024 vertical by 600 horizontal pixel array).

#### 1.2 Features

- ■10.1" TFT LCD Panel

- ■LED Light-bar Backlight System

- Supports WSVGA (V:1,024 lines, H:600 pixels) Resolution

- ■Compatible with RoHS Standard

1.3 Product Summary

| Items                        | Specifications                      | Unit               | Remark            |

|------------------------------|-------------------------------------|--------------------|-------------------|

| Screen Diagonal              | 10.1                                | inch               |                   |

| Active Area                  | 222.72(H) x 125.28(V)               | mm                 |                   |

| Pixels(H x V)                | 1,024 (x3) x 600                    | -                  |                   |

| Pixel Pitch                  | 0.2175(H) x 0.2088(V)               | mm                 |                   |

| Pixel Arrangement            | R.G.B. Vertical Stripe              | -                  |                   |

| Display Mode                 | TN Mode, Normally White             | -                  |                   |

| White Luminance              | 200 (Typ.)                          | cd/ m <sup>2</sup> | 5 Points Average, |

| writte Luminance             | 200 (Typ.)                          | Cu/ III            | 20mA per LED      |

| Contrast Ratio               | 500 (Typ.)                          | -                  |                   |

| Response Time                | 8 (Typ.)                            | ms                 |                   |

| View Angle(L/R/U/D)          | 45/45/15/35 (Typ.)                  | -                  |                   |

| Input Voltage                | +3.3 (Typ.)                         | V                  |                   |

| Power Consumption            | 2.4                                 | Watt               | Black Pattern     |

| Module Weight                | 190 (Max.)                          | g                  |                   |

| Outline Dimension(H x V x D) | 235.5(H) x 143.5(V) x 5.2(D) (Max.) | mm                 |                   |

| Electrical Interface (Logic) | LVDS                                | -                  |                   |

| Support Color                | 262 K                               | -                  |                   |

| NTSC                         | 45 (Typ.)                           | %                  |                   |

| Optimum Viewing Direction    | 6 o'clock                           | -                  | _                 |

| Surface Treatment            | Anti-Glare                          | -                  |                   |

KYOCERA DISPLAY CORPORATION 5-7-18, Higashi Nippori, Arakawa-ku, Tokyo, Japan 116-0014

| Document Title | TVL-55682D101U-LW-I-AAN F | Page No.   | 5/33       |          |    |

|----------------|---------------------------|------------|------------|----------|----|

| Document No.   |                           | Issue Date | 2013/02/21 | Revision | 00 |

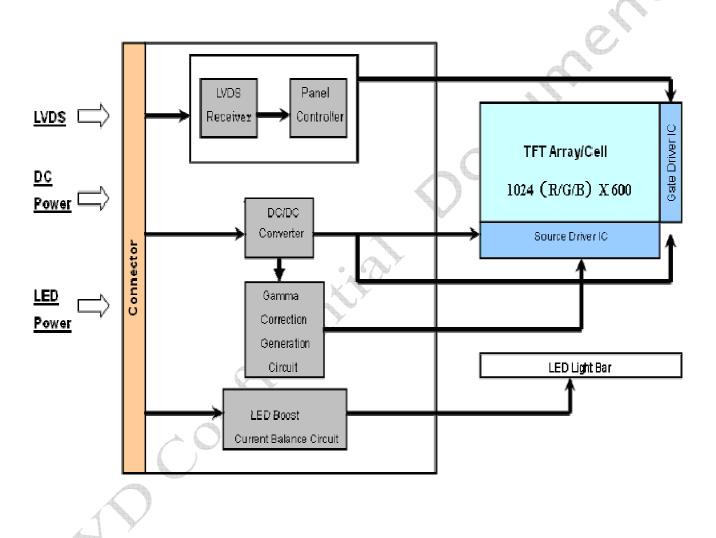

#### 1.4 Functional Block Diagram

Figure 1 shows the functional block diagram of the LCD module.

Figure 1 Block Diagram

| Document Title | TVL-55682D101U-LW-I-AAN P | Page No.   | 6/33       |          |    |

|----------------|---------------------------|------------|------------|----------|----|

| Document No.   |                           | Issue Date | 2013/02/21 | Revision | 00 |

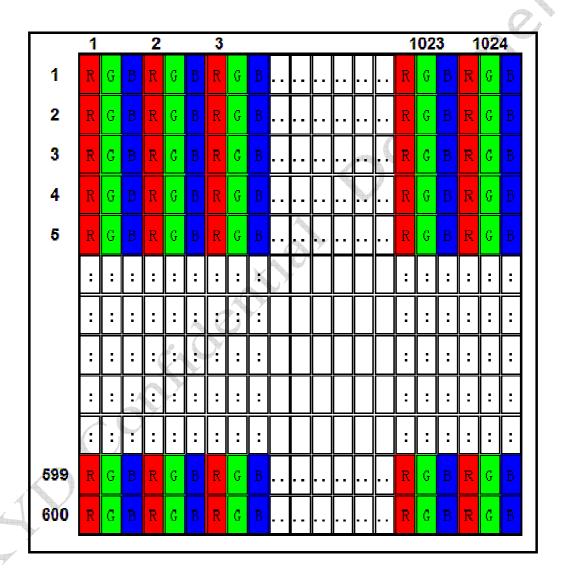

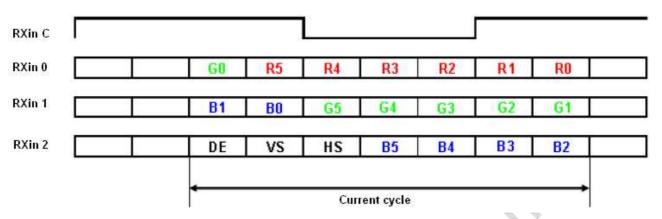

#### 1.5 Pixel Format Image

Figure 2 shows the relationship of the input signals and LCD pixel format image.

**Figure 2 Pixel Format**

KYOCERA DISPLAY CORPORATION 5-7-18, Higashi Nippori, Arakawa-ku, Tokyo, Japan 116-0014

| Document Title | TVL-55682D101U-LW-I-AAN P | Page No.   | 7/33       |          |    |

|----------------|---------------------------|------------|------------|----------|----|

| Document No.   |                           | Issue Date | 2013/02/21 | Revision | 00 |

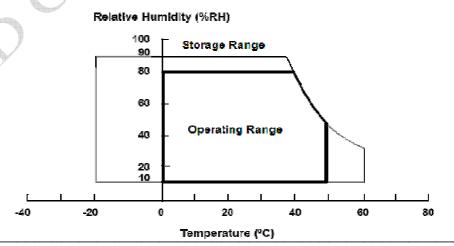

#### 2 Absolute Maximum Ratings

The followings are maximum values which, if exceeded, may cause faulty operation or damage to the LCD module.

Table 1

| Item                  | Symbol      | Min. | Max.     | Unit         | Conditions              |  |

|-----------------------|-------------|------|----------|--------------|-------------------------|--|

| Supply Voltage        | $V_{DD}$    | -0.3 | 4.0      | V            | -                       |  |

| Supply V_LED Voltage  | $V_{\_LED}$ | 5    | 21       | V            | -                       |  |

| Input Signal          | -           | -0.3 | 2.7      | V            | LVDS Signals            |  |

| Operating Temperature | TOP         | 0    | 50       | $^{\circ}$   | Note(3)                 |  |

| Operating Humidity    | HOP         | 10   | 80       | %RH          | Note(3)                 |  |

| Storage Temperature   | TST         | -20  | 60       | $^{\circ}$ C | Note(3)                 |  |

| Storage Humidity      | HST         | 10   | 90       | %RH          | Note(3)                 |  |

| Vibration             | Level       | -    | 1.5      | G            | 30min. for X, Y, Z axis |  |

|                       | Bandwidth   | - 💉  | 10~500Hz | Hz           |                         |  |

| Shock                 | Level       |      | 220      | G            | Half Sine Waveform, 2ms |  |

| LED Current           | I_LED       |      | 20.5     | mA           | Per LED                 |  |

#### Note

- (1)Maximum Wet-Bulb should be 39℃ and No condensation.

- (2)When you apply the LCD module for OA system, please make sure to keep the temperature of LCD module under 60  $^{\circ}$ C.

- (3) Storage / Operating temperature & humidity:

KYOCERA DISPLAY CORPORATION 5-7-18, Higashi Nippori, Arakawa-ku, Tokyo, Japan 116-0014

| Document Title | TVL-55682D101U-LW-I-AAN F | Page No.   | 8/33       |          |    |

|----------------|---------------------------|------------|------------|----------|----|

| Document No.   |                           | Issue Date | 2013/02/21 | Revision | 00 |

### 3 Electrical Specification

### 3.1 Electrical Characteristics

**Table 2 Electrical Characteristics**

| Symbol             | Parame              | eter       | Min.   | Тур. | Max. | Units | Condition           |

|--------------------|---------------------|------------|--------|------|------|-------|---------------------|

| $V_{DD}$           | Logic/LCD Driv      | e Voltage  | 3      | 3.3  | 3.6  | ٧     | Note (1)            |

| I <sub>DD</sub>    | VDD Cui             | rent       | -      | 160  | -    | mA    | Black Pattern, 60Hz |

| P <sub>DD</sub>    | VDD Po              | wer        | -      | -    | 0.53 | W     | Black Pattern, 60Hz |

| Irush              | Rush Cu             | rrent      | -      | -    | 2    | Α     | Note (2)            |

| V ro               | Allowable Logic     | /LCD Drive |        |      | 300  | mVp-p |                     |

| V <sub>DD</sub> rp | Ripple Voltage      |            | -      | -    | 300  | шур-р | -                   |

| $V_{LED}$          | LED In              | out        | 5      | 12   | 21   | V     | -                   |

| $V_{F}$            | LED Forward Voltage |            | 2.95   | 3.3  | 3.4  | ٧     | -                   |

| I <sub>F</sub>     | LED Forward         | l Current  | 19.5   | 20   | 20.5 | mA    | -                   |

| $P_{LED}$          | LED Power Co        | nsumption  | -      | -    | 1.87 | W     | Note(3)             |

| $L_T$              | LED Life            | Time       | 10,000 | 20   | -    | Hours | Note(4)             |

| V                  | PWM Signal          | High       | 2      | 3.3  | 3.6  | ٧     |                     |

| $V_{PWM\_EN}$      | Voltage             | Low        | 0      | -    | 0.5  | ٧     | -                   |

| F <sub>PWM</sub>   | Output PWM F        | requency   |        | 200  | 1K   | Hz    | -                   |

| V                  | LED Enable          | High       | 2      | 3.3  | 3.6  | V     |                     |

| V_LED_EN           | Voltage             | Low        | 0      | -    | 0.5  | V     | -                   |

| PWM                | PWM Duty            | Ratio      | 5      | -    | 100  | %     | -                   |

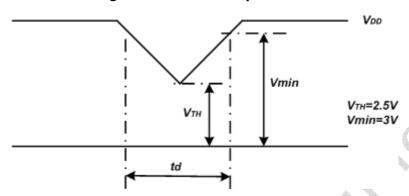

Note: (1)V<sub>DD</sub> Power Dip Condition

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 9/33 |

|----------------|-----------------------------------------------|------------|------------|----------|------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00   |

Figure 3 V<sub>DD</sub> Power Dip

If  $V_{TH} < V_{DD} \le V_{min}$  and  $t_d \le 10ms$ , our panel must revive automatically when the voltage returns to normal.

(2)Measure Condition

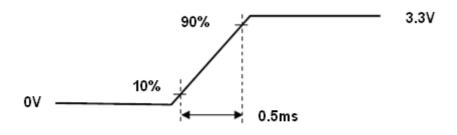

Figure 4 V<sub>DD</sub> rising time

#### VDD rising time

- (3)  $P_{LED}$  is calculation value for reference.  $P_{LED}$  =24 x  $V_F$  (Normal Distribution) x  $I_F$  (Normal Distribution) / Efficiency

- (4) The lifetime of LED is defined as the time when LED packages continue to operate under the conditions at  $Ta = 25^{\circ}C$  and  $I_{F}= 20$  mA (per chip) until the brightness becomes  $\leq 50\%$  of its original value.

- (5)All values are measured at condition of  $V_{LED}$  =12V and Ta=25°C.

YOCERA DISPLAY CORPORATION

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 10/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

#### 3.2 Interface Connector

### **Table 3 Connector Name / Designation**

| Manufacturer                  | I-PEX (or equivalent) |  |  |  |  |

|-------------------------------|-----------------------|--|--|--|--|

| Mating Receptacle/Part Number | 20453-040T(I-PEX)     |  |  |  |  |

### **Table 4 Signal Pin Assignment**

| Pin# | Signal Name          | Description                                   | Remarks                    |

|------|----------------------|-----------------------------------------------|----------------------------|

| 1    | GND                  | Ground                                        |                            |

| 2    | $V_{DD}$             | Power Supply 3.3V (Typ.)                      |                            |

| 3    | $V_{DD}$             | Power Supply 3.3V (Typ.)                      |                            |

| 4    | V <sub>EDID</sub>    | EDID +3.3V Power                              |                            |

| 5    | NC                   | Not Connected(Reserve)                        | LCD panel self test enable |

| 6    | CLK_ <sub>EDID</sub> | EDID Clock Input                              |                            |

| 7    | DAT_ <sub>EDID</sub> | EDID Data Input                               |                            |

| 8    | RXin0-               | -LVDS Differential Data Input(R0-R5,G0)       |                            |

| 9    | RXin0+               | +LVDS Differential Data Input(R0-R5,G0)       |                            |

| 10   | GND                  | Ground                                        |                            |

| 11   | RXin1-               | -LVDS Differential Data Input(G1-G5,B0-B1)    |                            |

| 12   | RXin1+               | +LVDS Differential Data Input(G1-G5,B0-B1)    |                            |

| 13   | GND                  | Ground                                        |                            |

| 14   | RXin2-               | -LVDS Differential Data Input(B2-B5,HS,VS,DE) |                            |

| 15   | RXin2+               | +LVDS Differential Data Input(B2-B5,HS,VS,DE) |                            |

| 16   | GND                  | Ground                                        |                            |

| 17   | CLKN-                | -LVDS Differential Clock Input                |                            |

| 18   | CLKN+                | +LVDS Differential Clock Input                |                            |

| 19   | NC                   | Not Connected(Reserve)                        |                            |

| 20   | NC                   | Not Connected(Reserve)                        |                            |

| 21   | NC                   | Not Connected(Reserve)                        |                            |

| 22   | GND                  | Ground-Shield                                 |                            |

| 23   | NC                   | Not Connected(Reserve)                        |                            |

| 24   | NC                   | Not Connected(Reserve)                        |                            |

| 25   | GND                  | Ground-Shield                                 |                            |

| 26   | NC                   | Not Connected(Reserve)                        |                            |

KYOCERA DISPLAY CORPORATION 5-7-18, Higashi Nippori, Arakawa-ku, Tokyo, Japan 116-0014

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 11/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

| 27 | NC                  | Not Connected(Reserve)        |  |

|----|---------------------|-------------------------------|--|

| 28 | GND                 | Ground-Shield                 |  |

| 29 | NC                  | Not Connected(Reserve)        |  |

| 30 | NC                  | Not Connected(Reserve)        |  |

| 31 | $V_{LED\_GND}$      | LED Ground                    |  |

| 32 | $V_{LED\_GND}$      | LED Ground                    |  |

| 33 | $V_{LED\_GND}$      | LED Ground                    |  |

| 34 | NC                  | Not Connected(Reserve)        |  |

| 35 | V <sub>PWM_EN</sub> | System PWM Logic Input Level  |  |

| 36 | $V_{LED_{EN}}$      | LED Enable Input Level(+3.3V) |  |

| 37 | NC                  | Not Connected(Reserve)        |  |

| 38 | $V_{LED}$           | LED Power Supply 5-21V        |  |

| 39 | $V_{LED}$           | LED Power Supply 5-21V        |  |

| 40 | $V_{LED}$           | LED Power Supply 5-21V        |  |

Note: All input signals shall be at low or Hi-Z state when  $V_{DD}$  is off.

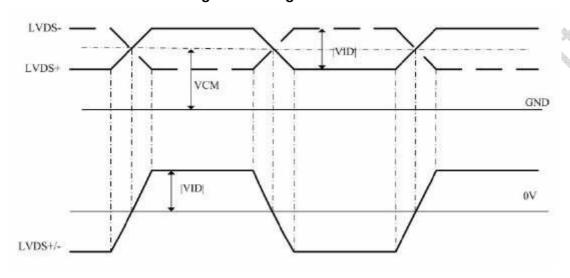

#### 3.3 LVDS Receiver

### 3.3.1 Signal Electrical Characteristics For LVDS Receiver

The built-in LVDS receiver is compatible with (ANSI/TIA/TIA-644) standard.

**Table 5 LVDS Receiver Electrical Characteristics**

| Parameter                            | Symbol          | Min.       | Тур. | Max.       | Unit | Conditions             |

|--------------------------------------|-----------------|------------|------|------------|------|------------------------|

| Differential Input High Threshold    | $V_{th}$        | -          | -    | +100       | mV   | V <sub>cm</sub> =+1.2V |

| Differential Input Low Threshold     | $V_{tI}$        | -100       | -    | -          | mV   | V <sub>cm</sub> =+1.2V |

| Magnitude Differential Input Voltage | V <sub>id</sub> | 100        | -    | 600        | mV   |                        |

| Common Mode Voltage                  | V <sub>cm</sub> | Vid/2 +0.6 | 1.2  | 1.8- Vid/2 | V    |                        |

| Common Mode Voltage Offset           | $\Delta V_{cm}$ | -          | -    | 50         | mV   | V <sub>cm</sub> =+1.2V |

### Note:

- (1)Input signals shall be at low or Hi-Z state when  $V_{DD}$  is off.

- (2)All electrical characteristics for LVDS signal are defined and shall be measured at the interface connector of LCD.

- (3)All values are measured at condition of  $V_{DD}$  =3.3V and Ta=25°C.

KYOCERA DISPLAY CORPORATION 5-7-18, Higashi Nippori, Arakawa-ku, Tokyo, Japan 116-0014

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 12/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

**Figure 5 Voltage Definitions**

Figure 6 Measurement System

Figure 7 Data mapping

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 13/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

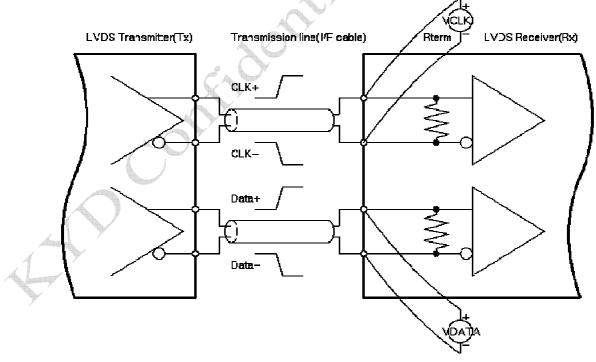

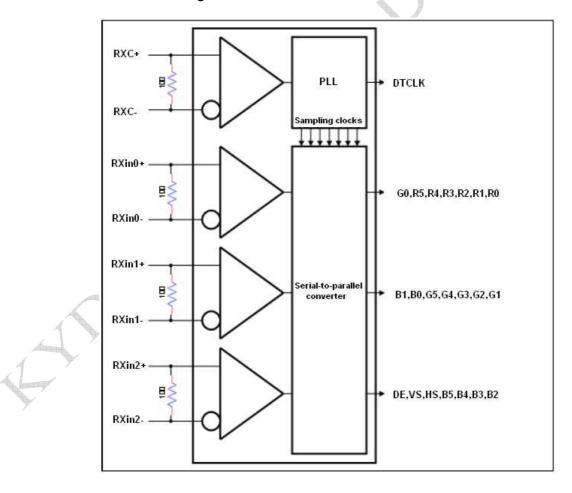

#### 3.3.2 LVDS Receiver Internal Circuit

Figure 8 LVDS Receiver Internal Circuit shows the internal block diagram of the LVDS receiver. This LCD module equips termination resistors for LVDS link.

**Figure 8 LVDS Receiver Internal Circuit**

KYOCERA DISPLAY CORPORATION 5-7-18, Higashi Nippori, Arakawa-ku, Tokyo, Japan 116-0014

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 14/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

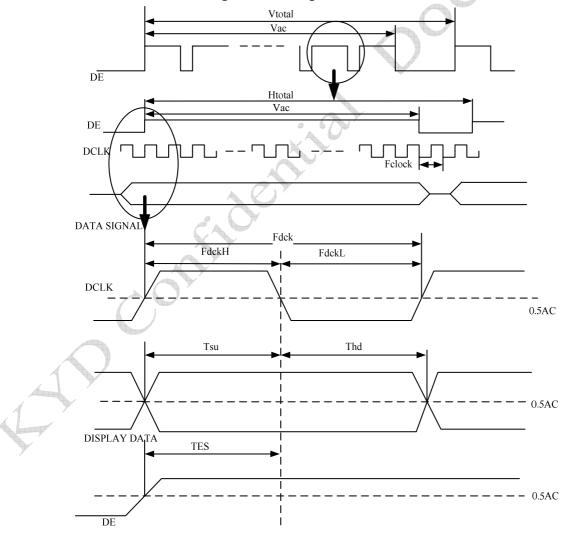

### 3.4 Interface Timings

### **Table 6 Interface Timings**

|                              |                    | _      |       |       |       |

|------------------------------|--------------------|--------|-------|-------|-------|

| Parameter                    | Symbol             | Unit   | Min.  | Тур.  | Max.  |

| LVDS Clock Frequency(single) | F <sub>dck</sub>   | MHz    | 44.4  | 50.4  | 65.2  |

| H Total Time                 | H <sub>total</sub> | Clocks | 1,320 | 1,344 | 1,362 |

| H Active Time                | H <sub>ac</sub>    | Clocks | 1,024 | 1,024 | 1,024 |

| V Total Time                 | V <sub>total</sub> | Lines  | 612   | 625   | 638   |

| V Active Time                | V <sub>ac</sub>    | Lines  | 600   | 600   | 600   |

| Frame Rate                   | V <sub>sync</sub>  | Hz     | 55    | 60    | 65    |

**Figure 9 Timing Characteristics**

KYOCERA DISPLAY CORPORATION 5-7-18, Higashi Nippori, Arakawa-ku, Tokyo, Japan 116-0014

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            | Page No. | 15/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

Note: TES is data enable signal setup time.

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            | Page No. | 16/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

### 3.5 Power ON/OFF Sequence

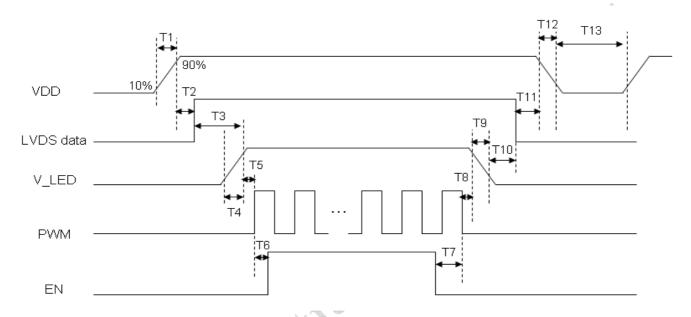

$V_{\text{DD}}$  power, interface signals, and lamp on/off sequence are showing on Figure 10. Signals shall be Hi-Z state or low level when  $V_{\text{DD}}$  is off.

Figure 10

**Table 7 Power Sequencing Requirements**

| Parameter                                       | Symbol | Min. | Typ. | Max. | Unit |

|-------------------------------------------------|--------|------|------|------|------|

| V <sub>DD</sub> Rising Time                     | T1     | 0.5  | -    | 10   | ms   |

| V <sub>DD</sub> Good to Signal Valid            | T2     | 30   | -    | 90   | ms   |

| Signal Valid to Backlight on                    | Т3     | 200  | -    | -    | ms   |

| Backlight Power on Time                         | T4     | 0.5  | -    | -    | ms   |

| Backlight V <sub>DD</sub> Good to System PWM on | T5     | 10   | -    | -    | ms   |

| System PWM on to Backlight Enable on            | T6     | 10   | -    | -    | ms   |

| Backlight Enable off to System PWM off          | T7     | 0    | -    | -    | ms   |

| System PWM off to B/L Power Disable             | Т8     | 10   | -    | -    | ms   |

| Backlight Power off Time                        | T9     | -    | 10   | 30   | ms   |

| Backlight off to Signal Disable                 | T10    | 200  | -    | -    | ms   |

| Signal Disable to Power Down                    | T11    | 0    | -    | 50   | ms   |

| V <sub>DD</sub> Falling Time                    | T12    | -    | 10   | 30   | ms   |

| Power off                                       | T13    | 500  | -    | -    | ms   |

KYOCERA DISPLAY CORPORATION 5-7-18, Higashi Nippori, Arakawa-ku, Tokyo, Japan 116-0014

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 17/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

### 4 Optical Characteristics

The optical characteristics are measured under stable conditions as following notes.

**Table 8 Optical Characteristics**

|                |                | bic o option |       |       | pecificat | ion               |          |

|----------------|----------------|--------------|-------|-------|-----------|-------------------|----------|

| Item           | Condition      | Conditions   |       | Тур.  | Max.      | Unit              | Note     |

| Viewing Angle  | Horizontal     | Left         | 40    | 45    | -         | Deg.              |          |

| [degrees]      | Honzontai      | Right        | 40    | 45    | -         | Deg.              | (1) (2)  |

| K=Contrast     | Vertical       | Up           | 10    | 15    | P-        | Deg.              | (1),(2)  |

| Ratio>10       | vertical       | Down         | 30    | 35    |           | Deg.              |          |

| Contrast Ratio | Center         |              | 400   | 500   | -         | -                 | (1),(3)  |

|                | Rising         |              | -     | 3     | ı         | ms                |          |

| Response Time  | Falling        |              | •     | 5     | 1         | ms                |          |

|                | Rising + Fa    | lling        | -     | 8     | 16        | ms                | (1),(4)  |

|                | Red            | X            |       | 0.579 |           | -                 | (1)      |

|                | Red            | у            |       | 0.346 |           | -                 | (1)      |

| Color          | Green          | x            | Тур.  | 0.336 | Тур.      | -                 | (1)      |

| Chromaticity   | Green          | y O          | -0.03 | 0.560 | +0.03     | -                 | (1)      |

| (CIE1931)      | Blue           | x            |       | 0.156 |           | -                 | (1)      |

| (0121331)      | Blue           | у            |       | 0.123 |           | -                 | (1)      |

|                | White          | X            | 0.283 | 0.313 | 0.343     | -                 | (1)      |

|                | White          | у            | 0.299 | 0.329 | 0.359     | -                 | (1)      |

| White          |                |              |       |       |           |                   |          |

| Luminance      | I_LED =20.0    | mA           | 180   | 200   | -         | cd/m <sup>2</sup> | (1), (5) |

| [cd/m^2]       | <i>y</i>       |              |       |       |           |                   |          |

| Luminance      | I_LED =20mA, 1 | 3points      | 62.5  | -     | -         | _                 | (1), (6) |

| Uniformity [%] | I_LED =20mA, 5 | points       | 80.0  | -     | -         | _                 | (1), (0) |

Note: (1)Measurement Setup

KYOCERA DISPLAY CORPORATION 5-7-18, Higashi Nippori, Arakawa-ku, Tokyo, Japan 116-0014

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 18/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

measurement should be executed after lighting backlight for 15 minutes in a windless room.

LCD Module

LCD Panel

Photo meter (DMS 1140)

Light Shield Room

\*Ambient Luminance<2lux

\*Ambient Temperature 25+/-3degC

**Figure 11 Measurement Setup**

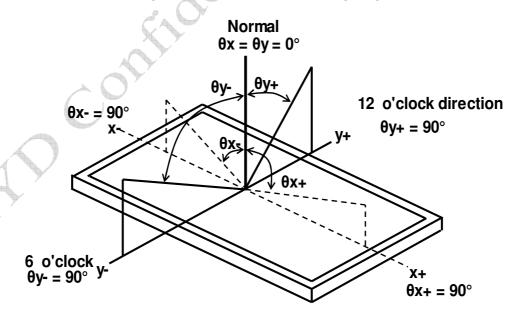

(2) Definition of Viewing Angle

**Figure 12 Definition of Viewing Angle**

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 19/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

#### (3) Definition of Contrast Ratio (CR)

The contrast ratio can be calculated by the following expression Contrast Ratio (CR) = L63 / L0

L63: Luminance of gray level 63, L0: Luminance of gray level 0

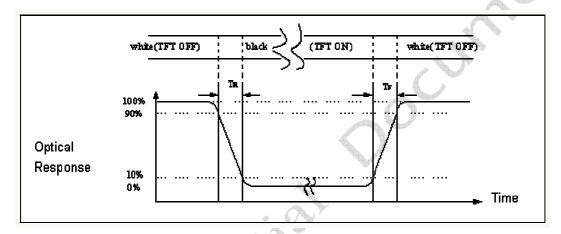

(4) Definition of Response Time (T<sub>R</sub>, T<sub>F</sub>)

**Figure 13 Definition of Response Time**

#### (5) Definition of Luminance White

Measure the luminance of gray level 63 at 5 points(Fig.14).

Center of Luminance = Y1

Average Luminance of 5 points =

$$\frac{Y_1 + Y_2 + Y_3 + Y_4 + Y_5}{5}$$

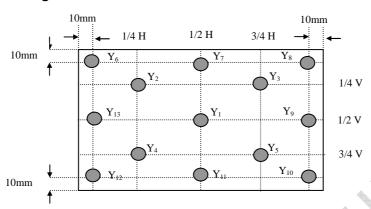

#### (6) Definition of Luminance Uniformity (Variation)

Measure the luminance of gray level 63 at 13 points.

Uniformity of 13 points =

$$\frac{\text{Min Luminance of Y1} \sim \text{Y13}}{\text{Max Luminance of Y1} \sim \text{Y13}} \times 100\%$$

Uniformity of 5 points =

$$\frac{\text{Min Luminance of Y1} \sim Y5}{\text{Max Luminance of Y1} \sim Y5} \times 100\%$$

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 20/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

Figure 14 Measurement Locations of 13 Points

CORRACIONA

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 21/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

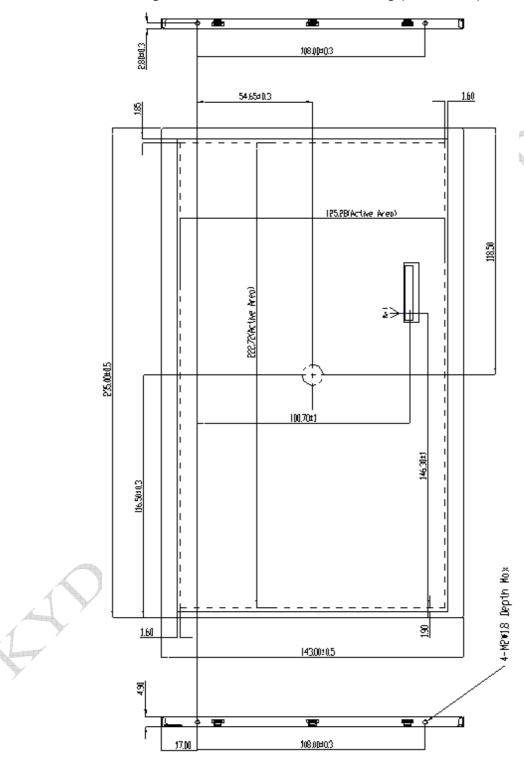

### 5 Mechanical Characteristics

Figure 15 Reference Outline Drawing (Front Side)

KYOCERA DISPLAY CORPORATION 5-7-18, Higashi Nippori, Arakawa-ku, Tokyo, Japan 116-0014

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 22/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

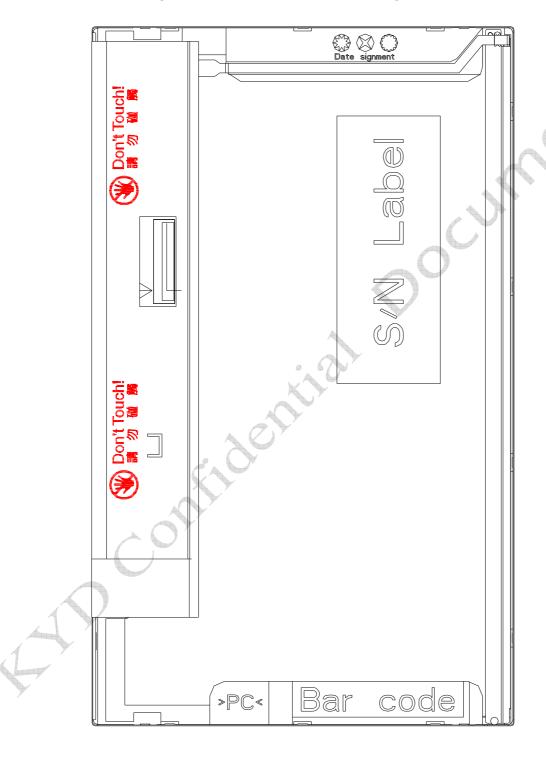

Figure 16 Reference Outline Drawing (Back Side)

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            | Page No. | 23/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

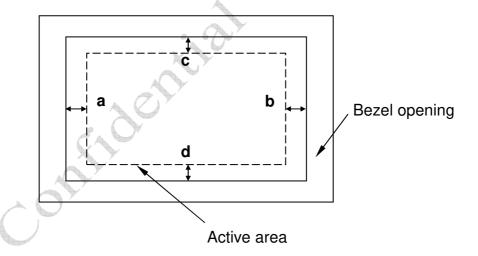

### 5.1 Dimension Specifications

Table 9

| I               | tem           | Value      | Unit |

|-----------------|---------------|------------|------|

| Width           |               | 235.00±0.5 | mm 4 |

| Height          |               | 143.00±0.5 | mm 📝 |

| Thickness(Max.) |               | 5.2        | mm   |

| Bezel Opening   | х             | 226.47±0.5 | mm   |

| Jozof opolining | Υ             | 128.48±0.5 | mm   |

| Weight(Max.)    |               | 190        | g    |

| BM Width        | a-b   &   c-d | ≤1.0       | mm   |

KYOCERA DISPLAY CORPORATION 5-7-18, Higashi Nippori, Arakawa-ku, Tokyo, Japan 116-0014

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 24/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |

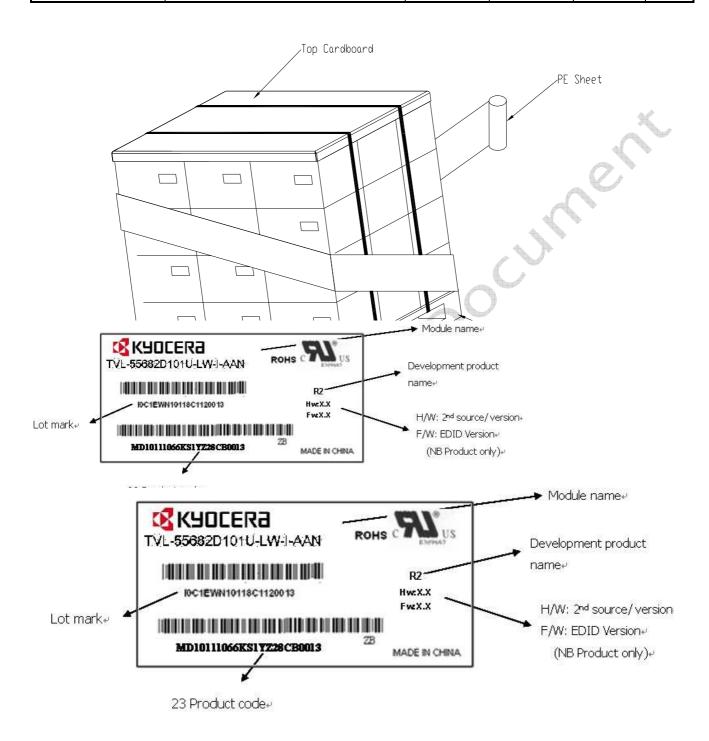

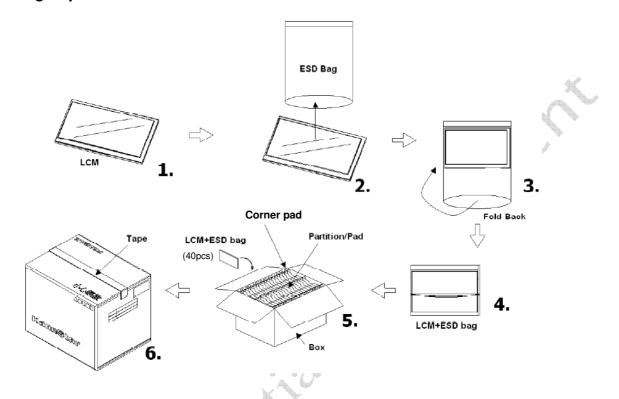

### 6 Package Specification

| Document Title | TVL-55682D101U-LW-I-AAN Product Specification |            |            |          | 25/33 |

|----------------|-----------------------------------------------|------------|------------|----------|-------|

| Document No.   |                                               | Issue Date | 2013/02/21 | Revision | 00    |