Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **Features**

- Supply Voltage 5 V

- Very Low Power Consumption 125 mW

- Very Good Image Rejection By Means of Phase Control Loop for Precise 90° Phase Shifting

- Duty-cycle Regeneration for Single-ended LO Input Signal

- Low LO Input Level -10 dBm

- LO Frequency from 70 MHz to 1 GHz

- Power-down Mode

- 25 dB Gain Control

- Very Low I/Q Output DC Offset Voltage Typically < 5 mV

### **Benefits**

- Low Current Consumption

- Easy to Implement

- Perfect Performance for Large Variety of Wireless Applications

Electrostatic sensitive device.

Observe precautions for handling.

# **Description**

The silicon monolithic integrated circuit U2794B is a quadrature demodulator manufactured using Atmel's advanced UHF technology. This demodulator features a frequency range from 70 MHz to 1000 MHz, low current consumption, selectable gain, power-down mode and adjustment-free handling. The IC is suitable for direct conversion and image rejection applications in digital radio systems up to 1 GHz such as cellular radios, cordless telephones, cable TV and satellite TV systems.

# 1000-MHz Quadrature Demodulator

U2794B

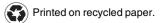

Figure 1. Block Diagram

# **Pin Configuration**

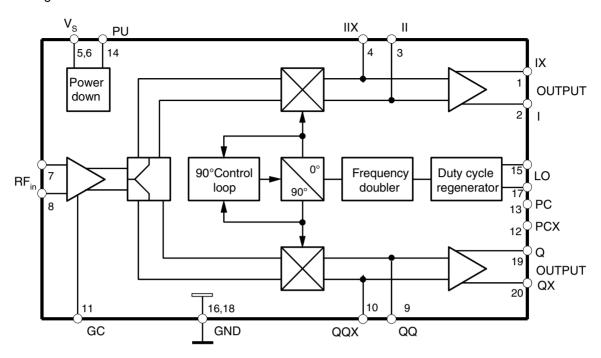

Figure 2. Pinning SSO20

# **Pin Description**

| Pin | Symbol            | Function             |

|-----|-------------------|----------------------|

| 1   | IX                | IX output            |

| 2   | I                 | I output             |

| 3   | II                | II lowpass filter I  |

| 4   | IIX               | IIX lowpass filter I |

| 5   | V <sub>S</sub>    | Supply voltage       |

| 6   | V <sub>S</sub>    | Supply voltage       |

| 7   | RF <sub>in</sub>  | RF input             |

| 8   | RFX <sub>in</sub> | RFX input            |

| 9   | QQ                | QQ lowpass filter Q  |

| 10  | QQX               | QQX lowpass filter Q |

| 11  | GC                | GC gain control      |

| 12  | PCX               | PCX phase control    |

| 13  | PC                | PC phase control     |

| 14  | PU                | PU power up          |

| 15  | LOX <sub>in</sub> | LOX input            |

| 16  | GND               | Ground               |

| 17  | LO <sub>in</sub>  | LO input             |

| 18  | GND               | Ground               |

| 19  | Q                 | Q output             |

| 20  | QX                | QX output            |

# **Absolute Maximum Ratings**

| Parameters                | Symbol           | Value               | Unit |

|---------------------------|------------------|---------------------|------|

| Supply voltage            | $V_S$            | 6                   | V    |

| Input voltage             | V <sub>i</sub>   | 0 to V <sub>S</sub> | V    |

| Junction temperature      | T <sub>j</sub>   | +125                | °C   |

| Storage-temperature range | T <sub>stg</sub> | -40 to +125         | °C   |

## **Thermal Resistance**

| Parameters             | Symbol     | Value | Unit |

|------------------------|------------|-------|------|

| Junction ambient SSO20 | $R_{thJA}$ | 140   | K/W  |

# **Operating Range**

| Parameters                | Symbol           | Value        | Unit |

|---------------------------|------------------|--------------|------|

| Supply-voltage range      | V <sub>S</sub>   | 4.75 to 5.25 | V    |

| Ambient-temperature range | T <sub>amb</sub> | -40 to +85   | °C   |

## **Electrical Characteristics**

Test conditions (unless otherwise specified);  $V_S = 5 \text{ V}$ ,  $T_{amb} = 25^{\circ}\text{C}$ , referred to test circuit System impedance  $Z_O = 50 \Omega$ , fiLO = 950 MHz, PiLO = -10 dBm

| No. | Parameters                | Test Conditions                                         | Pin        | Symbol           | Min. | Тур.      | Max. | Unit     | Type*  |

|-----|---------------------------|---------------------------------------------------------|------------|------------------|------|-----------|------|----------|--------|

| 1.1 | Supply-voltage range      |                                                         | 5, 6       | Vs               | 4.75 |           | 5.25 | V        | Α      |

| 1.2 | Supply current            |                                                         | 5, 6       | Is               | 22   | 30        | 35   | mA       | Α      |

| 2   | Power-down Mode           |                                                         |            |                  |      |           |      |          |        |

| 2.1 | "OFF" mode supply current | $V_{PU} \le 0.5 \text{ V}$ $V_{PU} = 1.0 \text{ V}$ (1) | 14, 5<br>6 | I <sub>SPU</sub> |      | ≤ 1<br>20 |      | μA<br>μA | B<br>D |

| 3   | Switch Voltage            |                                                         | •          | •                | •    |           | •    |          |        |

| 3.1 | "Power ON"                |                                                         | 14         | V <sub>PON</sub> | 4    |           |      | V        | D      |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. During power-down status a load circuitry with DC-isolation to GND is assumed, otherwise a current of I ≈ (VS -0.8 V)/RI has to be added to the above power-down current for each output I, IX, Q, QX.

- 2. The required LO-Level is a function of the LO frequency (see Figure 8).

- 3. Measured with input matching. For 950 MHz, the optional transmission line T3 at the RF input may be used for this purpose. Noise figure measurements without using the differential output signal result in a worse noise figure.

- 4. Using Pins 7 and 8 as a symmetric RF input, the second-order IIP can be improved.

- 5. Due to test board parasitics, this bandwidth may be reduced and not be equal for I, IX, Q, QX. If symmetry and full bandwidth is required, the lowpass Pins 3, 4 and 9, 10 should be isolated from the board. the bandwidth of the I/Q outputs can be increased further by using a resistor between Pins 3, 4, 9 and 10. These resistors shunt the internal loads of RI ~ 5.4 kΩ. The decrease in gain here has to be considered.

- 6. The internal current of the output emitter followers is 0.6 mA. This reduces the undistorted output voltage swing at a 50  $\Omega$  load to approximately 30 mV. For low signal distortion the load impedance should be RI  $\geq$  5 k $\Omega$ .

- 7. Referred to the level of the output vector  $\sqrt{I^2 + Q^2}$

- 8. The low-gain status is achieved with an open or high-ohmic Pin 11. A recommended application circuit for switching between high and low gain status is hown in Figure 3.

# **Electrical Characteristics (Continued)**

Test conditions (unless otherwise specified);  $V_S = 5 \text{ V}$ ,  $T_{amb} = 25^{\circ}\text{C}$ , referred to test circuit System impedance  $Z_O = 50 \Omega$ , fiLO = 950 MHz, PiLO = -10 dBm

| No. | Parameters                            | Test Conditions                                        | Pin             | Symbol                                   | Min. | Тур.           | Max. | Unit  | Type* |

|-----|---------------------------------------|--------------------------------------------------------|-----------------|------------------------------------------|------|----------------|------|-------|-------|

| 3.2 | "Power DOWN"                          |                                                        | 14              | $V_{POFF}$                               |      |                | 1    | V     | D     |

| 4   | LO Input, LO <sub>in</sub>            |                                                        |                 |                                          |      |                |      |       | '     |

| 4.1 | Frequency range                       |                                                        | 17              | f <sub>iLO</sub>                         | 70   |                | 1000 | MHz   | D     |

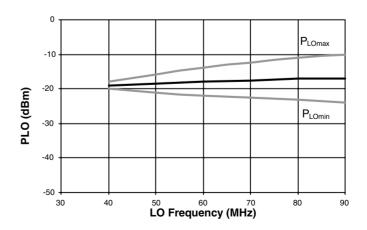

| 4.2 | Input level                           | (2)                                                    | 17              | $P_{iLO}$                                | -12  | -10            | -5   | dBm   | D     |

| 4.3 | Input impedance                       | See Figure 12                                          | 17              | Z <sub>iLO</sub>                         |      | 50             |      | Ω     | D     |

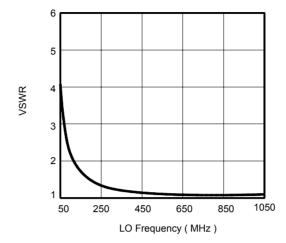

| 4.4 | Voltage standing wave ratio           | See Figure 5                                           | 17              | VSWR <sub>LO</sub>                       |      | 1.2            | 2    |       | D     |

| 4.5 | Duty-cycle range                      |                                                        | 17              | DCR <sub>LO</sub>                        | 0.4  |                | 0.6  |       | D     |

| 5   | RF Input, RF <sub>in</sub>            |                                                        | ı               | •                                        | •    |                | l    |       |       |

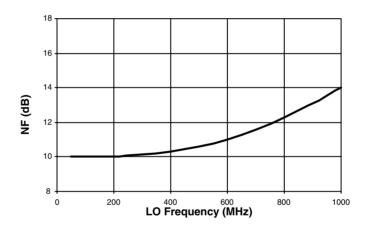

| 5.1 | Noise figure (DSB) symmetrical output | at 950 MHz <sup>(3)</sup><br>at 100 MHz                | 7, 8            | NF                                       |      | 12<br>10       |      | dB    | D     |

| 5.2 | Frequency range                       | $f_{iRF} = Fi_{LO} \pm BW_{YQ}$                        | 7, 8            | f <sub>iRF</sub>                         | 40   |                | 1030 | MHz   | D     |

| 5.3 | -1 dB input compression point         | High gain<br>Low gain                                  | 7, 8            | P <sub>1dBHG</sub><br>P <sub>1dBLG</sub> |      | -8<br>+3.5     |      | dBm   | D     |

| 5.4 | Second order IIP                      | (4)                                                    | 7, 8            | IIP <sub>2HG</sub>                       |      | 35             |      | dBm   | D     |

| 5.5 | Third order IIP                       | High gain<br>Low gain                                  | 7, 8            | IIP <sub>3HG</sub><br>IIP <sub>3LG</sub> |      | +3<br>+13      |      | dBm   | D     |

| 5.6 | LO leakage                            | Symmetric input<br>Asymmetric input                    | 7, 8            | L <sub>OL</sub>                          |      | ≤ -60<br>≤ -55 |      | dBm   | D     |

| 5.7 | Input impedance                       | see Figure 12                                          | 7, 8            | Z <sub>iRF</sub>                         |      | 500110.8       |      | ΩllpF | D     |

| 6   | I/Q Outputs (I, IX, Q,                | I/Q Outputs (I, IX, Q, QX) Emitter Follower I = 0.6 mA |                 |                                          |      |                |      |       |       |

| 6.1 | 3-dB bandwidth w/o external C         |                                                        | 1, 2, 19,<br>20 | BWI/Q                                    | ≥ 30 |                |      | MHz   | D     |

| 6.2 | I/Q amplitude error                   |                                                        | 1, 2, 19,<br>20 | Ae                                       | -0.5 | ≤±0.2          | +0.5 | dB    | В     |

| 6.3 | I/Q phase error                       |                                                        | 1, 2, 19,<br>20 | Pe                                       | -3   | ≤±1.5          | +3   | Deg   | В     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. During power-down status a load circuitry with DC-isolation to GND is assumed, otherwise a current of I  $\approx$  (VS -0.8 V)/RI has to be added to the above power-down current for each output I, IX, Q, QX.

- 2. The required LO-Level is a function of the LO frequency (see Figure 8).

- 3. Measured with input matching. For 950 MHz, the optional transmission line T3 at the RF input may be used for this purpose. Noise figure measurements without using the differential output signal result in a worse noise figure.

- 4. Using Pins 7 and 8 as a symmetric RF input, the second-order IIP can be improved.

- 5. Due to test board parasitics, this bandwidth may be reduced and not be equal for I, IX, Q, QX. If symmetry and full bandwidth is required, the lowpass Pins 3, 4 and 9, 10 should be isolated from the board. the bandwidth of the I/Q outputs can be increased further by using a resistor between Pins 3, 4, 9 and 10. These resistors shunt the internal loads of RI  $\sim$  5.4 k $\Omega$ . The decrease in gain here has to be considered.

- 6. The internal current of the output emitter followers is 0.6 mA. This reduces the undistorted output voltage swing at a 50  $\Omega$  load to approximately 30 mV. For low signal distortion the load impedance should be RI  $\geq$  5 k $\Omega$ .

- 7. Referred to the level of the output vector  $\sqrt{I^2 + Q^2}$

- 8. The low-gain status is achieved with an open or high-ohmic Pin 11. A recommended application circuit for switching between high and low gain status is hown in Figure 3.

# **Electrical Characteristics (Continued)**

Test conditions (unless otherwise specified);  $V_S = 5$  V,  $T_{amb} = 25$ °C, referred to test circuit System impedance  $Z_O = 50$   $\Omega$ , fiLO = 950 MHz, PiLO = -10 dBm

| No. | Parameters                                   | Test Conditions                        | Pin             | Symbol                                  | Min. | Тур.           | Max. | Unit             | Type*         |

|-----|----------------------------------------------|----------------------------------------|-----------------|-----------------------------------------|------|----------------|------|------------------|---------------|

| 6.4 | I/Q maximum output swing                     | Symm. output $R_L > 5 \text{ k}\Omega$ | 1, 2, 19,<br>20 | V <sub>PP</sub>                         |      |                | 2    |                  | D             |

| 6.5 | DC output voltage                            |                                        | 1, 2, 19,<br>20 | V <sub>OUT</sub>                        | 2.5  | 2.8            | 3.1  | V                | Α             |

| 6.6 | DC output offset voltage                     | (6)                                    | 1, 2, 19,<br>20 | V <sub>offset</sub>                     |      | < 5            |      | mV               | Test<br>Spec. |

| 6.7 | Output impedance                             | see Figure 12                          | 1, 2, 19,<br>20 | Z <sub>out</sub>                        |      | 50             |      | Ω                | D             |

| 7   | Gain Control, GC                             |                                        |                 |                                         |      |                | •    |                  |               |

| 7.1 | Control range power<br>Gain high<br>Gain low | (7)                                    | 11              | GCR<br>G <sub>H</sub><br>G <sub>L</sub> |      | 25<br>23<br>-2 |      | dB<br>dBm<br>dBm | D<br>B<br>D   |

| 7.2 | Switch Voltage                               | 1                                      |                 |                                         |      |                |      |                  |               |

| 7.3 | "Gain high"                                  |                                        | 11              |                                         |      |                | 1    | V                |               |

| 7.4 | "Gain low"                                   | (8)                                    | 11 < open       |                                         |      |                |      |                  |               |

| 7.5 | Settling Time, ST                            |                                        |                 |                                         |      |                | •    |                  |               |

| 7.6 | Power "OFF" - "ON"                           |                                        |                 | T <sub>SON</sub>                        |      | < 4            |      | μs               | D             |

| 7.7 | Power "ON" - "OFF"                           |                                        |                 | T <sub>SOFF</sub>                       |      | < 4            |      | μs               | D             |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes

- During power-down status a load circuitry with DC-isolation to GND is assumed, otherwise a current of I ≈ (VS -0.8 V)/RI

has to be added to the above power-down current for each output I, IX, Q, QX.

- 2. The required LO-Level is a function of the LO frequency (see Figure 8).

- 3. Measured with input matching. For 950 MHz, the optional transmission line T3 at the RF input may be used for this purpose. Noise figure measurements without using the differential output signal result in a worse noise figure.

- 4. Using Pins 7 and 8 as a symmetric RF input, the second-order IIP can be improved.

- 5. Due to test board parasitics, this bandwidth may be reduced and not be equal for I, IX, Q, QX. If symmetry and full bandwidth is required, the lowpass Pins 3, 4 and 9, 10 should be isolated from the board. the bandwidth of the I/Q outputs can be increased further by using a resistor between Pins 3, 4, 9 and 10. These resistors shunt the internal loads of RI  $\sim$  5.4 k $\Omega$ . The decrease in gain here has to be considered.

- 6. The internal current of the output emitter followers is 0.6 mA. This reduces the undistorted output voltage swing at a 50  $\Omega$  load to approximately 30 mV. For low signal distortion the load impedance should be RI  $\geq$  5 k $\Omega$ .

- 7. Referred to the level of the output vector  $\sqrt{l^2 + Q^2}$

- 8. The low-gain status is achieved with an open or high-ohmic Pin 11. A recommended application circuit for switching between high and low gain status is hown in Figure 3.

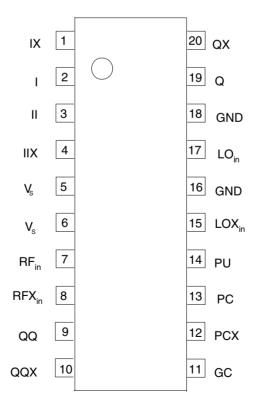

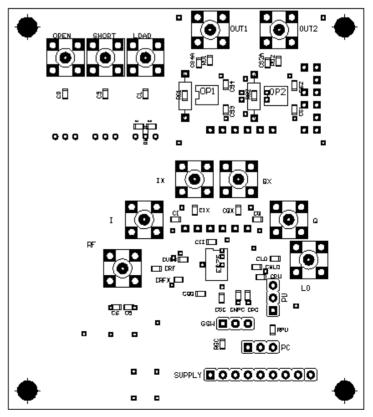

Figure 3. Test Circuit

$<sup>^*</sup>$  optional for single-ended tests (notice 3 dB bandwidth of AD620) T1, T2 = transmission line  $Z_O$  = 50  $\Omega.$

If no GC function is required, connect Pin 11 to GND.

For high and low gain status GC´ is to be switched to GND respectively to V<sub>S</sub>.

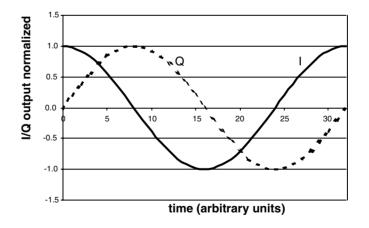

**Figure 4.** I and Q phase for  $f_{RF} > f_{LO}$ . For  $f_{RF} < f_{LO}$  the phase is inverted.

Figure 5. Typical VSWR Frequency Response of the LO Input

**Figure 6.** Noise Figure versus LO Frequency; o: Value at 950 MHz with RF Input Matching with T3

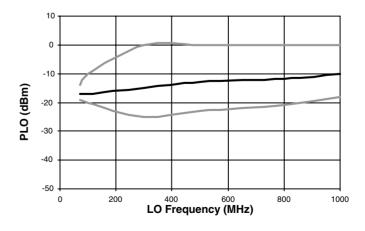

Figure 7. Typical Suitable LO Power Range versus Frequency

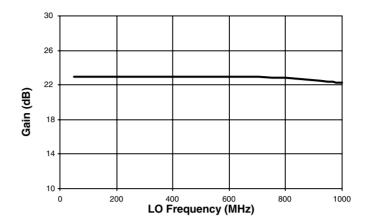

**Figure 8.** Gain versus LO Frequency; x: Value at 950 MHz with RF Input Matching with T3

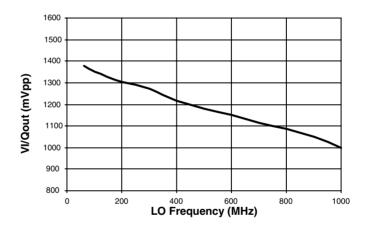

**Figure 9.** Typical Output Signal versus LO Frequency for  $P_{RF}$  = -15 dBm and PLO = -15 dBm

Figure 10. Typical Suitable LO Power Range versus Frequency

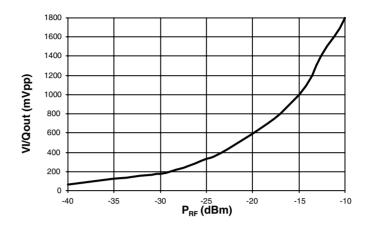

**Figure 11.** Typical Output Voltage (single ended) versus  $P_{RF}$  at  $T_{amb} = 25^{\circ}C$  and PLO = -15 dBm

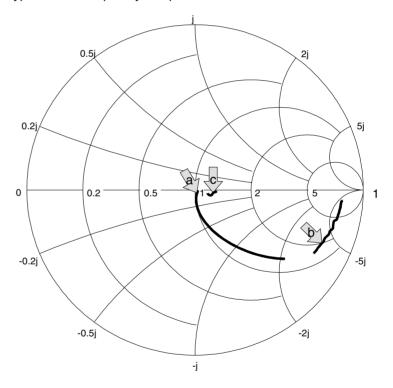

Figure 12. Typical S11 Frequency Response

a: LO input, LO frequency from 100 MHz to 1100 MHz, marker: 950 MHz

b: RF input, RF frequency from 100 MHz to 1100 MHz, marker: 950 MHz

c: I/Q Outputs, Baseband Frequency from 5 MHz to 55 MHz, marker: 25 MHz

10-Demodulator 6 10-Dem

Figure 13. Evaluation Board Layout

Figure 14. Evaluation Board

## **External Components**

CUCC 100 nF

CRFX 1 nF

CLO 100 pF

CNLO 1 nF

CRF 100 pF

CII, CQQ optional external lowpass filters

T3 transmission line for RF-input matching, to connect

optionally

baseband outputs

CI, CIX optional for AC-coupling at

CQ, CQX

CPDN 100 pF not connected

CGC 100 pF

CPC 100 pF not connected CNPC 100 pF not connected GSW gain switch

## **Calibration Part**

CO, CS, CL 100 pF RL 50  $\Omega$

# **Conversion to Single Ended Output**

(see data sheet of AD620)

OP1, OP2 AD620

RG1, RG2 prog. gain, see datasheet, for 5.6 k $\Omega$  a gain of 1 at

50  $\Omega$  is achieved together with RD1 and RD2.

RD1, RD2 450  $\Omega$ CS1, CS2 100 nF CS3, CS4 100 nF

# Description of the Evaluation Board

Board material: epoxy;  $\epsilon r = 4.8$ , thickness = 0.5 mm, transmission lines:  $Z_0 = 50~\Omega$ The board offers the following functions:

- Test circuit for the U2794B:

- The supply voltage and the control inputs GC, PC and PU are connected via a plug strip. The control input voltages can be generated via external potentiometers; then the inputs should be AC-grounded (time requirements in burst mode for power up have to be considered).

- The outputs I, IX, Q, QX are DC coupled via an plug strip or can be AC-connected via SMB plugs for high frequency tests e.g. noise figure or s-parameter measurement. The Pins II, IIX, QQ, QQX allow user-definable filtering with 2 external capacitors CII, CQQ.

- The offsets of both channels can be adjusted with two potentimeters or resistors.

- The LO- and the RF-inputs are AC-coupled and connected via SMB plugs. If transmission line T3 is connected to the RF-input and AC-grounded at the other end, gain and noise performance can be improved (input matching to 50  $\Omega$ ).

- The complementary RF-input is AC-coupled to GND (CRFX = 1 nF), the same appears to the complementary LO input (CNLO = 1 nF).

- A calibration part which allows to calibrate an s-parameter analyzer directly to the inand output- signal ports of the U2794B.

- For single-ended measurements at the demodulator outputs, two OPs (e.g., AD620 or other) can be con-figured with programmable gain; together with an output-divider network RD = 450  $\Omega$  to RL = 50  $\Omega$ , direct measurements with 50  $\Omega$  load impedances are possible at frequencies t < 100 kHz.

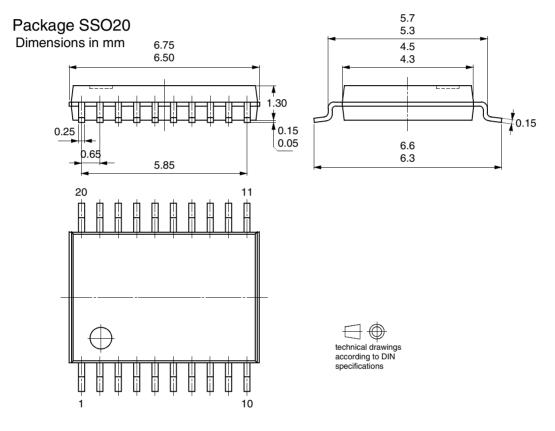

# **Ordering Information**

| Extended Type Number | Package | Remarks                        |

|----------------------|---------|--------------------------------|

| U2794B-MFS           | SSO20   | Tube, MOQ 830 pcs              |

| U2794B-MFSG3         | SSO20   | Taped and reeled, MOQ 4000 pcs |

# **Package Information**

## **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

### Europe

Atmel Sarl

Route des Arsenaux 41

Case Postale 80

CH-1705 Fribourg

Switzerland

TEL (41) 26-426-5555

FAX (41) 26-426-5500

### Asia

Room 1219

Chinachem Golden Plaza

77 Mody Road Tsimhatsui

East Kowloon

Hong Kong

TEL (852) 2721-9778

FAX (852) 2722-1369

### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

### **Atmel Operations**

### Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Avenue de Rochepleine

BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

*e-mail* literature@atmel.com

Web Site http://www.atmel.com

### © Atmel Corporation 2003.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Atmel® is the registered trademark of Atmel.

Other terms and product names may be the trademarks of others.