Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **UBA2072**

# Low Voltage Full-bridge control IC for CCFL backlighting

Rev. 08.0 — February 2007

Preliminary data sheet

# 1. General description

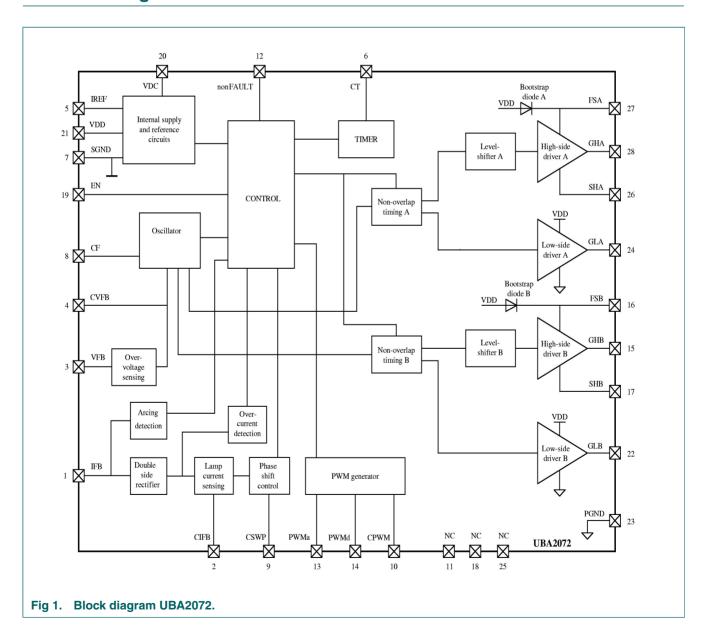

The UBA2072 is a low voltage IC intended to drive Cold Cathode Fluorescent Lamps (CCFLs) for back-lighting applications. The IC contains level-shifters, bootstrap diodes and drivers for the external full-bridge power switches.

Furthermore, the UBA2072 has a build-in HF oscillator which determines the operating frequency, a phase shift controller for obtaining constant lamp current, and a PWM generator which is used to set the brightness level of the CCFLs.

The UBA2072 is designed to operate over a wide low voltage inverter supply range, up to 30V. The IC can be supplied directly from the inverter supply.

#### 2. Features

Wide supply voltage range (9 V to 30 V DC)

Adjustable maximum fault timing

Integrated level-shifters

Integrated bootstrap diodes

Lamp current control

Over-voltage control

Over-current protection

Ignition failure detection

Arcing detection

Brightness level adjustment through PWM dimming

Integrated PWM generator

# 3. Applications

LCD-backlighting, including LCD-TV and LCD-Monitor applications. The IC is intended to drive and control a full-bridge inverter with resonant load circuit for CCFLs, but can also drive an array of External Electrode Fluorescent Lamps (EEFLs).

# 4. Ordering information

Table 1: Ordering information

|             |         |                                                                   | 7.0      |  |  |  |

|-------------|---------|-------------------------------------------------------------------|----------|--|--|--|

| Type number | Package |                                                                   |          |  |  |  |

|             | Name    | Description                                                       | Version  |  |  |  |

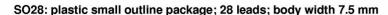

| UBA2072T    | SO28    | plastic small outline package; 28 leads; body width 7.5 mm        | SOT136-1 |  |  |  |

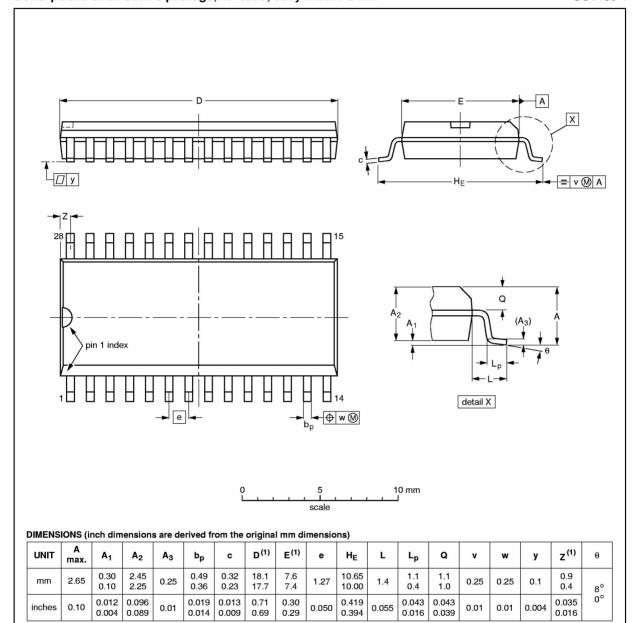

| UBA2072TS   | SSOP28  | plastic shrink small outline package; 28 leads; body width 5.3 mm | SOT341-1 |  |  |  |

# 5. Block diagram

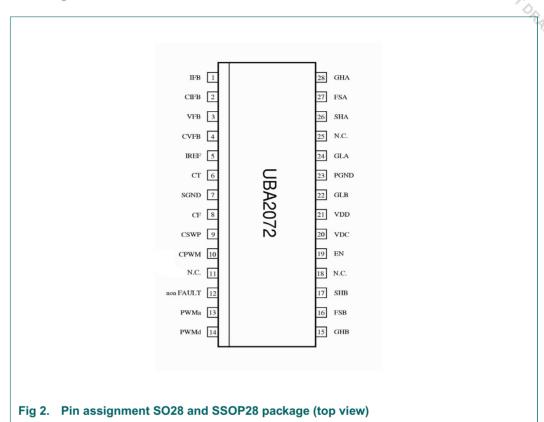

# 6. Pinning information

# 6.1 Pinning

#### 6.2 Pin description

Table 2: Pin description

| Symbol | Pin | Description                    | Function                                                                                                                                                  |

|--------|-----|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| IFB    | 1   | current feedback input.        | Input signal for the lamp current control loop. Should be connected to a voltage proportional to the lamp current.                                        |

| CIFB   | 2   | current regulation capacitor.  | A capacitor must be connected between this pin and the signal ground. It sets the time constant of the lamp current control loop.                         |

| VFB    | 3   | voltage feedback input         | Input signal for the voltage control loop. Should be connected to a voltage proportional to the transformer output voltage                                |

| CVFB   | 4   | voltage regulation capacitor   | A capacitor must be connected between this pin and the signal ground. It sets the time constant of the voltage control loop.                              |

| IREF   | 5   | reference current output       | A $33k\Omega$ resistor must be connected between this pin and the signal ground. The IC uses it to make accurate internal currents.                       |

| СТ     | 6   | fault timing capacitor         | A capacitor must be connected between this pin and the signal ground. It sets the time that a fault condition is allowed before the IC shuts itself down. |

| SGND   | 7   | signal ground                  |                                                                                                                                                           |

| CF     | 8   | HF-oscillator timing capacitor | A capacitor must be connected between this pin and the signal ground. It sets the minimum switching frequency of the full bridge.                         |

Table 2: Pin description ...continued

| NXP Ser  | nico | nductors                           | UBA2072                                                                                                                                                                                                                                                                  |

|----------|------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      |                                    | Low Voltage Full-bridge control IC for CCFL backlighting                                                                                                                                                                                                                 |

| Table 2: |      | escriptioncontinued                |                                                                                                                                                                                                                                                                          |

| Symbol   | Pin  | Description                        | Function                                                                                                                                                                                                                                                                 |

| CSWP     | 9    | phase-shift sweep capacitor        | A capacitor must be connected between this pin and the signal ground. It sets the time in which the phase difference between bridge halve A and bridge halve B is swept down from regulation level to zero or swept up from zero to regulation level during PWM dimming. |

| CPWM     | 10   | PWM timing capacitor               | If a capacitor is connected between this pin and the signal ground, it sets the frequency of the PWM oscillator.                                                                                                                                                         |

|          |      |                                    | If this pin is connected to signal ground the internal PWM oscillator is disabled.                                                                                                                                                                                       |

| NC       | 11   | not connected                      |                                                                                                                                                                                                                                                                          |

| nonFAULT | 12   | status signal<br>input/output      | The IC signals a fault condition to an external circuit by pulling this pin low and external circuits can also signal a fault condition to the IC by pulling this pin low.                                                                                               |

| PWMa     | 13   | analog PWM dimming input           | The dutycycle of the internally generated PWM signal is proportional to the voltage on this pin.                                                                                                                                                                         |

| PMWd     | 14   | digital PWM dimming input/output   | Digital output of internally generated PWM signal if a capacitor is connected to the CPWM-pin.                                                                                                                                                                           |

|          |      |                                    | Digital input of PWM signal if the CPWM-pin is connected to signal ground.                                                                                                                                                                                               |

|          |      |                                    | Note that the signal on the PWMd-pin is active low, so low voltage on the PWMd-pin means lamps are on.                                                                                                                                                                   |

| GHB      | 15   | high-side driver output B          | Gate connection of the high side power switch of full bridge halve B                                                                                                                                                                                                     |

| FSB      | 16   | floating supply output B           | A buffer capacitor must be connected between this pin and the SHB-pin. This capacitor is charged when the low side switch B is on and supplies the high side driver B.                                                                                                   |

| SHB      | 17   | high-side source connection B      | Return for high side gate driver B. Must be connected to the source of the high side power switch of full bridge halve B.                                                                                                                                                |

| NC       | 18   | not connected                      |                                                                                                                                                                                                                                                                          |

| EN       | 19   | chip enable input                  | A low voltage on this pin will reset and shutt down the IC                                                                                                                                                                                                               |

| VDC      | 20   | IC low-voltage supply input        | IC supply                                                                                                                                                                                                                                                                |

| VDD      | 21   | regulated 12 V supply output/input | A buffer capacitor must be connected between this pin and power ground                                                                                                                                                                                                   |

| GLB      | 22   | low-side driver output B           | Gate connection of the low side power switch of full bridge halve B                                                                                                                                                                                                      |

| PGND     | 23   | power ground                       | return for low side drivers A and B                                                                                                                                                                                                                                      |

| GLA      | 24   | low-side driver output A           | Gate connection of the low side power switch of full bridge halve A                                                                                                                                                                                                      |

| NC       | 25   | not connected                      |                                                                                                                                                                                                                                                                          |

| SHA      | 26   | high-side source connection A      | Return for high side gate driver A. Must be connected to the source of the high side power switch of full bridge halve A.                                                                                                                                                |

| FSA      | 27   | floating supply output A           | A buffer capacitor must be connected between this pin and the SHA-pin. This capacitor is charged when the low side switch A is on and supplies the high side driver A.                                                                                                   |

| GHA      | 28   | high-side driver output A          | Gate connection of the high side power switch of full bridge halve A                                                                                                                                                                                                     |

# 7. Functional description

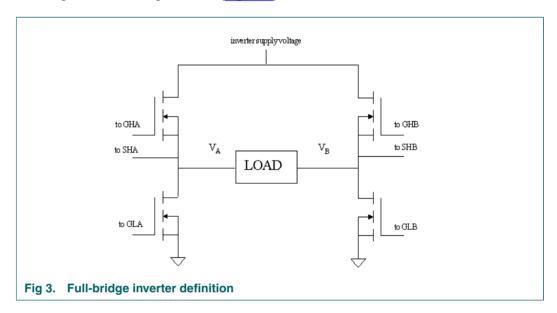

The UBA2072 is designed to drive a full-bridge inverter with resonant load. The load consists typically of transformers with CCFLs. Two parameters are used by the UBA2072 to control the switches of the full-bridge inverter: the phase shift and the switching frequency.

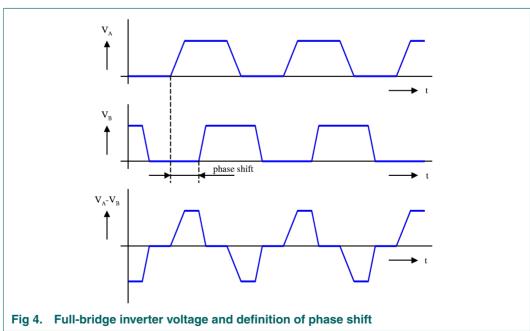

The two full bridge halves A and B (<u>Figure 3</u>) always operate at the same switching frequency. The frequency is used to control transformer output voltage during the first ignition of the lamps. The phase difference between the full-bridge halves A and B voltages ( $V_A$  and  $V_B$ ) controls the lamp current, as this determines the rms value of the full-bridge inverter voltage  $V_A$  -  $V_B$  (Figure 4).

#### Low Voltage Full-bridge control IC for CCFL backlighting

#### 7.1 IC Supply

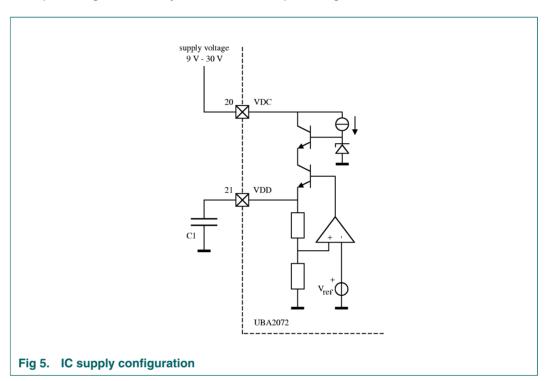

The VDC pin is connected to an external supply with a voltage of 9 V to 30 V. The VDD-pin must be connected to a buffer capacitor (see <u>Figure 5</u>). The VDD-pin acts as a regulated 12 V output, from which the gate drivers are supplied. External auxiliary circuits may also be supplied from the VDD pin. **Never supply the IC directly via the VDD-pin**. VDC-pin voltage must always<sup>1</sup> be above VDD-pin voltage.

#### 7.2 Start-up and Under-Voltage Lock-Out (UVLO)

The IC starts up at  $V_{VDC(start)}$  and locks out (stops oscillating) when the voltage on the VDC-pin drops below  $V_{DC(stop)}$ .

#### 7.3 Enable

The UBA2072 is put in standby when the voltage on the EN-pin comes below  $V_{\text{EN(low)}}$  (see Table 5). The IC will stop oscillating, and most of the internal circuits will shut down. However, the internal linear regulator between VDC and VDD will remain active, but with reduced current supply capability. All internal signals are reset when the EN-pin is low.

When the voltage on the EN-pin comes above V<sub>EN(high)</sub> the IC will start up again.

#### 7.4 Lamp (re-)ignition

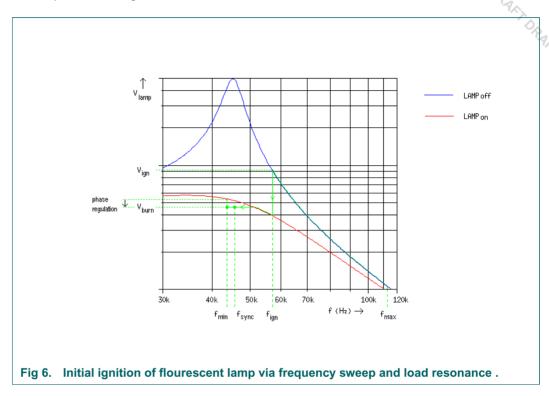

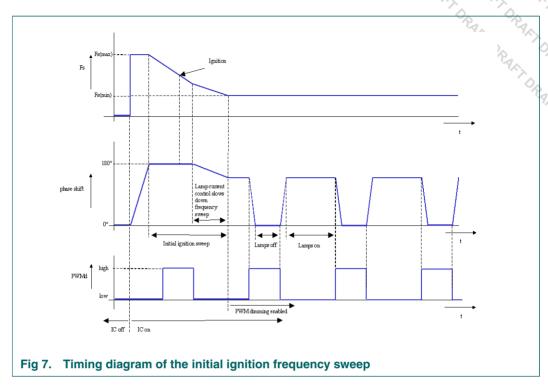

The IC starts at its maximum switching frequency  $F_{s(max)}$ . First the capacitors at the CIFB-pin and CSWP-pin are charged (setting the phase shift between the two bridge halves to maximum). Then the frequency is swept down to the minimum frequency  $F_{s(min)}$  (see Figure 7). During this initial ignition frequency sweep the lamp voltage will increase

<sup>1.</sup> During normal operation. During switch off faster fall down of VDC with respect to VDD is acceptable.

#### Low Voltage Full-bridge control IC for CCFL backlighting

as the frequency comes closer to the resonant frequency of the unloaded resonance circuit. Once the ignition voltage  $V_{ign}$  is reached, the lamps will ignite and the lamp voltage will drop to the voltage of the loaded resonance curve.

Advantage of the sweep rather then a fixed ignition frequency is that sensitivity for spread in resonance frequency is much lower.

Once the lamps are ignited the frequency sweep down continues, gradually increasing the lamp current (the resonance circuit should now still be inductive, so current increases as frequency drops) untill the current regulation level is reached and the current regulation loop starts decreasing the phase shift between the bridge halves in order to keep the lamp current constant. If the current regulation loop cannot decrease the phase shift fast enough to counteract the frequency sweep down, then the frequency sweep is slowed down. Once the frequency has reached Fs(min), PWM dimming is enabled (See Figure 7).

Initial ignition frequency sweep and PWM-generator are not synchronised, and once the frequency sweep is finished PWM dimming can start anywhere in its cycle.

7 of 28

# **UBA2072**

#### Low Voltage Full-bridge control IC for CCFL backlighting

During PWM dimming the switching frequency is constant. Only the phase shift is swept from its regulated value to its minimum value and back. The phase shift sweep has to provide re-ignition of the lamps, therefor the unloaded resonance curve of <u>Figure 6</u> has to be high enough at the normal operation switching frequency Fs(min).

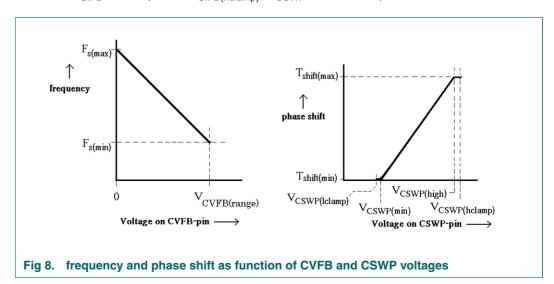

The voltage at the CVFB-pin is inverse proportional to the switching frequency,(see <u>Figure 8</u>). The voltage at the CVFB-pin is clamped at the voltage V<sub>CVFB(range)</sub> were the switching frequency is Fs(min).

The voltage at the CSWP-pin is proportional to the phase shift (see <u>Figure 8</u>). The voltage at the CSWP-pin is clamped at the low side at  $V_{CSWP(Iclamp)}$  and at the high side at  $V_{CIFB}$ . Because  $V_{CIFB}$  is clamped at  $V_{CIFB(hclamp)}$ ,  $V_{CSWP}$  is also clamped.

® NXP B.V. 2007. All rights reserved.

#### Low Voltage Full-bridge control IC for CCFL backlighting

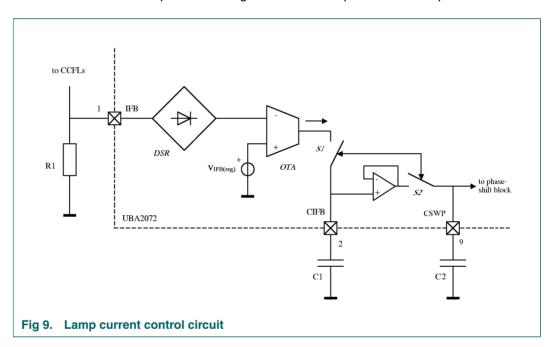

#### 7.5 Lamp current control

The lamp current control is active during the initial ignition frequency sweep and when the lamps are on. It is disabled during the time within a PWM dim cycle that the lamps are off.

An (AC or DC) voltage representing the lamp current, usually the voltage across an external sense resistor, is to be connected to the IFB-pin. This voltage is internally double-side rectified (DSR), and compared to a reference level V<sub>IFB(reg)</sub> by an operational transconductance amplifier (OTA), as shown in Figure 9.

When the current is being regulated, switches S1 and S2 (see Figure 9) are closed (conducting). The output current of the OTA is fed into capacitor C1, which is connected to the CIFB-pin. The voltage across this capacitor is copied into capacitor C2, which is connected to the CSWP-pin. The voltage on the CSWP-pin controls the phase shift.

#### 7.6 PWM dimming

During the time within a PWM dim cycle that the lamps are off, switches S1 and S2 are opened (non-conducting). In this way the regulation level is stored in C1 when the current regulation loop is opened (see Figure 9).

After the regulation loop is opened, C2 is discharged (the voltage on the CSWP-pin is swept down) to switch off the lamps, and charged again to turn the lamps on again. The lamps on versus off time is determined by the signal on the PWMd-pin (low = lamps on).

The minimum phase difference between the bridge halves during the lamps off period of each PWM cycle is  $\Delta \phi_{(min)}$ .

During the PWM lamps off period the phase shift level at which the lamp current was in regulation is preserved in the capacitor connected to the CIFB-pin (C1 in Figure 9). Switches S1 and S2 are closed (conducting) again when the voltage on the CSWP-pin has reached the voltage on the CIFB-pin again.

#### Low Voltage Full-bridge control IC for CCFL backlighting

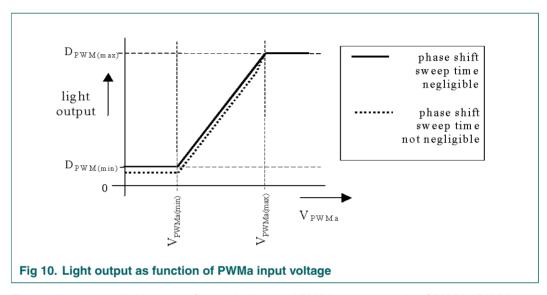

The phase shift sweep speed is determined by the capacitor connected to the CSWP-pin (C2 in Figure 9). The real lamp light output will be slightly less then the PWMd signal duty cycle because of the phase shift sweep time (see Figure 10). When the lamp-on time is too short to sweep up the voltage on the CSWP-pin, the IC will wait until the CSWP voltage has actually reached the current control level before sweeping down again. This prevents that the lamps go out completely when deep dimming is combined with a too large capacitor at the CSWP-pin.

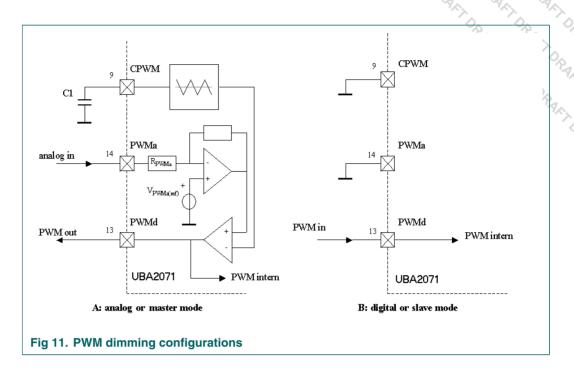

Three pins are available to configure the internal PWM generator: the CPWM-, PWMa-, and the PWMD-pin. The two possible PWM configurations are shown in <u>Figure 11</u>. In the analog or master mode the internal PWM generator is active and generating the PWM signal. This signal is put on the PWMd-pin, which is automatically configured as an output. The minimum dutycycle of the internal PWM generator is limited to D<sub>PWM(min,intern)</sub>.

When the CPWM-pin is connected to ground, the IC is put in digital or slave mode. The PWMd-pin is then an input and the IC uses the PWM signal provided on the PWMd-pin.

The signal on the PWMd-pin is active low. A voltage below  $V_{PWMD(low)}$  on the pin will turn the lamps on and a voltage above  $V_{PWMD(high)}$  will turn the lamps off.

PWM dimming of multiple ICs can be synchronised by configuring one IC as master and the others as slaves and connecting all PWMd-pins together.

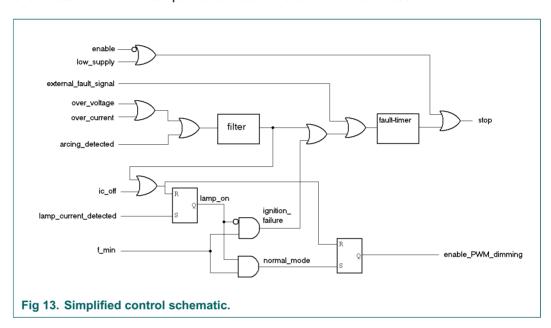

PWM dimming is only enabled in normal mode, when no fault condition excists. The only exception is when an external detected fault condition is entered via the nonFAULT-pin, then PWM dimming remains active (see Figure 13).

**UBA2072**

#### Low Voltage Full-bridge control IC for CCFL backlighting

#### 7.7 The fault timer

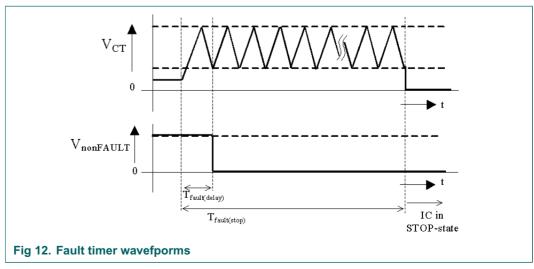

The fault timer provides a delay inbetween the detection of a fault and the shut down of the IC (enter STOP-state). Its time  $T_{fault(timeout)}$  is proportional to the capacitor connected to the CT-pin.

Any fault condition will start the timer. When the timer is activated, the capacitor at the CT-pin will be alternatingly charged and discharged (see Figure 12). These cycles are being counted by a four bit counter. After one cycle (the fault signalling delay  $T_{fault(delay)}$ ) the nonFAULT-pin is activated (pulled low), to signal to any external circuit that there is a fault detected and the IC will stop if that fault continues. After 15 cycles is the fault time-out period  $T_{fault(timeout)}$  reached, and the IC will enter STOP-state.

If the fault timer is inactive, the CT-pin voltage is one Vbe (≅0.7V). The CT-timer has a protection that prevents the IC to start-up if the CT-pin is shorted to GND.

#### Low Voltage Full-bridge control IC for CCFL backlighting

#### 7.8 Protections

All fault conditions and how they are processed in the IC can be found in Figure 13.

The UBA2072 includes internal over voltage (OV), overcurrent (OC), bad contact or arcing (ARC) and ignition failure (IF) protections. There is also one pin (the nonFAULT-pin) which provides bidirectional fault signalling to and from any external circuit. Via this pin a lamp short detection or over temperature detection or such can be added.

In the next sections each fault protection function will be explained.

#### 7.8.1 Over voltage protection

The over voltage protection circuit is intended to prevent the transformer output voltage from exceeding its maximum rating. It can also be used to regulate the output voltage to the required lamp ignition voltage.

When the voltage on the VFB-pin exceeds the OV reference level  $V_{VFB(ovref)}$ , over voltage is detected. As result PWM dimming is disabled and the fault timer is started. Also the capacitor connected to the CVFB-pin is discharged (by  $I_{CVFB(ov)}$ ). When the voltage at the VFB-pin drops below the OV reference level, the CVFB capacitor is charged (by  $I_{CVFB(charge)}$ ) again. and the output voltage of the transformer will increase again. Because the charging and discharging of the CVFB capacitor follows the ripple on the VFB voltage, the feedback gain of the voltage control loop is set by the ripple on the feedback signal.

If CVFB is more discharged then charged (over a hf cycle) then the CVFB voltage will drop, and the switching frequency increase. As a result the output voltage of the transformer will decrease<sup>2</sup>. When this happens the current control loop is froozen (switch S1 of Figure 9 is opened (non-conducting), so the regulation level stored in C1 cannot be changed by the current regulation loop) in order to prevent the frequency increase being compensated by a phase shift difference increase by the current control.

<sup>2.</sup> Presuming that the effective full bridge load impedance is in inductive region.

#### Low Voltage Full-bridge control IC for CCFL backlighting

An internal latch makes the OV fault signal continuesly high even if the voltage at the VFB-pin only exceeds VVFB(ovref) during part of the output period. So the peak of the voltage on the VFB-pin determines if an over voltage fault condition is seen. In order to avoid that OV fault condition at the nominal switching frequency (with the lamps operating normally), the voltage ripple on the VFB-pin must not be too large.

The voltage at CVFB is limited by the oscillator circuit to  $V_{\text{CVFB(range)}}$  when the minimum switching frequency  $F_{\text{s(min)}}$  is reached. This ensures an immediate frequency increase capability at over voltage detection.

#### 7.8.2 Over current detection

When the absolute value<sup>3</sup> of the voltage across the current sense resistor (connected to the IFB-pin) exceeds the OC reference level  $V_{\text{IFB(ocref)}}$ , over-current is detected. As result PWM dimming is disabled and the fault timer is started.

#### 7.8.3 Arcing detection

If arcing occurs, for instance due to a bad lamp connection, it causes repetitive short current spikes that can be seen as voltage spikes at the IFB input<sup>4</sup>. The arcing detection circuit is directly connected to the IFB-pin, so it can only see spikes with a positive polarity. Usually that will be sufficient. It can detect spikes with amplitude above  $V_{\text{IFB}(arcref)}$  and a duration longer then  $T_{\text{SPIKE}(min)}$ . Each spike will trigger an internal one-shot, which signals to the control circuits that arcing has been detected. If this happens PWM dimming is disabled, and the fault timer is started.

#### 7.8.4 Ignition Failure (IF)

When the current control loop comes close to its regulation point, the lamps are presumed to be on (ignited). This is when the average double side rectified IFB-pin voltage is above  $V_{\text{IFB(lampon)}}$ . If the lamps are not on when the ignition sweep is finished (switching frequency has reached  $F_{\text{S(min)}}$ ), then an ignition failure is detected, PWM dimming is disabled and the fault timer is started.

#### 7.8.5 The nonFAULT-pin

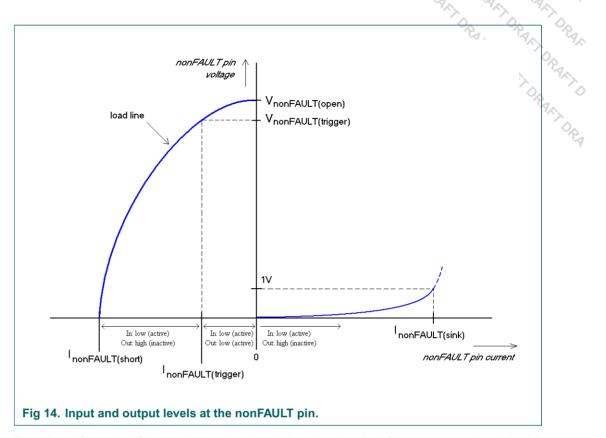

The nonFAULT-pin provides bidirectional signalling of the fault status between the IC and any external circuit. When no fault is detected, the voltage on the pin is pulled high by an internal current source.

An external circuit can signal to the IC that a fault has been detected by pulling down the pin. The IC will detect the current drawn from the pin and start the fault timer. To prevent interference with the PWM dimming, the IC will only look at the nonFAULT pin during the period that the lamp current regulation loop is closed (VCSWP=VCIFB).

When the IC detects a fault internal (as in <u>Section 7.8.1</u> to <u>Section 7.8.4</u>), it signals this via the nonFAULT pin by pulling the pin down. In this case the IC can not see anymore if there's an external detected fault, but that's no problem, because the faulttimer is then already running.

<sup>3.</sup> The OC comparator is behind the double side rectifier at the IFB-pin

<sup>4.</sup> Provided that the current sensing circuit is simple sense resistor only.

### UDAZUIZ

### Low Voltage Full-bridge control IC for CCFL backlighting

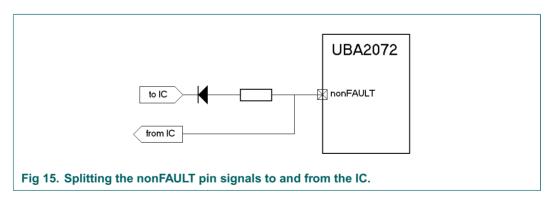

The signal from the IC is a voltage signal and the signal to the IC is a current signal. In this way a driving conflict is prevented. Also it leaves the possibility for the outside world to see the signal from the IC even while a fault condition is being signalled to the IC in the mean time, as illustrated in Figure 15.

#### 7.9 High- and low-side drivers

The four drivers are identical. The output of each driver is connected to the equivalent gate of an external power MOSFET. The bootstrap capacitors are charged from the VDD voltage when the low-side power MOSFETs are turned on, and they supply the high-side drivers. The VDD voltage directly supplies the low-side drivers. Current sourcing capability and the on-resistance of the drivers can be found in Table 5.

#### Low Voltage Full-bridge control IC for CCFL backlighting

#### 7.10 Non overlap

For each half bridge a delay is made between the switching-off of the external high side power transistor and the switching-on of the external low side power transistor and the other way round. The duration is the so called 'non-overlap' time (T<sub>NONOV</sub>).

# 8. Limiting values

Table 3: Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). All voltages are measured with respect to signal ground (pin 7); positive currents flow into the chip. The voltage ratings are valid provided other ratings are not violated.

| Symbol                               | Parameter                                             | Conditions                                          | Min                      | Max       | Unit |

|--------------------------------------|-------------------------------------------------------|-----------------------------------------------------|--------------------------|-----------|------|

| General                              |                                                       |                                                     |                          |           |      |

| R <sub>IREF</sub>                    | reference resistor value on pin IREF                  |                                                     | 30                       | 36        | kΩ   |

| SR                                   | slew rate on pins FSA, FSB,<br>GHA, GHB, SHA, and SHB |                                                     | -4                       | +4        | V/ns |

| T <sub>amb</sub>                     | ambient temperature                                   |                                                     | -25                      | +100      | °C   |

| Tj                                   | junction temperature                                  |                                                     | -25                      | +125      | °C   |

| T <sub>stg</sub>                     | storage temperature                                   |                                                     | <b>–55</b>               | +150      | °C   |

| Voltages                             |                                                       |                                                     |                          |           |      |

| V <sub>SHA</sub> , V <sub>SHB</sub>  | voltage on pins SHA and SHB                           |                                                     | 0                        | +30       | V    |

| V <sub>FSA</sub> , V <sub>FSB</sub>  | voltage on pins FSA and FSB                           | with respect to V <sub>SHA</sub> , V <sub>SHB</sub> | -0.3                     | +14       | V    |

| V <sub>EN</sub>                      | voltage on pin EN                                     |                                                     | -0.3                     | +14       | V    |

| V <sub>GLA</sub> , V <sub>GLB</sub>  | voltage on pins GLA and GLB                           |                                                     | -0.3                     | $V_{VDD}$ | V    |

| $V_{GHA}$                            | voltage on pins GHA                                   |                                                     | V <sub>SHA</sub><br>-0.3 | $V_{FSA}$ | V    |

| $V_{GHB}$                            | voltage on pins GHB                                   |                                                     | V <sub>SHB</sub><br>-0.3 | $V_{FSB}$ | V    |

| $V_{PGND}$                           | voltage on pin PGND                                   |                                                     | 0                        | 0         | V    |

| $V_{VDC}$                            | voltage on pin VDC                                    |                                                     | -0.3                     | +30       | V    |

| $V_{PWMa}, V_{PWMd}, \ V_{nonFAULT}$ | voltage on pins PWMa, PWMd and nonFAULT               |                                                     | -0.1                     | +5        | V    |

| $V_{VFB}$                            | voltage on pin VFB                                    | continuous                                          | -0.1                     | +5        | V    |

|                                      |                                                       | t<1ms                                               | -0.1                     | +8        | V    |

| $V_{IFB}$                            | voltage on pin IFB                                    | continuous                                          | -5                       | +5        | V    |

|                                      |                                                       | t<100μs                                             | -9                       | +9        | V    |

**ESD**

### Low Voltage Full-bridge control IC for CCFL backlighting

Table 3: Limiting values ...continued

| In accordance    |                              | ting System (IEC 60134). All voltages are m<br>hip. The voltage ratings are valid provided o          |      | •    | /\ <del>-</del> |

|------------------|------------------------------|-------------------------------------------------------------------------------------------------------|------|------|-----------------|

| Symbol           | Parameter                    | Conditions                                                                                            | Min  | Max  | Unit            |

| V <sub>ESD</sub> | electrostatic discharge volt | age                                                                                                   |      |      | Op              |

|                  | human body model             | IFB, CIFB, VFB, CVFB, IREF, CT,<br>CF, CSWP, CPWM, nonFAULT,<br>PWMa, PWMd, EN, VDC, VDD,<br>GLA, GLB | -2   | +2   | kV              |

|                  |                              | GHB, FSB, SHB, SHA, FSA, GHA                                                                          | -1   | +1   | kV              |

|                  | machine model                | all pins                                                                                              | -250 | +250 | V               |

| Latchup          |                              |                                                                                                       |      |      |                 |

|                  | SNW-FQ-303                   | all pins                                                                                              |      |      |                 |

#### Thermal characteristics

Thermal characteristics Table 4:

| Symbol        | Parameter               | Conditions                  | Тур | Unit |

|---------------|-------------------------|-----------------------------|-----|------|

| $R_{th(j-a)}$ | thermal resistance from | in free air; SO28 package   | 68  | K/W  |

|               | junction to ambient     | in free air; SSOP28 package | 108 | K/W  |

#### 10. Characteristics

#### **Characteristics**

$T_{amb}$  = 25 °C;  $V_{VDC}$  = 15 V;  $V_{EN}$ = $V_{VDD}$ ;  $C_{VDD}$ =100nF;  $R_{IREF}$  = 33 k $\Omega$  and CPWM pin connected to a capacitor, unless otherwise specified. All voltages are measured with respect to signal ground (pin 7); currents are positive when flowing into

| Symbol                                    | Parameter                                              | Conditions                                  |            | Min  | Тур  | Max             | Unit         |

|-------------------------------------------|--------------------------------------------------------|---------------------------------------------|------------|------|------|-----------------|--------------|

| Start-up                                  |                                                        |                                             |            |      |      |                 |              |

| V <sub>VDC(start)</sub>                   | start-up voltage level                                 |                                             |            | 8.6  | 9    | 9.4             | V            |

| V <sub>VDC(stop)</sub>                    | stop voltage level                                     |                                             |            | 7.7  | 8    | 8.3             | V            |

| $V_{VDC(hys)}$                            | start-stop hysteresis level                            |                                             |            | 0.9  | 1    | 1.1             | V            |

| Supply                                    |                                                        |                                             |            |      |      |                 |              |

| I <sub>VDC(on)</sub>                      | total supply current on pin VDC                        | oscillating                                 | <u>[1]</u> |      |      | 5               | mΑ           |

| I <sub>VDC(on)</sub>                      | total supply current on pin VDC                        | VDC=30V; oscillating                        | <u>[1]</u> |      |      | 7.5             | mΑ           |

| I <sub>VDC(off)</sub>                     | total supply current on pin VDC                        | V <sub>EN</sub> =0V                         |            |      |      | 1.5             | mΑ           |

| I <sub>VDC(off)</sub>                     | total supply current on pin VDC                        | VDC=30V; V <sub>EN</sub> =0V                |            |      |      | 2               | mΑ           |

| V <sub>VDD(reg)</sub>                     | Regulated voltage on pin VDD                           | VDC=30V; V <sub>EN</sub> =0V                |            | 11.3 | 12   | 12.7            | V            |

| V <sub>VDD(reg)</sub>                     | Regulated voltage on pin VDD at maximum supply current | non-oscillating; I <sub>VDD</sub> =-36mA    |            | 11   |      |                 | V            |

| $V_{VDC}$ - $V_{VDD}$                     | Dropout voltage VDD regulator                          | VDC=10V; oscillating;                       | <u>[1]</u> |      | 1.5  |                 | V            |

| V <sub>boot</sub>                         | voltage drop bootstrap diode                           | I <sub>FSA</sub> = I <sub>FSB</sub> = 5mA   |            |      | 1.5  |                 | V            |

| Ignition                                  |                                                        |                                             |            |      |      |                 |              |

| F <sub>s(max)</sub> / F <sub>s(min)</sub> | VCO frequency ratio                                    |                                             |            | 2.2  | 2.4  | 2.6             |              |

| V <sub>CVFB(range)</sub>                  | VCO voltage range                                      |                                             |            |      | 2.5  |                 | V            |

| I <sub>CVFB(charge)</sub>                 | CVFB charge current                                    | V <sub>VFB</sub> =2V, V <sub>CVFB</sub> =2V |            | -24  | -21  | -18             | μΑ           |

| JBA2072                                   |                                                        |                                             |            |      | © NX | P B.V. 2007. AI | I rights res |

# Low Voltage Full-bridge control IC for CCFL backlighting

Table 5: Characteristics ...continued

$T_{amb}$  = 25 °C;  $V_{VDC}$  = 15 V;  $V_{EN}$ = $V_{VDD}$ ;  $C_{VDD}$ =100nF;  $R_{IREF}$  = 33 k $\Omega$  and CPWM pin connected to a capacitor, unless otherwise specified. All voltages are measured with respect to signal ground (pin 7); currents are positive when flowing into the IC.

| uie io.                      |                                                      |                                                                                               |      |       |      |      |

|------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|-------|------|------|

| Symbol                       | Parameter                                            | Conditions                                                                                    | Min  | Тур   | Max  | Unit |

| Normal operatio              | n                                                    |                                                                                               |      |       |      |      |

| F <sub>s(min)</sub>          | minimum switching frequency                          | C <sub>CF</sub> = 100 pF                                                                      | 43.0 | 44.8  | 46.6 | kHz  |

| F <sub>s(min)</sub>          | minimum switching frequency                          |                                                                                               | 10   |       | 100  | kHz  |

| V <sub>IFB(reg)</sub>        | current regulation reference<br>level                |                                                                                               | 1.24 | 1.32  | 1.40 | V    |

| $V_{IFB(min)}$               | minimum voltage of lineair operating range           |                                                                                               |      | - 2.5 |      | V    |

| V <sub>IFB(max)</sub>        | maximum voltage of linear operating range            |                                                                                               |      | 2.5   |      | V    |

| R <sub>IFB</sub>             | input impedance IFB pin                              | V <sub>IFB</sub> = 1V                                                                         |      | 40    |      | kΩ   |

| R <sub>IFB</sub>             | input impedance IFB pin                              | V <sub>IFB</sub> = -1V                                                                        |      | 20    |      | kΩ   |

| K <sub>IFB</sub>             | transconductance OTA                                 |                                                                                               | 13   | 16    | 19   | μA/V |

| Drivers                      |                                                      |                                                                                               |      |       |      |      |

| I <sub>driver</sub> (source) | sourcing current of drivers                          | $V_{GLA}$ , $V_{GLB}$ , $V_{GHA}$ , $V_{GHB}$ = 1V, $V_{VDD}$ = $V_{FSA}$ = $V_{FSB}$ =12V    | -180 | -145  | -110 | mA   |

| R <sub>driver(sink)</sub>    | sinking resistance of drivers                        | $V_{GLA}$ , $V_{GLB}$ , $V_{GHA}$ , $V_{GHB}$ = 1V,<br>$V_{VDD}$ = $V_{FSA}$ = $V_{FSB}$ =12V |      |       | 7.3  | Ω    |

| T <sub>nonov</sub>           | non-overlap time                                     |                                                                                               | 0.45 | 0.55  | 0.65 | μs   |

| PWM dimming                  |                                                      |                                                                                               |      |       |      |      |

| F <sub>PWM</sub>             | PWM frequency                                        |                                                                                               | 100  |       | 1000 | Hz   |

| F <sub>PWM</sub>             | PWM frequency                                        | C <sub>CPWM</sub> = 33 nF                                                                     | 308  | 324   | 340  | Hz   |

| $\Delta \phi_{(min)}$        | minimum phase shift                                  |                                                                                               |      | 0     |      | 0    |

| $\Delta \phi_{(max)}$        | maximum phase shift                                  |                                                                                               |      | 180   |      | 0    |

| V <sub>CSWP(low)</sub>       | CSWP voltage resulting in $\Delta \phi_{(min)}$      |                                                                                               |      | 1     |      | V    |

| V <sub>CSWP(high)</sub>      | CSWP voltage resulting in $\Delta \phi_{(max)}$      |                                                                                               |      | 3     |      | V    |

| V <sub>CIFB(hclamp)</sub>    | high CIFB clamp voltage                              |                                                                                               |      | 3.1   |      | V    |

| V <sub>CSWP(Iclamp)</sub>    | low CSWP clamp voltage                               |                                                                                               |      | 0.95  |      | V    |

| I <sub>CSWP(charge)</sub>    | CSWP charge current                                  |                                                                                               | -24  | -21   | -18  | μΑ   |

| I <sub>CSWP(discharge)</sub> | CSWP discharge current                               |                                                                                               | 18   | 21    | 24   | μΑ   |

| R <sub>PWMa</sub>            | input impedance PWMa pin                             |                                                                                               |      | 100   |      | kΩ   |

| V <sub>PWMa(min)</sub>       | input voltage on PWMa pin for minimum PWM duty cycle |                                                                                               |      | 1.24  |      | V    |

| V <sub>PWMa(max)</sub>       | input voltage on PWMa pin for maximum PWM duty cycle |                                                                                               |      | 3     |      | V    |

| D <sub>PWM(min,intern)</sub> | minimum PWM duty cycle                               |                                                                                               | [2]  | 12    |      | %    |

| D <sub>PWM(min,extern)</sub> | minimum PWM duty cycle                               | CPWM pin connected to SGND                                                                    | [2]  | 0     |      | %    |

| D <sub>PWM(max)</sub>        | maximum PWM duty cycle                               |                                                                                               | [2]  | 100   |      | %    |

| I <sub>PWMD(source)</sub>    | source capability PWMd output                        | V <sub>PWMd</sub> =3V                                                                         |      | -1    |      | mA   |

| I <sub>PWMD(sink)</sub>      | sink capability PWMd output                          | V <sub>PWMd</sub> =1V                                                                         |      | 1     |      | mA   |

#### Low Voltage Full-bridge control IC for CCFL backlighting

Table 5: Characteristics ...continued

| Symbol                          | Parameter                                  | Conditions                                                        | Min   | Тур   | Max   | Unit                            |

|---------------------------------|--------------------------------------------|-------------------------------------------------------------------|-------|-------|-------|---------------------------------|

| $V_{PWMD(high)}$                | logic high input level on PWMd             |                                                                   |       |       | 1.7   | s<br>ing into<br>Unit<br>V<br>V |

| V <sub>PWMD(low)</sub>          | logic low input level onPWMd               |                                                                   | 0.85  |       |       | V                               |

| Protections                     |                                            |                                                                   |       |       |       |                                 |

| V <sub>VFB(ovref)</sub>         | over voltage reference level               |                                                                   | 2.40  | 2.52  | 2.64  | V                               |

| I <sub>CVFB(ov)</sub>           | CVFB discharge current                     | V <sub>VFB</sub> >V <sub>VFB(ovref)</sub> , V <sub>CVFB</sub> =2V | 18    | 21    | 24    | μΑ                              |

| V <sub>IFB(lampon)</sub>        | lamp on detection level                    |                                                                   |       | 0.9   |       | V                               |

| V <sub>IFB(ocref)</sub>         | over current reference level               |                                                                   | 2.65  | 3.0   | 3.3   | V                               |

| V <sub>IFB(arcref)</sub>        | minimum detectable arcing spike amplitude  |                                                                   |       | 5     |       | V                               |

| T <sub>SPIKE(min)</sub>         | minimum detectable arcing spike duration   |                                                                   |       | 200   |       | ns                              |

| T <sub>fault(delay)</sub>       | fault output delay time                    | C <sub>CT</sub> = 100 nF                                          | 0.063 | 0.069 | 0.075 | s                               |

| T <sub>fault(stop)</sub>        | fault stop time                            | C <sub>CT</sub> = 100 nF                                          | 0.85  | 0.95  | 1.05  | s                               |

| V <sub>nonFAULT(open)</sub>     | open pin voltage on nonFAULT               |                                                                   | 4.7   | 5.0   | 5.3   | V                               |

| V <sub>nonFAULT</sub> (trigger) | input trigger voltage on pin<br>nonFAULT   |                                                                   | 3.8   | 4.3   | 4.8   | V                               |

| I <sub>nonFAULT(trigger)</sub>  | input trigger current of nonFAULT pin      |                                                                   | -32   | -27   | -22   | μΑ                              |

| I <sub>nonFAULT(3V)</sub>       | low input nonFAULT pin current             | V <sub>nonFAULT</sub> = 3V                                        | -220  | -190  | -160  | μΑ                              |

| I <sub>nonFAULT(short)</sub>    | short circuit current on pin nonFAULT      | $V_{\text{nonFAULT}} = 0V$                                        | -240  | -210  | -180  | μΑ                              |

| I <sub>nonFAULT(sink)</sub>     | maximum low output current on pin nonFAULT | V <sub>nonFAULT</sub> = 1V                                        | 0.75  | 1     | 1.5   | mA                              |

| Chip enable leve                | els                                        |                                                                   |       |       |       |                                 |

| V <sub>EN(high)</sub>           | logic high level on pin EN                 |                                                                   |       |       | 1.7   | V                               |

| V <sub>EN(low)</sub>            | logic low level on pin EN                  |                                                                   | 0.9   |       |       | V                               |

<sup>[1]</sup> GLA, GLB, GHA and GHB open.

# 11. Application information

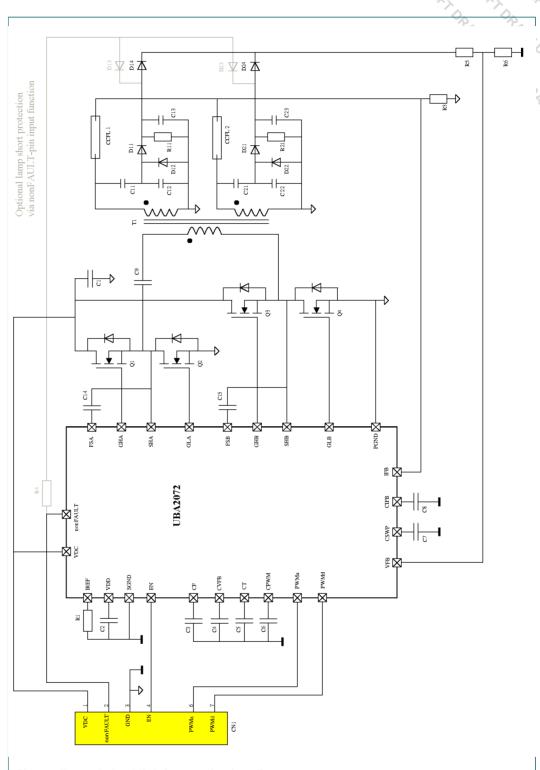

Figure 16 shows an example backlighting configuration, where the inverter and the IC are supplied from the same DC voltage. Two lamp are connected, each to another output of the same transformer. The leakage inductances of this transformer provides the ballast impedances for the lamp. An analogue voltage is converted to a PWM signal to provide for the desired brightness level. Optional lamp short detection is via the lamp voltage sensing and D13, D23 and the nonFAULT-pin is indicated.

PWMd is active low: A low level on the PWMd pin corresponds with lamps on. Example: DPWM=20% means PMWd is during 20% of each cyle low and the lamps are 20% of the time on, resulting in een light output of 20%.

**UBA2072**

# Low Voltage Full-bridge control IC for CCFL backlighting

Fig 16. Example backlighting application diagram

# 12. Test information

### 12.1 Quality information

The General Quality Specification for Integrated Circuits, SNW-FQ-611 is applicable.

# 13. Package outline

SOT136-1

#### Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE  |        | REFER    | RENCES | EUROPEAN   | ISSUE DATE                       |

|----------|--------|----------|--------|------------|----------------------------------|

| VERSION  | IEC    | JEDEC    | EIAJ   | PROJECTION | ISSUE DATE                       |

| SOT136-1 | 075E06 | MS-013AE |        |            | <del>-95-01-24</del><br>97-05-22 |

Fig 17. Package outline SO28 (SOT136-1)

#### SSOP28: plastic shrink small outline package; 28 leads; body width 5.3 mm

#### Note

1. Plastic or metal protrusions of 0.20 mm maximum per side are not included.

|      |            | ISSUE DATE                      |  |

|------|------------|---------------------------------|--|

| EIAJ | PROJECTION | ISSUE DATE                      |  |

| АН   |            | <del>93-09-08</del><br>95-02-04 |  |

|      | C EIAJ     | C EIAJ                          |  |

Fig 18. Package outline SSOP28 (SOT341-1)

### 14. Soldering

#### 14.1 Introduction

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our *Data Handbook IC26; Integrated Circuit Packages* (document order number 9398 652 90011).

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mount components are mixed on one printed-circuit board. Wave soldering can still be used for certain surface mount ICs, but it is not suitable for fine pitch SMDs. In these situations reflow soldering is recommended. Driven by legislation and environmental forces the worldwide use of lead-free solder pastes is increasing.

#### 14.2 Through-hole mount packages

#### 14.2.1 Soldering by dipping or by solder wave

Typical dwell time of the leads in the wave ranges from 3 to 4 seconds at 250 °C or 265 °C, depending on solder material applied, SnPb or Pb-free respectively.

The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature  $(T_{stg(max)})$ . If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### 14.2.2 Manual soldering

Apply the soldering iron (24 V or less) to the lead(s) of the package, either below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300  $^{\circ}$ C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400  $^{\circ}$ C, contact may be up to 5 seconds.

#### 14.3 Surface mount packages

#### 14.3.1 Reflow soldering

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example, convection or convection/infrared heating in a conveyor type oven. Throughput times (preheating, soldering and cooling) vary between 100 and 200 seconds depending on heating method.

Typical reflow peak temperatures range from 215 to 270 °C depending on solder paste material. The top-surface temperature of the packages should preferably be kept:

- below 225 °C (SnPb process) or below 245 °C (Pb-free process)

- for all the BGA and SSOP-T packages

#### Low Voltage Full-bridge control IC for CCFL backlighting

- for packages with a thickness ≥ 2.5 mm

- for packages with a thickness < 2.5 mm and a volume ≥ 350 mm<sup>3</sup> so called thick/large packages.

- below 240 °C (SnPb process) or below 260 °C (Pb-free process) for packages with a thickness < 2.5 mm and a volume < 350 mm<sup>3</sup> so called small/thin packages.

Moisture sensitivity precautions, as indicated on packing, must be respected at all times.

#### 14.3.2 Wave soldering

Conventional single wave soldering is not recommended for surface mount devices (SMDs) or printed-circuit boards with a high component density, as solder bridging and non-wetting can present major problems.

To overcome these problems the double-wave soldering method was specifically developed.

If wave soldering is used the following conditions must be observed for optimal results:

- Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a smooth laminar wave.

- For packages with leads on two sides and a pitch (e):

- larger than or equal to 1.27 mm, the footprint longitudinal axis is preferred to be parallel to the transport direction of the printed-circuit board;

- smaller than 1.27 mm, the footprint longitudinal axis must be parallel to the transport direction of the printed-circuit board.

The footprint must incorporate solder thieves at the downstream end.

• For packages with leads on four sides, the footprint must be placed at a 45° angle to the transport direction of the printed-circuit board. The footprint must incorporate solder thieves downstream and at the side corners.

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Typical dwell time of the leads in the wave ranges from 3 to 4 seconds at 250 °C or 265 °C, depending on solder material applied, SnPb or Pb-free respectively.

A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

#### 14.3.3 Manual soldering

Fix the component by first soldering two diagonally-opposite end leads. Use a low voltage (24 V or less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C.

When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320  $^{\circ}$ C.

#### 14.4 Package related soldering information

Table 6. Suitability of IC packages for wave, reflow and dipping soldering methods

| Low Voltage Full-bridge control IC for CCFL backlight  Package related soldering information  Table 6. Suitability of IC packages for wave, reflow and dipping soldering methods  Mounting Package[1] Soldering method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 072     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Table 6. Suitability of IC packages for wave, reflow and dipping soldering methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ighting |

| A The state of the | PASS    |

| mounting i dokage Journal incline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| Wave Reflow[2] Dippin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | pping   |

| Through-hole DBS, DIP, HDIP, RDBS, suitable — suitable mount SDIP, SIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | table   |

| Through-hole- PMFP <sup>[4]</sup> not suitable not – suitable suitable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

| Surface mount BGA, LBGA, LFBGA, not suitable suitable – SQFP, SSOP-T <sup>[5]</sup> , TFBGA, VFBGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |