Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **USB Dual-Port Power Switch and Current Monitor**

#### **Features**

- · Dual-Port Power Switches:

- 2.9V to 5.5V source voltage range

- 3.0A continuous current per  $V_{BUS}$  port with 18 m $\Omega$  On resistance per switch

- Independent port power switch enable pins

- DUAL fault ALERT# active drain output pins

- Constant Current or Trip mode current limiting behaviors

- Undervoltage and overvoltage lockout

- Back-drive, back-voltage protection

- Auto-recovery fault handling with low test current

- BOOST# logic output to increase DC-DC converter output under large load conditions

- SMBus 2.0/I<sup>2</sup>C Mode Features:

- Eight programmable current limits assignable to each power switch

- Other SMBus addresses available upon request

- Block read and block write

- Self-Contained Current Monitoring (No External Sense Resistor Required)

- Fully Programmable Per-Port Charge Rationing and Behaviors

- Configurable Per-Port BC1.2 V<sub>BUS</sub> Discharge Function

- · Wide Operating Temperature Range:

- -40°C to +105°C

#### **Description**

The UCS2114 is a dual USB port power switch configuration that can provide 3.0A continuous current (3.4A maximum) per  $V_{BUS}$  port with precision overcurrent limiting (OCL), port power switch enables, auto-recovery fault handling, undervoltage and overvoltage lockout, back-drive and back-voltage protection, and thermal protection.

The UCS2114 is well-suited for both stand-alone and applications having SMBus/l<sup>2</sup>C communications.

For applications with SMBus, the UCS2114 provides per-port current monitoring and eight programmable current limits per switch, ranging from 0.53A to 3.0A continuous current (3.4A maximum). Per-port charge rationing is also provided, ranging from 3.8 mAh to 246.3 Ah.

In Stand-Alone mode, the UCS2114 provides eight current limits for both switches, ranging from 0.53A + 0.53A to 3A + 3A total continuous current (see Table 1-1).

Both power switches include an independent  $V_{BUS}$  discharge function and Constant Current mode limiting for BC1.2 applications.

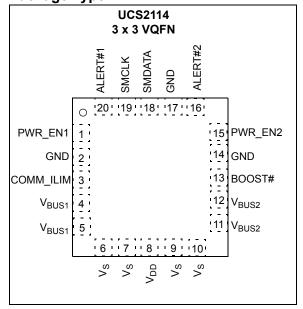

The UCS2114 is available in a 3x3 mm 20-pin VQFN package.

#### Package Type

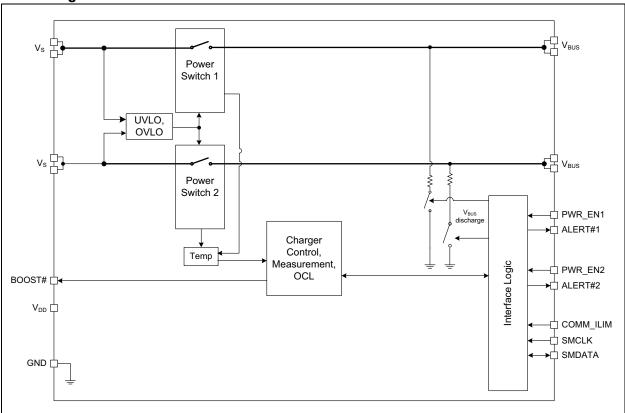

## **Block Diagram**

# 1.0 ELECTRICAL CHARACTERISTICS

### **Absolute Maximum Ratings †**

| Voltage on V <sub>DD</sub> , V <sub>S</sub> and V <sub>BUS</sub> pins | –0.3 to 6V                    |

|-----------------------------------------------------------------------|-------------------------------|

| Pull-Up Voltage (V <sub>PULLUP</sub> )                                | 0.3 to V <sub>DD</sub> + 0.3  |

| Port Power Switch Current                                             | Internally limited            |

| Voltage on any Other Pin to Ground                                    | 0.3 to V <sub>DD</sub> + 0.3V |

| Current on any Other Pin                                              | ±10 mA                        |

| Operating Ambient Temperature Range                                   | 40°C to +105°C                |

| Storage Temperature Range                                             | –55°C to +150°C               |

**† Notice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### TABLE 1-1: ELECTRICAL SPECIFICATIONS

**Electrical Characteristics:** Unless otherwise specified,  $V_{DD}$  = 4.5V to 5.5V,  $V_S$  = 2.9V to 5.5V,  $V_{PULLUP}$  = 3V to 5.5V,  $T_A$  = -40°C to 105°C. All typical values at  $V_{DD}$  =  $V_S$  = 5V,  $T_A$  = 27°C.

| 1 OLLO1                                                                                                |                         | ٠.   |      | 00   |      | <b>1</b>                                              |

|--------------------------------------------------------------------------------------------------------|-------------------------|------|------|------|------|-------------------------------------------------------|

| Characteristic                                                                                         | Symbol                  | Min. | Тур. | Max. | Unit | Conditions                                            |

| Power and Interrupts - DC                                                                              |                         |      |      |      |      |                                                       |

| Supply Voltage                                                                                         | $V_{DD}$                | 4.5  | 5    | 5.5  | V    |                                                       |

| Supply Current in Active (I <sub>DD_ACT</sub> + I <sub>S1_ACT</sub> + I <sub>S2_ACT</sub> )            | I <sub>ACTIVE</sub>     | _    | 700  | _    | μА   | Average current I <sub>BUS</sub> = 0 mA               |

| Supply Current in Sleep<br>(I <sub>DD_SLEEP</sub> + I <sub>S1_SLEEP</sub> +<br>I <sub>S2_SLEEP</sub> ) | I <sub>SLEEP</sub>      | _    | 6    | 20   | μА   | Average current V <sub>PULLUP</sub> ≤ V <sub>DD</sub> |

| Power-on Reset                                                                                         |                         |      |      |      |      |                                                       |

| V <sub>DD</sub> Low Threshold                                                                          | $V_{DD\_TH}$            | _    | 4    | 4.3  | V    | V <sub>DD</sub> voltage increasing (Note 1)           |

| V <sub>DD</sub> Low Hysteresis                                                                         | V <sub>DD_TH_HYST</sub> | _    | 500  | 600  | mV   | V <sub>DD</sub> voltage decreasing (Note 1)           |

**Note 1:** This parameter is characterized, not 100% tested.

- 2: This parameter is ensured by design and not 100% tested.

- 3: The current measurement full scale range maximum value is 3.4A. However, the UCS2114 cannot report values above I<sub>LIM</sub> (if I<sub>BUS\_R2MIN</sub> ≤ I<sub>LIM</sub>) or above I<sub>BUS\_R2MIN</sub> (if I<sub>BUS\_R2MIN</sub> > I<sub>LIM</sub> and I<sub>LIM</sub> ≤ 1.6A).

TABLE 1-1: ELECTRICAL SPECIFICATIONS (CONTINUED)

**Electrical Characteristics:** Unless otherwise specified,  $V_{DD}$  = 4.5V to 5.5V,  $V_{S}$  = 2.9V to 5.5V,  $V_{PULLUP}$  = 3V to 5.5V,  $V_{A}$  = -40°C to 105°C. All typical values at  $V_{DD}$  =  $V_{S}$  = 5V,  $V_{A}$  = 27°C.

| $V_{\text{PULLUP}} = 3V \text{ to 5.5V}, I_{\text{A}} = -2$ |                         | 1       | 1      |          | 1      | <u>-</u>                                                                  |

|-------------------------------------------------------------|-------------------------|---------|--------|----------|--------|---------------------------------------------------------------------------|

| Characteristic                                              | Symbol                  | Min.    | Тур.   | Max.     | Unit   | Conditions                                                                |

| I/O Pins - SMCLK, SMDATA                                    |                         | RT#, BC | OST# - | DC Parar | neters |                                                                           |

| Output Low Voltage                                          | V <sub>OL</sub>         | _       | _      | 0.4      | V      | I <sub>SINK_IO</sub> = 8 mA<br>SMDATA, ALERT#, BOOST#                     |

| Input High Voltage                                          | V <sub>IH</sub>         | 2.0     | _      | _        | V      | PWR_EN, SMDATA, SMCLK                                                     |

| Input Low Voltage                                           | V <sub>IL</sub>         | _       | _      | 0.8      | V      | PWR_EN, SMDATA, SMCLK                                                     |

| Leakage Current                                             | I <sub>LEAK</sub>       | _       | _      | ±5       | μA     | Powered or unpowered $V_{PULLUP} \le V_{DD}$ $T_A < 85^{\circ}C$ (Note 1) |

| Interrupt Pins - AC Parame                                  | ters                    |         |        |          |        |                                                                           |

| ALERT# Pin Blanking Time                                    | t <sub>BLANK</sub>      | _       | 25     | _        | ms     | Blanking time, coming out of reset                                        |

| ALERT# Pin Interrupt<br>Masking Time                        | t <sub>MASK</sub>       | _       | 5      |          | ms     |                                                                           |

| BOOST# Pin Minimum<br>Assertion Time                        | t <sub>BOOST_MAT</sub>  | _       | 1      | _        | S      |                                                                           |

| BOOST# Pin Assertion<br>Current                             | I <sub>BOOST</sub>      | _       | 1.9    | _        | Α      |                                                                           |

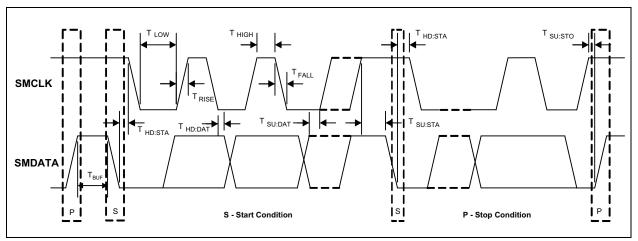

| SMBus/I <sup>2</sup> C Timing                               |                         |         |        |          |        |                                                                           |

| Input Capacitance                                           | C <sub>IN</sub>         | _       | 5      | _        | pF     |                                                                           |

| Clock Frequency                                             | f <sub>SMB</sub>        | 10      | _      | 400      | kHz    |                                                                           |

| Spike Suppression                                           | t <sub>SP</sub>         | _       | _      | 50       | ns     |                                                                           |

| Bus Free Time Stop to Start                                 | t <sub>BUF</sub>        | 1.3     | _      | _        | μs     |                                                                           |

| Start Setup Time                                            | t <sub>SU:STA</sub>     | 0.6     |        | _        | μs     |                                                                           |

| Start Hold Time                                             | t <sub>HD:STA</sub>     | 0.6     |        |          | μs     |                                                                           |

| Stop Setup Time                                             | t <sub>SU:STO</sub>     | 0.6     |        | _        | μs     |                                                                           |

| Data Hold Time                                              | t <sub>HD:DAT</sub>     | 0       | _      | _        | μs     | When transmitting to the master                                           |

| Data Hold Time                                              | t <sub>HD:DAT</sub>     | 0.3     |        | _        | μs     | When receiving from the master                                            |

| Data Setup Time                                             | t <sub>SU:DAT</sub>     | 0.6     | _      | _        | μs     |                                                                           |

| Clock Low Period                                            | t <sub>LOW</sub>        | 1.3     |        | _        | μs     |                                                                           |

| Clock High Period                                           | t <sub>HIGH</sub>       | 0.6     |        |          | μs     |                                                                           |

| Clock/Data Fall Time                                        | t <sub>FALL</sub>       | _       | _      | 300      | ns     | Min. = 20+0.1C <sub>LOAD</sub> ns<br>(Note 1)                             |

| Clock/Data Rise Time                                        | t <sub>RISE</sub>       |         | _      | 300      | ns     | Min. = 20+0.1C <sub>LOAD</sub> ns<br>(Note 1)                             |

| Capacitive Load                                             | C <sub>LOAD</sub>       |         |        | 400      | pF     | Per bus line (Note 1)                                                     |

| Time Out                                                    | t <sub>TIMEOUT</sub>    | 25      | _      | 35       | ms     | Disabled by default (Note 1)                                              |

| Idle Reset                                                  | t <sub>IDLE_RESET</sub> | 350     |        | _        | μs     | Disabled by default (Note 1)                                              |

Note 1: This parameter is characterized, not 100% tested.

<sup>2:</sup> This parameter is ensured by design and not 100% tested.

<sup>3:</sup> The current measurement full scale range maximum value is 3.4A. However, the UCS2114 cannot report values above  $I_{LIM}$  (if  $I_{BUS\_R2MIN} \le I_{LIM}$ ) or above  $I_{BUS\_R2MIN}$  (if  $I_{BUS\_R2MIN} > I_{LIM}$  and  $I_{LIM} \le 1.6A$ ).

TABLE 1-1: ELECTRICAL SPECIFICATIONS (CONTINUED)

**Electrical Characteristics:** Unless otherwise specified,  $V_{DD}$  = 4.5V to 5.5V,  $V_S$  = 2.9V to 5.5V,  $V_{PULLUP}$  = 3V to 5.5V,  $T_A$  = -40°C to 105°C. All typical values at  $V_{DD}$  =  $V_S$  = 5V,  $T_A$  = 27°C.

| Characteristic                            | Symbol                   | Min. | Тур. | Max. | Unit | Conditions                                                                                                                                                          |  |  |

|-------------------------------------------|--------------------------|------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Port Power Switch                         | •                        |      |      |      |      |                                                                                                                                                                     |  |  |

| Port Power Switch - DC Parameter          |                          |      |      |      |      |                                                                                                                                                                     |  |  |

| Overvoltage Lockout                       | V <sub>S_OV</sub>        | _    | 6    | _    | V    | Note 2                                                                                                                                                              |  |  |

| V <sub>S</sub> Low Threshold              | V <sub>S_UVLO</sub>      | _    | 2.5  | _    | V    | Note 2                                                                                                                                                              |  |  |

| V <sub>S</sub> Low Hysteresis             | V <sub>S_UVLO_HYST</sub> | _    | 100  | _    | mV   | Note 2                                                                                                                                                              |  |  |

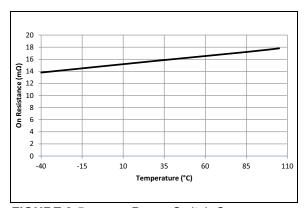

| On Resistance                             | R <sub>ON_PSW</sub>      | _    | 18   | 30   | mΩ   | 4.75V < V <sub>S</sub> < 5.25V                                                                                                                                      |  |  |

| V <sub>S</sub> Leakage Current            | I <sub>LEAK_VS</sub>     | _    | _    | 5    | μA   | Sleep state into V <sub>S</sub> pin on one channel ( <b>Note 1</b> )                                                                                                |  |  |

| Back-Voltage Protection<br>Threshold      | V <sub>BV_TH</sub>       | _    | 150  |      | mV   | V <sub>BUS</sub> > V <sub>S</sub><br>V <sub>S</sub> > V <sub>S_UVLO</sub>                                                                                           |  |  |

| Leakage Current                           | I <sub>LKG_1</sub>       | _    | 0    | 3    | μА   | $\begin{aligned} &V_{DD} < V_{DD\_TH}, \\ &Leakage \ current \ from \ V_{BUS} \ pins \\ &to \ the \ V_{DD} \ and \ the \ V_{S} \ pins \\ &(Note \ 1) \end{aligned}$ |  |  |

|                                           | I <sub>LKG_2</sub>       | _    | 0    | 2    | μА   | $V_{DD} > V_{DD\_TH}$ ,<br>Leakage current from $V_{BUS}$ pins<br>to the $V_{S}$ pins, when the power<br>switch is open                                             |  |  |

| Selectable Current Limits                 | I <sub>LIM1</sub>        | _    | 530  |      | mA   | $I_{LIM}$ Resistor = 0 or 47 kΩ (530 mA setting)                                                                                                                    |  |  |

|                                           | I <sub>LIM2</sub>        | _    | 960  |      | mA   | $I_{LIM}$ Resistor = 10 kΩ or 56 kΩ (960 mA setting)                                                                                                                |  |  |

|                                           | I <sub>LIM3</sub>        | _    | 1070 | 1    | mA   | $I_{LIM}$ Resistor = 12 kΩ or 68 kΩ (1070 mA setting)                                                                                                               |  |  |

|                                           | I <sub>LIM4</sub>        | _    | 1280 | 1    | mA   | $I_{LIM}$ Resistor = 15 kΩ or 82 kΩ (1280 mA setting)                                                                                                               |  |  |

|                                           | I <sub>LIM5</sub>        | _    | 1600 | _    | mA   | $I_{LIM}$ Resistor = 18 kΩ or 100 kΩ (1600 mA setting)                                                                                                              |  |  |

|                                           | I <sub>LIM6</sub>        | _    | 2130 | _    | mA   | $I_{LIM}$ Resistor = 22 kΩ or 120 kΩ (2130 mA setting)                                                                                                              |  |  |

|                                           | I <sub>LIM7</sub>        | 2500 | 2670 | 2900 | mA   | $I_{LIM}$ Resistor = 27 kΩ or 150 kΩ (2670 mA setting)                                                                                                              |  |  |

|                                           | I <sub>LIM8</sub>        | 3000 | 3200 | 3400 | mA   | $I_{LIM}$ Resistor = 33 kΩ or $V_{DD}$ (3200 mA setting)                                                                                                            |  |  |

| Pin Wake Time                             | t <sub>PIN_WAKE</sub>    | _    | 3    | _    | ms   |                                                                                                                                                                     |  |  |

| SMBus Wake Time                           | t <sub>SMB_WAKE</sub>    | _    | 4    | _    | ms   |                                                                                                                                                                     |  |  |

| Idle Sleep Time                           | t <sub>IDLE_SLEEP</sub>  | _    | 200  | _    | ms   |                                                                                                                                                                     |  |  |

| First Thermal Shutdown<br>Stage Threshold | T <sub>TSD_LOW</sub>     | _    | 120  | _    | °C   | Die Temperature at which the power switch will open if it is in Constant Current mode                                                                               |  |  |

Note 1: This parameter is characterized, not 100% tested.

<sup>2:</sup> This parameter is ensured by design and not 100% tested.

The current measurement full scale range maximum value is 3.4A. However, the UCS2114 cannot report values above  $I_{LIM}$  (if  $I_{BUS\_R2MIN} \le I_{LIM}$ ) or above  $I_{BUS\_R2MIN}$  (if  $I_{BUS\_R2MIN} > I_{LIM}$  and  $I_{LIM} \le 1.6A$ ).

TABLE 1-1: ELECTRICAL SPECIFICATIONS (CONTINUED)

**Electrical Characteristics:** Unless otherwise specified,  $V_{DD}$  = 4.5V to 5.5V,  $V_{S}$  = 2.9V to 5.5V,  $V_{PULLUP}$  = 3V to 5.5V,  $V_{A}$  = -40°C to 105°C. All typical values at  $V_{DD}$  =  $V_{S}$  = 5V,  $V_{A}$  = 27°C.

| Characteristic                              | Symbol                        | Min. | Тур. | Max. | Unit  | Conditions                                                                                                                                 |

|---------------------------------------------|-------------------------------|------|------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| First Thermal Shutdown<br>Stage Hysteresis  | T <sub>TSD_LOW_HYST</sub>     | _    | 10   | _    | °C    | Hysteresis for T <sub>TSD_LOW</sub> functionality. Temperature must drop by this value before any of the power switches can be closed.     |

| Second Thermal Shutdown<br>Stage Threshold  | T <sub>TSD_HIGH</sub>         | _    | 135  |      | °C    | Die Temperature at which both power switches will open                                                                                     |

| Second Thermal Shutdown<br>Stage Hysteresis | T <sub>TSD_HIGH_HYST</sub>    | _    | 25   |      | °C    | Hysteresis for T <sub>TSD_HIGH</sub> functionality. Temperature must drop by this value before any of the power switches can be closed.    |

| Auto-Recovery Test Current                  | I <sub>TEST</sub>             | _    | 190  |      | mA    | Portable device attached,<br>V <sub>BUS</sub> = 0 V, Die temp < T <sub>TSD</sub>                                                           |

| Auto-Recovery Test Voltage                  | V <sub>TEST</sub>             | _    | 750  | I    | mV    | Portable device attached, V <sub>BUS</sub> = 0 V before application, Die temp < T <sub>TSD</sub> Programmable, 250-1000 mV, default listed |

| Discharge Impedance                         | R <sub>DISCHARGE</sub>        | _    | 100  |      | Ω     |                                                                                                                                            |

| Port Power Switch - AC Par                  | rameters                      |      |      |      |       |                                                                                                                                            |

| Turn-on Delay                               | t <sub>ON_PSW</sub>           | _    | 0.9  |      | ms    | PWR_EN active toggle to switch on time, V <sub>BUS</sub> discharge not active                                                              |

| Turn-off Time                               | toff_psw_ina                  | _    | 0.75 | _    | ms    | PWR_EN inactive toggle to switch off time C <sub>BUS</sub> = 120 μF                                                                        |

| Turn-off Time                               | t <sub>OFF_PSW_ERR</sub>      | _    | 1    | _    | ms    | Overcurrent Error, V <sub>BUS</sub> Min<br>Error, or Discharge Error to<br>switch off<br>C <sub>BUS</sub> = 120 µF                         |

| Turn-off Time                               | t <sub>OFF_PSW_ERR1</sub>     | _    | 100  | _    | ns    | TSD or Back-drive Error to switch off C <sub>BUS</sub> = 120 µF                                                                            |

| V <sub>BUS</sub> Output Rise Time           | t <sub>R_BUS</sub>            | _    | 1.1  | _    | ms    | Measured from 10% to 90% of $V_{BUS}$ , $C_{LOAD}$ = 220 $\mu$ F $I_{LIM}$ = 1.0A                                                          |

| Soft Turn-On Rate                           | $\Delta I_{BUS} / \Delta_{t}$ | _    | 100  | _    | mΑ/μs |                                                                                                                                            |

| Temperature Update Time                     | t <sub>DC_TEMP</sub>          | _    | 200  | _    | ms    |                                                                                                                                            |

| Short-Circuit Response Time                 | tshort_lim                    | _    | 1.5  | _    | μs    | Time from detection of short to current limit applied. No C <sub>BUS</sub> applied                                                         |

| Short-Circuit Detection Time                | t <sub>SHORT</sub>            | _    | 6    | _    | ms    | Time from detection of short to port power switch disconnect and ALERT# pin assertion                                                      |

Note 1: This parameter is characterized, not 100% tested.

<sup>2:</sup> This parameter is ensured by design and not 100% tested.

<sup>3:</sup> The current measurement full scale range maximum value is 3.4A. However, the UCS2114 cannot report values above  $I_{LIM}$  (if  $I_{BUS\_R2MIN} \le I_{LIM}$ ) or above  $I_{BUS\_R2MIN}$  (if  $I_{BUS\_R2MIN} > I_{LIM}$  and  $I_{LIM} \le 1.6A$ ).

TABLE 1-1: ELECTRICAL SPECIFICATIONS (CONTINUED)

**Electrical Characteristics:** Unless otherwise specified,  $V_{DD}$  = 4.5V to 5.5V,  $V_S$  = 2.9V to 5.5V,  $V_{PULLUP}$  = 3V to 5.5V,  $V_A$  = -40°C to 105°C. All typical values at  $V_{DD}$  =  $V_S$  = 5V,  $V_A$  = 27°C.

| Characteristic                                | Symbol                   | Min.     | Тур.       | Max.       | Unit     | Conditions                                                                                                          |

|-----------------------------------------------|--------------------------|----------|------------|------------|----------|---------------------------------------------------------------------------------------------------------------------|

| Latched Mode Cycle Time                       | t <sub>UL</sub>          | _        | 7          | ı          | ms       | From PWR_EN edge transition from inactive to active to begin error recovery.                                        |

| Auto-Recovery Mode Cycle<br>Time              | <sup>t</sup> cycle       |          | 25         | 1          | ms       | Time delay before error condition check. Programmable 15-50 ms, default listed.                                     |

| Auto-Recovery Delay                           | t <sub>TST</sub>         |          | 20         | 1          | ms       | Portable device attached, $V_{BUS}$ must be $\geq V_{TEST}$ after this time. Programmable 10-25 ms, default listed. |

| Discharge Time                                | <sup>†</sup> DISCHARGE   | _        | 200        | 1          | ms       | Amount of time discharge resistor applied. Programmable 100-400 ms, default listed.                                 |

| Port Power Switch Operation                   | on with Trip Mod         | le Curre | nt Limiti  | ing        |          |                                                                                                                     |

| Region 2 Current<br>Keep-Out                  | I <sub>BUS_R2MIN_1</sub> | _        | _          | 0.1        | Α        | Note 2                                                                                                              |

| Minimum V <sub>BUS</sub><br>Allowed at Output | V <sub>BUS_MIN_1</sub>   | 2.0      |            | 1          | V        | Note 2                                                                                                              |

| Port Power Switch Operation                   | on with Constan          | t Currer | nt Limitir | ıg (Varial | ole Slop | e)                                                                                                                  |

| Region 2 Current<br>Keep-Out                  | I <sub>BUS_R2MIN</sub>   | _        | _          | 2.13       | Α        | Note 2                                                                                                              |

| Minimum V <sub>BUS</sub><br>Allowed at Output | V <sub>BUS_MIN</sub>     | 2.0      | _          | _          | V        | Note 2                                                                                                              |

| Current Measurement - DC                      | ,                        |          |            |            |          | •                                                                                                                   |

| Current Measurement Range                     | I <sub>BUS_M</sub>       | 0        | _          | 3400       | mA       | Range (Note 2 and Note 3)                                                                                           |

| Reported Current<br>Measurement Resolution    | ΔI <sub>BUS_M</sub>      | _        | 13.3       | _          | mA       | 1 LSB                                                                                                               |

| Current Measurement                           |                          | _        | ±2         | _          | %        | 200 mA < I <sub>BUS</sub> < I <sub>LIM</sub>                                                                        |

| Accuracy                                      |                          | _        | ±2         | _          | LSB      | I <sub>BUS</sub> < 200 mA                                                                                           |

| Current Measurement - AC                      |                          |          |            |            |          |                                                                                                                     |

| Sampling Rate                                 | _                        | _        | 1.1        | _          | ms       | Note 2                                                                                                              |

| Conversion Time<br>Both Channels              | t <sub>CONV</sub>        | _        | 2.2        | _          | ms       | All registers updated in digital (Note 2)                                                                           |

| Charge Rationing - DC                         |                          |          |            |            |          |                                                                                                                     |

| Accumulated Current<br>Measurement Accuracy   | _                        | _        | ±4.5       | _          | %        |                                                                                                                     |

| Charge Rationing - AC                         |                          | •        |            |            |          |                                                                                                                     |

| Current Measurement<br>Update Time            | t <sub>PCYCLE</sub>      | _        | 1          | _          | s        |                                                                                                                     |

- Note 1: This parameter is characterized, not 100% tested.

- 2: This parameter is ensured by design and not 100% tested.

- 3: The current measurement full scale range maximum value is 3.4A. However, the UCS2114 cannot report values above  $I_{LIM}$  (if  $I_{BUS\_R2MIN} \le I_{LIM}$ ) or above  $I_{BUS\_R2MIN}$  (if  $I_{BUS\_R2MIN} > I_{LIM}$  and  $I_{LIM} \le 1.6A$ ).

FIGURE 1-1: SMBus Timing.

TABLE 1-2: TEMPERATURE SPECIFICATIONS

| Parameters                     | Sym.            | Min. | Тур. | Max. | Units | Conditions                                                                                    |

|--------------------------------|-----------------|------|------|------|-------|-----------------------------------------------------------------------------------------------|

| Temperature Ranges             |                 |      |      |      |       |                                                                                               |

| Operating Temperature Range    | T <sub>A</sub>  | -40  | _    | +105 | °C    |                                                                                               |

| Operating Junction Temperature | TJ              | -40  | _    | +125 | °C    |                                                                                               |

| Storage Temperature Range      | T <sub>A</sub>  | -55  | _    | +150 | °C    |                                                                                               |

| Thermal Package Resistances    |                 |      |      |      |       |                                                                                               |

| 3x3 mm 20-pin VQFN             | θ <sub>JA</sub> |      | 48   | _    | °C/W  | Typical 4-layer board with interconnecting vias, recommended land pattern from this document. |

### 1.1 ESD and Transient Performance

#### TABLE 1-3: ESD RATINGS

| ESD Specification                                   | Rating or Value |

|-----------------------------------------------------|-----------------|

| Human Body Model (JEDEC JESD22-A114) - All pins     | 8 kV            |

| Charged Device Model (JEDEC JESD22-C101) - All pins | 500V            |

# 1.1.1 HUMAN BODY MODEL (HBM) PERFORMANCE

HBM testing verifies the ability to withstand ESD strikes, like those that occur during handling and manufacturing, and is done without power applied to the IC. To pass the test, the device must have no change in operation or performance due to the event.

# 1.1.2 CHARGED DEVICE MODEL (CDM) PERFORMANCE

CDM testing verifies the ability to withstand ESD strikes, like those that occur during handling and assembly, with pick-and-place-style machinery and is done without power applied to the IC. To pass the test, the device must have no change in operation or performance due to the event.

NOTES:

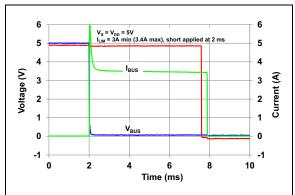

#### 2.0 TYPICAL PERFORMANCE CURVES

Note: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**Note:** Unless otherwise indicated,  $V_{DD} = V_S = 5V$ ,  $T_A = +27$ °C.

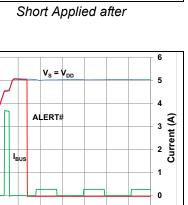

FIGURE 2-1: Short Applied after Power-Up.

Voltage (V)

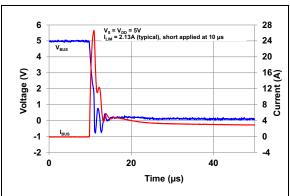

FIGURE 2-2: Power-Up Into a Short.

Time (ms)

FIGURE 2-3: Internal Power Switch Short Response.

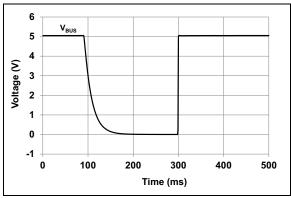

FIGURE 2-4: V<sub>BUS</sub> Discharge Behavior.

FIGURE 2-5: Power Switch On Resistance vs. Temperature.

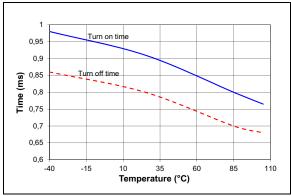

FIGURE 2-6: Power Switch On/Off Time vs. Temperature.

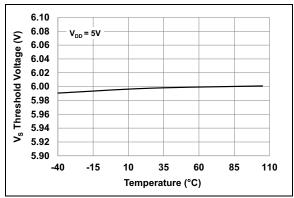

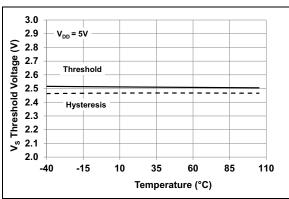

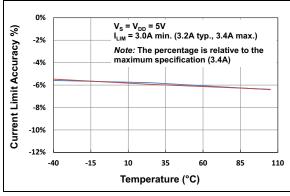

**Note:** Unless otherwise indicated,  $V_{DD} = V_S = 5V$ ,  $T_A = +27$ °C.

**FIGURE 2-7:**  $V_S$  Overvoltage Threshold vs. Temperature.

**FIGURE 2-8:** V<sub>S</sub> Undervoltage Threshold vs. Temperature.

**FIGURE 2-9:** Trip Current Limit Operation vs. Temperature.

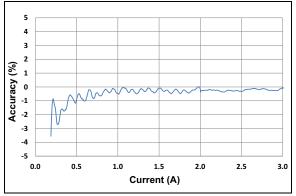

**FIGURE 2-10:** I<sub>BUS</sub> Measurement Accuracy.

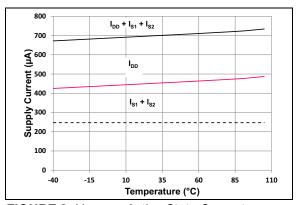

FIGURE 2-11: Active State Current vs. Temperature (both channels on, PWR\_EN1 = PWR\_EN2 = 1).

**Note:** Unless otherwise indicated,  $V_{DD} = V_S = 5V$ ,  $T_A = +27$ °C.

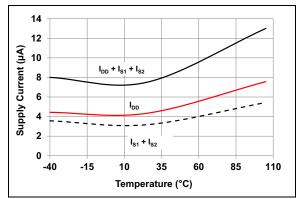

**FIGURE 2-12:** Sleep State Current vs. Temperature.

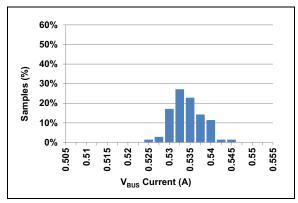

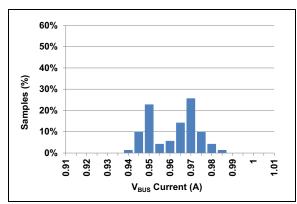

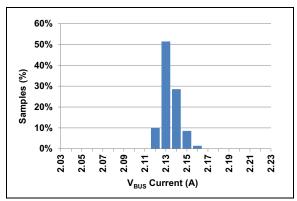

**FIGURE 2-13:** ILIM1 Trip Current Distribution.

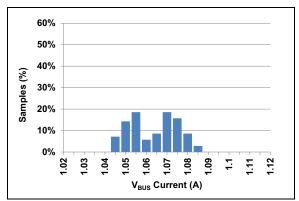

**FIGURE 2-14:** ILIM2 Trip Current Distribution<sup>(1)</sup>.

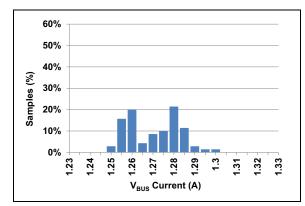

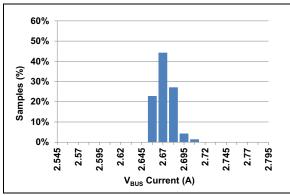

**FIGURE 2-15:** ILIM3 Trip Current Distribution<sup>(1)</sup>.

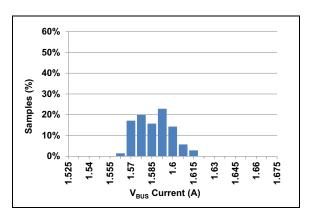

**FIGURE 2-16:** ILIM4 Trip Current Distribution<sup>(1)</sup>.

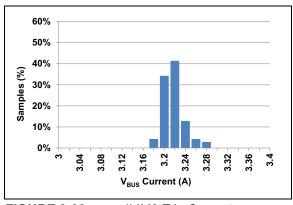

**FIGURE 2-17:** ILIM5 Trip Current Distribution<sup>(1)</sup>.

**Note 1:** The histogram aspect is caused by a mixture of two normal distributions, corresponding to the two V<sub>BUS</sub> channels.

**Note:** Unless otherwise indicated,  $V_{DD} = V_S = 5V$ ,  $T_A = +27^{\circ}C$ .

**FIGURE 2-18:** ILIM6 Trip Current Distribution.

FIGURE 2-19: ILIM7 Trip Current Distribution.

**FIGURE 2-20:** ILIM8 Trip Current Distribution.

Note 1: The histogram aspect is caused by a mixture of two normal distributions, corresponding to the two  $V_{BUS}$  channels.

DS20005743A-page 15

## 3.0 PIN DESCRIPTION

Descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| UCS2114<br>3x3 VQFN | Symbol            | Function                                                                                 | Pin Type        | Connection Type if Pin Not Used                                                            |

|---------------------|-------------------|------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------|

| 1                   | PWR_EN1           | Port power switch enable #1                                                              | DI              | Connect to ground or V <sub>DD</sub> (depending on the polarity decoded via COMM_ILIM pin) |

| 2                   | GND               | Ground                                                                                   | Power           | N/A                                                                                        |

| 3                   | COMM_ILIM         | Enables SMBus or Stand-Alone mode at power-up. Hardware strap for maximum current limit. | AIO             | N/A                                                                                        |

| 4, 5                | V <sub>BUS1</sub> | Port power switch #1 output (requires both pins tied together)                           | High Power, AIO | Leave open                                                                                 |

| 6, 7                | $V_S$             | Voltage input to port power switch $V_{BUS1}$ (requires both pins tied together)         | High Power, AIO | Connect to ground                                                                          |

| 8                   | V <sub>DD</sub>   | Common supply voltage                                                                    | Power           | N/A                                                                                        |

| 9, 10               | V <sub>S</sub>    | Voltage input to port power switch V <sub>BUS2</sub> (requires both pins tied together)  | High Power, AIO | Connect to ground                                                                          |

| 11, 12              | V <sub>BUS2</sub> | Port power switch #2 output (requires both pins tied together)                           | High Power, AIO | Leave open                                                                                 |

| 13                  | BOOST#            | Logic output for DC-DC converter voltage increase (requires pull-up resistor)            | OD              | Connect to ground                                                                          |

| 14                  | GND               | Ground                                                                                   | Power           | N/A                                                                                        |

| 15                  | PWR_EN2           | Port power switch enable #2                                                              | DI              | Connect to ground or V <sub>DD</sub> (depending on the polarity decoded via COMM_ILIM pin) |

| 16                  | ALERT#2           | Output fault ALERT for V <sub>BUS2</sub> (requires pull-up resistor)                     | OD              | Connect to ground                                                                          |

| 17                  | GND               | Ground                                                                                   | Power           | N/A                                                                                        |

| 18                  | SMDATA            | SMDATA - SMBus data input/output (requires pull-up resistor)                             | DIOD            | Connect to V <sub>PULLUP</sub> (or to ground in Stand-Alone mode)                          |

| 19                  | SMCLK             | SMCLK - SMBus clock input (requires pull-up resistor)                                    | DI              | Connect to V <sub>PULLUP</sub> (or to ground in Stand-Alone mode)                          |

| 20                  | ALERT#1           | Output fault ALERT for V <sub>BUS1</sub> (requires pull-up resistor)                     | OD              | Connect to ground                                                                          |

### TABLE 3-2: PIN TYPES

| Pin Type | Description                                                                                                    |

|----------|----------------------------------------------------------------------------------------------------------------|

| Power    | This pin is used to supply power or ground to the device                                                       |

| Hi-Power | This pin is a high-current pin                                                                                 |

| AIO      | Analog Input/Output - this pin is used as an I/O for analog signals                                            |

| DI       | Digital Input - this pin is used as a digital input                                                            |

| DIOD     | Open-Drain Digital Input/Output - this pin is bidirectional. It is open-drain and requires a pull-up resistor. |

| OD       | Open-Drain Digital Output - used as a digital output. It is open-drain and requires a pull-up resistor.        |

### 4.0 TERMS AND ABBREVIATIONS

Note:

The PWR\_EN2 and PWR\_EN1 pins each have configuration bits ("<pin name>\_S" in General Configuration 2 register (Address 11h) and General Configuration 1 register (Address 12h)) that may be used to perform the same function as the external pin state. These bits are accessed via the SMBus/I<sup>2</sup>C and are OR'd with the respective pin. This OR'd combination of pin state and register bit is referenced as the <pin name> control.

#### TABLE 4-1: TERMS AND ABBREVIATIONS

| Term/Abbreviation      | Description                                                                                                                                                                                                                                                                                                                                         |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CC                     | Constant Current                                                                                                                                                                                                                                                                                                                                    |

| Current Limiting mode  | Determines the action that is performed when the $I_{BUS}$ current reaches the $I_{LIM}$ threshold. Trip opens the port power switch. Constant Current (variable slope) allows $V_{BUS}$ to be dropped by the portable device.                                                                                                                      |

| I <sub>BUS_R2MIN</sub> | Current limiter mode boundary                                                                                                                                                                                                                                                                                                                       |

| I <sub>LIM</sub>       | The $I_{BUS}$ current threshold used in current limiting. In Trip mode, when $I_{LIM}$ is reached, the port power switch is opened. In Constant Current mode, when the current exceeds $I_{LIM}$ , operation continues at a reduced voltage and increased current; if $V_{BUS}$ voltage drops below $V_{BUS}$ MIN, the port power switch is opened. |

| OCL                    | Overcurrent limit                                                                                                                                                                                                                                                                                                                                   |

| POR                    | Power-on Reset                                                                                                                                                                                                                                                                                                                                      |

| Portable Device        | USB device attached to the USB port                                                                                                                                                                                                                                                                                                                 |

| Stand-Alone mode       | Indicates that the communications protocol is not active and all communications between the UCS2114 and a controller are done via the external pins only (PWR_EN1 and PWR_EN2 as inputs, and ALERT1# and ALERT2# as outputs)                                                                                                                        |

NOTES:

### 5.0 GENERAL DESCRIPTION

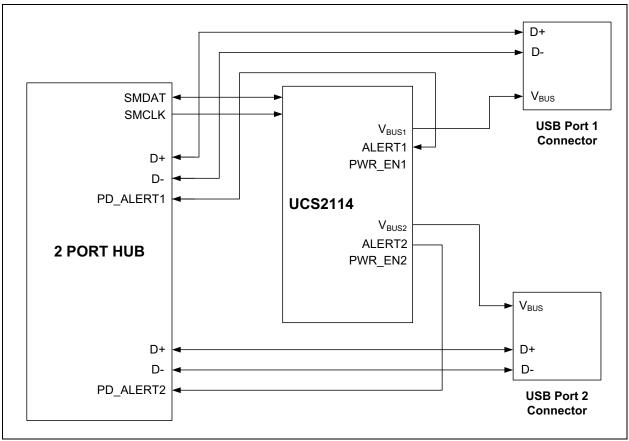

The UCS2114 is a dual-port power switch. Two USB power ports are supported with current limits up to 3.0A continuous current (3.4A maximum) each. Selectable and programmable current limiting configurations are also available to the application. A typical block diagram is shown in Figure 5-1.

FIGURE 5-1: Typical USB Application.

#### 5.1 UCS2114 Power States

Power states are indicators of the device's current consumption in the system and of the functionality of the digital logic. Table 5-1 details the UCS2114 power states.

TABLE 5-1: POWER STATES DESCRIPTION

| State  | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Off    | This power state is entered when the voltage at the $V_{DD}$ pin voltage is $< V_{DD\_TH}$ . In this state, the device is considered "off". The UCS2114 will not retain its digital states and register contents nor respond to SMBus/I <sup>2</sup> C communications. The port power switch will be off. See Section 5.1.1 "Off State Operation".                                                                                   |

| Sleep  | This is the lowest power state available. While in this state, the UCS2114 will retain digital functionality and wake to respond to SMBus/I <sup>2</sup> C communications. See <b>Section 5.1.2</b> "Sleep State Operation".                                                                                                                                                                                                         |

| Error  | This power state is entered when a fault condition exists. Error power state is one or both channels in Fault Handling. This state is updated as Priority One. The Interrupt Status registers for each channel will update the fault detected per channel. Only the channel that has detected a Fault will be affected since the other channel can remain active if no fault is detected. See Section 5.1.4 "Error State Operation". |

| Active | Active power State is one, or both channels active and sourcing current to the V <sub>BUS</sub> Port. This state is updated as Priority Two. None of the channels have detected Fault. This power state provides full functionality. While in this state, operations include activation of the port power switch, current limiting and charge rationing. See Section 5.1.3 "Active State Operation".                                 |

Table 5-2 shows the settings for the various power states, except Off and Error. If  $V_{DD} < V_{DD\_TH}$ , the UCS2114 is in the Off state.

TABLE 5-2: POWER STATES CONTROL SETTINGS

| Power<br>State | PWR_EN1  | PWR_EN2  | Behavior                                                                                 |  |

|----------------|----------|----------|------------------------------------------------------------------------------------------|--|

| Sleep          | disabled | disabled | All switches disabled                                                                    |  |

|                |          |          | V <sub>BUS</sub> will be near ground potential                                           |  |

|                |          |          | The UCS2114 wakes to respond to SMBus                                                    |  |

|                |          |          | communications                                                                           |  |

| Active         | enabled  | disabled | Port power switch is on for V <sub>BUS1</sub>                                            |  |

|                |          |          | V <sub>BUS2</sub> pins are near ground potential or floating (Note 1)                    |  |

| disabled enab  |          | enabled  | Port power switch is on for V <sub>BUS2</sub>                                            |  |

|                |          |          | <ul> <li>V<sub>BUS1</sub> pins are near ground potential or floating (Note 1)</li> </ul> |  |

|                | enabled  | enabled  | Port power switch is on for V <sub>BUS1</sub> and V <sub>BUS2</sub>                      |  |

Note 1: If the bit EN\_VBUS\_DISCHG is '1', the V<sub>BUS</sub> is discharged automatically and V<sub>BUS</sub> is near ground potential. If the bit EN\_VBUS\_DISCHG is '0', then the corresponding V<sub>BUS</sub> pins are floating (V<sub>BUS</sub> discharge is controlled by the SMBus master).

#### 5.1.1 OFF STATE OPERATION

The device will be in the Off state if  $V_{DD}$  is less than  $V_{DD\_TH}$ . When the UCS2114 is in the Off state, it will do nothing and all circuitry will be disabled. Digital register values are not stored and the device will not respond to SMBus commands.

#### 5.1.2 SLEEP STATE OPERATION

The PWR\_EN1 and PWR\_EN2 pins may be used to cause the UCS2114 to enter/exit Sleep. These pins are AND'ed for Sleep mode.

When the UCS2114 is in the Sleep state, the device will be in its lowest power state. The port power switch will be disabled.  $V_{BUS1}$  and  $V_{BUS2}$  will be near ground

potential. The ALERT#1 and ALERT#2 pins will not be asserted. If asserted prior to entering the Sleep state, the ALERT# pin will be released. SMBus activity is limited to single byte read or write.

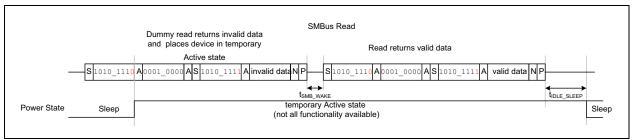

The first data byte read from the UCS2114 when it is in the Sleep state will wake it; however, the data to be read will return all 0's and should be considered invalid. This is a "dummy" read byte meant to wake the UCS2114. Subsequent read or write bytes will be accepted normally. After the dummy read, the UCS2114 will be in a higher power state (see Figure 5-2). After communication has not occurred for  $t_{\rm IDLE\ SLEEP}$ , the UCS2114 will return to Sleep.

FIGURE 5-2: Wake from Sleep using SMBus Read.

#### 5.1.3 ACTIVE STATE OPERATION

Every time the UCS2114 enters the Active state, the port power switches are closed. The UCS2114 cannot be in the Active state (and therefore, the port power switch cannot be turned on) if any of the following conditions exist:

- V<sub>S</sub> < V<sub>S</sub> UVLO

- PWR\_EN1 and PWR\_EN2 are disabled.

#### 5.1.4 ERROR STATE OPERATION

The UCS2114 will enter the Error state from the Active state when any of the following events are detected:

- The maximum allowable internal die temperature (T<sub>TSD HIGH</sub>) has been exceeded.

- The T<sub>TSD\_LOW</sub> die temperature has been exceeded and any of the following conditions is met:

- a power switch operates in Constant Current mode.

- PWR\_EN1 and/or PWR\_EN2 controls transition from inactive to active.

- it is a power-up situation and PWR\_EN1 and/or PWR\_EN2 pins are active.

- · An overcurrent condition has been detected.

- An undervoltage condition on either V<sub>BUS</sub> pin has been detected (see Section 5.3.4 "Undervoltage Lockout on VS").

- A back-voltage condition has been detected (see Section 5.3.2 "Back-Voltage Detection").

- · A discharge error has been detected.

- An overvoltage condition on the V<sub>S</sub> pin.

When the UCS2114 enters the Error state, the port power switch will be disabled while the ALERT# pin is asserted. It will remain off while in this power state. The UCS2114 will leave this state as determined by the fault handling selection.

With the Auto-recovery fault handler, after the  $t_{\mbox{CYCLE}}$  time period, the UCS2114 will check that all of the error conditions have been removed.

If all of the error conditions have been removed, the UCS2114 will return to the Active state.

If both PWR EN1 and PWR EN2 controls transition from active to inactive while the UCS2114 is in the Error state, the device will not enter the Sleep state. After the fault has been removed, the UCS2114 will not automatically enter the Sleep state if EN\_VBUS\_DISCHG bit from the General Configuration 1 register is not set (default setting). To enter the Sleep state, the PWR EN pins must be toggled or an SMBus read register command must be sent.

#### 5.2 Communication

The UCS2114 can operate in SMBus mode (see Section 7.0 "System Management Bus Protocol") or Stand-Alone mode. The resistor connected to the COMM ILIM pin determines the operating mode and

the hardware-set  $I_{LIM}$  setting, as shown in Table 5-3. Unless connected to GND or  $V_{DD}$ , the resistors in Table 5-3 are external pull-down resistors.

The SMBus address is specified in Section 7.2 "SMBus Address and RD/WR Bit".

TABLE 5-3: COMMUNICATION DECODE

| COMM_ILIM Pull Down<br>Resistor (±1%) | PWR_EN1 and PWR_EN2 Polarity | I <sub>LIM</sub> (A) | Total I <sub>LIM</sub> (A)<br>(Note 1) | Communication<br>Mode |

|---------------------------------------|------------------------------|----------------------|----------------------------------------|-----------------------|

| GND                                   | Active-High                  | 0.53                 | 0.53 + 0.53                            | SMBUS                 |

| 10 kΩ                                 | Active-High                  | 0.96                 | 0.96 + 0.96                            | SMBUS                 |

| 12 kΩ                                 | Active-High                  | 1.07                 | 1.07 + 1.07                            | SMBUS                 |

| 15 kΩ                                 | Active-High                  | 1.28                 | 1.28 + 1.28                            | SMBUS                 |

| 18 kΩ                                 | Active-High                  | 1.6                  | 1.6 + 1.6                              | SMBUS                 |

| <b>22</b> kΩ                          | Active-High                  | 2.13                 | 2.13 + 2.13                            | SMBUS                 |

| 27 kΩ                                 | Active-High                  | 2.67                 | 2.67 + 2.67                            | SMBUS                 |

| 33 kΩ                                 | Active-High                  | 3.2                  | 3.2 + 3.2                              | SMBUS                 |

| 47 kΩ                                 | Active-Low                   | 0.53                 | 0.53 + 0.53                            | Stand-Alone           |

| 56 kΩ                                 | Active-Low                   | 0.96                 | 0.96 + 0.96                            | Stand-Alone           |

| 68 kΩ                                 | Active-Low                   | 1.07                 | 1.07 + 1.07                            | Stand-Alone           |

| 82 kΩ                                 | Active-Low                   | 1.28                 | 1.28 + 1.28                            | Stand-Alone           |

| 100 kΩ                                | Active-Low                   | 1.6                  | 1.6 + 1.6                              | Stand-Alone           |

| 120 kΩ                                | Active-Low                   | 2.13                 | 2.13 + 2.13                            | Stand-Alone           |

| 150 kΩ                                | Active-Low                   | 2.67                 | 2.67 + 2.67                            | Stand-Alone           |

| V <sub>DD</sub>                       | Active-Low                   | 3.2                  | 3.2 + 3.2                              | Stand-Alone           |

Note 1: The total maximum current depends on the power dissipation characteristics of the design (see Table 1-1).

### 5.3 Supply Voltages

#### 5.3.1 V<sub>DD</sub> SUPPLY VOLTAGE

The UCS2114 requires 4.5V to 5.5V to be present on the  $V_{DD}$  pin for core device functionality. Core device functionality consists of maintaining register states and wake-up upon SMBus/I<sup>2</sup>C query.

#### 5.3.2 BACK-VOLTAGE DETECTION

The back-voltage detector is functional in all power states (Sleep and Active).

When in Sleep, the UCS2114 will enter the Error state from Sleep if a back-voltage condition was detected.

Whenever the following condition is true for either port, the port power switch will be disabled and a back-voltage event will be flagged. This will cause the UCS2114 to enter the Error power state (see Section 5.1.4 "Error State Operation").

Note: The  $V_{BUS}$  voltage exceeds the  $V_{S}$  and/or the  $V_{DD}$  pin voltage by  $V_{BV\_TH}$  and the port power switch is closed. The port power switch will be opened immediately. If the condition lasts for longer than  $t_{MASK}$ , then the UCS2114 will enter the Error state. Otherwise, the port power switch will be turned on as soon as the condition is removed.

# 5.3.3 BACK-DRIVE CURRENT PROTECTION

If a portable self-powered device is attached, it may drive the  $V_{BUS}$  port to its power supply voltage level; however, the UCS2114 is designed such that leakage current from the  $V_{BUS}$  pins to the  $V_{DD}$  and/or the  $V_S$  pin shall not exceed  $I_{LKG\_1}$  (if the  $V_{DD}$  and/or  $V_S$  voltage is zero) or  $I_{LKG\_2}$  (if the  $V_{DD}$  and/or  $V_S$  voltage exceeds  $V_{DD\ TH}$  and the power switch is open).

#### 5.3.4 UNDERVOLTAGE LOCKOUT ON V<sub>S</sub>

The UCS2114 requires a minimum voltage ( $V_{S\_UVLO}$ ) to be present on the  $V_S$  pin for Active power state.

# 5.3.5 OVERVOLTAGE DETECTION AND LOCKOUT ON VS

Both power switches will be disabled if the voltage on any  $V_S$  pin exceeds a voltage ( $V_{S\_OV}$ ) for longer than the specified time ( $t_{MASK}$ ). This will cause the device to enter the Error state and both ALERT#1 and ALERT#2 pins will be asserted.

#### 5.3.6 PWR\_EN1 AND PWR\_EN2 INPUT

The PWR\_EN control affects the power state and enables the port power switch to be turned on if conditions are met (see Table 5-2). The port power switch cannot be closed if PWR\_EN is disabled. However, if PWR\_EN is enabled, the port power switch is not necessarily closed (see Section 5.1.3 "Active State Operation"). In SMBus mode, the PWR\_EN1 and PWR\_EN2 pins states will be ignored by the UCS2114 if the PIN\_IGN configuration bit is set; otherwise, the PWR\_EN1S and PWR\_EN2S configuration bits are checked along with the pins.

#### 5.4 Discrete Output Pins

# 5.4.1 ALERT#1 AND ALERT#2 OUTPUT PINS

The UCS2114 has two independent ALERT# out pins. ALERT#1 is tied to the status of the  $V_{BUS1}$  pin. ALERT#2 is tied to the status of the  $V_{BUS2}$  pin.

The ALERT# pin is an active-low open-drain interrupt to the host controller. The ALERT# pin is asserted when an error occurs. Also, when charge rationing is enabled, the ALERT# pin is asserted by default when the current rationing threshold is reached (as determined by RATION\_BEH<1:0>). The ALERT# pin is released when all error conditions that may assert the ALERT# pin (such as an error condition and charge rationing) have been removed or reset as necessary.

The UCS2114 is compatible with the Microchip hub devices supporting single pin power control feature. These hub devices have a single connection to the PWR\_EN and ALERT# pins of the UCS2114, which are tied together in the application.

#### 5.4.2 BOOST# OUTPUT PIN

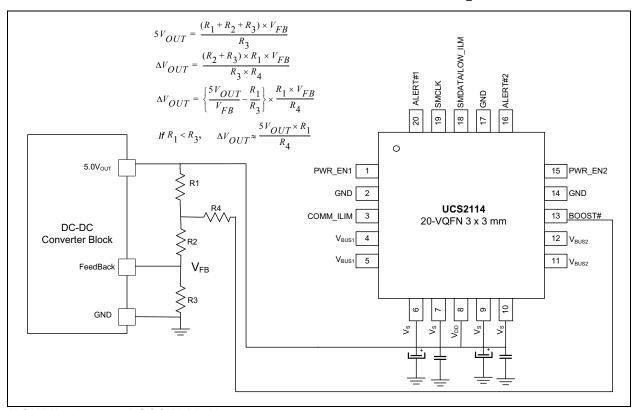

The UCS2114 provides a BOOST# output pin to compensate for voltage drops during high loads. The BOOST# pin is an active-low, open-drain output that would be connected to a resistor in the DC-DC converter's feedback error voltage loop (see Figure 5-3).

The BOOST# pin can then be asserted when the  $V_{BUS}$  Current >  $I_{BOOST}$ .  $I_{BOOST}$  typical value is 1.9A. The BOOST# is OR'ed for both  $V_{BUS1}$  and  $V_{BUS2}$  ports. When the BOOST# pin is asserted, it will remain in this state for at least  $t_{BOOST}$  MAT (minimum assertion time).

FIGURE 5-3: BOOST# Pin Usage.

### 5.5 Discrete Input Pins

#### 5.5.1 COMM\_ILIM INPUT

The COMM\_ILIM input determines the communications mode, as shown in Table 6-1. This is also the hardware strap for MAX Current Limit.

#### 5.5.2 SMCLK

When operated in Stand-Alone mode, this pin should be tied to ground. When the UCS2114 is configured for SMBus communications, the SMCLK is the clock input.

#### 5.5.3 SMDATA

When used in Stand-Alone, this pin should be tied to ground.

When the UCS2114 is configured for SMBus communications, the SMDATA is the data input/output.

#### 6.0 USB PORT POWER SWITCH

To assure compliance to various charging specifications, the UCS2114 contains a USB port power switch that supports two current-limiting modes: Trip and Constant current (variable slope). The current limit ( $I_{LIM}$ ) is pin selectable (and may be updated via the register set). The switch also includes soft-start circuitry and a separate short-circuit current limit.

The port power switch is on in the Active state (except when  $V_{BUS}$  is discharging).

### 6.1 Current Limiting

#### 6.1.1 CURRENT LIMIT SETTING

The UCS2114 hardware set current limit,  $I_{LIM}$ , can be one of eight values. This resistor value is read once upon UCS2114 power-up. The current limit can be changed via the SMBus/ $I^2$ C after power-up; however, the programmed current limit cannot exceed the hardware set current limit. Unless connected to  $V_{DD}$ , the resistors in Table 6-1 are pull-down resistors.

At power-up, the communication mode (Stand-Alone or SMBus/ $I^2C$ ) and hardware current limit ( $I_{LIM}$ ) are determined via the pull-down resistor (or pull-up resistor if connected to  $V_{DD}$ ) on the COMM\_ILIM pin, as shown in Table 6-1.

# 6.1.2 SHORT-CIRCUIT OUTPUT CURRENT LIMITING

Short-circuit current limiting occurs when the output current is above the selectable current limit ( $I_{LIMx}$ ). This event will be detected and the current will immediately be limited (within  $t_{SHORT\_LIM}$  time). If the condition remains, the port power switch will flag an Error condition and enter the Error state.

#### 6.1.3 SOFT START

When the PWR\_EN control changes states to enable the port power switch, the UCS2114 invokes a soft-start routine for the duration of the V<sub>BUS</sub> rise time (t<sub>R\_BUS</sub>). This soft-start routine will limit current flow from V<sub>S</sub> into V<sub>BUS</sub> while it is active. This circuitry will prevent current spikes due to a step in the portable device current draw.

In the case when a portable device is attached while the PWR\_EN pin is already enabled, if the bus current exceeds  $I_{LIM}$ , the UCS2114 current limiter will respond within a specified time ( $t_{SHORT\_LIM}$ ) and will operate normally at this point. The  $C_{BUS}$  capacitor will deliver the extra current, if any, as required by the load change.

TABLE 6-1: I<sub>LIM</sub> DECODE

| COMM_ILIM<br>Pulldown<br>Resistor<br>(±1%) | PWR_EN1<br>and<br>PWR_EN2<br>Polarity | I <sub>LIM</sub> (A) | Total I <sub>LIM</sub> (A) (Note 1) |

|--------------------------------------------|---------------------------------------|----------------------|-------------------------------------|

| GND                                        | Active-High                           | 0.53                 | 0.53+0.53                           |

| 10 kΩ                                      | Active-High                           | 0.96                 | 0.96+0.96                           |

| 12 kΩ                                      | Active-High                           | 1.07                 | 1.07+1.07                           |

| 15 kΩ                                      | Active-High                           | 1.28                 | 1.28+1.28                           |

| 18 kΩ                                      | Active-High                           | 1.6                  | 1.6+1.6                             |

| 22 kΩ                                      | Active-High                           | 2.13                 | 2.13+2.13                           |

| 27 kΩ                                      | Active-High                           | 2.67                 | 2.67+2.67                           |

| 33 kΩ                                      | Active-High                           | 3.2                  | 3.2+3.2                             |

| 47 kΩ                                      | Active-Low                            | 0.53                 | 0.53+0.53                           |

| 56 kΩ                                      | Active-Low                            | 0.96                 | 0.96+0.96                           |

| 68 kΩ                                      | Active-Low                            | 1.07                 | 1.07+1.07                           |

| 82 kΩ                                      | Active-Low                            | 1.28                 | 1.28+1.28                           |

| 100 kΩ                                     | Active-Low                            | 1.6                  | 1.6+1.6                             |

| 120 kΩ                                     | Active-Low                            | 2.13                 | 2.13+2.13                           |

| 150 kΩ                                     | Active-Low                            | 2.67                 | 2.67+2.67                           |

| $V_{DD}$                                   | Active-Low                            | 3.2                  | 3.2+3.2                             |

**Note 1:** The total maximum current depends on power dissipation characteristics of the design (see Table 1-1).

#### 6.1.4 CURRENT LIMITING MODES

The UCS2114 current limiting has two modes: Trip and Constant Current (variable slope). Either mode functions at all times when the port power switch is closed.

#### 6.1.4.1 Trip Mode

When using Trip current limiting, the UCS2114 USB port power switch functions as a low-resistance switch and rapidly turns off if the current limit is exceeded. While operating using Trip current limiting, the  $V_{BUS}$  output voltage will be held relatively constant (equal to the  $V_{S}$  voltage minus the  $R_{ON}\,x\,I_{BUS}$  current) for all current values up to the  $I_{LIM}$ .

If the current drawn by a portable device exceeds  $I_{LIM}$ , the following occurs:

- The port power switch will be turned off (Trip action).

- The UCS2114 will enter the Error state and assert the ALERT# pin.

- 3. The fault handling circuitry will then determine subsequent actions.