# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### INTEGRATED CIRCUITS

Preliminary specification

2003 Apr 10

### UDA1355H

| CONTENTS                                                |                                                                                                                                                                                       | 11                                                                            | I <sup>2</sup> C-BUS DESCRIPTION                                                                                                                                                    |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>2 | FEATURES<br>General<br>Control<br>IEC 60958 input<br>IEC 60958 output<br>Digital I/O interface<br>ADC digital sound processing<br>DAC digital sound processing<br>GENERAL DESCRIPTION | 11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10 | Characteristics<br>Bit transfer<br>Byte transfer<br>Data transfer<br>Register address<br>Device address<br>Start and stop conditions<br>Acknowledgment<br>Write cycle<br>Read cycle |

| 3                                                       | ORDERING INFORMATION                                                                                                                                                                  | 12                                                                            | REGISTER MAPPING                                                                                                                                                                    |

| 4<br>5<br>6                                             | QUICK REFERENCE DATA<br>BLOCK DIAGRAM<br>PINNING                                                                                                                                      | 12.1<br>12.2<br>12.3                                                          | Address mapping<br>Read/write registers mapping<br>Read registers mapping                                                                                                           |

| 7                                                       | FUNCTIONAL DESCRIPTION                                                                                                                                                                | 13                                                                            | LIMITING VALUES                                                                                                                                                                     |

| ,<br>7.1                                                |                                                                                                                                                                                       | 14                                                                            | THERMAL CHARACTERISTICS                                                                                                                                                             |

| 7.2                                                     | Microcontroller interface                                                                                                                                                             | 15                                                                            | CHARACTERISTICS                                                                                                                                                                     |

| 7.3                                                     | Clock systems                                                                                                                                                                         | 16                                                                            | TIMING CHARACTERISTICS                                                                                                                                                              |

| 7.4                                                     | IEC 60958 decoder                                                                                                                                                                     | 17                                                                            | PACKAGE OUTLINE                                                                                                                                                                     |

| 7.5<br>7.6                                              | IEC 60958 encoder<br>Analog input                                                                                                                                                     | 18                                                                            | SOLDERING                                                                                                                                                                           |

| 7.0<br>7.7<br>7.8<br>7.9                                | Analog output<br>Digital audio input and output<br>Power-on reset                                                                                                                     | 18.1<br>18.2                                                                  | Introduction to soldering surface mount<br>packages<br>Reflow soldering                                                                                                             |

| 8                                                       | APPLICATION MODES                                                                                                                                                                     | 18.3                                                                          | Wave soldering                                                                                                                                                                      |

| 8.1<br>8.2                                              | Static mode pin assignment<br>Static mode basic applications                                                                                                                          | 18.4<br>18.5                                                                  | Manual soldering<br>Suitability of surface mount IC packages for<br>wave and reflow soldering methods                                                                               |

| 8.3<br>8.4                                              | Microcontroller mode pin assignment<br>Microcontroller mode applications                                                                                                              | 19                                                                            | DATA SHEET STATUS                                                                                                                                                                   |

| 9                                                       | SPDIF SIGNAL FORMAT                                                                                                                                                                   | 20                                                                            | DISCLAIMERS                                                                                                                                                                         |

| 9.1<br>9.2<br>9.3                                       | SPDIF channel encoding<br>SPDIF hierarchical layers<br>Timing characteristics                                                                                                         | 21                                                                            | TRADEMARKS                                                                                                                                                                          |

| 10                                                      | L3-BUS DESCRIPTION                                                                                                                                                                    |                                                                               |                                                                                                                                                                                     |

| 10.1<br>10.2<br>10.3                                    | Device addressing<br>Register addressing<br>Data write mode                                                                                                                           |                                                                               |                                                                                                                                                                                     |

10.4 Data read mode

| 2003 Apr | 10 |

|----------|----|

|----------|----|

### UDA1355H

#### **1 FEATURES**

#### 1.1 General

- 2.7 to 3.6 V power supply

- Integrated digital interpolator filter and Digital-to-Analog Converter (DAC)

- 24-bit data path in interpolator

- · No analog post filtering required for DAC

- Integrated Analog-to-Digital Converter (ADC), Programmable Gain Amplifier (PGA) and digital decimator filter

- · 24-bit data path in decimator

- Master or slave mode for digital audio data I/O interface

- I<sup>2</sup>S-bus, MSB-justified, LSB-justified 16, 18, 20, and 24 bits formats supported on digital I/O interface.

#### 1.2 Control

Controlled by means of static pins or microcontroller (L3-bus or l<sup>2</sup>C-bus) interface.

#### 1.3 IEC 60958 input

- On-chip amplifier for converting IEC 60958 input to CMOS levels

- Supports level I, II and III timing

- Selectable IEC 60958 input channel, one of four

- Supports input frequencies from 28 to 96 kHz

- Lock indication signal available on pin LOCK

- 40 status bits can be read for left and right channel via L3-bus or I<sup>2</sup>C-bus

- Channel status bits available via L3-bus or I<sup>2</sup>C-bus: lock, pre-emphasis, audio sample frequency, two channel Pulse Code Modulation (PCM) indication and clock accuracy

- Pre-emphasis information of incoming IEC 60958 bitstream available in register

- Detection of digital data preamble, such as AC3, available on pin in microcontroller mode.

### 1.4 IEC 60958 output

- CMOS output level converted to IEC 60958 output signal

- Full-swing digital signal, with level II timing using crystal oscillator clock

- 32, 44.1 and 48 kHz output frequencies supported in static mode

- 32, 44.1 and 48 kHz output frequencies (including double and half of these frequencies) supported in microcontroller mode

- Via microcontroller, 40 status bits can be set for left and right channel.

#### 1.5 Digital I/O interface

- Supports sampling frequencies from 16 to 100 kHz

- Supported static mode:

- I<sup>2</sup>S-bus format

- LSB-justified 16 and 24 bits format

- MSB-justified format.

- Supported microcontroller mode:

- I<sup>2</sup>S-bus format

- LSB-justified 16, 18, 20 or 24 bits format

- MSB-justified format.

- BCK and WS signals can be slave or master, depending on application mode.

#### 1.6 ADC digital sound processing

- Supports sampling frequencies from 16 to 100 kHz

- Analog front-end includes a 0 to +24 dB PGA in steps of 3 dB, selectable via microcontroller interface

- Digital independent left and right volume control of +24 to -63.5 dB in steps of 0.5 dB via microcontroller interface

- Bitstream ADC operating at 64fs

- Comb filter decreases sample rate from 64fs to 8fs

- Decimator filter (8fs to fs) made of a cascade of three FIR half-band filters.

#### 1.7 DAC digital sound processing

- Digital de-emphasis for 32, 44.1, 48 and 96 kHz audio sampling frequencies

- Automatic de-emphasis when using IEC 60958 to DAC

- Soft mute made of a cosine roll-off circuit selectable via pin MUTE or L3-bus interface

### UDA1355H

- Programmable digital silence detector

- Interpolating filter (f<sub>s</sub> to 64f<sub>s</sub> or f<sub>s</sub> to 128f<sub>s</sub>) comprising a recursive and a FIR filter in cascade

- Selectable fifth-order noise shaper operating at 64fs or third-order noise shaper operating at 128fs (specially for low sampling frequencies, e.g. 16 kHz) generating bitstream for DAC

- Filter Stream DAC (FSDAC)

- In microcontroller mode:

- Left and right volume control (for balance control) 0 to -78~dB and  $-\infty$

- Left and right bass boost and treble control

- Optional resonant bass boost control

- Mixing possibility of two data streams.

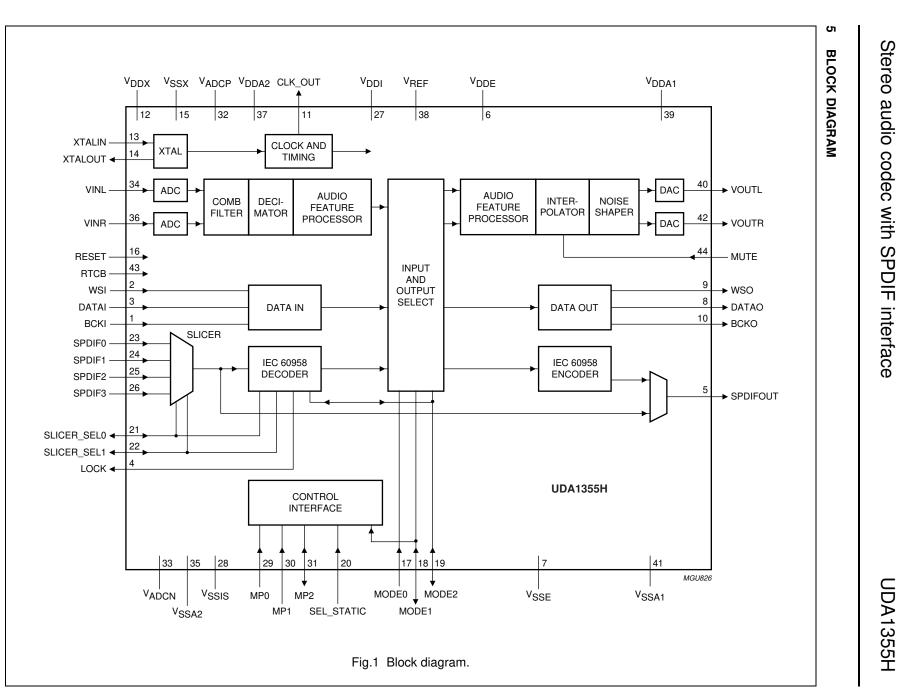

### 2 GENERAL DESCRIPTION

The UDA1355H is a single-chip IEC 60958 decoder and encoder with integrated stereo digital-to-analog converters and analog-to-digital converters employing bitstream conversion techniques.

The UDA1355H has a selectable one-of-four SPDIF input (accepting level I, II and III timing) and one SPDIF output

which can generate level II output signals with CMOS levels. In microcontroller mode the UDA1355H offers a large variety of possibilities for defining signal flows through the IC, offering a flexible analog, digital and SPDIF converter chip with possibilities for off-chip sound processing via the digital input and output interface.

A lock indicator is available on pin LOCK when the IEC 60958 decoder and the clock regeneration mechanism is in lock. By default the DAC output and the digital data interface output are muted when the decoder is not in lock.

The UDA1355H contains two clock systems which can run at independent frequencies, allowing to lock-on to an incoming SPDIF or digital audio signal, and in the mean time generating a stable signal by means of the crystal oscillator for driving, for example, the ADC or SPDIF output signal.

Using the crystal oscillator (which requires a 12.288 MHz crystal) and the on-chip low jitter PLL, all standard audio sampling frequencies ( $f_s = 32$ , 44.1 and 48 kHz including half and double these frequencies) can be generated.

### **3 ORDERING INFORMATION**

| ТҮРЕ     |       | PACKAGE                                                                                      |          |

|----------|-------|----------------------------------------------------------------------------------------------|----------|

| NUMBER   | NAME  | DESCRIPTION                                                                                  | VERSION  |

| UDA1355H | QFP44 | plastic quad flat package; 44 leads (lead length 1.3 mm); body $10 \times 10 \times 1.75$ mm | SOT307-2 |

### UDA1355H

### 4 QUICK REFERENCE DATA

| SYMBOL              | PARAMETER                                             | CONDITIONS                               | MIN. | TYP.     | MAX. | UNIT     |

|---------------------|-------------------------------------------------------|------------------------------------------|------|----------|------|----------|

| Supplies            |                                                       |                                          | I    |          |      |          |

| V <sub>DDA1</sub>   | DAC supply voltage                                    |                                          | 2.7  | 3.0      | 3.6  | V        |

| V <sub>DDA2</sub>   | ADC supply voltage                                    |                                          | 2.7  | 3.0      | 3.6  | V        |

| V <sub>DDX</sub>    | crystal oscillator and PLL supply voltage             |                                          | 2.7  | 3.0      | 3.6  | V        |

| V <sub>DDI</sub>    | digital core supply voltage                           |                                          | 2.7  | 3.0      | 3.6  | V        |

| V <sub>DDE</sub>    | digital pad supply voltage                            |                                          | 2.7  | 3.0      | 3.6  | V        |

| I <sub>DDA1</sub>   | DAC supply current                                    | f <sub>s</sub> = 48 kHz; power-on        | -    | 4.7      | -    | mA       |

|                     |                                                       | f <sub>s</sub> = 96 kHz; power-on        | -    | 4.7      | -    | mA       |

|                     |                                                       | f <sub>s</sub> = 48 kHz; power-down      | -    | 1.7      | -    | μA       |

|                     |                                                       | f <sub>s</sub> = 96 kHz; power-down      | -    | 1.7      | -    | μA       |

| I <sub>DDA2</sub>   | ADC supply current                                    | f <sub>s</sub> = 48 kHz; power-on        | -    | 10.2     | -    | mA       |

|                     |                                                       | f <sub>s</sub> = 96 kHz; power-on        | -    | 10.4     | -    | mA       |

|                     |                                                       | f <sub>s</sub> = 48 kHz; power-down      | -    | 0.2      | -    | μA       |

|                     |                                                       | f <sub>s</sub> = 96 kHz; power-down      | _    | 0.2      | -    | μA       |

| I <sub>DDX</sub>    | crystal oscillator and PLL                            | f <sub>s</sub> = 48 kHz; power-on        | -    | 0.9      | -    | mA       |

|                     | supply current                                        | f <sub>s</sub> = 96 kHz; power-on        | -    | 1.2      | -    | mA       |

| I <sub>DDI</sub>    | digital core supply current                           | f <sub>s</sub> = 48 kHz; all on          | _    | 18.2     | -    | mA       |

|                     |                                                       | f <sub>s</sub> = 96 kHz; all on          | -    | 34.7     | -    | mA       |

| I <sub>DDE</sub>    | digital pad supply current                            | f <sub>s</sub> = 48 kHz; all on          | -    | 0.5      | -    | mA       |

|                     |                                                       | f <sub>s</sub> = 96 kHz; all on          | _    | 0.7      | _    | mA       |

| T <sub>amb</sub>    | ambient temperature                                   |                                          | -40  | _        | +85  | °C       |

| Digital-to-anal     | og converter; f <sub>i</sub> = 1 kHz; V <sub>DD</sub> | <sub>A1</sub> = 3.0 V                    |      | <u>.</u> | 4    | <b>!</b> |

| V <sub>o(rms)</sub> | output voltage (RMS value)                            |                                          | -    | 900      | -    | mV       |

| ΔV <sub>o</sub>     | output voltage unbalance                              |                                          | _    | 0.1      | _    | dB       |

| (THD+N)/S           | total harmonic                                        | IEC 60958 input; f <sub>s</sub> = 48 kHz |      |          |      |          |

| . ,                 | distortion-plus-noise to                              | at 0 dB                                  | _    | -88      | _    | dB       |

|                     | signal ratio                                          | at –20 dB                                | _    | -75      | _    | dB       |

|                     |                                                       | at –60 dB; A-weighted                    | _    | -37      | _    | dB       |

|                     |                                                       | IEC 60958 input; f <sub>s</sub> = 96 kHz |      |          |      |          |

|                     |                                                       | at 0 dB                                  | _    | -83      | _    | dB       |

|                     |                                                       | at –60 dB; A-weighted                    | _    | -37      | _    | dB       |

| S/N                 | signal-to-noise ratio                                 | IEC 60958 input; code = 0;<br>A-weighted |      |          |      |          |

|                     |                                                       | $f_s = 48 \text{ kHz}$                   | _    | 98       | _    | dB       |

|                     |                                                       | $f_s = 96 \text{ kHz}$                   |      |          |      | dB       |

|                     |                                                       | $I_{c} = 90 \text{ KHZ}$                 | -    | 96       | —    | uD       |

| SYMBOL               | PARAMETER                                              | CONDITIONS                               | MIN. | TYP.   | MAX. | UNIT |

|----------------------|--------------------------------------------------------|------------------------------------------|------|--------|------|------|

| Analog-to-digi       | tal converter; f <sub>i</sub> = 1 kHz; V <sub>DD</sub> | <sub>A2</sub> = 3.0 V                    |      |        |      |      |

| V <sub>i</sub> (rms) | input voltage (RMS value)                              | $V_o = -1.16$ dBFS digital output        | _    | 1.0    | -    | V    |

| $\Delta V_i$         | input voltage unbalance                                |                                          | _    | 0.1    | _    | dB   |

| (THD+N)/S            | total harmonic                                         | f <sub>s</sub> = 48 kHz                  |      |        |      |      |

|                      | distortion-plus-noise to                               | at 0 dB                                  | _    | -85    | _    | dB   |

|                      | signal ratio                                           | at –60 dB; A-weighted                    | _    | -35    | _    | dB   |

|                      |                                                        | f <sub>s</sub> = 96 kHz                  |      |        |      |      |

|                      |                                                        | at 0 dB                                  | _    | -85    | _    | dB   |

|                      |                                                        | at -60 dB; A-weighted                    | _    | -35    | _    | dB   |

| S/N                  | signal-to-noise ratio                                  | code = 0; A-weighted                     |      |        |      |      |

|                      |                                                        | f <sub>s</sub> = 48 kHz                  | _    | 97     | _    | dB   |

|                      |                                                        | f <sub>s</sub> = 96 kHz                  | _    | 95     | _    | dB   |

| $\alpha_{cs}$        | channel separation                                     |                                          | _    | 100    | _    | dB   |

| External cryst       | al                                                     |                                          |      |        |      |      |

| f <sub>xtal</sub>    | crystal frequency                                      |                                          | _    | 12.288 | -    | MHz  |

| C <sub>L(xtal)</sub> | crystal load capacitor                                 |                                          | _    | 10     | -    | pF   |

| Device reset         |                                                        |                                          |      |        |      |      |

| t <sub>rst</sub>     | reset time                                             |                                          | _    | 250    | _    | μs   |

| Power consun         | nption                                                 |                                          |      |        |      |      |

| P <sub>tot</sub>     | total power consumption                                | IEC 60958 input; f <sub>s</sub> = 48 kHz |      |        |      |      |

|                      |                                                        | DAC in playback mode                     | _    | 74     | -    | mW   |

|                      |                                                        | DAC in Power-down mode                   | _    | 63     | -    | mW   |

2003 Apr 10

7

NXP Semiconductors

### UDA1355H

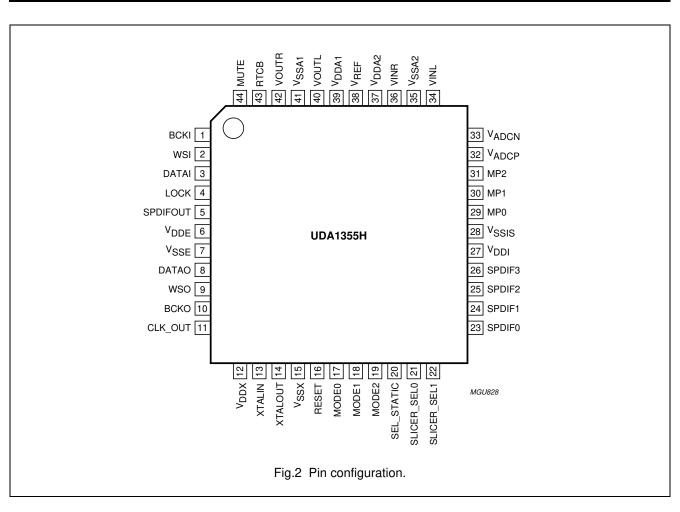

### 6 PINNING

| SYMBOL            | PIN | <b>PAD</b> <sup>(1)</sup> | DESCRIPTION                                                                                               |  |

|-------------------|-----|---------------------------|-----------------------------------------------------------------------------------------------------------|--|

| BCKI              | 1   | bpt4mtht5v                | bit clock input (master or slave)                                                                         |  |

| WSI               | 2   | bpt4mtht5v                | word select input (master or slave)                                                                       |  |

| DATAI             | 3   | iptht5v                   | digital data input                                                                                        |  |

| LOCK              | 4   | op4mc                     | PLL lock indicator output                                                                                 |  |

| SPDIFOUT          | 5   | op4mc                     | SPDIF output                                                                                              |  |

| V <sub>DDE</sub>  | 6   | vdde                      | digital pad supply voltage                                                                                |  |

| V <sub>SSE</sub>  | 7   | vsse                      | digital pad ground                                                                                        |  |

| DATAO             | 8   | ops5c                     | digital data output                                                                                       |  |

| WSO               | 9   | bpt4mtht5v                | word select output (master or slave)                                                                      |  |

| BCKO              | 10  | bpt4mtht5v                | bit clock output (master or slave)                                                                        |  |

| CLK_OUT           | 11  | op4mc                     | clock output; 256fs or 384fs                                                                              |  |

| V <sub>DDX</sub>  | 12  | vddco                     | crystal oscillator and PLL supply voltage                                                                 |  |

| XTALIN            | 13  | apio                      | crystal oscillator input                                                                                  |  |

| XTALOUT           | 14  | apio                      | crystal oscillator output                                                                                 |  |

| V <sub>SSX</sub>  | 15  | VSSCO                     | crystal oscillator and PLL ground                                                                         |  |

| RESET             | 16  | ipthdt5v                  | reset input                                                                                               |  |

| MODE0             | 17  | apio                      | mode selection input 0 for static mode or microcontroller mode (grounded for I <sup>2</sup> C-bus)        |  |

| MODE1             | 18  | bpts5tht5v                | mode selection input 1 for static mode or AO address input and output for microcontroller mode            |  |

| MODE2             | 19  | bpts5tht5v                | mode selection input 2 for static mode or U_RDY output for microcontroller mode                           |  |

| SEL_STATIC        | 20  | apio                      | selection input for static mode, I <sup>2</sup> C-bus mode or L3-bus mode                                 |  |

| SLICER_SEL0       | 21  | bpts5tht5v                | SPDIF slicer selection input 0 for static mode and USER bit output for microcontroller mode               |  |

| SLICER_SEL1       | 22  | bpts5tht5v                | SPDIF slicer selection input 1 for static mode and AC3 preamble detect output for microcontroller mode    |  |

| SPDIF0            | 23  | apio                      | SPDIF input 0                                                                                             |  |

| SPDIF1            | 24  | apio                      | SPDIF input 1                                                                                             |  |

| SPDIF2            | 25  | apio                      | SPDIF input 2                                                                                             |  |

| SPDIF3            | 26  | apio                      | SPDIF input 3                                                                                             |  |

| V <sub>DDI</sub>  | 27  | vddi                      | digital core supply voltage                                                                               |  |

| V <sub>SSIS</sub> | 28  | vssis                     | digital core ground                                                                                       |  |

| MP0               | 29  | apio                      | multi-purpose pin 0: frequency select for static mode, not used for microcontroller mode                  |  |

| MP1               | 30  | iptht5v                   | multi-purpose pin 1: SFOR1 for static mode, SCL for I <sup>2</sup> C-bus mode and L3CLOCK for L3-bus mode |  |

| MP2               | 31  | iic400kt5v                | multi-purpose pin 2: SFOR0 for static mode, SDA for I <sup>2</sup> C-bus mode and L3DATA for L3-bus mode  |  |

| V <sub>ADCP</sub> | 32  | vddco                     | positive ADC reference voltage                                                                            |  |

| V <sub>ADCN</sub> | 33  | VSSCO                     | negative ADC reference voltage                                                                            |  |

| V <sub>SSA1</sub> | 41 | VSSCO |

|-------------------|----|-------|

| VOUTR             | 42 | apio  |

### MUTE Note

RTCB

1. See Table 1.

Table 1 Pad description

| PAD        | DESCRIPTION                                                                                                   |  |

|------------|---------------------------------------------------------------------------------------------------------------|--|

| iptht5v    | input pad; push-pull; TTL with hysteresis; 5 V tolerant                                                       |  |

| ipthdt5v   | input pad; push-pull; TTL with hysteresis; pull-down; 5 V tolerant                                            |  |

| op4mc      | output pad; push-pull; 4 mA output drive; CMOS                                                                |  |

| ops5c      | output pad; push-pull; 5 ns slew rate control; CMOS                                                           |  |

| bpt4mtht5v | bidirectional pad; push-pull input; 3-state output; 4 mA output drive; TTL with hysteresis; 5 V tolerant      |  |

| bpts5tht5v | bidirectional pad; push-pull input; 3-state output; 5 ns slew rate control; TTL with hysteresis; 5 V tolerant |  |

| iic400kt5v | I <sup>2</sup> C-bus pad; 400 kHz I <sup>2</sup> C-bus specification with open drain; 5 V tolerant            |  |

| apio       | analog pad; analog input or output                                                                            |  |

| vddco      | analog supply pad                                                                                             |  |

| VSSCO      | analog ground pad                                                                                             |  |

| vdde       | digital supply pad                                                                                            |  |

| vsse       | digital ground pad                                                                                            |  |

| vddi       | digital core supply pad                                                                                       |  |

| vssis      | digital core ground pad                                                                                       |  |

PIN

34

35

36

37

38

39

40

43

44

SYMBOL

VINL

V<sub>SSA2</sub>

VINR

V<sub>DDA2</sub>

$V_{\mathsf{REF}}$

$V_{\text{DDA1}}$

VOUTL

### Stereo audio codec with SPDIF interface

**PAD**<sup>(1)</sup>

apio

apio

apio

apio

vssco

vddco

vddco

ipthdt5v

iipthdt5v

ADC left channel input

ADC right channel input

reference voltage for ADC and DAC

ADC supply voltage

DAC supply voltage

DAC left channel output

DAC right channel output

ADC ground

DAC ground

test control input DAC mute input

### UDA1355H

DESCRIPTION

UDA1355H

### Stereo audio codec with SPDIF interface

### 7 FUNCTIONAL DESCRIPTION

#### 7.1 IC control

The UDA1355H can be controlled either via static pins or via the microcontroller serial hardware interface being the  $I^2$ C-bus with a clock up to 400 kHz or the L3-bus with a clock up to 2 MHz. It is recommended to use the microcontroller interface since this gives full access to all the IC features.

The two microcontroller interfaces only differ in interface format. The register addresses and features that can be controlled are identical for L3-bus mode and I<sup>2</sup>C-bus mode.

The UDA1355H can operate in three control modes:

- Static mode with limited features

- L3-bus mode with full featuring

- I<sup>2</sup>C-bus mode with full featuring.

The modes are selected via the 3-level pin SEL\_STATIC according to Table 2.

Table 2

Control mode selection via pin SEL\_STATIC

| LEVEL | MODE                      |

|-------|---------------------------|

| HIGH  | static mode               |

| MID   | I <sup>2</sup> C-bus mode |

| LOW   | L3-bus mode               |

#### 7.2 Microcontroller interface

The UDA1355H has a microcontroller interface and all the sound processing features and system settings can be controlled by the microcontroller.

The controllable settings are:

- Restoring L3-bus defaults

- Power-on settings for all blocks

- · Digital interface input and output formats

- · Volume settings for the decimator

- PGA gain settings

### UDA1355H

- Set two times 40 bits of channel status bits of the SPDIF output

- · Select one of four SPDIF input sources

- Enable digital mixer inside interpolator

- · Control mute and mixer volumes of digital mixer

- Selection of filter mode and settings of treble and bass boost for the interpolator (DAC) section

- Volume settings of interpolator

- Selection of soft mute via cosine roll-off (only effective in L3-bus control mode) and bypass of auto mute

- Selection of de-emphasis

NXP Semiconductors

• Enable and control of digital mixer inside interpolator.

The readable settings are:

- Mute status of interpolator

- PLL lock and adaptive lock

- Two times 40 bits of channels status bits of the SPDIF input signal.

### 7.3 Clock systems

The UDA1355H has two clock systems.

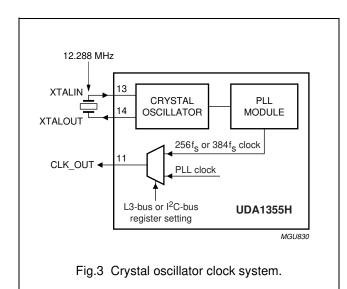

The first system uses an external crystal of 12.288 MHz to generate the audio related system clocks. Only a crystal with a frequency of 12.288 MHz is allowed.

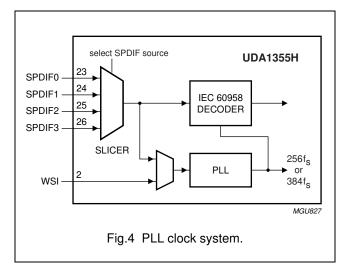

The second system is a PLL which locks on the SPDIF or incoming digital audio signal (e.g. I<sup>2</sup>S-bus) and recovers the system clock.

### 7.3.1 CRYSTAL OSCILLATOR CLOCK SYSTEM

The crystal oscillator and the on-chip PLL and divider circuit can be used to generate internal and external clock signals related to standard audio sampling frequencies (such as 32, 44.1 and 48 kHz including half and double of these frequencies).

The audio frequencies supported in either microcontroller mode or static mode are given in Table 3.

| Table 3 | Output frequencies |

|---------|--------------------|

|---------|--------------------|

|                          | OUTPUT FREQUENCY              |                             |  |

|--------------------------|-------------------------------|-----------------------------|--|

| BASIC AUDIO<br>FREQUENCY | MICRO-<br>CONTROLLER<br>MODE  | STATIC MODE                 |  |

| 32 kHz                   | 256 × 16 kHz                  |                             |  |

|                          | $384 \times 16 \text{ kHz}$   |                             |  |

|                          | $256 \times 32 \text{ kHz}$   | $256 \times 32 \text{ kHz}$ |  |

|                          | $384\times32\ kHz$            |                             |  |

|                          | $256 \times 64 \text{ kHz}$   |                             |  |

|                          | $384 \times 64 \text{ kHz}$   |                             |  |

| 44.1 kHz                 | $256\times22.05\ kHz$         |                             |  |

|                          | $384\times22.05\ kHz$         |                             |  |

|                          | 256 × 44.1 kHz                | 256 × 44.1 kHz              |  |

|                          | $384 \times 44.1 \text{ kHz}$ |                             |  |

|                          | $256 \times 88.2 \text{ kHz}$ |                             |  |

|                          | $384 \times 88.2 \text{ kHz}$ |                             |  |

| 48 kHz                   | $256 \times 24 \text{ kHz}$   |                             |  |

|                          | $384 \times 24 \text{ kHz}$   |                             |  |

|                          | 256 × 48 kHz                  | 256 × 48 kHz                |  |

|                          | $384 \times 48 \text{ kHz}$   |                             |  |

|                          | 256 × 96 kHz                  |                             |  |

|                          | 384 × 96 kHz                  |                             |  |

### Remarks:

- If an application mode is selected which does not need a crystal oscillator, the crystal oscillator cannot be omitted. The reason is that the interpolator switches to the crystal clock when an SPDIF input signal is removed. This switch prevents the noise shaper noise from moving inside the audio band as the PLL gradually decreases in frequency.

- If no accurate output frequency is needed, the crystal can be replaced with a resonator.

- Instead of the crystal, a 12.288 MHz system clock can be applied to pin XTALIN.

The block diagram of the crystal oscillator and the PLL circuit is given in Fig.3.

### 7.3.2 PLL CLOCK SYSTEM

The PLL locks on the incoming digital data of the SPDIF or WS input signal. The PLL recovers the clock from the SPDIF or WSI signal and removes jitter to produce a stable system clock (see Fig.4).

#### 7.3.3 WORD SELECTION DETECTION CIRCUIT

This circuit is clocked by the 12.288 MHz crystal oscillator clock and generates a Word Selection (WS) detection signal. If the WS detector does not detect any WS edge, defined as 7 times LOW and 7 times HIGH, then the WS detection signal is LOW. This information can be used to set the clock for the noise shaper in the interpolator. This will prevent noise shaper noise in the audio band.

### 7.3.4 CLOCK OUTPUT

The UDA1355H has a clock output pin (pin CLK\_OUT), which can be used to drive other audio devices in the system. In microcontroller mode the output clock is  $256f_s$  or  $384f_s$ . In static mode the output clock is 256 times 32, 44.1 and 48 kHz.

The source of the output clock is either the crystal oscillator or the PLL, depending on the selected application and control mode.

### 7.4 IEC 60958 decoder

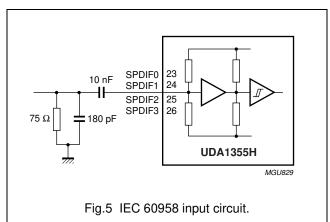

The UDA1355H IEC 60958 decoder can select one of four SPDIF input channels. An on-chip amplifier with hysteresis amplifies the SPDIF input signal to CMOS level, making it possible to accept both analog and digital SPDIF signals (see Fig.5).

### 7.4.1 AUDIO DATA

From the incoming SPDIF bitstream 24 bits of data for the left and right channel are extracted.

There is a hard mute (not a cosine roll-off mute) if the IEC 60958 decoder is out of lock or detects bi-mark phase encoding violations. The lock indicator and the key channel status bits are accessible in L3-bus mode.

The UDA1355H supports the following sample frequencies and data rates, including half and double of these frequencies:

- f<sub>s</sub> = 32 kHz; resulting in a data rate of 2.048 Mbit/s

- $f_s = 44.1$  kHz; resulting in a data rate of 2.8224 Mbit/s

- f<sub>s</sub> = 48 kHz; resulting in a data rate of 3.072 Mbit/s.

#### 7.4.2 CHANNEL STATUS AND USER BITS

As well as the data bits there are several IEC 60958 key channel status bits:

- Pre-emphasis and audio sampling frequency bits

- Two channel PCM indicator bits

- · Clock accuracy bits.

In total 40 status bits per channel are recovered from the incoming IEC 60958 bitstream. These are readable via the microcontroller interface.

User bits, which can contain a large variety of data, such as CD text, are output to pin SLICER\_SEL0 (see Table 4). In microcontroller mode this signal contains the raw user bits extracted from the SPDIF bitstream. Signal U\_RDY gives a pulse on pin MODE2 each time there is a new user bit available. Both signals can be used by an external microcontroller to grab and decode the user bits.

#### Table 4 Signal names in microcontroller mode

| PIN NAME    | SIGNAL NAME |

|-------------|-------------|

| SLICER_SEL0 | USER        |

| MODE2       | U_RDY       |

| SLICER_SEL1 | AC3         |

#### 7.4.3 DIGITAL DATA

Audio and digital data can be transmitted in the SPDIF bitstream. The PCM channel status bit should be set to logic 1 if the SPDIF bitstream is carrying digital data instead of audio data, but in practice it proves that not all equipment handles these channel status bits properly.

In the UDA1355H, digital data is detected via bit PCM, or via the sync bytes as specified by IEC. These sync bytes are two sync words, F872H and 4E1FH (two subframes) preceded by four or more subframes filled with zeros. Signal AC3 is kept HIGH for 4096 frames when the UDA1355H detects this burst preamble. Signal AC3 is present on pin SLICER\_SEL1 in microcontroller mode (see Table 4).

#### 7.5 IEC 60958 encoder

When using the crystal oscillator clock, the IEC 60958 encoder output is a full-swing digital signal with level II timing.

When the recovered clock from the PLL is used the IEC 60958 encoder will function correctly but will not meet level II timing requirements.

#### 7.5.1 STATIC MODE

All user and channel status bits are set to logic 0. This is default value specified by IEC.

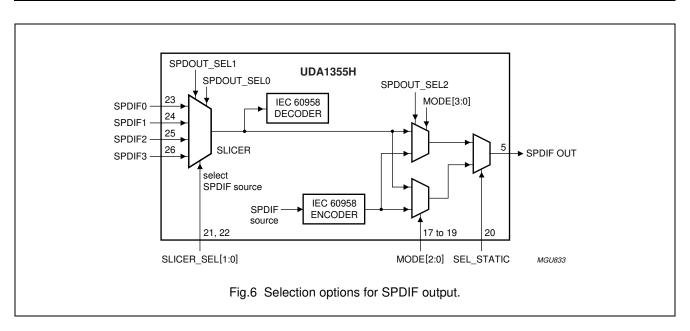

In static mode 0 and 2, the selected SPDIF input channel can be looped through to pin SPDIFOUT (see Fig.6).

#### 7.5.2 MICROCONTROLLER MODE

Two times 40 channel status bits can be set. Default value for each status bit is logic 0. When setting the channel status bits, it is possible to set only the left channel status bits and have the bits copied to the right channel.

The procedure of writing the channel status bits is as follows:

- 1. Set bit SPDO\_VALID = 0 to prevent immediately sending the status bits during writing.

- Set bit l\_r\_copy = 1 if the right channel needs the same status bits as the left channel or set bit l\_r\_copy = 0 if the right channel needs different status bits to the left channel.

- 3. Write the left and right channel status bits.

- 4. Set bit SPDO\_VALID = 1 after writing all channel status bits to the register. Starting from the next SPDIF block the IEC 60958 encoder will use the new status bits.

In microcontroller modes 2 and 13, the selected SPDIF input channel can be looped through to pin SPDIFOUT (see Fig.6).

### UDA1355H

### 7.6 Analog input

#### 7.6.1 ADC

The analog input is equipped with a Programmable Gain Amplifier (PGA) which can be controlled via the microcontroller interface. The control range is from 0 to 24 dB gain in 3 dB steps independent for the left and right channels.

In applications in with a 2 V (RMS) input signal, a 12 k $\Omega$  resistor must be used in series with the input of the ADC. The 12 k $\Omega$  resistor forms a voltage divider together with the internal ADC resistor and ensures that the voltage, applied to the input of the IC, never exceeds 1 V (RMS). In the application for a 2 V (RMS) input signal, the PGA must be set to 0 dB. When a 1 V (RMS) input signal is applied to the ADC in the same application, the PGA gain must be set to 6 dB.

An overview of the maximum input voltages allowed with and without an external resistor and the PGA gain setting is given in Table 5.

| Table 5 | Maximum input voltage; V <sub>DD</sub> = 3 V |

|---------|----------------------------------------------|

|---------|----------------------------------------------|

| EXTERNAL<br>RESISTOR<br>(12 kΩ) | PGA GAIN<br>SETTING | MAXIMUM<br>INPUT<br>VOLTAGE |

|---------------------------------|---------------------|-----------------------------|

| Present                         | 0 dB                | 2 V (RMS)                   |

|                                 | 6 dB                | 1 V (RMS)                   |

| Absent                          | 0 dB                | 1 V (RMS)                   |

|                                 | 6 dB                | 0.5 V (RMS)                 |

### 7.6.2 DECIMATION

The decimation from  $64f_s$  is performed in two stages: comb filter and decimation filter. The first stage realizes a

fourth-order  $\frac{\sin x}{x}$  characteristic with a decimation factor

of eight. The second stage consists of three half-band filters each decimating by a factor of two. Table 6 shows the characteristics.

| Table 6 | Decimation | filter | characteristics | ; |

|---------|------------|--------|-----------------|---|

| Table 6 | Decimation | tilter | characteristic  | S |

| ITEM                                          | CONDITIONS                           | VALUE (dB) |

|-----------------------------------------------|--------------------------------------|------------|

| Pass-band ripple                              | 0 to 0.45f <sub>s</sub>              | ±0.02      |

| Stop band                                     | >0.55f <sub>s</sub>                  | -60        |

| Dynamic range                                 | 0 to 0.45f <sub>s</sub>              | 140        |

| Overall gain from ADC input to digital output | DC; V <sub>I</sub> = 0 dB;<br>note 1 | -1.16      |

#### Note

1. The output is not 0 dB when  $V_{l(rms)} = 1$  V at  $V_{DD} = 3$  V. This is because the analog components can spread over the process. When there is no external resistor, the -1.16 dB scaling prevents clipping caused by process mismatch.

In the ADC path there are left and right independent digital volume controls with a range from +24 to -63.5 dB and  $-\infty \text{ dB}$ . This volume control is also used as a digital linear mute that can be used to prevent plops when powering-up or powering down the ADC front path.

### UDA1355H

#### 7.6.3 DC FILTERING

In the decimator there are two digital DC blocking circuits.

The first blocking circuit is in front of the volume control to remove DC bias from the ADC output. The DC bias is added in the ADC to prevent audio band Idle tones occurring in the noise shaper. With the DC components removed, a signal gain of 24 dB can be achieved.

The second blocking circuit removes the DC components introduced by the decimator stage.

#### 7.6.4 OVERLOAD DETECTION

Bit OVERFLOW = 1 when the output data in the left or right channel is larger than -1.16 dB of the maximum possible digital swing. This condition is set for at least  $512f_s$  cycles (that is 11.6 ms at  $f_s = 44.1$  kHz). This time-out is reset for each infringement.

### 7.7 Analog output

#### 7.7.1 AUDIO FEATURE PROCESSOR

The audio feature processor provides automatic de-emphasis for the IEC 60958 bitstream. In microcontroller mode all features are available and there is a default mute on start up.

### 7.7.2 INTERPOLATING FILTER

The digital filter interpolates from  $1f_s$  to  $64f_s$ , or from  $1f_s$  to  $128f_s$ , by cascading a half-band filter and a FIR filter.

The stereo interpolator has the following basic features:

- 24-bit data path

- Mixing of two channels:

- To prevent clipping inside the core, there is an automatic signal level correction of -6 dB scaling before mixing and +6 dB gain after digital volume control

- Position of mixing can be set before or after bass boost and treble

- Master volume control and mute with independent left and right channel settings for balance control

- Independently left and right channel de-emphasis, volume control and mute (no left or right)

- Output of the mixer is to the I<sup>2</sup>S-bus or IEC 60958 decoder.

- Full FIR filter implementation for all the upsampling filters

- Integrated digital silence detection for left and right channels with selectable silence detection time

Support for 1f<sub>s</sub> and 2f<sub>s</sub> input data rate and 192 kHz audio via I<sup>2</sup>S-bus.

The stereo interpolator has the following sound features:

- Linear volume control using 14-bit coefficients with 0.25 dB steps: range 0 to −78 dB and −∞ dB; hold for master volume and mixing volume control

- A cosine roll-off soft mute with 32 coefficients; each coefficient is used for four samples, in total 128 samples are needed to fully mute or de-mute (approximately 3 ms at  $f_s = 44.1 \text{ kHz}$ )

- Independent selectable de-emphasis for 32, 44.1, 48 and 96 kHz for both channels

- Treble is the selectable positive gain for high frequencies. The edge frequency of the treble is fixed and depends on the sampling frequency. Treble can be set independently for left and right channel with two settings:

- $f_c = 1.5 \text{ kHz}$ ;  $f_s = 44.1 \text{ kHz}$ ; 0 to 6 dB gain range with 2 dB steps

- $f_c = 3 \text{ kHz}$ ;  $f_s = 44.1 \text{ kHz}$ ; 0 to 6 dB gain range with 2 dB steps.

- Normal bass boost is the selectable positive gain for low frequencies. The edge frequency of the bass boost is fixed and depends on the sampling frequency. Normal bass boost can be set independently for the left and right channel with two sets:

- $f_c = 250 \text{ Hz}$ ;  $f_s = 44.1 \text{ kHz}$ ; 0 to 18 dB gain range with 2 dB steps

- $f_c = 300 \text{ Hz}$ ;  $f_s = 44.1 \text{ kHz}$ ; 0 to 24 dB gain range with 2 dB steps.

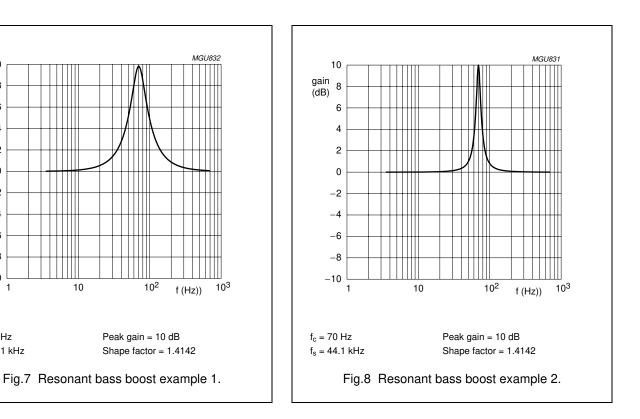

- Resonant bass boost optional function is selected if bit BASS\_SEL = 1. When selected, the characteristics are determined by six 14-bit coefficients. Resonant bass boost controls the left and right channel with the same characteristics. When resonant bass boost is selected, the treble control also changes to a single control for both channels following the gain setting of the left channel.

A software program is available for users to generate the required six 14-bit coefficients by entering the desired centre frequency ( $f_c$ ), positive or negative peak gain, sampling frequency ( $f_s$ ) and shape factor (see Figs 7 and 8).

### UDA1355H

| ITEM             | CONDITIONS                | VALUE (dB) |

|------------------|---------------------------|------------|

| Pass-band ripple | 0 to 0.45f <sub>s</sub>   | ±0.035     |

| Stop band        | >0.55f <sub>s</sub>       | -60        |

| Dynamic range    | 0 to 0.4535f <sub>s</sub> | 140        |

Table 7

Interpolation filter characteristics

#### 7.7.3 **DIGITAL MIXER**

10

8

6

4

2

0

-2

-4

-6

-8

-10

f<sub>c</sub> = 70 Hz

f<sub>s</sub> = 44.1 kHz

10

10<sup>2</sup>

gain

(dB)

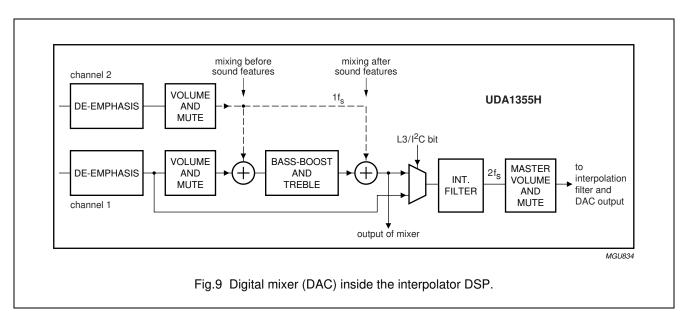

The UDA1355H has a digital mixer inside the interpolator. The digital mixer can be used as a cross over or a selector. A functional block diagram of the mixer mode is shown in Fig.9. This mixer can be used in microcontroller mode only.

The UDA1355H can be set to the mixer mode by setting bit MIX = 1. In the mixer mode, there are three volume and mute controls available: for source 1, for source 2 and for the master (sum) signal. All three volume ranges can be controlled in 0.25 dB steps.

To prevent clipping inside the mixer, the signals are scaled with -6 dB before mixing, therefore the sum of the two signals is always equal to or lower than 0 dB. After the mixing there is a 6 dB gain in the master volume control. This means that at the analog output the signal can clip, but the clipping can be undone by decreasing the master volume control.

The output of the mixer is available via the I<sup>2</sup>S-bus output or via the SPDIF output. The output signal of the mixer is scaled to a maximum of 0 dB, so the digital output can never clip.

### UDA1355H

### 7.7.4 DIGITAL SILENCE DETECTOR

The UDA1355H is equipped with a digital silence detector. This detects whether a certain amount of consecutive samples are 0. The number of samples can be set with bits SD\_VALUE[1:0] to 3200, 4800, 9600 or 19600 samples.

The digital silence detection status can be read via the microcontroller interface.

#### 7.7.5 NOISE SHAPER (DAC)

The noise shaper shifts in-band quantization noise to frequencies above the audio band. The noise shaper output is converted into an analog signal using a Filter Stream Digital-to-Analog Converter (FSDAC). This noise shaping technique enables high signal-to-noise ratios to be achieved.

The UDA1355H is equipped with two noise shapers:

- A third-order noise shaper operating at 128fs. Which is used at low sampling frequencies (8 to 16 kHz) to prevent noise shaper noise shifting into the audio band for the fifth-order noise shaper

- A fifth-order noise shaper operating at 64f<sub>s</sub>. Which is used at high sampling frequencies (from 32 kHz upwards).

When the noise shaper changes, the clock to the FSDAC changes and the filter characteristic of the FSDAC also changes. The effect on the roll of is compensated by selecting the filter matching speed and order of the noise shaper.

### 7.7.6 FILTER STREAM DAC

The FSDAC is a semi digital reconstruction filter that converts the 1-bit data bitstream of the noise shaper to an analog output voltage. The filter coefficients are implemented as current sources and are summed at virtual ground of the operational amplifier output. In this way, very high signal-to-noise performance and low clock jitter sensitivity are achieved. A post filter is not needed due to the inherent filter function of the FSDAC. On-chip amplifiers convert the FSDAC output current to an output voltage signal capable of driving a line output. The output voltage of the FSDAC scales proportionally with the supply voltage.

#### 7.7.7 DAC MUTE

The DAC and interpolator can be muted by setting pin MUTE to a HIGH level. The output signal is muted to zero via a cosine roll-off curve and the DAC is powered down. When pin MUTE is at LOW level the signal rise follows the same cosine curve.

To prevent plops in case of changing inputs, clock to the DAC or application modes, a special mute circuit for the DAC is implemented (see Table 8).

In all application modes in which the DAC is active the DAC can be muted by pin MUTE. The microcontroller mute bits and pin MUTE act as an OR function.

### UDA1355H

#### Table 8 Muting to prevent plopping

| 000401011                         |                | BIT  |     |                                |

|-----------------------------------|----------------|------|-----|--------------------------------|

| OCCASION                          | MT1            | MT2  | МТМ | - DE-MUTE CONDITION            |

| Input selection                   |                |      |     |                                |

| Select channel 1 source           | х              | _    | _   | no mute after selection        |

| Select channel 2 source           | -              | х    | -   | no mute after selection        |

| Select chip mode                  |                |      |     |                                |

| PLL is source for the DAC         | -              | -    | х   | wait until PLL is locked again |

| Crystal is source for the DAC     | -              | -    | х   | no mute after selection        |

| Select between microcontroller mc | ode and static | mode |     |                                |

| PLL is source for the DAC         | -              | _    | x   | wait until PLL is locked again |

| Crystal is source for the DAC     | -              | _    | х   | no mute after selection        |

| Audio features                    |                |      |     |                                |

| Select noise shaper order         | -              | -    | х   | no mute after selection        |

| Select FSDAC output polarity      | -              | -    | х   | no mute after selection        |

| Select SPDIF input                | -              | -    | х   | PLL is locked again            |

| Select mixer                      | -              | -    | _   | no mute needed                 |

| Select mixer position             | -              | -    | _   | no mute needed                 |

| Select crystal clock source       | -              | _    | х   | no mute after selection        |

### 7.8 Digital audio input and output

The selection of the digital audio input and output formats and master or slave modes differ for static and microcontroller mode.

In master mode, when  $256f_s$  output clock is selected and the digital interface is master, the BCK output clock will be  $64f_s$ . In case  $384f_s$  output clock is selected, the BCK output clock will be  $48f_s$ .

In the static mode the digital audio input formats are:

- I<sup>2</sup>S-bus

- LSB-justified; 16 bits

- LSB-justified; 24 bits

- MSB-justified.

The digital audio output formats are:

- I<sup>2</sup>S-bus

- MSB-justified.

In the microcontroller mode, the following formats are independently selectable:

- I<sup>2</sup>S-bus

- LSB-justified; 16 bits

- LSB-justified; 18 bits

- LSB-justified; 20 bits

- LSB-justified; 24 bits

- MSB-justified.

### 7.9 Power-on reset

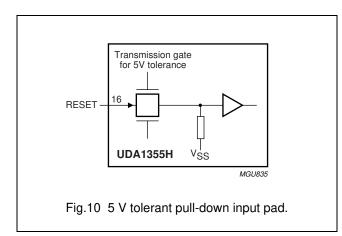

The UDA1355H has a dedicated reset pin with an internal pull-down resistor. In this way a Power-on reset circuit can be made with a capacitor and a resistor at pin RESET. The external resistor is needed since the pad is 5 V tolerant. This means that there is a transmission gate in series with the input and the resistor inside the pad cannot be seen from the outside world (see Fig.10).

The reset timing is determined by the external pull-down resistor and the external capacitor which is connected to pin RESET. At Power-on reset, all the digital sound processing features and the system controlling features are set to the default setting of the microcontroller mode. Since the bit controlling the clock of the synchronous registers is set to enable, the synchronous registers are also reset.

### UDA1355H

The clock should be running during the reset time. When no clock can be guaranteed in microcontroller mode, a soft reset should be given when the system is running by writing to register 7FH.

#### 8 APPLICATION MODES

In this chapter the application modes for static mode and microcontroller mode are described.

The UDA1355H can be controlled by static pins, the L3-bus or  $I^2C$ -bus interface. Due to the limitations imposed by the pin count, only basic functions are available in static mode. For optimum use of the UDA1355H features, the microcontroller mode is strongly recommended.

There are 11 application modes available in the static mode and 14 application modes in microcontroller mode. The application modes are explained in the two sections: Section 8.2 explains the application modes 0 to 10. Section 8.4 explains the more advanced features of modes 0 to 10 and modes 12 to 14 available in the microcontroller mode.

#### 8.1 Static mode pin assignment

The default values for all non-pin controlled settings are identical to the start-up defaults from the microcontroller mode. Whether BCK and WS are master or slave depends on the selected application mode.

Table 9 defines the pin functions in static mode.

| PIN           | STATIC MODE<br>SYMBOL  | LEVEL      | DESCRIPTION                                                                                                     |

|---------------|------------------------|------------|-----------------------------------------------------------------------------------------------------------------|

| 4             | LOCK LOW               |            | IEC 60958 decoder out of lock (when SPDIF input) or clock regeneration out of lock (I <sup>2</sup> S-bus input) |

|               |                        | HIGH       | IEC 60958 decoder in lock (when SPDIF input) or clock regeneration in lock (I <sup>2</sup> S-bus input)         |

| 16            | RESET                  | LOW        | normal operation                                                                                                |

|               |                        | HIGH       | reset                                                                                                           |

| 17, 18,<br>19 | MODE0, MODE1,<br>MODE2 | -          | select application mode; see Table 10                                                                           |

| 20            | SEL_STATIC             | HIGH       | static pin control                                                                                              |

|               |                        | LOW        | microcontroller mode                                                                                            |

| 22, 21        | SLICER_SEL1,           | LOW, LOW   | IEC 60958 input from pin SPDIF0                                                                                 |

|               | SLICER_SEL0            | LOW, HIGH  | IEC 60958 input from pin SPDIF1                                                                                 |

|               |                        | HIGH, LOW  | IEC 60958 input from pin SPDIF2                                                                                 |

|               |                        | HIGH, HIGH | IEC 60958 input from pin SPDIF3                                                                                 |

| 29            | FREQ_SEL               | LOW        | select 44.1 kHz sampling frequency for the crystal oscillator, note 1                                           |

|               |                        | MID        | select 32 kHz sampling frequency for the crystal oscillator, note 1                                             |

|               |                        | HIGH       | select 48 kHz sampling frequency for the crystal oscillator, note 1                                             |

Table 9

Static mode pin assignment

### UDA1355H

| PIN    | STATIC MODE<br>SYMBOL | LEVEL      | DESCRIPTION                                                                                                                  |

|--------|-----------------------|------------|------------------------------------------------------------------------------------------------------------------------------|

| 30, 31 | SFOR1, SFOR0          | LOW, LOW   | set I <sup>2</sup> S-bus format for digital data input and output interface                                                  |

|        |                       | LOW, HIGH  | set LSB-justified 16 bits format for digital data input interface and MSB-justified format for digital data output interface |

|        |                       | HIGH, LOW  | set LSB-justified 24 bits format for digital data input interface and MSB-justified format for digital data output interface |

|        |                       | HIGH, HIGH | set MSB-justified format for digital data input and output interface                                                         |

| 44     | MUTE                  | LOW        | normal operation                                                                                                             |

|        |                       | HIGH       | mute active                                                                                                                  |

#### Note

1. FPLL 256fs is output from pin CLKOUT in PLL locked static mode.

#### 8.2 Static mode basic applications

The static application modes are selected with the pins MODE2, MODE1 and MODE0, with pin MODE0 being a 3-level pin. In Table 10, the encoding of the pins MODE[2:0] is given.

|      | MODE SELECTION PINS <sup>(1)</sup> |       |       | MODE SELECTION PINS <sup>(1)</sup> CLOCK <sup>(2)</sup> |                 |      |      |                                        |                                          | PLL                  |

|------|------------------------------------|-------|-------|---------------------------------------------------------|-----------------|------|------|----------------------------------------|------------------------------------------|----------------------|

| MODE | MODE2                              | MODE1 | MODE0 | SPDIF<br>INPUT                                          | SPDIF<br>OUTPUT | ADC  | DAC  | I <sup>2</sup> S-BUS<br>INPUT<br>SLAVE | I <sup>2</sup> S-BUS<br>OUTPUT<br>MASTER | LOCKS<br>ON<br>INPUT |

| 0    | L                                  | L     | L     | PLL                                                     | PLL             | —    | PLL  | Ι                                      | PLL                                      | SPDIF                |

| 1    | L                                  | L     | М     | Ι                                                       | PLL             | _    | PLL  | PLL                                    | _                                        | I <sup>2</sup> S-bus |

| 2    | L                                  | L     | Н     | PLL                                                     | PLL             | _    | PLL  | PLL                                    | PLL                                      | SPDIF                |

| 3    | L                                  | Н     | L     | _                                                       | xtal            | xtal | -    | -                                      | xtal                                     | -                    |

| 4    | L                                  | Н     | М     | Ι                                                       | xtal            | xtal | xtal | xtal                                   | xtal                                     | _                    |

| 5    | L                                  | Н     | Н     | _                                                       | xtal            | xtal | xtal | xtal                                   | xtal                                     | -                    |

| 6    | Н                                  | L     | L     | _                                                       | PLL             | xtal | PLL  | PLL                                    | xtal                                     | I <sup>2</sup> S-bus |

| 7    | Н                                  | L     | М     | PLL                                                     | xtal            | xtal | PLL  | -                                      | xtal                                     | SPDIF                |

| 8    | Н                                  | L     | Н     | -                                                       | xtal            | xtal | PLL  | PLL                                    | xtal                                     | I <sup>2</sup> S-bus |

| 9    | Н                                  | Н     | L     | PLL                                                     | xtal            | _    | xtal | xtal                                   | PLL                                      | SPDIF                |

| 10   | Н                                  | Н     | М     | PLL                                                     | xtal            | _    | PLL  | xtal                                   | PLL                                      | SPDIF                |

| 11   | Н                                  | Н     | Н     | not used                                                |                 |      |      |                                        |                                          |                      |

#### Table 10 Static mode basic applications

#### Notes

1. In column mode selection pins means:

L: pin at 0 V; M: pin at half  $V_{DDD}$ ; H: pin at  $V_{DDD}$ .

2. In column clock means:

xtal: the clock is based on the crystal oscillator; PLL: the clock is based on the PLL.

### UDA1355H

The first 11 application modes are given in this section. Schematic diagrams of these application modes are given in Table 11. In this table the basic features are mentioned and also the extra features in case of microcontroller mode are given. It should be noted that the blocks running at the crystal clock (XTAL) are marked unshaded while the blocks running at the PLL clock are shaded.

| able 11 Overview of static mode basic applications |

|----------------------------------------------------|

|----------------------------------------------------|

| MODE | FEATURES                                                                                                                                                                                                                                                                                                                                                                                                    | SCHEMATIC                                                                                                             |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 0    | <ul> <li>Data path:</li> <li>Input SPDIF to outputs DAC, I<sup>2</sup>S or SPDIFOUT via loop through.</li> <li>Features:</li> <li>System locks onto the SPDIF input signal</li> <li>BCK and WS are master</li> <li>Microcontroller mode: <ul> <li>DAC sound features can be used</li> <li>SPDIF input channel status bits (two times 40 bits) can be read.</li> </ul> </li> </ul>                           | PLL SPDIF LOCK<br>MUTE<br>DAC<br>SPDIFOUT<br>SPDIF IN<br>I <sup>2</sup> S OUTPUT<br>I <sup>2</sup> S master<br>MGU836 |

| 1    | <ul> <li>Data path:</li> <li>Input I<sup>2</sup>S to outputs DAC or SPDIF (level II not guaranteed: depends on I<sup>2</sup>S-bus clock).</li> <li>Features:</li> <li>System locks onto the WSI signal</li> <li>BCKI and WSI are slave</li> <li>Microcontroller mode: <ul> <li>DAC sound features can be used</li> <li>SPDIF output channel status bits (two times 40 bits) setting.</li> </ul> </li> </ul> | PLL I <sup>2</sup> S LOCK<br>MUTE<br>DAC<br>I <sup>2</sup> S slave → I <sup>2</sup> S INPUT<br>MGUB37                 |

| MODE | FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SCHEMATIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |