Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **UDA1384**

# Multichannel audio coder-decoder

Rev. 02 — 17 January 2005

**Product data sheet**

#### **General description** 1.

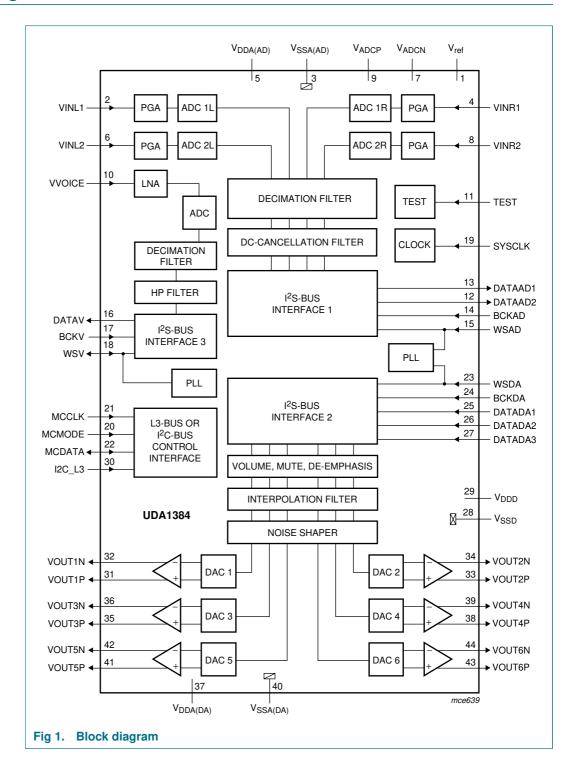

The UDA1384 is a single-chip consisting of 4 plus 1 Analog-to-Digital Converters (ADC) and 6 Digital-to-Analog Converters (DAC) with signal processing features employing bitstream conversion techniques. The multichannel configuration makes the device eminently suitable for use in digital audio equipment which incorporates surround feature.

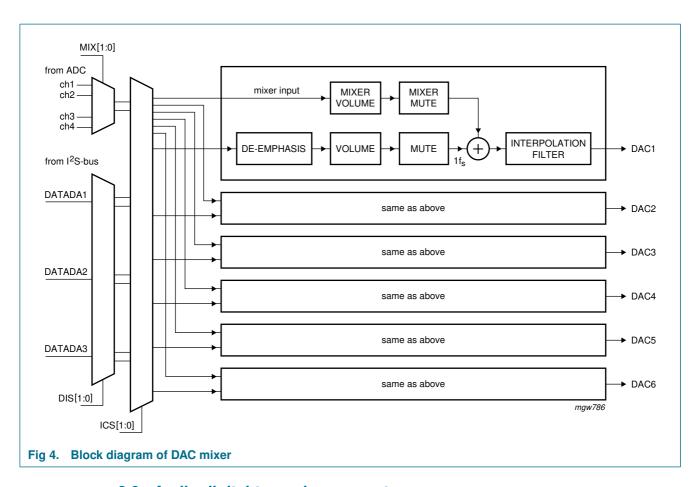

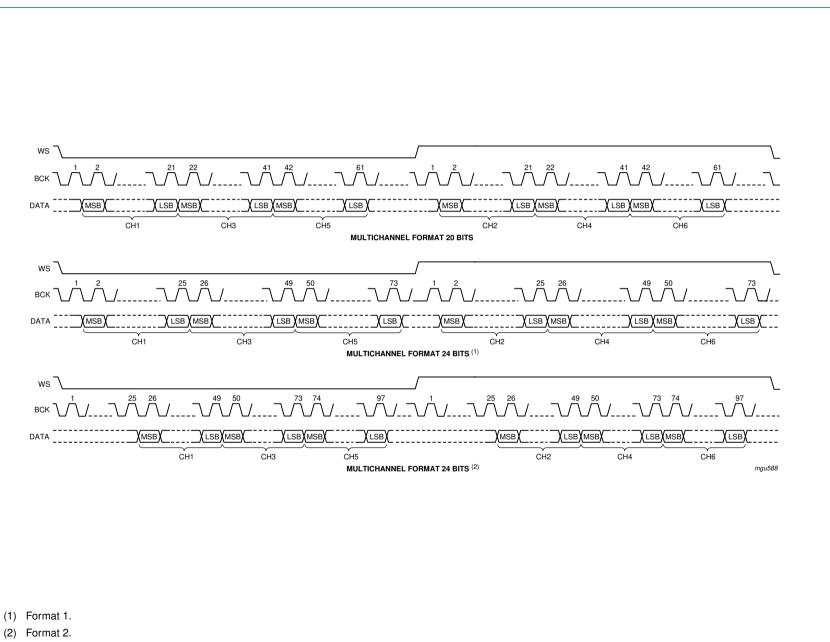

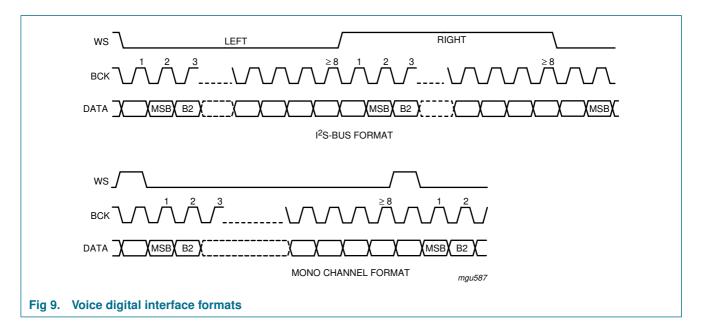

The UDA1384 supports conventional 2 channels per line data transfer conformable to the I<sup>2</sup>S-bus format with word lengths of up to 24 bits, the MSB-justified format with word lengths of up to 24 bits and the LSB-justified format with word lengths of 16 bits, 20 bits and 24 bits, as well as 4 channels to 6 channels per line transfer mode. The device also supports a combination of the MSB-justified output format and the LSB-justified input format. The UDA1384 has special sound processing features in the Direct Stream Digital (DSD) playback mode, de-emphasis, volume and mute which can be controlled via the L3-bus or I<sup>2</sup>C-bus interface.

#### 2. **Features**

#### 2.1 General

- 2.7 V to 3.6 V power supply

- 5 V tolerant digital inputs

- 24-bit data path

- Selectable control: via L3-bus or l<sup>2</sup>C-bus microcontroller interface

- Supports sample frequency ranges for:

- Audio ADC: f<sub>s</sub> = 16 kHz to 100 kHz

- Voice ADC: f<sub>s</sub> = 7 kHz to 50 kHz

- ◆ Audio DAC: f<sub>s</sub> = 16 kHz to 200 kHz

- Separate power control for ADC and DAC

- ADC plus integrated high-pass filter to cancel DC offset

- Integrated digital filter plus DAC

- Slave mode only applications

- Easy application

#### Multichannel audio coder-decoder

# 2.2 Multiple format data interface

- Audio interface supports standard I<sup>2</sup>S-bus, MSB-justified, LSB-justified and two multichannel formats

- Voice interface supports I<sup>2</sup>S-bus and mono channel formats

### 2.3 Digital sound processing

- Control via L3-bus or I<sup>2</sup>C-bus:

- Channel independent digital logarithmic volume

- ◆ Digital de-emphasis for f<sub>s</sub> = 32 kHz, 44.1 kHz, 48 kHz or 96 kHz

- Soft or quick mute

- Output signal polarity control

# 2.4 Advanced audio configuration

- Inputs:

- ◆ 4 single-ended audio inputs (2 × stereo) with programmable gain amplifiers

- ◆ 1 single-ended voice input

- Outputs:

- ◆ 6 differential audio outputs (3 × stereo)

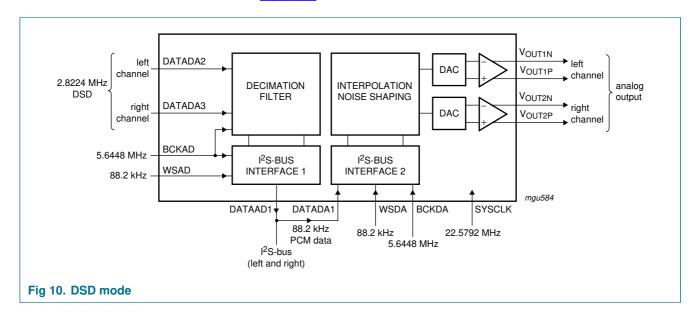

- DSD mode to support stereo DSD playback

- High linearity, wide dynamic range and low distortion

- DAC digital filter with selectable sharp or soft roll-off

# 3. Applications

■ Excellently suitable for multichannel home audio-video application

# 4. Quick reference data

Table 1: Quick reference data

$V_{DDD} = V_{DDA(AD)} = V_{DDA(DA)} = 3.3 \text{ V; } T_{amb} = 25 \,^{\circ}\text{C; } R_L = 22 \,\text{k}\Omega; \text{ all voltages referenced to ground (pins $V_{SS}$); unless otherwise specified.}$

| Symbol               | Parameter                 | Conditions                                                            | Min | Тур | Max | Unit |

|----------------------|---------------------------|-----------------------------------------------------------------------|-----|-----|-----|------|

| Supplies             |                           |                                                                       |     |     |     |      |

| V <sub>DDA(AD)</sub> | ADC analog supply voltage |                                                                       | 2.7 | 3.3 | 3.6 | V    |

| V <sub>DDA(DA)</sub> | DAC analog supply voltage |                                                                       | 2.7 | 3.3 | 3.6 | V    |

| $V_{DDD}$            | digital supply voltage    |                                                                       | 2.7 | 3.3 | 3.6 | V    |

| I <sub>DDA(AD)</sub> | ADC analog supply current | $f_{ADC} = 48 \text{ kHz}$                                            | -   | 30  | -   | mA   |

| I <sub>DDA(DA)</sub> | DAC analog supply current | $f_{DAC} = 48 \text{ kHz}$                                            | -   | 20  | -   | mA   |

| I <sub>DDD</sub>     | digital supply current    | $f_{ADC} = f_{DAC} = 48 \text{ kHz};$<br>$f_{VOICE} = 48 \text{ kHz}$ | -   | 31  | -   | mA   |

9397 750 14366

#### Multichannel audio coder-decoder

Table 1: Quick reference data ...continued

$V_{DDD} = V_{DDA(AD)} = V_{DDA(DA)} = 3.3 \text{ V}; T_{amb} = 25 \,^{\circ}\text{C}; R_L = 22 \, \text{k}\Omega;$  all voltages referenced to ground (pins  $V_{SS}$ ); unless otherwise specified.

| $ \frac{\text{lodD(pd)}}{\text{in Power-down mode}} \begin{tabular}{ll} & audio and voice & ADCs power-down & - & 14 & - & mA \\ \hline T_{amb} & ambient temperature & -20 & - & +85 & ^{\circ}C \\ \hline {Audio analog-to-digital converter} \\ \hline D_0 & digital output level & 900 mV input \\ \hline (THD+N)/S & total harmonic distortion-plus-noise to signal ratio & code = 0; A-weighted & 89 & 98 & - & dB \\ \hline {\alpha_{cs}} & channel separation & at 0 dBFS digital input & 1.9 & 2.0 & 2.1 & V \\ \hline (THD+N)/S & total harmonic distortion-plus-noise ratio & code = 0; A-weighted & 89 & 98 & - & dB \\ \hline {\alpha_{cs}} & channel separation & - & 100 & - & dB \\ \hline {Digital-to-analog converter} \\ \hline Differential mode & volumber & at 0 dBFS digital input & 1.9 & 2.0 & 2.1 & V \\ \hline {CTHD+N}/S & total harmonic distortion-plus-noise to signal ratio & code = 0; A-weighted & 100 & 110 & - & dB \\ \hline {\alpha_{cs}} & channel separation & - & -50 & -45 & dB \\ \hline {\alpha_{cs}} & channel separation & - & 114 & - & dB \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & at 0 dBFS digital input & - & -50 & -45 & dB \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -50 & -45 & dB \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -50 & -45 & dB \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -88 & - & dB \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -88 & - & dB \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -88 & - & dB \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -88 & - & dB \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -88 & - & dB \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -88 & - & dB \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -88 & - & dB \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -88 & - & dB \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -88 & - & -88 \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -88 & - & -88 \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -88 & - & -88 \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -88 & - & -88 \\ \hline {C}_{(rms)} & coultput voltage (RMS value) & - & -88 & - & -88 \\ \hline {C}_{($                                                              | Symbol              | Parameter              | Conditions           |         | Min  | Тур  | Max        | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|----------------------|---------|------|------|------------|------|

| Tamb   ambient temperature   -20   -   +85   °C   Audio analog-to-digital converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $I_{DDD(pd)}$       |                        |                      |         | -    | 18   | -          | mA   |

| Audio analog-to-digital converter           D₀         digital output level (digital output level 200 mV input)         at 0 dB setting; 900 mV input         [1][2] -2.5 -1.2 -0.7 dB         dB           (THD+N)/S (THD+N)/S (distortion-plus-noise to signal ratio)         at -1 dBFS at -60 dBFS; A-weighted         - 88 -82 dB         dB           S/N (Signal-to-noise ratio) coses         channel separation         code = 0; A-weighted         89 98 - dB         dB           Digital-to-analog converter         bigital-to-analog conve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                        | DAC power-down       |         | -    | 14   | -          | mA   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | T <sub>amb</sub>    | ambient temperature    |                      |         | -20  | -    | +85        | °C   |

| ThD+N)/S   total harmonic distortion-plus-noise to signal ratio   at -1 dBFS  88   -82   dB   at -60 dBFS;   -37   -30   dB   at -60 dBFS;   -37   -45   -37   dB   at -60 dBFS;   -37   -37   -30   dB   at -60 dBFS;   -37   -37   -37   -30   dB   at -60 dBFS;   -37   -37   -37   -37   -37   -30   dB   at -60 dBFS;   -37   -37   -37   -37   -37   -37   -37   -3                                                                                                                                                                                                                                                                                       | Audio analo         | g-to-digital converter |                      |         |      |      |            |      |

| $\frac{\text{distortion-plus-noise}}{\text{to signal ratio}}  \frac{\text{at } -60 \text{ dBFS};}{\text{A-weighted}}  -  -37  -30  \text{dB}}{\text{A-weighted}}$ $S/N  \text{signal-to-noise ratio}  \text{code} = 0; \text{A-weighted}  89  98  -  \text{dB}}{\text{C}_{\text{CS}}}  \text{channel separation}  -  100  -  \text{dB}}{\text{Digital-to-analog converter}}$ $\frac{\text{Differential mode}}{\text{Differential mode}}  \text{Differential mode}$ $V_{\text{O(rms)}}  \text{output voltage}  \text{at 0 dBFS digital}  1.9  2.0  2.1  V  \text{orms}  \text{output voltage}  \text{finput}  \text{input}  \text{output voltage}  \text{for dBFS};  -  -98  -89  \text{dB}}{\text{distortion-plus-noise}}  \text{at 0 dBFS};  -  -50  -45  \text{dB}}{\text{A-weighted}}$ $S/N  \text{signal-to-noise ratio}  \text{code} = 0; \text{A-weighted}  100  110  -  \text{dB}}{\text{A-weighted}}$ $S_{\text{O(rms)}}  \text{output voltage}  \text{at 0 dBFS digital}  -  114  -  \text{dB}}{\text{Single-ended mode}}$ $V_{\text{O(rms)}}  \text{output voltage}  \text{at 0 dBFS digital}  -  1.0  -  V  \text{output voltage}  \text{finput}}{\text{input}}$ $(THD+N)/S  \text{total harmonic}  \text{distortion-plus-noise}  \text{do dBFS};  -  -88  -  \text{dB}}{\text{dasortion-plus-noise}}  \text{at 0 dBFS};  -  -45  -  \text{dB}}{\text{dasortion-plus-noise}}  \text{do dBFS};  -  -45  -  \text{dB}}{\text{dasortion-plus-noise}}  \text{do dBFS};  -  -45  -  \text{dB}}{\text{dasortion-plus-noise}}  \text{dasortion-plus-noise}}  \text{dasortion-plus-noise}  \text{dasortion-plus-noise}}  \text{dasortion-plus-noise}  \text{dasortion-plus-noise}}  \text{dasortion-plus-noise}  \text{dasortion-plus-noise}}  \text{dasortion-plus-noise}  \text$ | D <sub>0</sub>      | digital output level   |                      | [1] [2] | -2.5 | -1.2 | -0.7       | dB   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (THD+N)/S           |                        | at -1 dBFS           |         | -    | -88  | -82        | dB   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                        |                      |         | -    | -37  | -30        | dB   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S/N                 | signal-to-noise ratio  | code = 0; A-weighted |         | 89   | 98   | -          | dB   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\alpha_{cs}$       | channel separation     |                      |         | -    | 100  | -          | dB   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Digital-to-ar       | nalog converter        |                      |         |      |      |            |      |

| (RMS value)         input           (THD+N)/S         total harmonic distortion-plus-noise to signal ratio         at 0 dBFS98 -89 dB           S/N         signal-to-noise ratio         code = 0; A-weighted           S/N         signal-to-noise ratio         code = 0; A-weighted           Single-ended mode         - 114 - dB           Single-ended mode         - 114 - dB           Vo(rms)         output voltage (RMS value)         at 0 dBFS digital input         - 1.0 - V           (THD+N)/S         total harmonic distortion-plus-noise to signal ratio         at 0 dBFS;45 - dB           A-weighted        45 - dB           S/N         signal-to-noise ratio         code = 0; A-weighted         - 105 - dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Differential n      | node                   |                      |         |      |      |            |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $V_{o(rms)}$        |                        | •                    |         | 1.9  | 2.0  | 2.1        | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (THD+N)/S           |                        | at 0 dBFS            |         | -    | -98  | -89        | dB   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                        | •                    |         | -    | -50  | <b>–45</b> | dB   |

| Single-ended mode           Vo(rms)         output voltage (RMS value)         at 0 dBFS digital input         -         1.0         -         V           (THD+N)/S         total harmonic distortion-plus-noise to signal ratio         at 0 dBFS         -         -88         -         dB           S/N         signal-to-noise ratio         code = 0; A-weighted         -         105         -         dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | S/N                 | signal-to-noise ratio  | code = 0; A-weighted |         | 100  | 110  | -          | dB   |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\alpha_{cs}$       | channel separation     |                      |         | -    | 114  | -          | dB   |

| $ (RMS \ value) \qquad input \\ (THD+N)/S \qquad total \ harmonic \\ distortion-plus-noise \\ to \ signal \ ratio \qquad at \ 0 \ dBFS \qquad - \qquad -88 \qquad - \qquad dB \\ \hline at \ -60 \ dBFS; \qquad - \qquad -45 \qquad - \qquad dB \\ \hline S/N \qquad signal-to-noise \ ratio \qquad code = 0; A-weighted \qquad - \qquad 105 \qquad - \qquad dB $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Single-ended        | d mode                 |                      |         |      |      |            |      |

| distortion-plus-noise to signal ratio  at -60 dBFS;45 - dB  A-weighted  S/N signal-to-noise ratio code = 0; A-weighted - 105 - dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>o(rms)</sub> |                        | •                    |         | -    | 1.0  | -          | V    |

| to signal ratio  A-weighted  S/N signal-to-noise ratio code = 0; A-weighted - 105 - dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (THD+N)/S           | total harmonic         | at 0 dBFS            |         | -    | -88  | -          | dB   |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |                        |                      |         | -    | -45  | -          | dB   |

| $\alpha_{cs}$ channel separation - 110 - dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | S/N                 | signal-to-noise ratio  | code = 0; A-weighted |         | -    | 105  | -          | dB   |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\alpha_{cs}$       | channel separation     |                      |         | -    | 110  | -          | dB   |

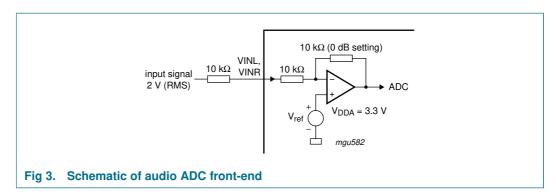

<sup>[1]</sup> The input voltage can be up to 2 V (RMS) when the current through the ADC input pin is limited to approximately 1 mA by using a series resistor.

# 5. Ordering information

Table 2: Ordering information

| Type number | Package |                                                                                              |          |  |  |

|-------------|---------|----------------------------------------------------------------------------------------------|----------|--|--|

|             | Name    | Description                                                                                  | Version  |  |  |

| UDA1384H    | QFP44   | plastic quad flat package; 44 leads (lead length 1.3 mm); body $10 \times 10 \times 1.75$ mm | SOT307-2 |  |  |

<sup>[2]</sup> The input voltage to the ADC scales proportionally with the power supply voltage.

# Multichannel audio coder-decoder

# 6. Block diagram

# Multichannel audio coder-decoder

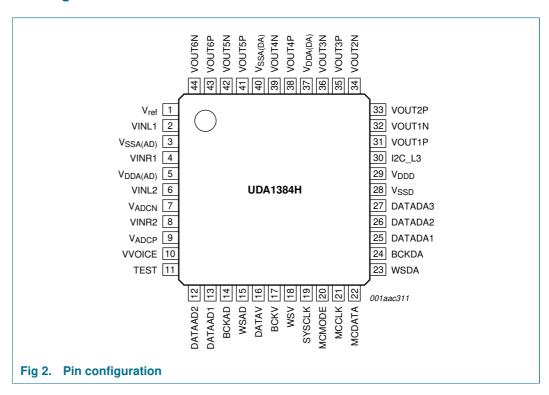

# 7. Pinning information

# 7.1 Pinning

# 7.2 Pin description

Table 3: Pin description

| Symbol               | Pin | Туре | Description                                                                                     |

|----------------------|-----|------|-------------------------------------------------------------------------------------------------|

| V <sub>ref</sub>     | 1   | AIO  | ADC reference voltage                                                                           |

| VINL1                | 2   | AIO  | ADC 1 input left                                                                                |

| V <sub>SSA(AD)</sub> | 3   | AGND | ADC analog ground                                                                               |

| VINR1                | 4   | AIO  | ADC 1 input right                                                                               |

| V <sub>DDA(AD)</sub> | 5   | AS   | ADC analog supply voltage                                                                       |

| VINL2                | 6   | AIO  | ADC 2 input left                                                                                |

| V <sub>ADCN</sub>    | 7   | AIO  | ADC reference voltage N                                                                         |

| VINR2                | 8   | AIO  | ADC 2 input right                                                                               |

| V <sub>ADCP</sub>    | 9   | AIO  | ADC reference voltage P                                                                         |

| VVOICE               | 10  | AIO  | voice ADC input                                                                                 |

| TEST                 | 11  | DID  | test input; must be connected to digital ground $(V_{\mbox{\footnotesize SSD}})$ in application |

| DATAAD2              | 12  | DO   | ADC 2 data output                                                                               |

| DATAAD1              | 13  | DO   | ADC 1 data output                                                                               |

| BCKAD                | 14  | DIS  | ADC bit clock input                                                                             |

| WSAD                 | 15  | DI   | ADC word select input                                                                           |

### Multichannel audio coder-decoder

Table 3:

Pin description ...continued

| iubic o.                    | The descriptioncommaca |      |                                                                                                    |  |

|-----------------------------|------------------------|------|----------------------------------------------------------------------------------------------------|--|

| Symbol                      | Pin                    | Туре | Description                                                                                        |  |

| DATAV                       | 16                     | DO   | voice data output                                                                                  |  |

| BCKV                        | 17                     | DIS  | voice bit clock input                                                                              |  |

| WSV                         | 18                     | DIO  | voice word select input or output                                                                  |  |

| SYSCLK                      | 19                     | DIS  | system clock input: 256f <sub>s</sub> , 384f <sub>s</sub> , 512f <sub>s</sub> or 768f <sub>s</sub> |  |

| MCMODE                      | 20                     | DI   | L3-bus L3MODE input or I <sup>2</sup> C-bus DAC mute control input                                 |  |

| MCCLK                       | 21                     | DIS  | L3-bus L3CLOCK input or I2C-bus SCL input                                                          |  |

| MCDATA                      | 22                     | IIC  | L3-bus L3DATA input and output or I2C-bus SDA input and output                                     |  |

| WSDA                        | 23                     | DI   | DAC word select input                                                                              |  |

| BCKDA                       | 24                     | DIS  | DAC bit clock input                                                                                |  |

| DATADA1                     | 25                     | DI   | DAC channel 1 and channel 2 data input                                                             |  |

| DATADA2                     | 26                     | DI   | DAC channel 3 and channel 4 data input                                                             |  |

| DATADA3                     | 27                     | DI   | DAC channel 5 and channel 6 data input                                                             |  |

| $V_{SSD}$                   | 28                     | DGND | digital ground                                                                                     |  |

| $V_{DDD}$                   | 29                     | DS   | digital supply voltage                                                                             |  |

| I2C_L3                      | 30                     | DI   | selection input for L3-bus or I <sup>2</sup> C-bus control                                         |  |

| VOUT1P                      | 31                     | AIO  | DAC 1 positive output                                                                              |  |

| VOUT1N                      | 32                     | AIO  | DAC 1 negative output                                                                              |  |

| VOUT2P                      | 33                     | AIO  | DAC 2 positive output                                                                              |  |

| VOUT2N                      | 34                     | AIO  | DAC 2 negative output                                                                              |  |

| VOUT3P                      | 35                     | AIO  | DAC 3 positive output                                                                              |  |

| VOUT3N                      | 36                     | AIO  | DAC 3 negative output                                                                              |  |

| $V_{DDA(DA)} \\$            | 37                     | AS   | DAC analog supply voltage                                                                          |  |

| VOUT4P                      | 38                     | AIO  | DAC 4 positive output                                                                              |  |

| VOUT4N                      | 39                     | AIO  | DAC 4 negative output                                                                              |  |

| $V_{\text{SSA}(\text{DA})}$ | 40                     | AGND | DAC analog ground                                                                                  |  |

| VOUT5P                      | 41                     | AIO  | DAC 5 positive output                                                                              |  |

| VOUT5N                      | 42                     | AIO  | DAC 5 negative output                                                                              |  |

| VOUT6P                      | 43                     | AIO  | DAC 6 positive output                                                                              |  |

| VOUT6N                      | 44                     | AIO  | DAC 6 negative output                                                                              |  |

|                             |                        |      |                                                                                                    |  |

# [1] See <u>Table 4</u>.

Table 4: Pin types

| Туре | Description                                    |

|------|------------------------------------------------|

| AGND | analog ground                                  |

| AIO  | analog input and output                        |

| AS   | analog supply                                  |

| DGND | digital ground                                 |

| DI   | digital input                                  |

| DID  | digital input with internal pull-down resistor |

| DIO  | digital input and output                       |

Multichannel audio coder-decoder

Table 4: Pin types ...continued

| Туре | Description                                          |

|------|------------------------------------------------------|

| DIS  | digital Schmitt-triggered input                      |

| DO   | digital output                                       |

| DS   | digital supply                                       |

| IIC  | input and open-drain output for I <sup>2</sup> C-bus |

# 8. Functional description

# 8.1 System clock

The UDA1384 operates in slave mode only; this means that in all applications the system must provide either the system clock (the bit clock for the voice ADC) or the word clock.

The audio ADC part, the voice ADC part and the DAC part can operate at different sampling frequencies (DAC-WS and ADC-WS modes) as well as a common frequency (SYSCLK, WSDA and DSD modes).

The voice ADC part supports a sampling frequency up to 50 kHz and the audio ADC supports a sampling frequency up to 100 kHz. The DAC sampling frequency range is extended up to 200 kHz with the range above 100 kHz being supported through 192 kHz sampling mode, which halves the oversampling ratio of SYSCLK and internal clocks.

The mode of operation of the audio and voice channels can be set via the L3-bus or  $I^2C$ -bus microcontroller interface and are summarized in <u>Table 5</u> and <u>Table 6</u>.

When applied, the system clock must be locked in frequency to the corresponding digital interface clocks.

The voice ADC part can either receive or generate the WSV signal as shown in Table 6.

Table 5: Audio ADC and DAC operating clock mode

| Mode   | Audio ADC |                                                                                | Audio DAC |                                                                                                           |  |

|--------|-----------|--------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------|--|

|        | Clock     | Frequency                                                                      | Clock     | Frequency                                                                                                 |  |

| SYSCLK | SYSCLK    | 256f <sub>s</sub> , 384f <sub>s</sub> , 512f <sub>s</sub> or 768f <sub>s</sub> | SYSCLK    | 256f <sub>s</sub> , 384f <sub>s</sub> , 512f <sub>s</sub> or 768f <sub>s</sub>                            |  |

|        |           |                                                                                | SYSCLK    | 128f <sub>s</sub> , 192f <sub>s</sub> , 256f <sub>s</sub> or 384f <sub>s</sub> ;<br>192 kHz sampling mode |  |

| DAC-WS | SYSCLK    | $256f_s$ , $384f_s$ , $512f_s$ or $768f_s$                                     | WSDA      | 1f <sub>s</sub>                                                                                           |  |

| ADC-WS | WSAD      | 1f <sub>s</sub>                                                                | SYSCLK    | 256f <sub>s</sub> , 384f <sub>s</sub> , 512f <sub>s</sub> or 768f <sub>s</sub>                            |  |

|        |           |                                                                                | SYSCLK    | 128f <sub>s</sub> , 192f <sub>s</sub> , 256f <sub>s</sub> or 384f <sub>s</sub> ;<br>192 kHz sampling mode |  |

| WSDA   | WSDA      | 1f <sub>s</sub>                                                                | WSDA      | 1f <sub>s</sub>                                                                                           |  |

| DSD    | SYSCLK    | 44.1 kHz × 512                                                                 | SYSCLK    | 44.1 kHz × 512                                                                                            |  |

Table 6: Voice ADC operating clock mode

| Mode    | Voice ADC                                                                           |                   |  |  |

|---------|-------------------------------------------------------------------------------------|-------------------|--|--|

|         | Bit clock frequency (BCKV)                                                          | Word select (WSV) |  |  |

| WSV-in  | input: 32f <sub>s</sub> , 64f <sub>s</sub> , 128f <sub>s</sub> or 256f <sub>s</sub> | input             |  |  |

| WSV-out | input: $32f_s$ , $64f_s$ , $128f_s$ or $256f_s$                                     | output            |  |  |

9397 750 14366

Multichannel audio coder-decoder

# 8.2 Audio analog-to-digital converter (audio ADC)

The audio analog-to-digital front-end of the UDA1384 consists of 4-channel single-ended ADCs with programmable gain stage (from 0 dB to 24 dB with 3 dB steps), controlled via the microcontroller interface. Using the PGA feature, it is possible to accept an input signal of 900 mV (RMS) or 1.8 V (RMS) if an external resistor of 10 k $\Omega$  is used in series. The schematic of audio ADC front-end is shown in Figure 3.

# 8.3 Voice Analog-to-Digital Converter (voice ADC)

The voice analog-to-digital front-end of the UDA1384 consists of a single-channel single-ended ADC with a fixed gain (26 dB) Low Noise Amplifier (LNA). Together with the digital variable gain amplification stage, the voice ADC provides optimal processing and reproduction of the microphone signal. The supported sampling frequency range is from 7 kHz to 50 kHz. Power-down of the LNA and the ADC can be controlled separately.

#### 8.4 Decimation filter of audio ADC

The decimation from  $64f_s$  is performed in two stages. The first stage realizes  $\left(\frac{\sin x}{x}\right)^4$

characteristics with a decimation factor of 8. The second stage consists of three half-band filters, each decimating by a factor of 2. The filter characteristics are shown in Table 7.

| Table 7: | Decimation filter | characteristics | (audio ADC) |

|----------|-------------------|-----------------|-------------|

|----------|-------------------|-----------------|-------------|

| Item             | Condition                             | Value (dB)      |

|------------------|---------------------------------------|-----------------|

| Pass-band ripple | Of <sub>s</sub> to 0.45f <sub>s</sub> | ±0.01           |

| Pass-band droop  | 0.45f <sub>s</sub>                    | -0.2            |

| Stop band        | > 0.55f <sub>s</sub>                  | <del>-7</del> 0 |

| Dynamic range    | 0f <sub>s</sub> to 0.45f <sub>s</sub> | > 135           |

#### 8.5 Decimation filter of voice ADC

The voice ADC decimation filter is realized with the combination of a Finite Impulse Response (FIR) filter and Infinite Impulse Response (IIR) filter for shorter group delay. The filter characteristics are shown in <u>Table 8</u>. During the power-on sequence, the output of the ADC is hard muted for a certain period. This hard-mute time can be chosen between 1024 samples and 2048 samples.

Multichannel audio coder-decoder

| Item             | Condition                             | Value (dB) |

|------------------|---------------------------------------|------------|

| Pass-band ripple | Of <sub>s</sub> to 0.45f <sub>s</sub> | ±0.05      |

| Pass-band droop  | 0.45f <sub>s</sub>                    | -0.2       |

| Stop band        | > 0.55f <sub>s</sub>                  | <b>-65</b> |

| Dynamic range    | 0f <sub>s</sub> to 0.45f <sub>s</sub> | > 110      |

# 8.6 Interpolation filter of DAC

The digital interpolation filter interpolates from  $1f_s$  to  $128f_s$  (or to  $64f_s$  in the 192 kHz sampling mode) by cascading FIR filters, and has two sets of filter coefficients for sharp and slow roll-off as given in <u>Table 9</u> and <u>Table 10</u>.

Table 9: Interpolation filter characteristics (sharp roll-off)

| Item             | Condition                             | Value (dB)     |

|------------------|---------------------------------------|----------------|

| Pass-band ripple | 0f <sub>s</sub> to 0.45f <sub>s</sub> | ±0.002         |

| Stop band        | > 0.55f <sub>s</sub>                  | <del>-75</del> |

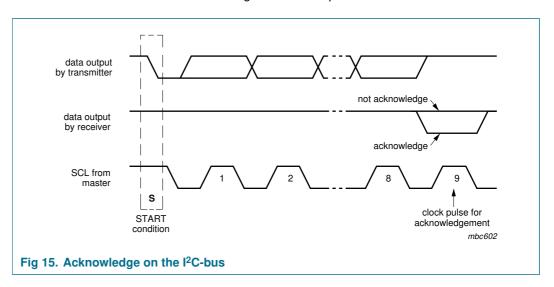

| Dynamic range    | $0f_s$ to $0.45f_s$                   | > 135          |