Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **UPSD3254A, UPSD3254BV UPSD3253B, UPSD3253BV**

Flash programmable system devices with 8032 MCU and 256 Kbit SRAM

#### **Features**

- Fast 8-bit 8032 MCU

- 40 MHz at 5.0 V, 24 MHz at 3.3 V

- Core, 12-clocks per instruction

- Dual Flash memories with memory management

- Place either memory into 8032 program address space or data address space

- Read-while-write operation for inapplication programming and EEPROM emulation

- Single voltage program and erase

- 100,000 minimum erase cycles, 15-year retention

- Clock, reset, and supply management

- Normal, idle, and power down modes

- Power-on and low voltage reset supervisor

- Programmable watchdog timer

- Programmable logic, general-purpose

- 16 macrocells

- Implements state machines, glue-logic, etc.

- Timers and interrupts

- Three 8032 standard 16-bit timers

- 10 Interrupt sources with two external interrupt pins

LQFP80 (U) 80-lead, thin, quad flat package

- A/D converter

- Four channels, 8-bit resolution, 10 µs

- Communication interfaces

- USB v1.1, low-speed 1.5 Mbps, 3 endpoints

- I<sup>2</sup>C master/slave bus controller

- Two UARTs with independent baud rate

- Six I/O ports with up to 46 I/O pins

- 8032 address/data bus available on TQFP80 package

- 5 PWM outputs, 8-bit resolution

- JTAG in-system programming

- Program the entire device in as little as 10 seconds

- Single supply voltage

- 4.5 to 5.5 V

- 3.0 to 3.6 V

- ECOPACK® packages

Table 1. Device summary

| Order code      | Max. clock<br>(MHz) | 1st<br>Flash | 2nd<br>Flash | SRAM  | GPIO | USB | 8032<br>bus | V <sub>CC</sub> (V) | Pkg.   | Temp.         |

|-----------------|---------------------|--------------|--------------|-------|------|-----|-------------|---------------------|--------|---------------|

| UPSD3253B-40T6  | 40                  | 128 KB       | 32 KB        | 32 KB | 37   | No  | No          | 4.5-5.5             | TQFP52 | –40°C to 85°C |

| UPSD3253BV-24T6 | 24                  | 128 KB       | 32 KB        | 32 KB | 37   | No  | No          | 3.0-3.6             | TQFP52 | –40°C to 85°C |

| UPSD3254BV-24U6 | 24                  | 256 KB       | 32 KB        | 32 KB | 46   | No  | Yes         | 3.0-3.6             | TQFP80 | –40°C to 85°C |

| UPSD3254A-40T6  | 40                  | 256 KB       | 32 KB        | 32 KB | 37   | Yes | No          | 4.5-5.5             | TQFP52 | –40°C to 85°C |

| UPSD3254A-40U6  | 40                  | 256 KB       | 32 KB        | 32 KB | 46   | Yes | Yes         | 4.5-5.5             | TQFP80 | –40°C to 85°C |

# **Contents**

| 1 | UPSD  | )325xx (    | description                    | . 9  |  |  |  |  |

|---|-------|-------------|--------------------------------|------|--|--|--|--|

|   | 1.1   | 52-pin p    | package I/O port               | 15   |  |  |  |  |

| 2 | Archi | tecture     | overview                       | 16   |  |  |  |  |

|   | 2.1   | Memory      | organization                   | 16   |  |  |  |  |

|   | 2.2   | Registe     | rs                             | 16   |  |  |  |  |

|   |       | 2.2.1       | Accumulator                    | . 17 |  |  |  |  |

|   |       | 2.2.2       | B register                     | . 17 |  |  |  |  |

|   |       | 2.2.3       | Stack pointer                  | . 17 |  |  |  |  |

|   |       | 2.2.4       | Program counter                | . 18 |  |  |  |  |

|   |       | 2.2.5       | Program status word            | . 18 |  |  |  |  |

|   |       | 2.2.6       | Registers R0~R7                | . 18 |  |  |  |  |

|   |       | 2.2.7       | Data pointer register          | . 18 |  |  |  |  |

|   | 2.3   | Progran     | n memory                       | 19   |  |  |  |  |

|   | 2.4   | Data memory |                                |      |  |  |  |  |

|   | 2.5   | RAM .       |                                | 19   |  |  |  |  |

|   | 2.6   | XRAM-       | DDC                            | 20   |  |  |  |  |

|   | 2.7   | XRAM-       | PSD                            | 20   |  |  |  |  |

|   | 2.8   | SFR .       |                                | 20   |  |  |  |  |

|   | 2.9   | Address     | sing modes                     | 21   |  |  |  |  |

|   |       | 2.9.1       | Direct addressing              | . 21 |  |  |  |  |

|   |       | 2.9.2       | Indirect addressing            | . 22 |  |  |  |  |

|   |       | 2.9.3       | Register addressing            | . 22 |  |  |  |  |

|   |       | 2.9.4       | Register-specific addressing   | . 22 |  |  |  |  |

|   |       | 2.9.5       | Immediate constants addressing | . 22 |  |  |  |  |

|   |       | 2.9.6       | Indexed addressing             | . 22 |  |  |  |  |

|   | 2.10  | Arithme     | tic instructions               | 23   |  |  |  |  |

|   | 2.11  | Logical     | instructions                   | 24   |  |  |  |  |

|   | 2.12  | Data tra    | nsfers                         | 25   |  |  |  |  |

|   |       | 2.12.1      | Internal RAM                   | . 25 |  |  |  |  |

|   |       | 2.12.2      | External RAM                   | . 28 |  |  |  |  |

|   |       | 2.12.3      | Lookup tables                  | . 28 |  |  |  |  |

|   | 2.13  | Boolear     | n instructions                 | 29   |  |  |  |  |

|   | 2.14  | Relative offset              |

|---|-------|------------------------------|

|   | 2.15  | Jump instructions            |

|   | 2.16  | Machine cycles               |

| 3 | UPSI  | D325xx hardware description  |

| 4 | MCU   | module description           |

|   | 4.1   | Special function registers   |

| 5 | Inter | rupt system                  |

|   | 5.1   | External Int0 interrupt      |

|   | 5.2   | Timer 0 and 1 interrupts     |

|   | 5.3   | Timer 2 interrupt            |

|   | 5.4   | I <sup>2</sup> C interrupt   |

|   | 5.5   | External Int1 interrupt      |

|   | 5.6   | DDC interrupt                |

|   | 5.7   | USB interrupt                |

|   | 5.8   | USART interrupt              |

|   | 5.9   | Interrupt priority structure |

|   | 5.10  | Interrupt enable structure   |

|   | 5.11  | How interrupts are handled   |

| 6 | Powe  | er-saving mode               |

|   | 6.1   | Idle mode                    |

|   | 6.2   | Power-down mode              |

|   | 6.3   | Power control register       |

|   | 6.4   | Idle mode                    |

|   | 6.5   | Power-down mode              |

| 7 | I/O p | orts (MCU module)51          |

|   | 7.1   | Port type and description 52 |

| 8 | Osci  | llator 54                    |

| 9 | Supe  | ervisory 55                  |

|     | 9.1                 | External reset                                      | 55   |

|-----|---------------------|-----------------------------------------------------|------|

|     | 9.2                 | Low V <sub>DD</sub> voltage reset                   | 55   |

|     | 9.3                 | Watchdog timer overflow                             | 56   |

|     | 9.4                 | USB reset                                           | 56   |

| 10  | Watc                | hdog timer                                          | 57   |

| 11  | Time                | r/counters (Timer 0, Timer 1 and Timer 2)           | 59   |

|     | 11.1                | Timer 0 and Timer 1                                 | 59   |

|     |                     | 11.1.1 Mode 0                                       | . 60 |

|     |                     | 11.1.2 Mode 1                                       | . 60 |

|     |                     | 11.1.3 Mode 2                                       | . 61 |

|     |                     | 11.1.4 Mode 3                                       | . 62 |

|     | 11.2                | Timer 2                                             | 62   |

| 12  | Stand               | dard serial interface (UART)                        | 66   |

|     | 12.1                | Multiprocessor communications                       | 66   |

|     | 12.2                | Serial port control register                        | 67   |

|     |                     | 12.2.1 Baud rates                                   | . 68 |

|     |                     | 12.2.2 Using Timer 1 to generate baud rates         | . 68 |

|     |                     | 12.2.3 Using Timer/counter 2 to generate baud rates | . 68 |

|     |                     | 12.2.4 More about Mode 0                            | . 69 |

|     |                     | 12.2.5 More about Mode 1                            | . 70 |

|     |                     | 12.2.6 More about Modes 2 and 3                     | . 71 |

| 13  | Analo               | og-to-digital convertor (ADC)                       | 77   |

|     | 13.1                | ADC interrupt                                       | 77   |

| 14  | Pulse               | e width modulation (PWM)                            | 80   |

|     | 14.1                | 4-channel PWM unit (PWM 0-3)                        | 80   |

|     | 14.2                | Programmable period 8-bit PWM                       | 82   |

|     | 14.3                | PWM 4-channel operation                             |      |

| 15  | I <sup>2</sup> C ir | nterface                                            | 84   |

| - • | 15.1                | Serial status register (SxSTA: S1STA, S2STA)        |      |

|     |                     | ,                                                   |      |

|     | 15.2                | Data shift register (SxDAT: S1DAT, S2DAT)           | βþ   |

|    | 15.3         | Address register (SxADR: S1ADR, S2ADR)                          |  |  |  |  |  |  |  |  |

|----|--------------|-----------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 16 | DDC          | interface                                                       |  |  |  |  |  |  |  |  |

|    | 16.1         | Special Function register for the DDC interface                 |  |  |  |  |  |  |  |  |

|    |              | 16.1.1 DDCDAT register                                          |  |  |  |  |  |  |  |  |

|    |              | 16.1.2 DDCADR register                                          |  |  |  |  |  |  |  |  |

|    | 16.2         | Host type detection                                             |  |  |  |  |  |  |  |  |

|    | 16.3         | DDC1 protocol                                                   |  |  |  |  |  |  |  |  |

|    | 16.4         | DDC2B protocol                                                  |  |  |  |  |  |  |  |  |

| 17 | USB hardware |                                                                 |  |  |  |  |  |  |  |  |

|    | 17.1         | 17.1 USB related registers                                      |  |  |  |  |  |  |  |  |

|    | 17.2         | Transceiver                                                     |  |  |  |  |  |  |  |  |

|    |              | 17.2.1 USB physical layer characteristics                       |  |  |  |  |  |  |  |  |

|    |              | 17.2.2 Low speed driver characteristics                         |  |  |  |  |  |  |  |  |

|    | 17.3         | Receiver characteristics                                        |  |  |  |  |  |  |  |  |

|    | 17.4         | External USB pull-up resistor                                   |  |  |  |  |  |  |  |  |

| 18 | PSD module   |                                                                 |  |  |  |  |  |  |  |  |

|    | 18.1         | Functional overview                                             |  |  |  |  |  |  |  |  |

|    | 18.2         | In-system programming (ISP)                                     |  |  |  |  |  |  |  |  |

| 19 | Deve         | lopment system109                                               |  |  |  |  |  |  |  |  |

| 20 | PSD          | module register description and address offset 110              |  |  |  |  |  |  |  |  |

| 21 | PSD          | module detailed operation                                       |  |  |  |  |  |  |  |  |

| 22 | Mem          | ory blocks112                                                   |  |  |  |  |  |  |  |  |

|    | 22.1         | Primary Flash memory and secondary Flash memory description 112 |  |  |  |  |  |  |  |  |

|    | 22.2         | Memory block select signals                                     |  |  |  |  |  |  |  |  |

|    |              | 22.2.1 Ready/Busy (PC3)                                         |  |  |  |  |  |  |  |  |

|    |              | 22.2.2 Memory operation                                         |  |  |  |  |  |  |  |  |

|    | 22.3         | Instructions                                                    |  |  |  |  |  |  |  |  |

|    | 22.4         | Power-down instruction and Power-up mode                        |  |  |  |  |  |  |  |  |

|    |              | 22.4.1 Power-up mode                                            |  |  |  |  |  |  |  |  |

|    | 22.5  | Read     |                                                        | . 115 |

|----|-------|----------|--------------------------------------------------------|-------|

|    |       | 22.5.1   | Read memory contents                                   | 115   |

|    |       | 22.5.2   | Read memory sector protection status                   | 115   |

|    |       | 22.5.3   | Reading the Erase/Program status bits                  | 115   |

|    |       | 22.5.4   | Data polling flag (DQ7)                                | 116   |

|    |       | 22.5.5   | Toggle flag (DQ6)                                      | 116   |

|    |       | 22.5.6   | Error flag (DQ5)                                       | 116   |

|    |       | 22.5.7   | Erase time-out flag (DQ3)                              | 117   |

|    | 22.6  | Progran  | nming Flash memory                                     | . 117 |

|    |       | 22.6.1   | Data Polling                                           | 117   |

|    |       | 22.6.2   | Data toggle                                            | 118   |

|    |       | 22.6.3   | Unlock Bypass                                          | 119   |

|    | 22.7  | Erasing  | Flash memory                                           | . 120 |

|    |       | 22.7.1   | Flash Bulk Erase                                       | 120   |

|    |       | 22.7.2   | Flash Sector Erase                                     | 120   |

|    |       | 22.7.3   | Suspend Sector Erase                                   | 120   |

|    |       | 22.7.4   | Resume Sector Erase                                    | 121   |

|    | 22.8  | Specific | features                                               | . 121 |

|    |       | 22.8.1   | Flash memory sector protect                            | 121   |

|    |       | 22.8.2   | Reset Flash                                            | 122   |

|    |       | 22.8.3   | Reset (RESET) signal                                   | 122   |

|    | 22.9  | SRAM .   |                                                        | . 122 |

|    | 22.10 | Sector S | Select and SRAM Select                                 | . 123 |

|    |       | 22.10.1  | Example                                                | 123   |

|    |       | 22.10.2  | Memory Select configuration in Program and Data spaces | 123   |

|    |       | 22.10.3  | Separate Space mode                                    | 124   |

|    |       | 22.10.4  | Combined Space modes                                   | 124   |

|    | 22.11 | Page re  | gister                                                 | . 125 |

| 23 | PLDs  |          |                                                        | . 127 |

|    | 23.1  | Turbo bi | t in PSD module                                        | . 127 |

|    | 23.2  | Decode   | PLD (DPLD)                                             | . 128 |

|    | 23.3  |          | x PLD (CPLD)                                           |       |

|    | 23.4  | •        | macrocell (OMC)                                        |       |

|    | 23.5  | -        | term allocator                                         |       |

|    | ۵.5   | 23.5.1   | Loading and Reading the Output Macrocells (OMC)        |       |

|    |       | ۷۵.۵.۱   | Loading and heading the Output Macrocells (OMO)        | 132   |

|    |       |          |                                                        |       |

| 23.6  I/O po 24.1 24.2 24.3 24.4 24.5 24.6 24.7 24.8           | Genera<br>Port ope<br>MCU I/O<br>PLD I/O<br>Address<br>Periphe            | OMC mask register  Output enable of the OMC  nacrocells (IMC)  If port architecture  erating modes  O mode  O mode  Solution of the OMC  O mode  O mode  O mode             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O po<br>24.1<br>24.2<br>24.3<br>24.4<br>24.5<br>24.6<br>24.7 | Input morts (PS) Genera Port ope MCU I/O PLD I/O Address Periphe          | acrocells (IMC)  D module)  Il port architecture  erating modes  O mode  D mode  S Out mode                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| I/O po<br>24.1<br>24.2<br>24.3<br>24.4<br>24.5<br>24.6<br>24.7 | Genera<br>Port ope<br>MCU I/O<br>PLD I/O<br>Address<br>Periphe            | SD module) Il port architecture erating modes O mode D mode s Out mode                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24.1<br>24.2<br>24.3<br>24.4<br>24.5<br>24.6<br>24.7           | Genera<br>Port ope<br>MCU I/O<br>PLD I/O<br>Address<br>Periphe            | ort architecture  erating modes  O mode  mode  o mode  s Out mode                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24.2<br>24.3<br>24.4<br>24.5<br>24.6<br>24.7                   | Port open MCU I/O PLD I/O Address Periphe                                 | erating modes  O mode  mode  o mode  o mode                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24.3<br>24.4<br>24.5<br>24.6<br>24.7                           | MCU I/O<br>PLD I/O<br>Address<br>Periphe                                  | O mode                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul><li>24.4</li><li>24.5</li><li>24.6</li><li>24.7</li></ul>  | PLD I/C<br>Address<br>Periphe                                             | O mode                                                                                                                                                                      | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul><li>24.5</li><li>24.6</li><li>24.7</li></ul>               | Address<br>Periphe                                                        | s Out mode                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24.6<br>24.7                                                   | Periphe                                                                   |                                                                                                                                                                             | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 24.7                                                           | -                                                                         | eral I/O mode                                                                                                                                                               | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                | IT∧⊜ i∽                                                                   |                                                                                                                                                                             | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 24.8                                                           | J IAG III                                                                 | n-system programming (ISP)                                                                                                                                                  | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                | Port cor                                                                  | nfiguration registers (PCR)                                                                                                                                                 | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                | 24.8.1                                                                    | Control register                                                                                                                                                            | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                | 24.8.2                                                                    | Direction register                                                                                                                                                          | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                | 24.8.3                                                                    | Drive Select register                                                                                                                                                       | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 24.9                                                           | Port dat                                                                  | ta registers                                                                                                                                                                | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                | 24.9.1                                                                    | Data In                                                                                                                                                                     | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                | 24.9.2                                                                    | Data Out register                                                                                                                                                           | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                | 24.9.3                                                                    | · · · · · · · · · · · · · · · · · · ·                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                | 24.9.4                                                                    | <u> </u>                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                | 24.9.5                                                                    | • • • • • • • • • • • • • • • • • • • •                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                |                                                                           |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                |                                                                           |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                |                                                                           |                                                                                                                                                                             | 141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                |                                                                           | •                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24.13                                                          | Externa                                                                   | al chip select                                                                                                                                                              | 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Power                                                          | r manag                                                                   | gement                                                                                                                                                                      | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 25.1                                                           | PLD po                                                                    | -<br>wer management                                                                                                                                                         | 147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 25.2                                                           | PSD ch                                                                    | nip select input (CSI, PD2)                                                                                                                                                 | 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 25.3                                                           |                                                                           |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 25.4                                                           |                                                                           |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                | T timin                                                                   |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                | 24.10<br>24.11<br>24.12<br>24.13<br>Power<br>25.1<br>25.2<br>25.3<br>25.4 | 24.8.2 24.8.3 24.9 Port da 24.9.1 24.9.2 24.9.3 24.9.4 24.9.5 24.9.6 24.10 Ports A 24.11 Port C 24.12 Port D 24.13 Externa Power mana 25.1 PLD po 25.2 PSD ch 25.3 Input cl | 24.8.2 Direction register 24.8.3 Drive Select register  24.9 Port data registers 24.9.1 Data In 24.9.2 Data Out register 24.9.3 Output macrocells (OMC) 24.9.4 OMC mask register 24.9.5 Input macrocells (IMC) 24.9.6 Enable out  24.10 Ports A and B – functionality and structure 24.11 Port C – functionality and structure 24.12 Port D – functionality and structure 24.13 External chip select  Power management  25.1 PLD power management 25.2 PSD chip select input (CSI, PD2) 25.3 Input clock |

|    | 26.1   | Warm F    | RESET                                         | 150 |

|----|--------|-----------|-----------------------------------------------|-----|

|    | 26.2   | I/O pin,  | register and PLD status at RESET              | 150 |

|    | 26.3   | Reset o   | of Flash Memory Erase and Program Cycles      | 150 |

| 27 | Prog   | rammin    | g in-circuit using the JTAG serial interface  | 152 |

|    | 27.1   | Standa    | rd JTAG Signals                               | 152 |

|    | 27.2   | JTAG e    | extensions                                    | 152 |

|    | 27.3   | Security  | y and Flash memory protection                 | 153 |

| 28 | Initia | l deliver | ry state                                      | 154 |

| 29 | AC/D   | C paran   | meters                                        | 155 |

| 30 | Maxi   | mum rat   | tings                                         | 158 |

| 31 | ЕМС    | charact   | teristics                                     | 159 |

|    | 31.1   | Functio   | nal EMS (electromagnetic susceptibility)      | 159 |

|    |        | 31.1.1    | ESD                                           | 159 |

|    |        | 31.1.2    | FTB                                           | 159 |

|    | 31.2   | Designi   | ing hardened software to avoid noise problems | 159 |

|    |        | 31.2.1    | Software recommendations                      | 159 |

|    |        | 31.2.2    | Prequalification trials                       | 159 |

|    | 31.3   | Absolut   | te maximum ratings (electrical sensitivity)   | 160 |

|    |        | 31.3.1    | Electro-static discharge (ESD)                | 160 |

|    |        | 31.3.2    | Latch-up                                      | 160 |

|    |        | 31.3.3    | Dynamic latch-up                              | 160 |

| 32 | DC a   | nd AC p   | parameters                                    | 161 |

| 33 | Pack   | age med   | chanical information                          | 185 |

| 34 | Part : | number    | ing                                           | 187 |

| 35 | Revis  | sion his  | tory                                          | 188 |

# 1 UPSD325xx description

The UPSD325xx Series combines a fast 8051-based microcontroller with a flexible memory structure, programmable logic, and a rich peripheral mix including USB, to form an ideal embedded controller. At its core is an industry-standard 8032 MCU operating up to 40MHz.

A JTAG serial interface is used for In-System Programming (ISP) in as little as 10 seconds, perfect for manufacturing and lab development.

The USB 1.1 low-speed interface has one Control endpoint and two Interrupt endpoints suitable for HID class drivers.

The 8032 core is coupled to Programmable System Device (PSD) architecture to optimize the 8032 memory structure, offering two independent banks of Flash memory that can be placed at virtually any address within 8032 program or data address space, and easily paged beyond 64 Kbytes using on-chip programmable decode logic.

Dual Flash memory banks provide a robust solution for remote product updates in the field through In-Application Programming (IAP). Dual Flash banks also support EEPROM emulation, eliminating the need for external EEPROM chips.

General purpose programmable logic (PLD) is included to build an endless variety of glue-logic, saving external logic devices. The PLD is configured using the software development tool, PSDsoft Express, available from the web at **www.st.com/psm**, at no charge.

The UPSD325xx also includes supervisor functions such as a programmable watchdog timer and low-voltage reset.

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com.

ECOPACK® is an ST trademark.

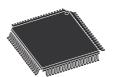

Figure 1. UPSD325xx block diagram

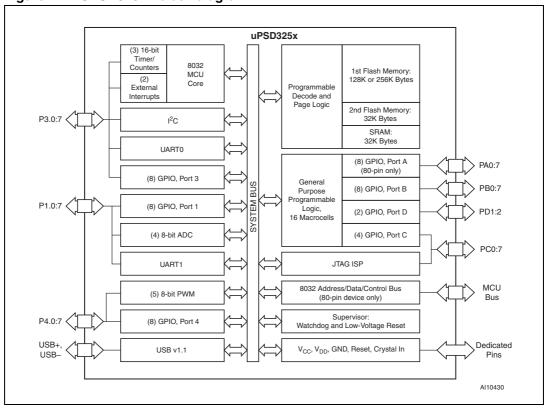

Figure 2. TQFP52 connections

1. Pull-up resistor required on pin 5 (2 k $\Omega$  for 3 V devices, 7.5 k $\Omega$  for 5 V devices) for all 52-pin devices, with or without USB function.

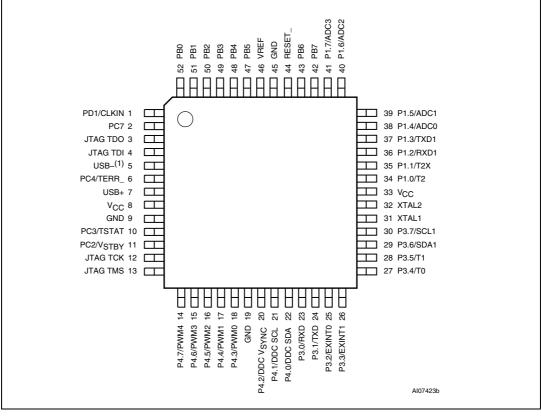

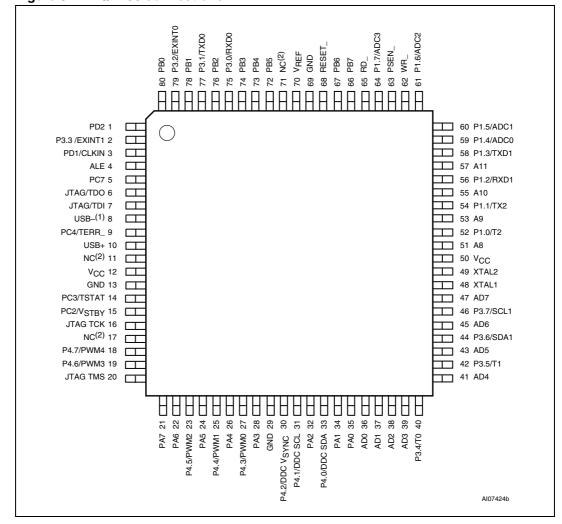

Figure 3. TQFP80 connections

- 1. Pull-up resistor required on pin 8 (2 k $\Omega$  for 3 V devices, 7.5 k $\Omega$  for 5 V devices) for all 82-pin devices, with or without USB function.

- 2. NC = Not Connected

Table 2. 80-pin package pin description

| Port | Signal | Pin | ln/ | Function                                            |           |

|------|--------|-----|-----|-----------------------------------------------------|-----------|

| pin  | name   | no. | out | Basic                                               | Alternate |

|      | AD0    | 36  | I/O | External Bus: Multiplexed<br>Address/Data bus A1/D1 |           |

|      | AD1    | 37  | I/O | Multiplexed Address/Data bus A0/D0                  |           |

|      | AD2    | 38  | I/O | Multiplexed Address/Data bus A2/D2                  |           |

|      | AD3    | 39  | I/O | Multiplexed Address/Data bus A3/D3                  |           |

|      | AD4    | 41  | I/O | Multiplexed Address/Data bus A4/D4                  |           |

|      | AD5    | 43  | I/O | Multiplexed Address/Data bus A5/D5                  |           |

|      | AD6    | 45  | I/O | Multiplexed Address/Data bus A6/D6                  |           |

Table 2. 80-pin package pin description (continued)

| Port | Signal                   | Pin | In/ | Function                           |                                          |  |  |

|------|--------------------------|-----|-----|------------------------------------|------------------------------------------|--|--|

| pin  | name                     | no. | out | Basic                              | Alternate                                |  |  |

|      | AD7                      | 47  | I/O | Multiplexed Address/Data bus A7/D7 |                                          |  |  |

| P1.0 | T2                       | 52  | I/O | General I/O port pin               | Timer 2 Count input                      |  |  |

| P1.1 | TX2                      | 54  | I/O | General I/O port pin               | Timer 2 Trigger input                    |  |  |

| P1.2 | RxD1                     | 56  | I/O | General I/O port pin               | 2nd UART Receive                         |  |  |

| P1.3 | TxD1                     | 58  | I/O | General I/O port pin               | 2nd UART Transmit                        |  |  |

| P1.4 | ADC0                     | 59  | I/O | General I/O port pin               | ADC Channel 0 input                      |  |  |

| P1.5 | ADC1                     | 60  | I/O | General I/O port pin               | ADC Channel 1 input                      |  |  |

| P1.6 | ADC2                     | 61  | I/O | General I/O port pin               | ADC Channel 2 input                      |  |  |

| P1.7 | ADC3                     | 64  | I/O | General I/O port pin               | ADC Channel 3 input                      |  |  |

|      | A8                       | 51  | 0   | External Bus, Address A8           |                                          |  |  |

|      | A9                       | 53  | 0   | External Bus, Address A9           |                                          |  |  |

|      | A10                      | 55  | 0   | External Bus, Address A10          |                                          |  |  |

|      | A11                      | 57  | 0   | External Bus, Address A11          |                                          |  |  |

| P3.0 | RxD0                     | 75  | I/O | General I/O port pin               | UART Receive                             |  |  |

| P3.1 | TxD0                     | 77  | I/O | General I/O port pin               | UART Transmit                            |  |  |

| P3.2 | EXINT0                   | 79  | I/O | General I/O port pin               | Interrupt 0 input / Timer 0 gate control |  |  |

| P3.3 | EXINT1                   | 2   | I/O | General I/O port pin               | Interrupt 1 input / Timer 1 gate control |  |  |

| P3.4 | T0                       | 40  | I/O | General I/O port pin               | Counter 0 input                          |  |  |

| P3.5 | T1                       | 42  | I/O | General I/O port pin               | Counter 1 input                          |  |  |

| P3.6 | SDA1                     | 44  | I/O | General I/O port pin               | I <sup>2</sup> C Bus serial data I/O     |  |  |

| P3.7 | SCL1                     | 46  | I/O | General I/O port pin               | I <sup>2</sup> C Bus clock I/O           |  |  |

| P4.0 | DDC<br>SDA               | 33  | I/O | General I/O port pin               |                                          |  |  |

| P4.1 | DDC<br>SCL               | 31  | I/O | General I/O port pin               |                                          |  |  |

| P4.2 | DDC<br>V <sub>SYNC</sub> | 30  | I/O | General I/O port pin               |                                          |  |  |

| P4.3 | PWM0                     | 27  | I/O | General I/O port pin               | 8-bit Pulse Width<br>Modulation output 0 |  |  |

| P4.4 | PWM1                     | 25  | I/O | General I/O port pin               | 8-bit Pulse Width<br>Modulation output 1 |  |  |

| P4.5 | PWM2                     | 23  | I/O | General I/O port pin               | 8-bit Pulse Width<br>Modulation output 2 |  |  |

| P4.6 | PWM3                     | 19  | I/O | General I/O port pin               | 8-bit Pulse Width<br>Modulation output 3 |  |  |

**577**

Table 2. 80-pin package pin description (continued)

| Port Signal Pin In/ |                  |     | ln/ | Function                                                                                 |                                                       |  |  |  |

|---------------------|------------------|-----|-----|------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| pin                 | name             | no. | out | Basic                                                                                    | Alternate                                             |  |  |  |

| P4.7                | PWM4             | 18  | I/O | General I/O port pin                                                                     | Programmable 8-bit Pulse<br>Width modulation output 4 |  |  |  |

|                     | USB-             | 8   | I/O | Pull-up resistor required (2 k $\Omega$ for 3 V devices, 7.5 k $\Omega$ for 5 V devices) |                                                       |  |  |  |

|                     | V <sub>REF</sub> | 70  | 0   | Reference Voltage input for ADC                                                          |                                                       |  |  |  |

|                     | RD_              | 65  | 0   | READ signal, external bus                                                                |                                                       |  |  |  |

|                     | WR_              | 62  | 0   | WRITE signal, external bus                                                               |                                                       |  |  |  |

|                     | PSEN_            | 63  | 0   | PSEN signal, external bus                                                                |                                                       |  |  |  |

|                     | ALE              | 4   | 0   | Address Latch signal, external bus                                                       |                                                       |  |  |  |

|                     | RESET_           | 68  | I   | Active low RESET input                                                                   |                                                       |  |  |  |

|                     | XTAL1            | 48  | I   | Oscillator input pin for system clock                                                    |                                                       |  |  |  |

|                     | XTAL2            | 49  | 0   | Oscillator output pin for system clock                                                   |                                                       |  |  |  |

| PA0                 |                  | 35  | I/O | General I/O port pin                                                                     |                                                       |  |  |  |

| PA1                 |                  | 34  | I/O | General I/O port pin                                                                     |                                                       |  |  |  |

| PA2                 |                  | 32  | I/O | General I/O port pin                                                                     | PLD macrocell outputs                                 |  |  |  |

| PA3                 |                  | 28  | I/O | General I/O port pin                                                                     | PLD inputs                                            |  |  |  |

| PA4                 |                  | 26  | I/O | General I/O port pin                                                                     | Latched address out (A0-A7)                           |  |  |  |

| PA5                 |                  | 24  | I/O | General I/O port pin                                                                     | Peripheral I/O mode                                   |  |  |  |

| PA6                 |                  | 22  | I/O | General I/O port pin                                                                     |                                                       |  |  |  |

| PA7                 |                  | 21  | I/O | General I/O port pin                                                                     |                                                       |  |  |  |

| PB0                 |                  | 80  | I/O | General I/O port pin                                                                     |                                                       |  |  |  |

| PB1                 |                  | 78  | I/O | General I/O port pin                                                                     |                                                       |  |  |  |

| PB2                 |                  | 76  | I/O | General I/O port pin                                                                     | PLD macrocell outputs                                 |  |  |  |

| PB3                 |                  | 74  | I/O | General I/O port pin                                                                     | PLD inputs                                            |  |  |  |

| PB4                 |                  | 73  | I/O | General I/O port pin                                                                     | Latched address out (A0-                              |  |  |  |

| PB5                 |                  | 72  | I/O | General I/O port pin                                                                     | A7)                                                   |  |  |  |

| PB6                 |                  | 67  | I/O | General I/O port pin                                                                     |                                                       |  |  |  |

| PB7                 |                  | 66  | I/O | General I/O port pin                                                                     |                                                       |  |  |  |

**Function** Port Signal Pin In/ pin name no. out **Basic Alternate JTAG** 20 Ī JTAG pin **TMS JTAG** 16 ١ JTAG pin **TCK** PLD macrocell outputs PC3 **TSTAT** 14 I/O General I/O port pin PLD inputs PC4 TERR 9 I/O General I/O port pin JTAG pins are dedicated **JTAG** pins 7 JTAG pin Τ TDI **JTAG** 6 0 JTAG pin TDO PC7 5 I/O General I/O port pin PLD I/O PD1 **CLKIN** I/O 3 General I/O port pin Clock input to PLD and APD PLD I/O PD2 1 I/O General I/O port pin Chip select to PSD module Vcc 12 Vcc 50 **GND** 13 **GND** 29 **GND** 69 USB+ 10 NC 11 NC 17

Table 2. 80-pin package pin description (continued)

#### 52-pin package I/O port 1.1

NC

The 52-pin package members of the UPSD325xx devices have the same port pins as those of the 80-pin package except:

- Port 0 (P0.0-P0.7, external address/data bus AD0-AD7)

- Port 2 (P2.0-P2.3, external address bus A8-A11)

- Port A (PA0-PA7)

- Port D (PD2)

- Bus control signal (RD,WR,PSEN,ALE)

71

Pin 5 requires a pull-up resistor (2 k $\Omega$  for 3 V devices, 7.5 k $\Omega$  for 5 V devices) for all devices, with or without USB function.

#### 2 Architecture overview

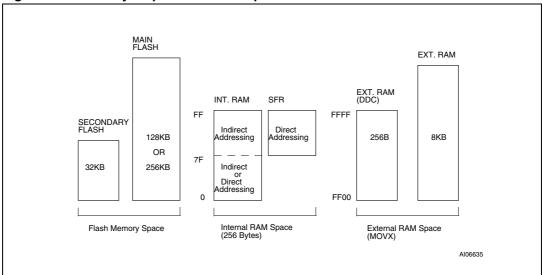

## 2.1 Memory organization

The UPSD325xx devices' standard 8032 Core has separate 64-Kbyte address spaces for Program memory and Data Memory. Program memory is where the 8032 executes instructions from. Data memory is used to hold data variables. Flash memory can be mapped in either program or data space. The Flash memory consists of two Flash memory blocks: the main Flash memory (1 or 2 Mbit) and the Secondary Flash memory (256 Kbit). Except during flash memory programming or update, Flash memory can only be read, not written to. A Page Register is used to access memory beyond the 64-Kbyte address space. Refer to the PSD module for details on mapping of the Flash memory.

The 8032 core has two types of data memory (internal and external) that can be read and written. The internal SRAM consists of 256 bytes, and includes the stack area.

The SFR (Special Function Registers) occupies the upper 128 bytes of the internal SRAM, the registers can be accessed by Direct addressing only. There are two separate blocks of external SRAM inside the UPSD325X devices: one 256-byte block is assigned for DDC data storage. Another 32 Kbytes resides in the PSD module that can be mapped to any address space defined by the user.

Figure 4. Memory map and address space

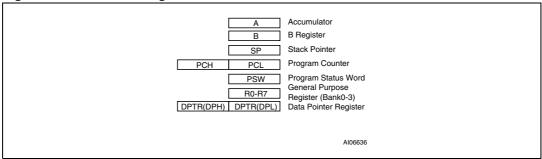

# 2.2 Registers

The 8032 has several registers; these are the Program Counter (PC), Accumulator (A), B Register (B), the Stack Pointer (SP), the Program Status Word (PSW), General purpose registers (R0 to R7), and DPTR (Data Pointer register).

Figure 5. 8032 MCU registers

#### 2.2.1 Accumulator

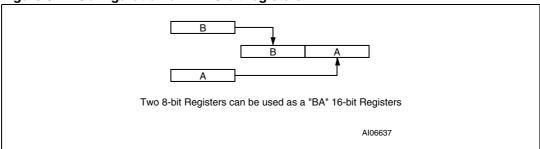

The Accumulator is the 8-bit general purpose register, used for data operation such as transfer, temporary saving, and conditional tests. The Accumulator can be used as a 16-bit register with B Register as shown below.

Figure 6. Configuration of BA 16-bit registers

## 2.2.2 B register

The B Register is the 8-bit general purpose register, used for an arithmetic operation such as multiply, division with Accumulator.

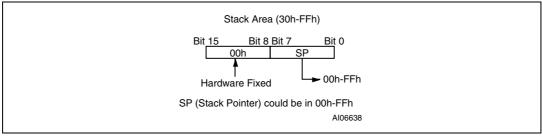

### 2.2.3 Stack pointer

The Stack Pointer Register is 8 bits wide. It is incremented before data is stored during PUSH and CALL executions. While the stack may reside anywhere in on-chip RAM, the Stack Pointer is initialized to 07h after reset. This causes the stack to begin at location 08h.

Figure 7. Stack pointer

577

#### 2.2.4 Program counter

The Program Counter is a 16-bit wide which consists of two 8-bit registers, PCH and PCL. This counter indicates the address of the next instruction to be executed. In RESET state, the program counter has reset routine address (PCH:00h, PCL:00h).

#### 2.2.5 Program status word

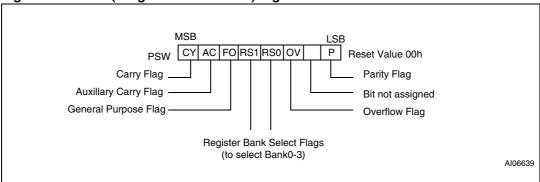

The Program Status Word (PSW) contains several bits that reflect the current state of the CPU and select Internal RAM (00h to 1Fh: Bank0 to Bank3). The PSW is described in *Figure 8*. It contains the Carry flag, the Auxiliary Carry flag, the Half Carry (for BCD operation), the General Purpose flag, the Register Bank Select flags, the Overflow flag, and Parity flag.

[Carry flag, CY]. This flag stores any carry or not borrow from the ALU of CPU after an arithmetic operation and is also changed by the Shift Instruction or Rotate Instruction.

[Auxiliary Carry flag, AC]. After operation, this flag is set when there is a carry from Bit 3 of ALU or there is no borrow from Bit 4 of ALU.

[Register Bank Select flags, RS0, RS1]. These flags select one of four banks (00~07H:bank0, 08~0Fh:bank1, 10~17h:bank2, 17~1Fh:bank3) in Internal RAM.

[Overflow flag, OV]. This flag is set to '1' when an overflow occurs as the result of an arithmetic operation involving signs. An overflow occurs when the result of an addition or subtraction exceeds +127 (7Fh) or -128 (80h). The CLRV instruction clears the overflow flag. There is no set instruction. When the BIT instruction is executed, Bit 6 of memory is copied to this flag.

[Parity flag, P]. This flag reflects the number of Accumulator's 1. If the number of Accumulator's 1 is odd, P=0; otherwise, P=1. The sum when adding Accumulator's 1 to P is always even.

#### 2.2.6 Registers R0~R7

General purpose 8-bit registers that are locked in the lower portion of internal data area.

#### 2.2.7 Data pointer register

Data Pointer Register is 16-bit wide which consists of two-8bit registers, DPH and DPL. This register is used as a data pointer for the data transmission with external data memory in the PSD module.

## 2.3 Program memory

The program memory consists of two Flash memories: the main Flash memory (1 or 2 Mbit) and the Secondary Flash memory (256 Kbit). The Flash memory can be mapped to any address space as defined by the user in the PSDsoft Tool. It can also be mapped to Data memory space during Flash memory update or programming.

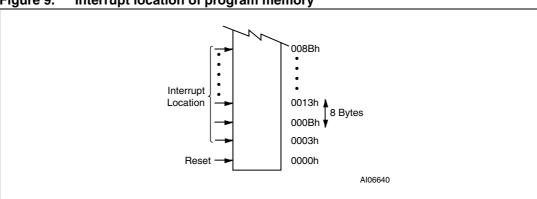

After reset, the CPU begins execution from location 0000h. As shown in *Figure 9*, each interrupt is assigned a fixed location in Program Memory. The interrupt causes the CPU to jump to that location, where it commences execution of the service routine. External Interrupt 0, for example, is assigned to location 0003h. If External Interrupt 0 is going to be used, its service routine must begin at location 0003h. If the interrupt is not going to be used, its service location is available as general purpose Program Memory.

The interrupt service locations are spaced at 8-byte intervals: 0003h for External Interrupt 0, 000Bh for Timer 0, 0013h for External Interrupt 1, 001Bh for Timer 1 and so forth. If an interrupt service routine is short enough (as is often the case in control applications), it can reside entirely within that 8-byte interval. Longer service routines can use a jump instruction to skip over subsequent interrupt locations, if other interrupts are in use.

## 2.4 Data memory

The internal data memory is divided into four physically separated blocks: 256 bytes of internal RAM, 128 bytes of Special Function Registers (SFRs) areas, 256 bytes of external RAM (XRAM-DDC) and 32 Kbytes (XRAM-PSD) in the PSD module.

#### 2.5 RAM

Four register banks, each 8 registers wide, occupy locations 0 through 31 in the lower RAM area. Only one of these banks may be enabled at a time. The next 16 bytes, locations 32 through 47, contain 128 directly addressable bit locations. The stack depth is only limited by the available internal RAM space of 256 bytes.

Figure 9. Interrupt location of program memory

#### 2.6 XRAM-DDC

The 256 bytes of XRAM-DDC used to support DDC interface is also available for system usage by indirect addressing through the address pointer DDCADR and data I/O buffer RAMBUF. The address pointer (DDCADR) is equipped with the post increment capability to facilitate the transfer of data in bulk (for details refer to DDC Interface part). However, it is also possible to address the RAM through MOVX command as normally used in the internal RAM extension of 80C51 derivatives. XRAM-DDC FF00 to FFFF is directly addressable as external data memory locations FF00 to FFFF via MOVX-DPTR instruction or via MOVX-Ri instruction. When XRAM-DDC is disabled, the address space FF00 to FFFF can be assigned to other resources.

### 2.7 XRAM-PSD

The 32 Kbytes of XRAM-PSD resides in the PSD module and can be mapped to any address space through the DPLD (Decoding PLD) as defined by the user in PSDsoft Development tool.

#### 2.8 SFR

The SFRs can only be addressed directly in the address range from 80h to FFh. *Table 15* gives an overview of the Special Function Registers. Sixteen address in the SFRs space are both-byte and bit-addressable. The bit-addressable SFRs are those whose address ends in 0h and 8h. The bit addresses in this area are 80h to FFh.

Table 3. RAM address

Byte address

| (in hexadecimal) (in de |     |    |    |           |           |    |    |     |          |

|-------------------------|-----|----|----|-----------|-----------|----|----|-----|----------|

| -<br>FFh                |     |    |    |           |           |    |    |     | -<br>255 |

| 30h                     |     |    |    |           |           |    |    |     | 48       |

| 30                      | MSB |    |    | Bit addre | ess (hex) |    |    | LSB |          |

| 2Fh                     | 7F  | 7E | 7D | 7C        | 7B        | 7A | 79 | 78  | 47       |

| 2Eh                     | 77  | 76 | 75 | 74        | 73        | 72 | 71 | 70  | 46       |

| 2Dh                     | 6F  | 6E | 6D | 6C        | 6B        | 6A | 69 | 68  | 45       |

| 2Ch                     | 67  | 66 | 65 | 64        | 63        | 62 | 61 | 60  | 44       |

| 2Bh                     | 5F  | 5E | 5D | 5C        | 5B        | 5A | 59 | 58  | 43       |

| 2Ah                     | 57  | 56 | 55 | 54        | 53        | 52 | 51 | 50  | 42       |

| 29h                     | 4F  | 4E | 4D | 4C        | 4B        | 4A | 49 | 48  | 41       |

| 28h                     | 47  | 46 | 45 | 44        | 43        | 42 | 41 | 40  | 40       |

| 27h                     | 3F  | 3E | 3D | 3C        | 3B        | 3A | 39 | 38  | 39       |

| 26h                     | 37  | 36 | 35 | 34        | 33        | 32 | 31 | 30  | 38       |

| 25h                     | 2F  | 2E | 2D | 2C        | 2B        | 2A | 29 | 28  | 37       |

| 24h                     | 27  | 26 | 25 | 24        | 23        | 22 | 21 | 20  | 36       |

| 23h                     | 1F  | 1E | 1D | 1C        | 1B        | 1A | 19 | 18  | 35       |

**577**

Byte address

0

Byte address Byte address (in hexadecimal) (in decimal) 22h 17 16 15 14 13 12 11 10 34 0F 0E 0D 0C 0B 0A 09 80 21h 33 20h 07 06 05 04 03 02 01 00 32 1Fh 31 Register bank 3 18h 24 17h 23 Register bank 2 10h 16 0Fh 15 Register bank 1 08h 8 7

Register bank 0

**RAM address (continued)** Table 3.

#### **Addressing modes** 2.9

07h

00h

The addressing modes in UPSD325xx devices instruction set are as follows

- 1. Direct addressing

- 2. Indirect addressing

- 3. Register addressing

- 4. Register-specific addressing

- 5. Immediate constants addressing

- 6. Indexed addressing

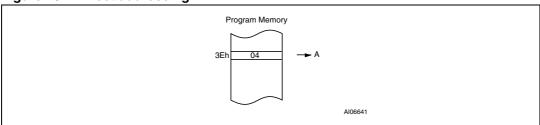

#### 2.9.1 **Direct addressing**

In a direct addressing the operand is specified by an 8-bit address field in the instruction. Only internal Data RAM and SFRs (80~FFH RAM) can be directly addressed.

Example:

mov A, 3EH; A <---- RAM[3E]

Figure 10. Direct addressing

#### 2.9.2 Indirect addressing

In indirect addressing the instruction specifies a register which contains the address of the operand. Both internal and external RAM can be indirectly addressed. The address register for 8-bit addresses can be R0 or R1 of the selected register bank, or the Stack Pointer. The address register for 16-bit addresses can only be the 16-bit "data pointer" register, DPTR.

#### Example:

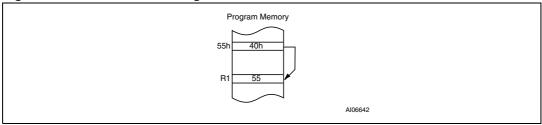

mov @R1, #40 H;[R1] <----40H

Figure 11. Indirect addressing

### 2.9.3 Register addressing

The register banks, containing registers R0 through R7, can be accessed by certain instructions which carry a 3-bit register specification within the opcode of the instruction. Instructions that access the registers this way are code efficient, since this mode eliminates an address byte. When the instruction is executed, one of four banks is selected at execution time by the two bank select bits in the PSW.

#### Example:

mov PSW, #0001000B; select Bank0 mov A, #30H mov R1, A

#### 2.9.4 Register-specific addressing

Some instructions are specific to a certain register. For example, some instructions always operate on the Accumulator, or Data Pointer, etc., so no address byte is needed to point it. The opcode itself does that.

#### 2.9.5 Immediate constants addressing

The value of a constant can follow the opcode in Program memory.

Example:

mov A, #10H.

## 2.9.6 Indexed addressing

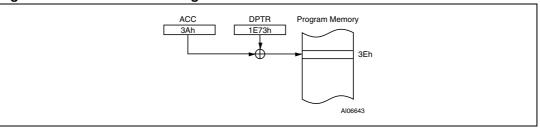

Only Program memory can be accessed with indexed addressing, and it can only be read. This addressing mode is intended for reading look-up tables in Program memory. A 16-bit base register (either DPTR or PC) points to the base of the table, and the Accumulator is set up with the table entry number. The address of the table entry in Program memory is formed by adding the Accumulator data to the base pointer.

Example:

movc A, @A+DPTR

Figure 12. Indexed addressing

#### 2.10 **Arithmetic instructions**

The arithmetic instructions is listed in *Table 4*. The table indicates the addressing modes that can be used with each instruction to access the <byte> operand. For example, the ADD A, <byte> instruction can be written as:

ADD a, 7FH (direct addressing)

ADD A, @R0 (indirect addressing)

ADD a, R7 (register addressing)

ADD A, #127 (immediate constant)

Note: Any byte in the internal Data Memory space can be incremented without going through the Accumulator.

> One of the INC instructions operates on the 16-bit Data Pointer. The Data Pointer is used to generate 16-bit addresses for external memory, so being able to increment it in one 16-bit operation is a useful feature.

> The MUL AB instruction multiplies the Accumulator by the data in the B register and puts the 16-bit product into the concatenated B and Accumulator registers.

> The DIV AB instruction divides the Accumulator by the data in the B register and leaves the 8-bit quotient in the Accumulator, and the 8-bit remainder in the B register.

> In shift operations, dividing a number by 2n shifts its "n" bits to the right. Using DIV AB to perform the division completes the shift in 4?s and leaves the B register holding the bits that were shifted out. The DAA instruction is for BCD arithmetic operations. In BCD arithmetic, ADD and ADDC instructions should always be followed by a DAA operation, to ensure that the result is also in BCD.

DAA will not convert a binary number to BCD. The DAA operation produces a meaningful result only as the second step in the addition of two BCD bytes.

**Arithmetic instructions** Table 4.

| Mnemonic              | Operation                          | Addressing modes |      |      |      |

|-----------------------|------------------------------------|------------------|------|------|------|

|                       |                                    | Dir.             | Ind. | Reg. | lmm. |

| ADD A, <byte></byte>  | A = A + <byte></byte>              | Х                | Х    | X    | X    |

| ADDC A, <byte></byte> | A = A + <byte> + C</byte>          | Х                | Х    | Х    | Х    |

| SUBB A, <byte></byte> | $A = A - \langle byte \rangle - C$ | Х                | Х    | Х    | Х    |

Note: