# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Ultra Fast USB 2.0 Multi-Slot Flash Media Controller

## **General Description**

The Microchip USB2250/50i/51/51i is a USB 2.0 compliant, Hi-Speed mass storage class peripheral controller intended for reading and writing to more than 24 popular flash media formats from the CompactFlash<sup>®</sup> (CF), SmartMedia<sup>TM</sup> (SM), xD-Picture Card<sup>TM</sup> (xD)<sup>1</sup>, Memory Stick<sup>®</sup> (MS), Secure Digital (SD), and MultiMediaCard<sup>TM</sup> (MMC) families.

The USB2250/50i/51/51i is a fully integrated, single chip solution capable of ultra high performance operation. Average sustained transfer rates exceeding 35 MB/s are possible if the media and host can support those rates.

## **Highlights**

- 128-pin VTQFP (14x14 mm) RoHS compliant package

- Targeted for applications in which single or "combo" media sockets are used

- Supports multiple simultaneous card insertions

- Flexible assignment of number of LUNs and how card types are associated with the LUNs

- Hardware-controlled data flow architecture for all self-mapped media

- Pipelined hardware support for access to nonself-mapped media

- Order number with "i" denotes the version that supports the industrial temperature range of -40°C to 85°C

## **Hardware Features**

- Single chip flash media controller with non-multiplexed interface for independent card sockets

- Flash Media Specification Revision Compliance

- CompactFlash 4.1

- Secure Digital 2.0

- MultiMediaCard 4.2

- MMC Streaming Mode support

- Memory Stick 1.43

- Memory Stick Pro Format 1.02

- Memory Stick Duo Format 1.10

- Memory Stick Pro-HG Duo Format 1.01

- xD-Picture Card 1.2

- SmartMedia 1.3

- Extended configuration options

xD player mode operation

- Socket switch polarities, etc.

- Media Activity LED

- On board 24 MHz crystal driver circuit

- Optional external 24 MHz clock input

4 Independent internal card power FETs

- 200 mA each

- "Fold-back" short circuit protection

- 8051 8-bit microprocessor

- 60 MHz single cycle execution

- 64 KB ROM | 14 KB RAM

- Internal regulator for 1.8 V core operation

- Optimized pinout improves signal routing which eases implementation for improved signal integrity

## **OEM Selectable**

- · Vendor, product, and language IDs

- Manufacturer ID and product strings (28 character)

- Serial number string (12h digit max)

- Customizable vendor specific data by optional use of external serial EEPROM

- · Bus- or self-powered selection

- · LED blink interval or duration

- Internal power FET configuration

## **Software Features**

- · Optimized for low latency interrupt handling

- Reduced memory footprint

- Device Firmware Upgrade (DFU) support of external EEPROM or External Flash

- Assembly line support

- End user field upgrade support

- DFU Package consists of driver, firmware, sample DFU application and source code, DFU driver API

- Optional custom firmware with up to 128 KB external ROM

## Applications

- · Flash Media Card Reader/Writer

- Printers

- · Desktop and Mobile PCs

- Consumer A/V

- Media Players/Viewers

- Vista ReadyBoost<sup>™</sup>

1.) xD-Picture Card not applicable to USB2251.

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## **Table of Contents**

| 1.0 Introduction         2.0 Pin Configuration         3.0 Block Diagram         4.0 Pin Table         5.0 Pin Descriptions         5.0 Diagram | 4<br>6 |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 3.0 Block Diagram                                                                                                                               | 7      |

| 4.0 Pin Table                                                                                                                                   | 8      |

| 5.0 Pin Descriptions                                                                                                                            | 10     |

| NU FIN Resel State Table                                                                                                                        | 17     |

| 7.0 Configuration Options                                                                                                                       | 21     |

| 3.0 AC Specifications                                                                                                                           | 32     |

| 0.0 DC Parameters                                                                                                                               | 34     |

| 10.0 Package Outline                                                                                                                            | 38     |

| Appendix A: Data Sheet Revision History                                                                                                         | 39     |

| Product Identification System                                                                                                                   | 40     |

| Fhe Microchip Web Site                                                                                                                          | 41     |

| Customer Change Notification Service                                                                                                            | 41     |

| Customer Change Notification Service                                                                                                            | 41     |

## 1.0 INTRODUCTION

The Microchip USB2250/50i/51/51i is a flash media card reader solution fully compliant with the USB 2.0 specification. All required resistors on the USB ports are integrated into the device. This includes all series termination resistors on  $D_{+}$  and  $D_{-}$  pins and all required pull-down and pull-up resistors. The over-current sense inputs for the downstream facing ports have internal pull-up resistors.

## **Hardware Features**

- · Single chip flash media controller

- USB2250/USB2251 supports the commercial temperature range of 0°C to +70°C

- USB2250i/USB2251i supports the industrial temperature range of -40°C to +85°C

- 8051 8-bit microprocessor

- 60 MHz single cycle execution

- 64 KB ROM |14 KB RAM

- · Integrated regulator for 1.8 V core operation

- Flash Media Card Specification Revision Compliance

- · Compact Flash 4.1

- CF UDMA Modes 0-4

- CF PIO Modes 0-6

- Secure Digital 2.0

- HS-SD and HC-SD

- TransFlash™ and reduced form factor media

- MultiMediaCard 4.2

- 1/4/8 bit MMC

- Memory Stick 1.43

- Memory Stick Pro Format 1.02

- Memory Stick Pro-HG Duo Format 1.01

- Memory Stick, MS Duo, HS-MS, MS Pro-HG, MS Pro

- Memory Stick Duo 1.10

- Smart Media 1.3

- xD-Picture Card 1.2

## **Software Features**

- If the OEM is using an external EEPROM, the following features are available:

- Customizable vendor, product, and device ID's

- 12-hex digits maximum for the serial number string

- 28-character manufacturer ID and product strings for the flash media reader/writer

## 1.1 Acronyms

|                | -                                             |

|----------------|-----------------------------------------------|

| ATA:           | Advanced Technology Attachment                |

| CFC:           | Compact Flash Controller                      |

| FET:           | Field Effect Transistor                       |

| LUN:           | Logical Unit Number                           |

| MMC:           | MultiMediaCard                                |

| MSC:           | Memory Stick Controller                       |

| PLL:           | Phase-Locked Loop                             |

| RoHS:          | Restriction of Hazardous Substances Directive |

| RXD:           | Received eXchange Data                        |

| SDC:           | Secure Digital Controller                     |

| SIE:           | Serial Interface Engine                       |

| SMC:           | SmartMedia Controller                         |

| True IDE Mode: | True Integrated Drive Electronics Mode        |

| TXD:           | Transmit eXchange Data                        |

| UART:          | Universal Asynchronous Receiver-Transmitter   |

| UCHAR:         | Unsigned Character                            |

| UINT:          | Unsigned Integer                              |

| VTQFP:         | Very Thin Quad Flat Package                   |

|                |                                               |

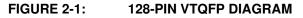

## 2.0 PIN CONFIGURATION

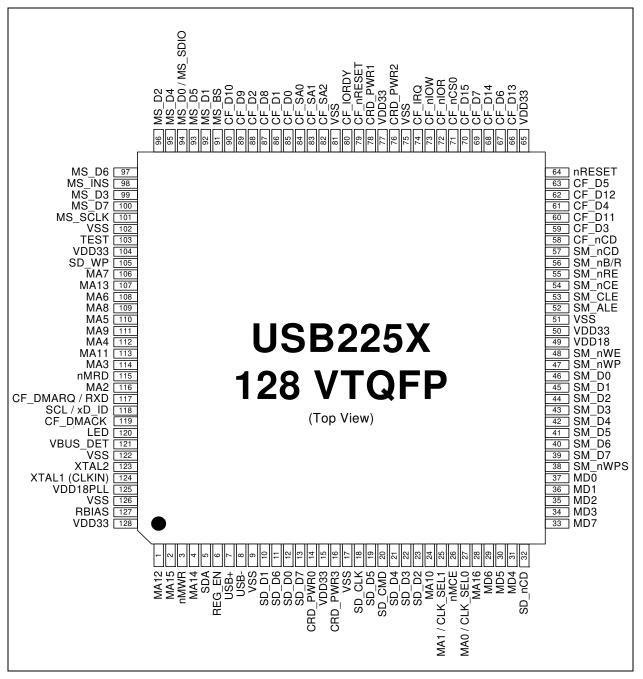

## 3.0 BLOCK DIAGRAM

FIGURE 3-1: USB2250/50I/51/51I BLOCK DIAGRAM

## 4.0 PIN TABLE

## 4.1 128-Pin Package

## TABLE 4-1: 128-PIN VTQFP PACKAGE

|          | COMPACT FLASH INT          | ERFACE (28 PINS)      |           |

|----------|----------------------------|-----------------------|-----------|

| CF_D0    | CF_D1                      | CF_D2                 | CF_D3     |

| CF_D4    | CF_D5                      | CF_D6                 | CF_D7     |

| CF_D8    | CF_D9                      | CF_D10                | CF_D11    |

| CF_D12   | CF_D13                     | CF_D14                | CF_D15    |

| CF_nIOR  | CF_nIOW                    | CF_IRQ                | CF_nRESET |

| CF_IORDY | CF_nCS0                    | CF_DMACK              | CF_SA0    |

| CF_SA1   | CF_SA2                     | CF_nCD                | CF_DMARQ  |

|          | SMARTMEDIA INTE            | RFACE (17 PINS)       |           |

| SM_D0    | SM_D1                      | SM_D2                 | SM_D3     |

| SM_D4    | SM_D5                      | SM_D6                 | SM_D7     |

| SM_ALE   | SM_CLE                     | SM_nRE                | SM_nWE    |

| SM_nWP   | SM_nB/R                    | SM_nCE                | SM_nCD    |

| SM_nWPS  |                            |                       |           |

|          | MEMORY STICK INT           | ERFACE (11 PINS)      |           |

| MS_BS    | MS_D0 / MS_SDIO            | MS_SCLK               | MS_INS    |

| MS_D1    | MS_D2                      | MS_D3                 | MS_D4     |

| MS_D5    | MS_D6                      | MS_D7                 |           |

| S        | ECURE DIGITAL / MULTIMEDIA | ACARD INTERFACE (12 P | INS)      |

| SD_CMD   | SD_CLK                     | SD_D0                 | SD_D1     |

| SD_D2    | SD_D3                      | SD_WP                 | SD_nCD    |

| SD_D4    | SD_D5                      | SD_D6                 | SD_D7     |

|          | USB INTERFA                | CE (6 PINS)           | 1         |

| USB+     | USB-                       | RBIAS                 |           |

| XTAL2    | XTAL1 (CLKIN)              | REG_EN                |           |

|                | MEMORY/IO INTEI | RFACE (28 PINS) |          |  |  |  |  |

|----------------|-----------------|-----------------|----------|--|--|--|--|

| MA0 / CLK_SEL0 | MA1 / CLK_SEL1  | MA2             | MA3      |  |  |  |  |

| MA4            | MA5             | MA6             | MA7      |  |  |  |  |

| MA8            | MA9             | MA10            | MA11     |  |  |  |  |

| MA12           | MA13            | MA14            | MA15     |  |  |  |  |

| MA16           | MD0             | MD1             | MD2      |  |  |  |  |

| MD3            | MD4             | MD5             | MD6      |  |  |  |  |

| MD7            | nMRD            | nMWR            | nMCE     |  |  |  |  |

|                | MISC (10 PINS)  |                 |          |  |  |  |  |

| nRESET         | VBUS_DET        | SCL / xD_ID     | SDA      |  |  |  |  |

| LED            | CRD_PWR0        | CRD_PWR1        | CRD_PWR2 |  |  |  |  |

| CRD_PWR3       | TEST            |                 |          |  |  |  |  |

|                | DIGITAL, POW    | /ER (16 PINS)   | <u>I</u> |  |  |  |  |

| (6) VDD33      | (8) VSS         | VDD18           | VDD18PLL |  |  |  |  |

|                | ΤΟΤΑΙ           | _ 128           | 1        |  |  |  |  |

## TABLE 4-1: 128-PIN VTQFP PACKAGE (CONTINUED)

## 5.0 PIN DESCRIPTIONS

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface. The pin descriptions are applied when using the internal default firmware and can be referenced in Section 7.0, "Configuration Options," on page 21. Please reference Section 1.1, "Acronyms," on page 5 for a list of the acronyms used.

The "n" symbol in the signal name indicates that the active, or asserted, state occurs when the signal is at a low voltage level. When "n" is not present in the signal name, the signal is asserted at the high voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signals. The term assert, or assertion, indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation, indicates that a signal is inactive.

## 5.1 128-Pin VTQFP Pin Descriptions

| Name                   | Symbol       | 128-Pin<br>VTQFP                             | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                  |

|------------------------|--------------|----------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |              | COMPACT FL                                   | ASH (CF) IN    | ITERFACE                                                                                                                                                                                                                                                                                                                     |

| CF Chip Select 0       | CF_nCS0      | 71                                           | O12PU          | This pin is the active low chip select 0 signal for<br>the task file registers of the CF ATA device in<br>True IDE mode. This pin has a weak internal<br>pull-up resistor.                                                                                                                                                   |

| CF Register<br>Address | CF_SA[2:0]   | 82<br>83<br>84                               | I/O12          | These pins are the register select address bits for the CF ATA device.                                                                                                                                                                                                                                                       |

| CF Interrupt           | CF_IRQ       | 74                                           | IPD            | This is the active high interrupt request signal from the CF device. This pin has a weak internal pull-down resistor.                                                                                                                                                                                                        |

| CF Data 15-8           | CF_D[15:8] / | 70<br>68<br>62<br>60<br>90<br>89<br>87       | I/O12PD        | CF_D[15:8]: These pins are the bi-directional data signals CF_D15 - CF_D8 in True IDE mode data transfer.<br>In True IDE mode, all task file register operations occur on CF_D[7:0], while data transfer occurs on CF_D[15:0].<br>These bi-directional data signals have weak internal pull-down resistors.                  |

| CF Data 7-0            | CF_D[7:0]    | 69<br>67<br>63<br>61<br>59<br>88<br>86<br>85 | I/O12PD        | CF_D[7:0]: These pins are the bi-directional<br>data signals CF_D7 - CF_D0 in True IDE mode<br>data transfer. In True IDE mode, all of the task<br>file register operations occur on CF_D[7:0],<br>while data transfer occurs on CF_D[15:0].<br>These bi-directional data signals have weak<br>internal pull-down resistors. |

| IO Ready               | CF_IORDY     | 80                                           | IPU            | This pin is the active high input signal for IORDY. This pin has a weak internal pull-up resistor.                                                                                                                                                                                                                           |

| CF Card<br>Detection1  | CF_nCD       | 58                                           | I/O12          | Designates as the Compact Flash card detection pin.                                                                                                                                                                                                                                                                          |

| CF Hardware<br>Reset   | CF_RESET_N   | 79                                           | O12            | This pin is an active low hardware reset signal to the CF device.                                                                                                                                                                                                                                                            |

| CF IO Read             | CF_nIOR      | 72                                           | O12            | This pin is an active low read strobe signal for the CF device.                                                                                                                                                                                                                                                              |

| CF IO Write<br>Strobe  | CF_nIOW      | 73                                           | O12            | This pin is an active low write strobe signal for the CF device.                                                                                                                                                                                                                                                             |

| Name                       | Symbol     | 128-Pin<br>VTQFP                             | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|------------|----------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CF DMA request             | CF_DMARQ / | 117                                          | I              | CF_DMARQ: This pin is the DMA request from the device to the CF controller.                                                                                                                                                                                                                                                                                |

|                            | RXD        |                                              |                | RXD: The signal can be used as input to the RXD of UART in the device. Custom firmware is required to activate this function.                                                                                                                                                                                                                              |

| CF DMA<br>acknowledge      | CF_DMACK   | 119                                          | 012            | CF_nDMACK: This pin is an active low DMA acknowledge signal for the CF device.                                                                                                                                                                                                                                                                             |

|                            |            | SMARTMED                                     | IA (SM) INT    | ERFACE                                                                                                                                                                                                                                                                                                                                                     |

| SM Write Protect           | SM_nWP     | 47                                           | O12PD          | This pin is an active low write protect signal for<br>the SM device and has a weak pull-down<br>resistor that is permanently enabled.                                                                                                                                                                                                                      |

| SM Address<br>Strobe       | SM_ALE     | 52                                           | O12PD          | This pin is an active high Address Latch Enable signal for the SM device and has a weak pull-down resistor that is permanently enabled.                                                                                                                                                                                                                    |

| SM Command<br>Strobe       | SM_CLE     | 53                                           | O12PD          | This pin is an active high Command Latch<br>Enable signal for the SM device and has a weak<br>pull-down resistor that is permanently enabled.                                                                                                                                                                                                              |

| SM Data 7-0                | SM_D[7:0]  | 39<br>40<br>41<br>42<br>43<br>44<br>45<br>46 | I/O12PD        | These pins are the bi-directional data signals SM_D7-SM_D0 and have weak internal pull-<br>down resistors.                                                                                                                                                                                                                                                 |

| SM Read Enable             | SM_nRE     | 55                                           | O12PU          | This pin is an active low read strobe signal for<br>the SM device.<br>When using the internal FET, this pin has a<br>weak internal pull-up resistor that is tied to the<br>output of the internal power FET.<br>If an external FET is used (internal FET is<br>disabled), then the internal pull-up is not<br>available (external pull-ups must be used).  |

| SM Write Enable            | SM_nWE     | 48                                           | O12PU          | This pin is an active low write strobe signal for<br>the SM device.<br>When using the internal FET, this pin has a<br>weak internal pull-up resistor that is tied to the<br>output of the internal power FET.<br>If an external FET is used (internal FET is<br>disabled), then the internal pull-up is not<br>available (external pull-ups must be used). |

| SM Write Protect<br>Switch | SM_nWPS    | 38                                           | IPU            | A write-protect seal is detected when this pin is low. This pin has a weak internal pull-up resistor.                                                                                                                                                                                                                                                      |

| SM Busy or Data<br>Ready   | SM_nB/R    | 56                                           | IPU            | This pin is connected to the BSY/RDY pin of the SM device.<br>When using the internal FET, this pin has a weak internal pull-up resistor that is tied to the output of the internal power FET.<br>If an external FET is used (internal FET is disabled), then the internal pull-up is not available (external pull-ups must be used).                      |

|                          |             | 128-Pin                                      | Buffer     | ESCRIPTIONS (CONTINUED)                                                                                                                                                                                                                                                                |

|--------------------------|-------------|----------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                     | Symbol      | VTQFP                                        | Туре       | Description                                                                                                                                                                                                                                                                            |

| SM Chip Enable           | SM_nCE      | 54                                           | O12PU      | This pin is the active low chip enable signal to the SM device.                                                                                                                                                                                                                        |

|                          |             |                                              |            | When using the internal FET, this pin has a weak internal pull-up resistor that is tied to the output of the internal power FET.                                                                                                                                                       |

|                          |             |                                              |            | If an external FET is used (internal FET is disabled), then the internal pull-up is not available (external pull-ups must be used).                                                                                                                                                    |

| SM Card<br>Detection     | SM_nCD      | 57                                           | I/O12      | Designates as the Smart Media card detection pin.                                                                                                                                                                                                                                      |

|                          |             | MEMORY STI                                   | CK (MS) IN | TERFACE                                                                                                                                                                                                                                                                                |

| MS Bus State             | MS_BS       | 91                                           | O12        | This pin is connected to the bus state pin of the MS device.                                                                                                                                                                                                                           |

|                          |             |                                              |            | It is used to control the bus states 0, 1, 2 and 3 (BS0, BS1, BS2 and BS3) of the MS device.                                                                                                                                                                                           |

| MS Card Insertion        | MS_INS      | 98                                           | IPU        | Designates as the Memory Stick card detection pin.                                                                                                                                                                                                                                     |

| MS System CLK            | MS_SCLK     | 101                                          | O12        | This pin is an output clock signal to the MS device. The clock frequency is software configurable.                                                                                                                                                                                     |

| MS System Data<br>In/Out | MS_D[7:1]   | 100<br>97<br>93                              | I/O12PD    | MS_D[7:1]: These pins are the bi-directional data signals for the MS device.                                                                                                                                                                                                           |

|                          |             | 95<br>99<br>96<br>92                         |            | MS_D2 and MS_D3 have weak pull-down resistors. MS_D1 has a pull-down resistor if it is in parallel mode, otherwise it is disabled.                                                                                                                                                     |

|                          |             | -                                            |            | In 4- or 8-bit parallel mode, each MS_D7:1 signal has a weak pull-down resistor.                                                                                                                                                                                                       |

| MS System Data<br>In/Out | MS_D0 /     | 94                                           | I/O12PD    | MS_D0: This pin is one of the bi-directional data signals for the MS device.                                                                                                                                                                                                           |

|                          |             |                                              |            | In serial mode, the most significant bit (MSB) of<br>each byte is transmitted first by either MSC or<br>the MS device on MS_D0, MS_D2, and MS_D3<br>(which have weak pull-down resistors). If<br>MS_D1 is in parallel mode, it has a pull-down<br>resistor; Otherwise, it is disabled. |

|                          |             |                                              |            | In 4- or 8-bit parallel mode, the MS_D0 signal has a weak pull-down resistor.                                                                                                                                                                                                          |

|                          | SECURE DIGI | TAL (SD) / MU                                | LTIMEDIAC  | ARD (MMC) INTERFACE                                                                                                                                                                                                                                                                    |

| SD Data 7-0              | SD_D[7:0]   | 13<br>11<br>19<br>21<br>22<br>23<br>10<br>12 | I/O12PU    | These pins are bi-directional data signals SD_D0 - SD_D7 and have weak pull-up resistors.                                                                                                                                                                                              |

| SD Clock                 | SD_CLK      | 18                                           | O12        | This is an output clock signal to the SD/MMC device.                                                                                                                                                                                                                                   |

|                          |             |                                              |            | The clock frequency is software configurable.                                                                                                                                                                                                                                          |

| Name                                              | Symbol           | 128-Pin<br>VTQFP                             | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------|------------------|----------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD Command                                        | SD_CMD           | 20                                           | I/O12PU        | This is a bi-directional signal that connects to the CMD signal of the SD/MMC device and has a weak internal pull-up resistor.                                                                                                                                                                                                |

| SD Write<br>Protected                             | SD_WP            | 105                                          | I/O12          | Designates as the Secure Digital card mechanical write detect pin.                                                                                                                                                                                                                                                            |

| SD Card Detect                                    | SD_nCD           | 32                                           | I/O12          | Designates as the Secure Digital card detection pin.                                                                                                                                                                                                                                                                          |

|                                                   |                  | USB                                          | INTERFAC       | E                                                                                                                                                                                                                                                                                                                             |

| USB Bus Data                                      | USB+<br>USB-     | 7<br>8                                       | I/O-U          | These pins connect to the USB bus data signals.                                                                                                                                                                                                                                                                               |

| USB Transceiver<br>Bias                           | RBIAS            | 127                                          | I-R            | A 12.0 k $\Omega$ , ±1.0% resistor is attached from VSS to this pin in order to set the transceiver's internal bias currents.                                                                                                                                                                                                 |

| 24 MHz Crystal<br>Input (External<br>Clock Input) | XTAL1<br>(CLKIN) | 124                                          | ICLKx          | This pin can be connected to one terminal of the<br>crystal or it can be connected to an external<br>24/48 MHz clock when a crystal is not used.<br>The MA[1:0] pins will be sampled while<br>RESET_N is asserted, and the value will be<br>latched upon RESET_N negation. This will<br>determine the clock source and value. |

| 24 MHz Crystal<br>Output                          | XTAL2            | 123                                          | OCLKx          | This is the other terminal of the crystal, or it is<br>left open when an external clock source is used<br>to drive XTAL1(CLKIN). It may not be used to<br>drive any external circuitry other than the crystal<br>circuit.                                                                                                     |

|                                                   |                  | MEMORY                                       | / IO INTER     | FACE                                                                                                                                                                                                                                                                                                                          |

| Memory<br>Data Bus                                | MD[7:0]          | 33<br>29<br>30<br>31<br>34<br>35<br>36<br>37 | I/O12PU        | These signals are used to transfer data between<br>the internal CPU and the external program<br>memory and have weak internal pull-up<br>resistors.                                                                                                                                                                           |

| Name                   | Symbol           | 128-Pin<br>VTQFP                                                                        | Buffer<br>Type | Description                                                                                                                                                                                                                             |  |  |                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|------------------------|------------------|-----------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

| Memory<br>Address Bus  | MA16             | 28                                                                                      | O12            | These signals address memory locations within the external memory.                                                                                                                                                                      |  |  |                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                        | MA[15:2]         | 2<br>4<br>107<br>1<br>113<br>24<br>111<br>109<br>106<br>108<br>110<br>112<br>114<br>116 | 012            | These signals address memory locations within the external memory.                                                                                                                                                                      |  |  |                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                        | MA[1:0] /        | 25                                                                                      | O12            | MA[1:0]: These signals address memory locations within the external memory.                                                                                                                                                             |  |  |                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                        | CLK_<br>SEL[1:0] | 27                                                                                      | I/O12PD        | CLK_SEL[1:0]: During RESET_N assertion,<br>these pins will select the operating frequency of<br>the external clock, and the corresponding weak<br>pull-down resistors are enabled.                                                      |  |  |                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                        |                  |                                                                                         |                | When RESET_N is negated, the value on these pins will be latched internally and these pins will revert to MA[1:0] functionality; the internal pull-downs will be disabled.                                                              |  |  |                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                        |                  |                                                                                         |                |                                                                                                                                                                                                                                         |  |  | CLK_SEL[1:0] = '00'. 24 MHz<br>CLK_SEL[1:0] = '01'. RESERVED<br>CLK_SEL[1:0] = '10'. RESERVED<br>CLK_SEL[1:0] = '11'. 48 MHz |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                        |                  |                                                                                         |                |                                                                                                                                                                                                                                         |  |  |                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|                        |                  |                                                                                         |                | If the latched value is '0', the corresponding MA pin will function identically to MA[15:3] pins at all times (other than during RESET_N assertion).                                                                                    |  |  |                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Memory Write<br>Strobe | nMWR             | 3                                                                                       | O12            | This pin is the active low program Memory Write strobe signal.                                                                                                                                                                          |  |  |                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Memory Read<br>Strobe  | nMRD             | 115                                                                                     | O12            | This pin is the active low program Memory Read strobe signal.                                                                                                                                                                           |  |  |                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Memory Chip<br>Enable  | nMCE             | 26                                                                                      | 012            | This pin is the active low program Memory Chip<br>Enable strobe signal.<br>This signal is asserted when any external<br>access is being done by the processor.<br>This signal is held to the logic 'high' while<br>RESET_N is asserted. |  |  |                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Name                                          | Symbol   | 128-Pin<br>VTQFP                   | Buffer<br>Type | Description                                                                                                                                           |

|-----------------------------------------------|----------|------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                               |          |                                    | MISC           |                                                                                                                                                       |

| General Purpose                               | LED      | 120                                | I/O12          | LED: It can be used as an LED output.                                                                                                                 |

| Input/Output                                  | VBUS_DET | 121                                | I/O12          | VBUS is a 3.3 volt input. A resistor divider must be used if connecting to 5 volts of USB power.                                                      |

|                                               | SCL /    | 118                                | O12            | SCL: This is the clock output when used with an external EEPROM.                                                                                      |

|                                               | xD_ID    |                                    | I/O12          | xD_ID: This is the xD-Picture Card detection pin only applicable to USB2250/USB2250i.                                                                 |

|                                               | SDA      | 5                                  | I/O12          | SDA: This is the data pin when used with an external serial EEPROM.                                                                                   |

|                                               | CRD_PWR0 | 14                                 | I/O12          | CRD_PWR: Card power drive of 3.3 V at either                                                                                                          |

|                                               |          |                                    | I/O200         | 100 mA or 200 mA.                                                                                                                                     |

|                                               | CRD_PWR1 | 78                                 | I/O12          | CRD_PWR: Card power drive of 3.3 V at either                                                                                                          |

|                                               |          |                                    | I/O200         | 100 mA or 200 mA.                                                                                                                                     |

|                                               | CRD_PWR2 | 76                                 | I/O200         | CRD_PWR: Card power drive of 3.3 V at either 100 mA or 200 mA.                                                                                        |

|                                               |          |                                    |                | Requirement: This must be the only FET used<br>to power SM devices. Failure to do this will<br>violate SM voltage specification on SM device<br>pins. |

|                                               | CRD_PWR3 | 16                                 | I/O200         | CRD_PWR: Card power drive of 3.3 V at either 100 mA or 200 mA.                                                                                        |

|                                               |          |                                    |                | Requirement: This must be the only FET used<br>to power SM devices. Failure to do this will<br>violate SM voltage specification on SM device<br>pins. |

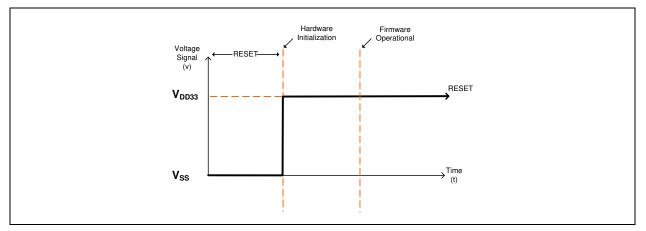

| RESET Input                                   | RESET_N  | 64                                 | IS             | This active low signal is used by the system to reset the chip. The active low pulse should be at least $1\mu$ s wide.                                |

| TEST Input                                    | TEST     | 103                                | I              | Tie this pin to ground for normal operation.                                                                                                          |

| Regulator Enable                              | REG_EN   | 6                                  | IPU            | This signal is used to enable the internal 1.8 V regulator.                                                                                           |

|                                               |          | DIGITAL PO                         | WER, and       | GROUND                                                                                                                                                |

| 1.8 V Digital Core<br>Power                   | VDD18    | 49                                 |                | If the internal regulator is enabled, then this pin must have a 1.0 $\mu$ F (or greater) ±20% (ESR <0.1 $\Omega$ ) capacitor to VSS.                  |

| 1.8 V PLL Power                               | VDD18PLL | 125                                |                | If the internal regulator is enabled, then this pin must have a 1.0 $\mu$ F (or greater) ±20% (ESR <0.1 $\Omega$ ) capacitor to VSS.                  |

| 3.3 V Power and<br>Voltage Regulator<br>Input | VDD33    | 15<br>50<br>65<br>77<br>104<br>128 |                | If the internal regulator is enabled, pins 50 and 128 each require an external bypass capacitor of 4.7 $\mu$ F minimum.                               |

| Name   | Symbol | 128-Pin<br>VTQFP                               | Buffer<br>Type | Description      |

|--------|--------|------------------------------------------------|----------------|------------------|

| Ground | VSS    | 9<br>17<br>51<br>75<br>81<br>102<br>122<br>126 |                | Ground Reference |

#### TABLE 5-1: USB2250/50I/51/51I 128-PIN VTQFP PIN DESCRIPTIONS (CONTINUED)

**Note 5-1** Hot-insertion capable card connectors are required for all flash media. It is required for the SD connector to have a Write Protect switch. This allows the chip to detect the MMC card.

**Note 5-2** nMCE is normally asserted except when the 8051 is in standby mode.

## 5.2 Buffer Type Descriptions

## TABLE 5-2: BUFFER TYPE DESCRIPTIONS

| BUFFER  | DESCRIPTION                                                                                    |

|---------|------------------------------------------------------------------------------------------------|

| 1       | Input.                                                                                         |

| IPU     | Input with internal weak pull-up resistor.                                                     |

| IPD     | Input with internal weak pull-down resistor.                                                   |

| IS      | Input with Schmitt trigger.                                                                    |

| I/O12   | Input/Output buffer with 12 mA sink and 12 mA source.                                          |

| I/O200  | Input/Output buffer 12 mA with FET disabled, 100/200 mA source only when the FET is enabled.   |

| I/O12PD | Input/Output buffer with 12 mA sink and 12 mA source with an internal weak pull-down resistor. |

| I/O12PU | Input/Output buffer with 12 mA sink and 12 mA source with a pull-up resistor.                  |

| O12     | Output buffer with 12 mA source.                                                               |

| O12PU   | Output buffer with 12 mA sink and 12 mA source, with a pull-up resistor.                       |

| O12PD   | Output buffer with 12 mA sink and 12 mA source, with a pull-down resistor.                     |

| ICLKx   | XTAL clock input.                                                                              |

| OCLKx   | XTAL clock output.                                                                             |

| I/O-U   | Analog Input/Output as defined in the USB 2.0 Specification.                                   |

| I-R     | RBIAS.                                                                                         |

## 6.0 PIN RESET STATE TABLE

## TABLE 6-1: LEGEND FOR PIN RESET STATES TABLE

| Symbol                        | Description                                                               |  |  |

|-------------------------------|---------------------------------------------------------------------------|--|--|

| 0                             | Output driven low                                                         |  |  |

| 1 Output driven high          |                                                                           |  |  |

| IP                            | Input enabled                                                             |  |  |

| PU                            | Hardware enables pull-up                                                  |  |  |

| PD Hardware enables pull-down |                                                                           |  |  |

|                               | Hardware disables function                                                |  |  |

| Z                             | Hardware disables pad. Both output driver and input buffers are disabled. |  |  |

## 6.1 128-Pin Reset States

## 6.2 128-Pin Reset States

## TABLE 6-2: USB2250/50I/51/51I 128-PIN RESET STATES

|     |           | Res      | et State              |           |     |                 | Res      | et State              |   |

|-----|-----------|----------|-----------------------|-----------|-----|-----------------|----------|-----------------------|---|

| Pin | Pin Name  | Function | Input/<br>Out-<br>put | PU/<br>PD | Pin | Pin Name        | Function | Input/<br>Out-<br>put |   |

| 85  | CF_D0     | None     | z                     |           | 58  | CF_nCD          | None     | IP                    |   |

| 86  | CF_D1     | None     | z                     |           | 46  | SM_D0           | SM       | z                     |   |

| 88  | CF_D2     | None     | z                     |           | 45  | SM_D1           | SM       | z                     |   |

| 59  | CF_D3     | None     | z                     |           | 44  | SM_D2           | SM       | z                     |   |

| 61  | CF_D4     | None     | z                     |           | 43  | SM_D3           | SM       | z                     |   |

| 63  | CF_D5     | None     | z                     |           | 42  | SM_D4           | SM       | z                     | - |

| 67  | CF_D6     | None     | z                     |           | 41  | SM_D5           | SM       | z                     | - |

| 69  | CF_D7     | None     | z                     |           | 40  | SM_D6           | SM       | z                     | 1 |

| 87  | CF_D8     | None     | z                     |           | 39  | SM_D7           | SM       | z                     | - |

| 89  | CF_D9     | None     | z                     |           | 52  | SM_ALE          | SM       | z                     | - |

| 90  | CF_D10    | None     | z                     |           | 53  | SM_CLE          | SM       | z                     | - |

| 60  | CF_D11    | None     | z                     |           | 47  | SM_nWP          | SM       | z                     | - |

| 62  | CF_D12    | None     | z                     |           | 38  | SM_nWPS         | SM       | z                     | - |

| 66  | CF_D13    | None     | z                     |           | 57  | SM_nCD          | None     | IP                    | - |

| 68  | CF_D14    | None     | z                     |           | 91  | MS_BS           | MS       | z                     | - |

| 70  | CF_D15    | None     | z                     |           | 101 | MS_SCLK         | MS       | z                     | - |

| 72  | CF_nIOR   | CF       | z                     |           | 94  | MS_D0 / MS_SDIO | MS       | z                     | - |

| 73  | CF_nIOW   | CF       | z                     |           | 92  | MS_D1           | MS       | z                     | - |

| 74  | CF_nIRQ   | CF       | z                     |           | 96  | MS_D2           | MS       | z                     | 1 |

| 79  | CF_nRESET | CF       | z                     |           | 99  | MS_D3           | MS       | Z                     |   |

| 80  | CF_IORDY  | CF       | z                     |           | 95  | MS_D4           | MS       | Z                     |   |

| 71  | CF_nCS0   | CF       | z                     |           | 93  | MS_D5           | MS       | z                     |   |

| 84  | CF_SA0    | CF       | z                     |           | 97  | MS_D6           | MS       | Z                     |   |

| 83  | CF_SA1    | CF       | z                     |           | 100 | MS_D7           | MS       | Z                     |   |

| 82  | CF_SA2    | CF       | z                     |           | 98  | MS_INS          | None     | IP                    |   |

| <b>TABLE 6-2:</b> | USB2250/50I/51/51I 128-PIN RESET STATES (CONTINUED) |

|-------------------|-----------------------------------------------------|

|-------------------|-----------------------------------------------------|

|     |                | Reset State |                       |           |  |  |

|-----|----------------|-------------|-----------------------|-----------|--|--|

| Pin | Pin Name       | Function    | Input/<br>Out-<br>put | PU/<br>PD |  |  |

| 119 | CF_DMACK       | None        | 0                     |           |  |  |

| 117 | CF_DMARQ       | None        | 0                     |           |  |  |

| 12  | SD_D0          | SD          | z                     |           |  |  |

| 10  | SD_D1          | SD          | z                     |           |  |  |

| 23  | SD_D2          | SD          | z                     |           |  |  |

| 22  | SD_D3          | SD          | z                     |           |  |  |

| 21  | SD_D4          | SD          | z                     |           |  |  |

| 19  | SD_D5          | SD          | z                     |           |  |  |

| 11  | SD_D6          | SD          | z                     |           |  |  |

| 13  | SD_D7          | SD          | z                     |           |  |  |

| 105 | SD_WP          | None        | 0                     |           |  |  |

| 32  | SD_nCD         | None        | IP                    | pu        |  |  |

| 27  | MA0 / CLK_SEL0 | МА          | IP                    | pd        |  |  |

| 25  | MA1 / CLK_SEL1 | МА          | IP                    | pd        |  |  |

| 116 | MA2            | MA          | IP                    | pd        |  |  |

| 114 | MA3            | MA          | IP                    | pd        |  |  |

| 112 | MA4            | MA          | 0                     |           |  |  |

| 110 | MA5            | MA          | 0                     |           |  |  |

| 108 | MA6            | МА          | 0                     |           |  |  |

| 106 | MA7            | МА          | 0                     |           |  |  |

| 109 | MA8            | MA          | 0                     |           |  |  |

| 111 | MA9            | МА          | 0                     |           |  |  |

| 24  | MA10           | МА          | 0                     |           |  |  |

| 113 | MA11           | МА          | 0                     |           |  |  |

| 107 | MA13           | МА          | 0                     |           |  |  |

| 28  | MA16           | МА          | 0                     |           |  |  |

| 37  | MD0            | МА          | z                     | pu        |  |  |

|     |             | Res      | Reset State           |           |  |  |  |

|-----|-------------|----------|-----------------------|-----------|--|--|--|

| Pin | Pin Name    | Function | Input/<br>Out-<br>put | PU/<br>PD |  |  |  |

| 20  | SD_CMD      | SD       | z                     |           |  |  |  |

| 34  | MD3         | МА       | Z                     | pu        |  |  |  |

| 18  | SD_CLK      | SD       | z                     |           |  |  |  |

| 31  | MD4         | МА       | z                     | pu        |  |  |  |

| 30  | MD5         | МА       | z                     | pu        |  |  |  |

| 29  | MD6         | МА       | z                     | pu        |  |  |  |

| 33  | MD7         | МА       | z                     | pu        |  |  |  |

| 115 | nMRD        | МА       | 1                     |           |  |  |  |

| 26  | nMCE        | МА       | 1                     |           |  |  |  |

| 120 | LED         | None     | 0                     |           |  |  |  |

| 118 | SCL / xD_ID | None     | 0                     |           |  |  |  |

| 14  | CRD_PWR0    | None     | z                     |           |  |  |  |

| 78  | CRD_PWR1    | None     | z                     |           |  |  |  |

| 76  | CRD_PWR2    | None     | z                     |           |  |  |  |

| 16  | CRD_PWR3    | None     | z                     |           |  |  |  |

| 103 | TEST        | TEST     | IP                    |           |  |  |  |

| 64  | nRESET      | nRESET   | IP                    |           |  |  |  |

| 1   | MA12        | МА       | 0                     |           |  |  |  |

| 4   | MA14        | МА       | 0                     |           |  |  |  |

| 2   | MA15        | МА       | 0                     |           |  |  |  |

| 3   | nMWR        | МА       | 1                     |           |  |  |  |

| 121 | VBUS_DET    | None     | IP                    |           |  |  |  |

| 5   | SDA         | None     | 0                     | pu        |  |  |  |

| 55  | SM_nRE      | SM       | z                     |           |  |  |  |

| 48  | SM_nWE      | SM       | z                     |           |  |  |  |

| 56  | SM_nB/R     | SM       | z                     |           |  |  |  |

| 54  | SM_nCE      | SM       | z                     |           |  |  |  |

|     | Reset State |          |                       |           | Res | et State |          |                       |           |

|-----|-------------|----------|-----------------------|-----------|-----|----------|----------|-----------------------|-----------|

| Pin | Pin Name    | Function | Input/<br>Out-<br>put | PU/<br>PD | Pin | Pin Name | Function | Input/<br>Out-<br>put | PU/<br>PD |

| 36  | MD1         | МА       | z                     | pu        | 7   | USB+     | USB+     | z                     |           |

| 35  | MD2         | MA       | Z                     | pu        | 8   | USB-     | USB-     | Z                     |           |

## TABLE 6-2: USB2250/50I/51/51I 128-PIN RESET STATES (CONTINUED)

## 7.0 CONFIGURATION OPTIONS

## 7.1 Card Reader

The Microchip USB2250/50i/51/51i is fully compliant with the following flash media card reader specifications:

- Compact Flash 4.1

- CF UDMA Modes 0-4

- CF PIO Modes 0-6

- Secure Digital 2.0

- HS-SD and HC-SD

- TransFlash<sup>™</sup> and reduced form factor media

- MultiMediaCard 4.2

- 1/4/8 bit MMC

- Memory Stick 1.43

- Memory Stick Pro Format 1.02

- Memory Stick Pro-HG Duo Format 1.01

- Memory Stick, MS Duo, HS-MS, MS Pro-HG, MS Pro

- Memory Stick Duo 1.10

- Smart Media 1.3

- xD-Picture Card 1.2

## 7.1.1 VBUS DETECT

According to Section 7.2.1 of the USB 2.0 Specification, a device cannot provide power to its D+ or D- pull-up resistors unless the upstream port's VBUS is in the asserted (powered) state. The VBUS\_DET pin on the device monitors the state of the upstream VBUS signal and will not pull-up the D+ resistor if VBUS is not active. If VBUS goes from an active to an inactive state (not powered), the device will remove power from the D+ pull-up resistor within 10 seconds.

## 7.2 System Configurations

## 7.2.1 EEPROM

The USB2250/50i/51/51i can be configured via a 2-wire (I<sup>2</sup>C) EEPROM (512x8) flash device containing the options for the USB2250/50i/51/51i. If an external configuration device does not exist the internal default values will be used. If one of the external devices is used for configuration, the OEM can update the values through the USB interface. The device will then "attach" to the upstream USB host.

The USBDM tool set is available in the USB225x Card Reader software release package. To download the software package from Microchip's website, please visit:

http://www.microchip.com/SWLibraryWeb/producttc.aspx?product=OBJ%20files%20for%20USB2250

to go to the OBJ Card Reader Software Download Agreement. Review the license, and if you agree, check the "I agree" box and then select "Confirm". You will then be able to download the USB225x Card reader combo release package zip files containing the USBDM tool set. Please note that the following applies to the system values and descriptions when used:

- N/A = Not applicable to this part

- Reserved = For internal use

## 7.2.2 EEPROM DATA DESCRIPTOR

## TABLE 7-1: INTERNAL FLASH MEDIA CONTROLLER CONFIGURATIONS

| Address             | Register Name   | Description                                       | Internal Default Value                |  |

|---------------------|-----------------|---------------------------------------------------|---------------------------------------|--|

| 00h                 | USB_SER_LEN     | USB Serial String<br>Descriptor Length            | 1Ah                                   |  |

| 01h                 | USB_SER_TYP     | USB Serial String<br>Descriptor Type              | 03h                                   |  |

| 02h-19h             | USB_SER_NUM     | USB Serial Number                                 | "000000225001"<br>(See Note 7-1)      |  |

| 1Ah-1Bh             | USB_VID         | USB Vendor Identifier                             | 0424                                  |  |

| 1Ch-1Dh             | USB_PID         | USB Product Identifier                            | 2250                                  |  |

| 1Eh                 | USB_LANG_LEN    | USB Language String Descriptor<br>Length          | 04h                                   |  |

| 1Fh                 | USB_LANG_TYP    | USB Language String Descriptor<br>Type            | 03h                                   |  |

| 20h                 | USB_LANG_ID_LSB | USB Language Identifier<br>Least Significant Byte | 09h<br>(See Note 7-2)                 |  |

| 21h                 | USB_LANG_ID_MSB | USB Language Identifier<br>Most Significant Byte  | 04h<br>(See Note 7-2)                 |  |

| 22h                 | USB_MFR_STR_LEN | USB Manufacturer String<br>Descriptor Length      | 10h                                   |  |

| 23h                 | USB_MFR_STR_TYP | USB Manufacturer String<br>Descriptor Type        | 03h                                   |  |

| 24h-31h USB_MFR_STR |                 | USB Manufacturer String                           | "Generic"<br>(See Note 7-1)           |  |

| 32h-5Dh             | Reserved        | -                                                 | 00h                                   |  |

| 5Eh                 | USB_PRD_STR_LEN | USB Product String<br>Descriptor Length           | 24h                                   |  |

| 5Fh                 | USB_PRD_STR_TYP | USB Product String<br>Descriptor Type             | 03h                                   |  |

| 60h-99h             | USB_PRD_STR     | USB Product String                                | "Flash Card Reader"<br>(See Note 7-1) |  |

| 9Ah                 | USB_BM_ATT      | USB BmAttribute                                   | 80h                                   |  |

| 9Bh                 | USB_MAX_PWR     | USB Max Power                                     | 30h (96 mA)                           |  |

| 9Ch                 | ATT_LB          | Attribute Lo byte                                 | 40h (Reverse SD_WP only)              |  |

| 9Dh                 | ATT_HLB         | Attribute Hi Lo byte                              | 00h                                   |  |

| 9Eh                 | ATT_LHB         | ATT_LHB Attribute Lo Hi byte                      |                                       |  |

| 9Fh                 | ATT_HB          | Attribute Hi byte                                 | 00h                                   |  |

| A0h                 | MS_PWR_LB       | Memory Stick Device<br>Power Lo byte              | 08h                                   |  |

| A1h                 | MS_PWR_HB       | Memory Stick Device<br>Power Hi byte              | 00h                                   |  |

| A2h                 | CF_PWR_LB       | Compact Flash Device<br>Power Lo byte             | 80h                                   |  |

| A3h                 | CF_PWR_HB       | Compact Flash Device<br>Power Hi byte             | 00h                                   |  |

| A4h                 | SM_PWR_LB       | Smart Media Device<br>Power Lo byte               | 00h                                   |  |

| A5h                 | SM_PWR_HB       | Smart Media Device<br>Power Hi byte               | 08h                                   |  |

| A6h                 | SD_PWR_LB       | Secure Digital Device<br>Power Lo byte            | 00h                                   |  |

| Address   | Register Name         | Description                            | Internal Default Value |

|-----------|-----------------------|----------------------------------------|------------------------|

| A7h       | SD_PWR_HB             | Secure Digital Device<br>Power Hi byte | 80h                    |

| A8h       | LED_BLK_INT           | LED Blink Interval                     | 02h                    |

| A9h       | LED_BLK_DUR           | LED Blink After Access                 | 28h                    |

| AAh - B0h | DEV0_ID_STR           | Device 0 Identifier String             | "CF"                   |