# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **USB 2.0 Hi-Speed 7-Port Hub Controller**

### **General Description**

The 7-Port Hub is a low power, OEM configurable, MTT (multi transaction translator) hub controller IC with 7 downstream ports for embedded USB solutions. The 7-port hub is fully compliant with the USB 2.0 Specification and will attach to an upstream port as a Full-Speed Hub or as a Full-/Hi-Speed Hub. The 7-Port Hub supports Low-Speed, Full-Speed, and Hi-Speed (if operating as a Hi-Speed Hub) downstream devices on all of the enabled downstream ports.

#### **General Features**

- · Hub Controller IC with 7 downstream ports

- High-performance multiple transaction translator MultiTRAK<sup>™</sup> Technology provides one transaction translator per port

- Enhanced OEM configuration options available through either a single serial I<sup>2</sup>C EEPROM, or SMBus Slave Port

- · 64-Pin (9x9 mm) QFN, RoHS compliant package

- Supports commercial (0°C to +70°C) and industrial (-40°C to +85°C) temperature ranges

### **Hardware Features**

- · Low power operation

- Full Power Management with individual or ganged power control of each downstream port

- On-chip Power On Reset (POR)

- Internal 1.8V Voltage Regulator

- Fully integrated USB termination and Pull-up/Pulldown resistors

- On Board 24MHz Crystal Driver, Resonator, or External 24/MHz clock input

- USB host/device speed indicator. Per-port 3-color LED drivers indicate the speed of USB host and device connection - hi-speed (480 Mbps), fullspeed (12 Mbps), low-speed (1.5 Mbps)

- Enhanced EMI rejection and ESD protection performance

## **OEM Selectable Features**

- Customizable Vendor ID, Product ID, and Device ID

- Select whether the hub is part of a compound device (When any downstream port is permanently hardwired to a USB peripheral device, the hub is part of a compound device.)

- Flexible port mapping and disable sequence. Ports can be disabled/reordered in any order to support multiple product SKUs. Hub will automatically reorder the remaining ports to match the Host controller's numbering scheme

- Programmable USB differential-pair pin location

Eases PCB layout by aligning USB signal

- lines directly to connectors

- Programmable USB signal drive strength. Recover USB signal integrity due to compromised system environments using 4-level driving strength resolution

- Select the presence of a permanently hardwired USB peripheral device on a port by port basis

- Configure the delay time for filtering the over-current sense inputs

- Configure the delay time for turning on downstream port power

- Indicate the maximum current that the 347-port hub consumes from the USB upstream port

- Indicate the maximum current required for the hub controller

- Support Custom String Descriptor up to 31 characters in length for:

- Product String

- Manufacturer String

- Serial Number String

- Pin Selectable Options for Default Configuration

- Select Downstream Ports as Non-Removable Ports

- Select Downstream Ports as Disabled Ports

- Select Downstream Port Power Control and Over-Current Detection on a Ganged or Individual Basis

- Select USB Signal Drive Strength

- Select USB Differential Pair Pin location

## Applications

- LCD monitors and TVs

- Multi-function USB peripherals

- · PC mother boards

- Set-top boxes, DVD players, DVR/PVR

- Printers and scanners

- PC media drive bay

- · Portable hub boxes

- Mobile PC docking

- · Embedded systems

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## **Table of Contents**

| 1.0 Acronyms & Definitions                        | 5  |

|---------------------------------------------------|----|

| 1.0 Acronyms & Definitions                        | 6  |

| 3.0 Pin Configuration                             | 7  |

| 3.0 Pin Configuration<br>4.0 Pin Table            | 8  |

|                                                   |    |

| 5.0 Pin Descriptions and Buffer Type Descriptions | 17 |

| 7.0 Configuration Options                         |    |

| B.0 DC Parameters                                 | 47 |

| 9.0 AC Specifications                             | 51 |

| 10.0 Package outline                              | 52 |

| Appendix A: Data Sheet Revision History           | 54 |

| The Microchip Web Site                            | 55 |

| Customer Change Notification Service              | 55 |

| Customer Support                                  | 55 |

| Product Identification System                     | 56 |

## USB2517/USB2517I

## 1.0 ACRONYMS & DEFINITIONS

EEPROMM: Electrically Erasable Programmable Read-Only Memory (a type of non-volatile memory)

- **EMI:** Electromagnetic Interference

- **ESD:** Electrostatic Discharge

- I<sup>2</sup>C: Inter-Integrated Circuit

- LCD: Liquid Crystal Display

- LED: Light Emitting Diode

- **OCS:** Over-current sense

- PCB: Printed Circuit Board

- PHY: Physical Layer

- PLL: Phase-Locked Loop

- PVR: Personal Video Recorder (also known as a Digital Video Recorder)

- QFN: Quad Flat No Leads

- **RoHS:** Restriction of Hazardous Substances Directive

- SCK: Serial Clock

- SD: Secure Digital

- SIE: Serial Interface Engine

- SMBus: System Management Bus

- TT: Transaction Translator

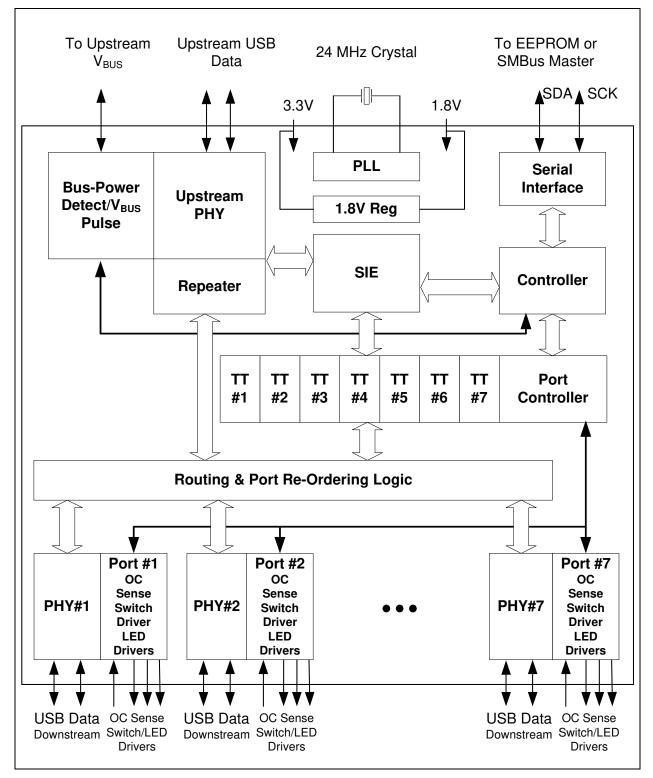

## 2.0 BLOCK DIAGRAM

### FIGURE 2-1: USB2517/USB2517I BLOCK DIAGRAM

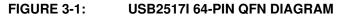

## 3.0 PIN CONFIGURATION

## 4.0 PIN TABLE

## 4.1 64-Pin List

#### TABLE 4-1: USB2517I 64-PIN TABLE

|                              | Upstream USB 2.0 Interfaces (3 pins) |                                     |                          |  |  |

|------------------------------|--------------------------------------|-------------------------------------|--------------------------|--|--|

| USBUP_DP                     | USBUP_DM                             | VBUS_DET                            |                          |  |  |

|                              | Downstream 7-Port US                 | B 2.0 Interfaces (43 Pins)          |                          |  |  |

| USBDN1_DP/<br>PRT_DIS_P1     | USBDN2_DP/<br>PRT_DIS_P2             | USBDN3_DP/<br>PRT_DIS_P3            | USBDN4_DP/<br>PRT_DIS_P4 |  |  |

| USBDN5_DP/<br>PRT_DIS_P5     | USBDN6_DP/<br>PRT_DIS_P6             | USBDN7_DP/<br>PRT_DIS_P7            | USBDN1_DM/<br>PRT_DIS_M1 |  |  |

| USBDN2_DM/<br>PRT_DIS_M2     | USBDN3_DM/<br>PRT_DIS_M3             | USBDN4_DM/<br>PRT_DIS_M4            | USBDN5_DM/<br>PRT_DIS_M5 |  |  |

| USBDN6_DM/<br>PRT_DIS_M6     | USBDN7_DM/<br>PRT_DIS_M7             | LED_A1_N/<br>PRT_SWP1               | LED_A2_N/<br>PRT_SWP2    |  |  |

| LED_A3_N/<br>PRT_SWP3        | LED_A4_N/<br>PRT_SWP4                | LED_A5_N/<br>PRT_SWP5               | LED_A6_N/<br>PRT_SWP6    |  |  |

| LED_A7_N/<br>PRT_SWP7        | LED_B1_N/<br>BOOST0                  | LED_B2_N/<br>BOOST1                 | LED_B3_N/<br>GANG_EN     |  |  |

| LED_B4_N                     | LED_B5_N                             | LED_B6_N                            | LED_B7_N                 |  |  |

| PRTPWR1                      | PRTPWR2                              | PRTPWR3                             | PRTPWR4                  |  |  |

| PRTPWR5                      | PRTPWR6                              | PRTPWR7                             | OCS1_N                   |  |  |

| OCS2_N                       | OCS3_N                               | OCS4_N                              | OCS5_N                   |  |  |

| OCS6_N                       | OCS7_N                               | RBIAS                               |                          |  |  |

|                              | Serial Port In                       | terface (4 Pins)                    |                          |  |  |

| SDA/<br>SMBDATA/<br>NON_REM1 | SCL/<br>SMBCLK/<br>CFG_SEL0          | HS_IND/<br>CFG_SEL1                 | CFG_SEL2                 |  |  |

|                              | MISC                                 | (5 Pins)                            |                          |  |  |

| XTAL1/CLKIN                  | XTAL2                                | SUSP_IND/<br>LOCAL_PWR/<br>NON_REM0 | RESET_N                  |  |  |

| TEST                         |                                      |                                     |                          |  |  |

## TABLE 4-1: USB2517I 64-PIN TABLE (CONTINUED)

|          | Analog Power (6 Pins) |                 |  |  |

|----------|-----------------------|-----------------|--|--|

| VDD18PLL | VDD33PLL              | (4) VDDA33      |  |  |

|          | Digital Power, 0      | Ground (3 Pins) |  |  |

| VDD33    | VDD18                 | VDD33CR         |  |  |

|          | Total 64              |                 |  |  |

## 5.0 PIN DESCRIPTIONS AND BUFFER TYPE DESCRIPTIONS

## 5.1 Pin Descriptions

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface.

The "N" symbol in the signal name indicates that the active, or asserted, state occurs when the signal is at a low voltage level. When "N" is not present before the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signals. The term assert, or assertion, indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation, indicates that a signal is inactive.

| Symbol                                                                    | 64 QFN                                                                   | Buffer Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                           |                                                                          | Upst        | ream USB Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| USBUP_DP<br>USBUP_DM                                                      | 59<br>58                                                                 | IO-U        | USB Bus Data<br>These pins connect to the upstream USB bus data signals (Host<br>port, or upstream hub).                                                                                                                                                                                                                                                                                                                                                                          |

| VBUS_DET                                                                  | 44                                                                       | I/O12       | Detect Upstream VBUS Power<br>Detects state of Upstream VBUS power. The MCHP Hub monitors<br>VBUS_DET to determine when to assert the internal D+ pull-up<br>resistor (signaling a connect event).<br>When designing a detachable hub, this pin must be connected to<br>the VBUS power pin of the USB port that is upstream from the hub.<br>For self-powered applications with a permanently attached host,<br>this pin must be connected to 3.3V or 5.0V (typically VDD33).     |

|                                                                           | Downstream 7-Port USB 2.0 Interfaces                                     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| USBDN[7:1]_DP/<br>PRT_DIS_P[7:1]<br>&<br>USBDN[7:1]_DM/<br>PRT_DIS_M[7:1] | 56<br>54<br>12<br>9<br>7<br>4<br>2<br>55<br>53<br>11<br>8<br>6<br>3<br>1 | IO-U        | Hi-Speed USB Data & Port Disable Strap Option<br>USBDN_DP[7:1] / USBDN_DM[7:1]: These pins connect to the<br>downstream USB peripheral devices attached to the hub's port.<br>Downstream Port Disable Strap option:<br>PRT_DIS_P[7:1] / PRT_DIS_M[7:1]: If the strap is enabled by<br>package and configuration settings (see Table 5-2), this pin will be<br>sampled at RESET_N negation to determine if the port is disabled.<br>To disable, pull up with 10K resistor to 3.3V. |

| PRTPWR[7:1]                                                               | 36<br>39<br>30<br>20<br>23<br>26<br>29                                   | 012         | USB Power Enable<br>Enables power to USB peripheral devices downstream.<br><b>Note:</b> The hub supports active high power controllers only!                                                                                                                                                                                                                                                                                                                                      |

TABLE 5-1: USB2517/USB2517I PIN DESCRIPTIONS

| Symbol                        | 64 QFN                                 | Buffer Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------|----------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED_A[7:1]_N/<br>PRT_SWP[7:1] | 15<br>17<br>31<br>33<br>47<br>49<br>51 | I/O12       | Port LED Indicators & Port Swap strapping option<br>Indicator LED for ports 1-7. Will be active low when LED support is<br>enabled via EEPROM or SMBus.<br>If this strap is enabled by package and configuration settings (see<br>Table 5-2), this pin will be sampled at RESET_N negation to deter-<br>mine the electrical connection polarity of the downstream USB<br>Port pins (USB_DP and USB_DM).<br>Also, the active state of the LED will be determined as follows:<br>'0' = Port Polarity is normal, LED is active high.<br>'1' = Port Polarity (USB_DP and USB_DM) is swapped, LED is<br>active low. |

| LED_B[7:4]_N                  | 14<br>16<br>18<br>32                   | I/O12       | Enhanced Indicator Port 4-7 LED<br>Enhanced Indicator LED for ports 4-7. Will be active low when LED<br>support is enabled via EEPROM or SMBus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LED_B3_N/<br>GANG_EN          | 34                                     | I/O12       | Enhanced Port 3 LED, Gang Power, and Over-current Strap<br>Option<br>Enhanced Indicator LED for port 3. Will be active low when LED<br>support is enabled via EEPROM or SMBus.<br>GANG_EN: Selects between Gang or Individual Port power and<br>Over-current sensing.<br>If this strap is enabled by package and configuration settings (see<br>Table 5-2), this pin will be sampled at RESET_N negation to deter-<br>mine the mode as follows:<br>'0' = Individual sensing & switching, and LED_B3_N is active high.<br>'1' = Ganged sensing & switching, and LED_B3_N is active low.                         |

| TABLE 5-1: | USB2517/USB2517I PIN DESCRIPTIONS (CONT |  |

|------------|-----------------------------------------|--|

| IADEE J-I. |                                         |  |

| TABLE 5-1: | USB2517/USB2517I PIN DESCRIPTIONS (CONTINUED) |  |

|------------|-----------------------------------------------|--|

|------------|-----------------------------------------------|--|

| Symbol                      | 64 QFN   | Buffer Type | Description                                                                                                                                                                                                                                                                                                         |

|-----------------------------|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED_B[2:1]_N/<br>BOOST[1:0] | 48<br>50 | I/O12       | Enhanced Port [2:1] LED & PHY Boost strapping option                                                                                                                                                                                                                                                                |

|                             |          |             | Enhanced Indicator LED for ports 1 & 2. Will be active low when                                                                                                                                                                                                                                                     |

|                             |          |             | LED support is enabled via EEPROM or SMBus.                                                                                                                                                                                                                                                                         |

|                             |          |             | BOOST[1:0]: If this strap is enabled by package and configuration settings (see Table 5-2), this pin will be sampled at RESET_N negation to determine if all PHY ports (upstream and downstream) operate at a normal or boosted electrical level. Also, the active state of the LEDs will be determined as follows: |

|                             |          |             | See Section 7.2.1.26, "Register F6h: Boost_Up" and Section 7.2.1.28, "Register F8h: Boost_4:0".                                                                                                                                                                                                                     |

|                             |          |             | BOOST[1:0] = BOOST_IOUT[1:0]                                                                                                                                                                                                                                                                                        |

|                             |          |             | BOOST[1:0] = '00',                                                                                                                                                                                                                                                                                                  |

|                             |          |             | LED_B2_N is active high,                                                                                                                                                                                                                                                                                            |

|                             |          |             | LED_B1_N is active high.                                                                                                                                                                                                                                                                                            |

|                             |          |             | BOOST[1:0] = '01',                                                                                                                                                                                                                                                                                                  |

|                             |          |             | LED_B2_N is active high,                                                                                                                                                                                                                                                                                            |

|                             |          |             | LED_B1_N is active low.                                                                                                                                                                                                                                                                                             |

|                             |          |             | BOOST[1:0] = '10',                                                                                                                                                                                                                                                                                                  |

|                             |          |             | LED_B2_N is active low,                                                                                                                                                                                                                                                                                             |

|                             |          |             | LED_B1_N is active high.                                                                                                                                                                                                                                                                                            |

|                             |          |             | BOOST[1:0] = '11',                                                                                                                                                                                                                                                                                                  |

|                             |          |             | LED_B2_N is active low,                                                                                                                                                                                                                                                                                             |

|                             |          |             | LED_B1_N is active low.                                                                                                                                                                                                                                                                                             |

| OCS[7:1]_N                  | 37       | IPU         | Over-current Sense                                                                                                                                                                                                                                                                                                  |

|                             | 38<br>35 |             | Input from external current monitor indicating an over-current con-                                                                                                                                                                                                                                                 |

|                             | 21       |             | dition.                                                                                                                                                                                                                                                                                                             |

|                             | 22       |             |                                                                                                                                                                                                                                                                                                                     |

|                             | 27       |             | {Note: Contains internal pull-up to 3.3V supply}                                                                                                                                                                                                                                                                    |

|                             | 28       | . –         |                                                                                                                                                                                                                                                                                                                     |

| RBIAS                       | 63       | I-R         | USB Transceiver Bias                                                                                                                                                                                                                                                                                                |

|                             |          |             | A 12.0k $\Omega$ (+/- 1%) resistor is attached from the ground to this pin                                                                                                                                                                                                                                          |

|                             |          |             | to set the transceiver's internal bias settings.                                                                                                                                                                                                                                                                    |

| Symbol               | 64 QFN | Buffer Type | Description                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------|--------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |        | S           | erial Port Interface                                                                                                                                                                                                                                                                                                                                                        |

| SDA/                 | 40     | I/OSD12     | Serial Data / SMB Data                                                                                                                                                                                                                                                                                                                                                      |

| SMBDATA/<br>NON_REM1 |        |             | NON_REM1: Non-removable port strap option.                                                                                                                                                                                                                                                                                                                                  |

|                      |        |             | If this strap is enabled by package and configuration settings (see Table 5-2) this pin will be sampled (in conjunction with SUSP_IND/LOCAL_PWR/NON_REM0) at RESET_N negation to determine if ports [3:1] contain permanently attached (non-removable) devices:                                                                                                             |

|                      |        |             | NON_REM[1:0] = '00', All ports are removable,                                                                                                                                                                                                                                                                                                                               |

|                      |        |             | NON_REM[1:0] = '01', Port 1 is non-removable,                                                                                                                                                                                                                                                                                                                               |

|                      |        |             | NON_REM[1:0] = '10', Ports 1 & 2 are non-removable,                                                                                                                                                                                                                                                                                                                         |

|                      |        |             | NON_REM[1:0] = '11', Ports 1, 2 & 3 are non-removable.                                                                                                                                                                                                                                                                                                                      |

| SCL/                 | 41     | I/OSD12     | Serial Clock (SCL)                                                                                                                                                                                                                                                                                                                                                          |

|                      |        |             | SMBus Clock (SMBCLK)                                                                                                                                                                                                                                                                                                                                                        |

| SMBCLK/              |        |             | Configuration Select_SEL0: The logic state of this multifunctional                                                                                                                                                                                                                                                                                                          |

| CFG_SEL0             |        |             | pin is internally latched on the rising edge of RESET_N (RESET_N negation), and will determine the hub configuration method as described in Table 5-2, "USB2517I SMBUS or EEPROM Interface Behavior".                                                                                                                                                                       |

| HS_IND/<br>CFG_SEL1  | 42     | I/O12       | Hi-Speed Upstream port indicator & Configuration Programming Select                                                                                                                                                                                                                                                                                                         |

|                      |        |             | HS_IND: High Speed Indicator for upstream port connection speed.                                                                                                                                                                                                                                                                                                            |

|                      |        |             | The active state of the LED will be determined as follows:                                                                                                                                                                                                                                                                                                                  |

|                      |        |             | CFG SEL1 = '0',                                                                                                                                                                                                                                                                                                                                                             |

|                      |        |             | HS_IND is active high,                                                                                                                                                                                                                                                                                                                                                      |

|                      |        |             | CFG_SEL1 = '1',                                                                                                                                                                                                                                                                                                                                                             |

|                      |        |             | HS_IND is active low,                                                                                                                                                                                                                                                                                                                                                       |

|                      |        |             | 'Asserted' = Hub is connected at HS<br>'Negated' = Hub is connected at FS                                                                                                                                                                                                                                                                                                   |

|                      |        |             | CFG_SEL1: The logic state of this pin is internally latched on the rising edge of RESET_N (RESET_N negation), and will determine the hub configuration method as described in Table 5-2, "USB2517I SMBUS or EEPROM Interface Behavior".                                                                                                                                     |

| CFG_SEL2             | 13     | Ι           | Configuration Programming Select<br>This pin is not available in all packages; it is held to a logic '0' when<br>not available.<br>The logic state of this pin is internally latched on the rising edge of<br>RESET_N (RESET_N negation), and will determine the hub con-<br>figuration method as described in Table 5-2, "USB2517I SMBUS<br>or EEPROM Interface Behavior". |

| <b>TABLE 5-1</b> : | USB2517/USB2517I PIN DESCRIPTIONS ( | (CONTINUED) | ) |

|--------------------|-------------------------------------|-------------|---|

|--------------------|-------------------------------------|-------------|---|

## TABLE 5-1: USB2517/USB2517I PIN DESCRIPTIONS (CONTINUED)

| Symbol                              | 64 QFN | Buffer Type | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     |        |             | MISC                                                                                                                                                                                                                                                                                                                                                                                                   |

| XTAL1/<br>CLKIN                     | 61     | ICLKx       | Crystal Input/External Clock Input                                                                                                                                                                                                                                                                                                                                                                     |

|                                     |        |             | 24MHz crystal or external clock input.<br>This pin connects to either one terminal of the crystal or to an<br>external 24MHz clock when a crystal is not used.                                                                                                                                                                                                                                         |

| XTAL2                               | 60     | OCLKx       | Crystal Output                                                                                                                                                                                                                                                                                                                                                                                         |

|                                     |        |             | 24MHz Crystal<br>This is the other terminal of the crystal. It can be treated as a no<br>connect when an external clock source is used to drive XTAL1/<br>CLKIN. This output must not be used to drive any external circuitry<br>other than the crystal circuit.                                                                                                                                       |

| RESET_N                             | 43     | IS          | RESET Input                                                                                                                                                                                                                                                                                                                                                                                            |

|                                     |        |             | The system can reset the chip by driving this input low. The minimum active low pulse is 1 $\mu s.$                                                                                                                                                                                                                                                                                                    |

|                                     |        |             | When the RESET_N pin is pulled to VDD33, the internal POR (Power on Reset) is enabled and no external reset circuitry is required. The internal POR holds the internal logic in reset until the power supplies are stable.                                                                                                                                                                             |

| SUSP_IND/<br>LOCAL_PWR/<br>NON_REM0 | 45     | I/O12       | Active/Suspend status LED or Local-Power & Non-Removable Strap Option                                                                                                                                                                                                                                                                                                                                  |

|                                     |        |             | Suspend Indicator: Indicates the USB state of the hub.                                                                                                                                                                                                                                                                                                                                                 |

|                                     |        |             | 'negated' = Unconfigured or configured and in USB suspend<br>'asserted' = Hub is configured, and is active (i.e., not in suspend)                                                                                                                                                                                                                                                                      |

|                                     |        |             | Local Power: Detects availability of local self-power source.                                                                                                                                                                                                                                                                                                                                          |

|                                     |        |             | Low = Self/local power source is NOT available (i.e., Hub gets all<br>power from the upstream USB VBus).<br>High = Self/local power source is available.                                                                                                                                                                                                                                               |

|                                     |        |             | NON_REM0 Strap Option:<br>If this strap is enabled by package and configuration settings (see<br>Table 5-2, "USB2517I SMBUS or EEPROM Interface Behavior"),<br>this pin will be sampled (in conjunction with NON_REM1) at<br>RESET_N negation to determine if ports [3:1] contain permanently<br>attached (non-removable) devices. Also, the active state of the<br>LED will be determined as follows: |

|                                     |        |             | NON_REM[1:0] = '00', All ports are removable, and the LED is active high                                                                                                                                                                                                                                                                                                                               |

|                                     |        |             | NON_REM[1:0] = '01', Port 1 is non-removable, and the LED is active low                                                                                                                                                                                                                                                                                                                                |

|                                     |        |             | NON_REM[1:0] = '10', Ports 1 & 2 are non-removable, and the LED is active high                                                                                                                                                                                                                                                                                                                         |

|                                     |        |             | NON_REM[1:0] = '11', Ports 1, 2 & 3 are non-removable, and the LED is active low                                                                                                                                                                                                                                                                                                                       |

| Symbol   | 64 QFN   | Buffer Type | Description                                                                                                                                                               |

|----------|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST     | 19       | IPD         | TEST pin                                                                                                                                                                  |

|          |          |             | XNOR continuity tests all signal pins on the hub. Please contact<br>your MCHP representative for a detailed description of how this<br>test mode is enabled and utilized. |

|          | •        | Powe        | r, Ground, No Connect                                                                                                                                                     |

| VDD18    | 25       |             | VDD Core                                                                                                                                                                  |

|          |          |             | +1.8V core power. This pin must have a 1.0 $\mu$ F (or greater) ±20% (ESR <0.1 $\Omega$ ) capacitor to VSS.                                                               |

| VDD33PLL | 64       |             | VDD 3.3 PLL Regulator Reference                                                                                                                                           |

|          |          |             | +3.3V power supply for the Digital I/O. If the internal PLL 1.8V regulator is enabled, then this pin acts as the regulator input.                                         |

| VDD18PLL | 62       |             | VDD PLL                                                                                                                                                                   |

|          |          |             | +1.8V Filtered analog power for internal PLL. This pin must have a $1.0\mu F$ (or greater) ±20% (ESR <0.1 $\Omega$ ) capacitor to VSS.                                    |

| VDD33    | 46       |             | VDD I/O                                                                                                                                                                   |

|          |          |             | +3.3V Digital I/O power                                                                                                                                                   |

| VDDA33   | 5<br>10  |             | VDD Analog I/O                                                                                                                                                            |

|          | 52<br>57 |             | +3.3V Filtered analog PHY power which is shared between adja-<br>cent ports.                                                                                              |

| VDD33CR  | 24       |             | VDDIO/VDD 3.3 Core Regulator Reference                                                                                                                                    |

|          |          |             | +3.3V power supply for the Digital I/O. If the internal core regulator is enabled, then VDD33CR acts as the regulator input.                                              |

| Ground   | VSS      | Slug        | Ground                                                                                                                                                                    |

#### TABLE 5-1: USB2517/USB2517I PIN DESCRIPTIONS (CONTINUED)

#### TABLE 5-2: USB2517I SMBUS OR EEPROM INTERFACE BEHAVIOR

| CFG_SEL2 | CFG_SEL1 | CFG_SEL0 | SMBus or EEPROM Interface Behavior                                                                                                                                                                                                 |

|----------|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | 0        | 0        | Internal Default Configuration <ul> <li>Strap Option sare Enabled</li> </ul>                                                                                                                                                       |

| 0        | 0        | 1        | <ul> <li>Configured as an SMBus slave for external download of user-defined descriptors</li> <li>SMBus slave address is '0101100'</li> <li>Strap Options are Disabled</li> <li>All Settings are Controlled by Registers</li> </ul> |

| 0        | 1        | 0        | Internal Default Configuration <ul> <li>Strap Options are Enabled</li> <li>Bus Power Operation</li> <li>LED Mode = USB</li> </ul>                                                                                                  |

© 2013-2016 Microchip Technology Inc.

| CFG_SEL2 | CFG_SEL1 | CFG_SEL0 | SMBus or EEPROM Interface Behavior                                                                                                                                         |

|----------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | 1        | 1        | <ul> <li>2-Wire I<sup>2</sup>C EEPROMS are supported</li> <li>Strap Options are Disabled</li> <li>All Settings are Controlled by Registers</li> </ul>                      |

| 1        | 0        | 0        | <ul><li>Internal Default Configuration</li><li>Strap Options are Disabled</li><li>Dynamic Power Switching is Enabled</li></ul>                                             |

| 1        | 0        | 1        | Internal Default Configuration <ul> <li>Strap Options are Disabled</li> <li>Dynamic Power Switching is Enabled</li> <li>LED Mode = USB</li> </ul>                          |

| 1        | 1        | 0        | Internal Default Configuration <ul> <li>Strap Options are Disabled</li> </ul>                                                                                              |

| 1        | 1        | 1        | Internal Default Configuration <ul> <li>Strap Options are Disabled</li> <li>LED Mode = USB</li> <li>Ganged Power Switching</li> <li>Ganged Over-Current Sensing</li> </ul> |

## TABLE 5-2: USB2517I SMBUS OR EEPROM INTERFACE BEHAVIOR (CONTINUED)

## 5.2 Buffer Type Descriptions

### TABLE 5-3: USB2517/USB2517I BUFFER TYPE DESCRIPTIONS

| Buffer  | Description                                                                                                 |

|---------|-------------------------------------------------------------------------------------------------------------|

| I       | Input.                                                                                                      |

| IPD     | Input with internal weak pull-down resistor.                                                                |

| IPU     | Input with internal weak pull-up resistor.                                                                  |

| IS      | Input with Schmitt trigger.                                                                                 |

| O12     | Output 12mA.                                                                                                |

| I/O12   | Input/Output buffer with 12mA sink and 12mA source.                                                         |

| I/OSD12 | Open drain12mA sink with Schmitt trigger, and must meet $I^2C$ -Bus Specification Version 2.1 requirements. |

| ICLKx   | XTAL clock input.                                                                                           |

| OCLKx   | XTAL clock output.                                                                                          |

| I-R     | RBIAS.                                                                                                      |

| IO-U    | Analog Input/Output Defined in USB specification.                                                           |

## 6.0 LED USAGE DESCRIPTION

## 6.1 LED Functionality

The hub supports 2 different (mutually exclusive) LED modes. The USB Mode provides 14 LED's that conform to the USB 2.0 specification functional requirements for Green and Amber LED's. The LED Mode "Speed indicator" provides the downstream device connection speed.

#### 6.1.1 USB MODE 14-WIRE

The LED\_A[7:1]\_N pins are used to provide Green LED support as defined in the USB 2.0 specification. The LED\_B[7:1]\_N pins are used to provide Amber LED support as defined in the USB 2.0 specification. The USB Specification defines the LED's as port status indicators for the downstream ports. Please note that no indication of port speed is possible in this mode. The pins are utilized as follows:

- LED\_A1\_N = Port 1 green LED

- LED\_A2\_N = Port 2 green LED

- LED\_A3\_N = Port 3 green LED

- LED A4 N = Port 4 green LED

- LED A5 N = Port 5 green LED

- LED A6 N = Port 6 green LED

- LED\_A7\_N = Port 7 green LED

- LED B1 N = Port 1 amber LED

- LED B2 N = Port 2 amber LED

- LED B3 N = Port 3 amber LED

- LED B4 N = Port 4 amber LED

- LED B5 N = Port 5 amber LED

- LED B6 N = Port 6 amber LED

- LED B7 N = Port 7 amber LED

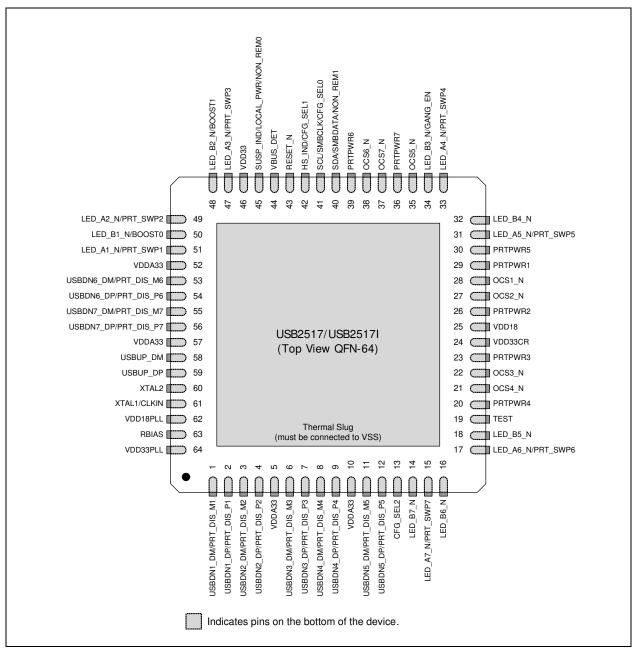

### 6.1.2 LED MODE SPEED INDICATION

The LED\_A[7:1]\_N pins are used to provide connection status as well as port speed by using dual color LED's. This scheme requires that the LED's be in the same package, and that a third color is produced so that the user perceives both LED's as being driven "simultaneously".

The LED\_A[7:1] pins used in this mode are connected to 7 dual color LED's (each LED pair in a single package). These pins indicate the USB speed of each attached downstream device.

Each dual color LED provides two separate colors (commonly Green and Red). If each of these separate colors are pulsed on and off at a rapid rate, a user will see a third color (in this example, Orange). Using this method, 4 different "color" states are possible (Green, Red, Orange, and Off).

#### FIGURE 6-1: DUAL COLOR LED IMPLEMENTATION EXAMPLE

Figure 6-1 shows a simple example of how this LED circuit will be implemented. The circuit should be replicated for each of the 7 LED pins on the HUB. In this circuit, when the LED pin is driven to a logic low state, the Green LED will light up. When the LED pin is driven to a Logic High state the Red LED will light up. When a 1 KHz square wave is driven out on the LED pin, the Green and Red LED's will both alternately light up giving the effect of the color Orange. When nothing is driven out on the LED pin (i.e. the pin floats to a "tri-state" condition), neither the Green nor Red LED will light up, this is the "Off" state.

The assignment is as follows:

- LED\_A1\_N = LED D1 (Downstream Port 1)

- LED\_A2\_N = LED D2 (Downstream Port 2)

- LED\_A3\_N = LED D3 (Downstream Port 3)

- LED\_A4\_N = LED D4 (Downstream Port 4)

- LED\_A5\_N = LED D5 (Downstream Port 5)

- LED\_A6\_N = LED D6 (Downstream Port 6)

- LED\_A7\_N = LED D7 (Downstream Port 7)

The usage is as follows:

- LED\_Ax\_N Driven to Logic Low = LS device attached (Green LED)

- LED\_Ax\_N Driven to Logic High = FS device attached (Red LED)

- LED\_Ax\_N Pulsed @ 1 KHz= HS device attached (Orange color by pulsing Red & Green).

- LED\_Ax\_N is tri-state= No devices are attached, or the hub is in suspend, LED's are off.

## 7.0 CONFIGURATION OPTIONS

## 7.1 7-Port Hub

The USB 2.0 7-Port Hub is fully compliant to the Universal Serial Bus Specification Revision 2.0 from April 27, 2000 (12/ 7/2000 and 5/28/2002 Errata). Please reference Chapter 11 (Hub Specification) for general details regarding Hub operation and functionality.

For performance reasons, the 7-Port Hub provides 1 Transaction Translator (TT) per port (defined as Multi-TT configuration), divided into 4 non-periodic buffers per TT.

#### 7.1.1 HUB CONFIGURATION OPTIONS

The MCHP Hub supports a large number of features (some are mutually exclusive), and must be configured in order to correctly function when attached to a USB host controller. There are three principal ways to configure the Hub: SMBus, EEPROM, or by internal default settings (with or without pin strapping option overrides). In all cases, the configuration method will be determined by the CFG\_SEL2, CFG\_SEL1 and CFG\_SEL0 pins immediately after RESET\_N negation.

#### 7.1.1.1 Power Switching Polarity

Note: The hub will support active high power controllers only!

#### 7.1.2 VBUS DETECT

According to Section 7.2.1 of the USB 2.0 Specification, a downstream port can never provide power to its D+ or D- pull up resistors unless the upstream port's VBUS is in the asserted (powered) state. The VBUS\_DET pin on the Hub monitors the state of the upstream VBUS signal and will not pull up the D+ resistor if VBUS is not active. If VBUS goes from an active to an inactive state (not powered), the Hub will remove power from the D+ pull up resistor within 10 seconds.

#### 7.2 **EEPROM** Interface

The MCHP Hub can be configured via a 2-wire (I<sup>2</sup>C) EEPROM (256x8). (Please see Table 5-2, "USB2517I SMBUS or EEPROM Interface Behavior" for specific details on how to enable configuration via an I<sup>2</sup>C EEPROM).

The internal state machine will (when configured for EEPROM support) read the external EEPROM for configuration data. The Hub will then "attach" to the upstream USB host.

**Note:** The Hub does not have the capacity to write, or "Program," an external EEPROM. The Hub only has the capability to read external EEPROMs. The external EEPROM will be read (even if it is blank or non-populated), and the Hub will be "configured" with the values that are read.

Please see Internal Register Set (Common to EEPROM and SMBus) for a list of data fields available.

#### 7.2.1 INTERNAL REGISTER SET (COMMON TO EEPROM AND SMBUS)

#### TABLE 7-1: INTERNAL DEFAULT, EEPROM AND SMBUS REGISTER MEMORY MAP

| Reg Addr | R/W | Register Name | Abbr | Internal<br>Default ROM | SMBus and<br>EEPROM POR<br>Values |

|----------|-----|---------------|------|-------------------------|-----------------------------------|

| 00h      | R/W | VID LSB       | VIDL | 24h                     | 0x00                              |

| 01h      | R/W | VID MSB       | VIDM | 04h                     | 0x00                              |

| 02h      | R/W | PID LSB       | PIDL | 17h                     | 0x00                              |

| 03h      | R/W | PID MSB       | PIDM | 25h                     | 0x00                              |

| 04h      | R/W | DID LSB       | DIDL | 00h                     | 0x00                              |

| 05h      | R/W | DID MSB       | DIDM | 00h                     | 0x00                              |

© 2013-2016 Microchip Technology Inc.

## USB2517/USB2517I

| Reg Addr | R/W | Register Name                        | Abbr    | Internal<br>Default ROM | SMBus and<br>EEPROM POR<br>Values |

|----------|-----|--------------------------------------|---------|-------------------------|-----------------------------------|

| 06h      | R/W | Config Data Byte 1                   | CFG1    | 9Bh                     | 0x00                              |

| 07h      | R/W | Config Data Byte 2                   | CFG2    | 20h                     | 0x00                              |

| 08h      | R/W | Config Data Byte 3                   | CFG3    | 00h                     | 0x00                              |

| 09h      | R/W | Non-Removable Devices                | NRD     | 00h                     | 0x00                              |

| 0Ah      | R/W | Port Disable (Self)                  | PDS     | 00h                     | 0x00                              |

| 0Bh      | R/W | Port Disable (Bus)                   | PDB     | 00h                     | 0x00                              |

| 0Ch      | R/W | Max Power (Self)                     | MAXPS   | 01h                     | 0x00                              |

| 0Dh      | R/W | Max Power (Bus)                      | MAXPB   | 32h                     | 0x00                              |

| 0Eh      | R/W | Hub Controller Max Current<br>(Self) | HCMCS   | 01h                     | 0×00                              |

| 0Fh      | R/W | Hub Controller Max Current<br>(Bus)  | HCMCB   | 32h                     | 0×00                              |

| 10h      | R/W | Power-on Time                        | PWRT    | 32h                     | 0x00                              |

| 11h      | R/W | LANG_ID_H                            | LANGIDH | 00h                     | 0x00                              |

| 12h      | R/W | LANG_ID_L                            | LANGIDL | 00h                     | 0x00                              |

| 13h      | R/W | MFR_STR_LEN                          | MFRSL   | 00h                     | 0x00                              |

| 14h      | R/W | PRD_STR_LEN                          | PRDSL   | 00h                     | 0x00                              |

| 15h      | R/W | SER_STR_LEN                          | SERSL   | 00h                     | 0x00                              |

| 16h-53h  | R/W | MFR_STR                              | MANSTR  | 00h                     | 0x00                              |

| 54h-91h  | R/W | PROD_STR                             | PRDSTR  | 00h                     | 0x00                              |

| 92h-Cfh  | R/W | SER_STR                              | SERSTR  | 00h                     | 0x00                              |

| D0h-F5h  | R/W | Reserved                             | N/A     | 00h                     | 0x00                              |

| F6h      | R/W | Boost_Up                             | BOOSTUP | 00h                     | 0x00                              |

| F7h      | R/W | Boost_7:5                            | BOOST75 | 00h                     | 0x00                              |

| F8h      | R/W | Boost_4:0                            | BOOST40 | 00h                     | 0x00                              |

| F9h      | R/W | Reserved                             | N/A     | 00h                     | 0x00                              |

| FAh      | R/W | Port Swap                            | PRTSP   | 00h                     | 0x00                              |

| FBh      | R/W | Port Remap 12                        | PRTR12  | 00h                     | 0x00                              |

| FCh      | R/W | Port Remap 34                        | PRTR34  | 00h                     | 0x00                              |

| FDh      | R/W | Port Remap 56                        | PRTR56  | 00h                     | 0x00                              |

## TABLE 7-1: INTERNAL DEFAULT, EEPROM AND SMBUS REGISTER MEMORY MAP

| Reg Addr | R/W | Register Name                                         | Abbr  | Internal<br>Default ROM | SMBus and<br>EEPROM POR<br>Values |

|----------|-----|-------------------------------------------------------|-------|-------------------------|-----------------------------------|

| FEh      | R/W | Port Remap 7                                          | PRTR7 | 00h                     | 0x00                              |

| FFh      | R/W | Status/Command<br><b>Note:</b> SMBus register<br>only | STCD  | 00h                     | 0x00                              |

## TABLE 7-1: INTERNAL DEFAULT, EEPROM AND SMBUS REGISTER MEMORY MAP

## 7.2.1.1 Register 00h: Vendor ID (LSB)

| Bit<br>Number | Bit Name | Description                                                                                                                                                                                                                                |

|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0           | VID_LSB  | Least Significant Byte of the Vendor ID. This is a 16-bit value that uniquely identifies the Vendor of the user device (assigned by USB-Interface Forum). This field is set by the OEM using either the SMBus or EEPROM interface options. |

## 7.2.1.2 Register 01h: Vendor ID (MSB)

| Bit<br>Number | Bit Name | Description                                                                                                                                                                                                                               |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0           | VID_MSB  | Most Significant Byte of the Vendor ID. This is a 16-bit value that uniquely identifies the Vendor of the user device (assigned by USB-Interface Forum). This field is set by the OEM using either the SMBus or EEPROM interface options. |

## 7.2.1.3 Register 02h: Product ID (LSB)

| Bit<br>Number | Bit Name | Description                                                                                                                                                                                                                                      |

|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0           | PID_LSB  | Least Significant Byte of the Product ID. This is a 16-bit value that the Vendor can assign that uniquely identifies this particular product (assigned by OEM). This field is set by the OEM using either the SMBus or EEPROM interface options. |

## 7.2.1.4 Register 03h: Product ID (MSB)

| Bit<br>Number | Bit Name | Description                                                                                                                                                                                                                                     |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0           | PID_MSB  | Most Significant Byte of the Product ID. This is a 16-bit value that the Vendor can assign that uniquely identifies this particular product (assigned by OEM). This field is set by the OEM using either the SMBus or EEPROM interface options. |

## 7.2.1.5 Register 04h: Device ID (LSB)

| Bit<br>Number | Bit Name | Description                                                                                                                                                                                               |

|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0           | DID_LSB  | Least Significant Byte of the Device ID. This is a 16-bit device release num-<br>ber in BCD format (assigned by OEM). This field is set by the OEM using<br>either the SMBus or EEPROM interface options. |

## 7.2.1.6 Register 05h: Device ID (MSB)

| Bit<br>Number | Bit Name | Description                                                                                                                                                                                      |

|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0           | DID_MSB  | Most Significant Byte of the Device ID. This is a 16-bit device release number in BCD format (assigned by OEM). This field is set by the OEM using either the SMBus or EEPROM interface options. |

## 7.2.1.7 Register 06h: CONFIG\_BYTE\_1

| Bit<br>Number | Bit Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |