Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **USB 2.0 Hi-Speed 3-Port Hub Controller**

#### PRODUCT FEATURES

**Datasheet**

#### **Highlights**

- Hub Controller IC with 3 downstream ports

- USB-IF Battery Charger revision 1.2 support on up & downstream ports (DCP, CDP, SDP)

- Battery charging support for Apple devices

- FlexConnect: Downstream port 1 able to swap with upstream port, allowing master capable devices to control other devices on the hub

- USB to I<sup>2</sup>C<sup>TM</sup> bridge endpoint support

- USB Link Power Management (LPM) support

- SUSPEND pin for remote wakeup indication to host

- Vendor Specific Messaging (VSM) support

- Enhanced OEM configuration options available through a single serial I<sup>2</sup>C<sup>TM</sup> EEPROM, OTP, or SMBus Slave Port

- 36-pin (6x6mm) SQFN, RoHS compliant package

- Footprint compatible with USB2513B

#### **Target Applications**

- LCD monitors and TVs

- Multi-function USB peripherals

- PC mother boards

- Set-top boxes, DVD players, DVR/PVR

- Printers and scanners

- PC media drive bay

- Portable hub boxes

- Mobile PC docking

- Embedded systems

#### **Additional Features**

- MultiTRAK<sup>TM</sup>

- Dedicated Transaction Translator per port

- PortMap

- Configurable port mapping and disable sequencing

- PortSwap

- Configurable differential intra-pair signal swapping

- PHYBoost<sup>TM</sup>

- Programmable USB transceiver drive strength for recovering signal integrity

- VariSense<sup>TM</sup>

- Programmable USB receiver sensitivity

- Low power operation

- Full Power Management with individual or ganged power control of each downstream port

- Built-in Self-Powered or Bus-Powered internal default settings provide flexibility in the quantity of USB expansion ports utilized without redesign

- Supports "Quad Page" configuration OTP flash

Four consecutive 200 byte configuration pages

- Fully integrated USB termination and Pull-up/Pulldown resistors

- On-chip Power On Reset (POR)

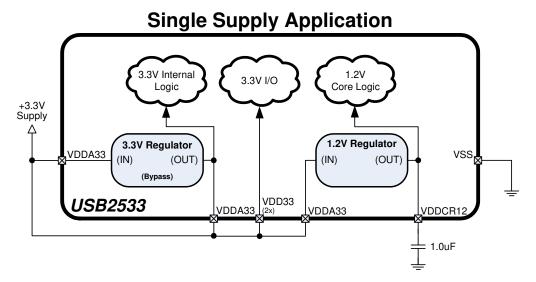

- Internal 3.3V and 1.2V voltage regulators

- On Board 24MHz Crystal Driver, Resonator, or External 24MHz clock input

- Environmental

- Commercial temperature range support (0°C to 70°C)

- Industrial temperature range support (-40°C to 85°C)

### Order Number(s):

| ORDER NUMBER       | TEMPERATURE<br>RANGE | PACKAGE TYPE                 |

|--------------------|----------------------|------------------------------|

| USB2533-1080AEN    | 0°C to +70°C         | 36-pin SQFN                  |

| USB2533-1080AEN-TR | 0°C to +70°C         | 36-pin SQFN<br>(Tape & Reel) |

| USB2533i-1080AEN   | -40°C to +85°C       | 36-pin SQFN                  |

| USB2533-1080AEN-TR | -40°C to +85°C       | 36-pin SQFN<br>(Tape & Reel) |

#### This product meets the halogen maximum concentration values per IEC61249-2-21

The table above represents valid part numbers at the time of printing and may not represent parts that are currently available. For the latest list of valid ordering numbers for this product, please contact the nearest sales office.

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## **Table of Contents**

| Chapter 1 General Description    7      1.1 Block Diagram    8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2 Acronyms and Definitions92.1 Acronyms92.2 Reference Documents9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Chapter 3 Pin Descriptions103.1 Pin Descriptions113.2 Pin Assignments193.3 Buffer Type Descriptions20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Chapter 4 Power Connections214.1 Integrated Power Regulators214.2 Power Connection Diagrams21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

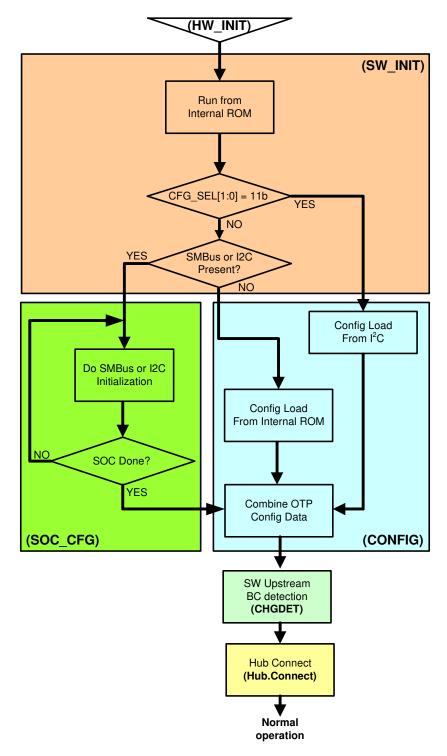

| Chapter 5 Modes of Operation       22         5.1 Boot Sequence       24         5.1.1 Standby Mode       24         5.1.2 Hardware Initialization Stage (HW_INIT)       24         5.1.3 Software Initialization Stage (SW_INIT)       24         5.1.4 SOC Configuration Stage (SOC_CFG)       24         5.1.5 Configuration Stage (CONFIG)       24         5.1.6 Battery Charger Detection Stage (CHGDET)       25         5.1.7 Hub Connect Stage (Hub.Connect)       25         5.1.8 Normal Mode       25                                                                                |

| Chapter 6 Device Configuration         26           6.1 Configuration Method Selection         26           6.2 Customer Accessible Functions         26           6.2.1 USB Accessible Functions         27           6.2.2 SMBus Accessible Functions         28           6.3 Device Configuration Straps         28           6.3.1 Non-Removable Device (NON_REM[1:0])         29           6.3.2 Configuration Select (CFG_SEL[1:0])         29           6.3.3 Downstream Battery Charging Enable (BC_EN[3:1])         29           6.3.4 Port Disable (PRT_DIS_Mx/PRT_DIS_Px)         30 |

| Chapter 7 Device Interfaces.       31         7.1 I2C Master Interface       31         7.1.1 I2C Message Format       31         7.1.2 Pull-Up Resistors for I2C       32         7.2 SMBus Slave Interface       32                                                                                                                                                                                                                                                                                                                                                                            |

| Chapter 8 Functional Descriptions       33         8.1 Battery Charger Detection & Charging       33         8.1.1 Upstream Battery Charger Detection       33                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### Datasheet

| Chapter 11 Datasheet Revision History 4         | 8  |

|-------------------------------------------------|----|

| Chapter 10 Package Outline4                     | 7  |

| 9.6.2 External Reference Clock (REFCLK)         | .6 |

| 9.6.1 Oscillator/Crystal                        |    |

| 9.6 Clock Specifications                        |    |

| 9.5.5 I2C Timing                                | 5  |

| 9.5.4 SMBus Timing                              |    |

| 9.5.3 USB Timing                                |    |

| 9.5.2 Reset and Configuration Strap Timing4     |    |

| 9.5.1 Power-On Configuration Strap Valid Timing |    |

| 9.4 DC Specifications                           |    |

| 9.3.2 Suspend / Standby                         |    |

| 9.3.1 Operational / Unconfigured                |    |

| 9.3 Power Consumption                           |    |

| 9.2 Operating Conditions**                      |    |

| 9.1 Absolute Maximum Ratings*                   |    |

| Chapter 9 Operational Characteristics4          |    |

| 3.6 High Speed Indicator (HS_IND)               | 9  |

| 8.5.2 Modified Resume Behavior                  |    |

| 8.5.1 Normal Resume Behavior                    |    |

| 3.5 Remote Wakeup Indicator (SUSP_IND)          |    |

| 3.4 Link Power Management (LPM)                 |    |

| 8.3.3 USB Bus Reset                             |    |

| 8.3.2 External Chip Reset (RESET_N)             | 6  |

| 8.3.1 Power-On Reset (POR)                      |    |

| 3.3 Resets                                      |    |

| 3.2 Flex Connect                                |    |

| 8.1.2 Downstream Battery Charging               |    |

|                                                 |    |

# **List of Figures**

| Figure 1.1  | System Block Diagram                      | . 8 |

|-------------|-------------------------------------------|-----|

| Figure 3.1  | 36-SQFN Pin Assignments                   | 10  |

| Figure 4.1  | Power Connections                         | 21  |

| Figure 5.1  | Hub Operational Mode Flowchart            | 23  |

| Figure 7.1  | I2C Sequential Access Write Format        | 31  |

| Figure 7.2  | I2C Sequential Access Read Format         | 32  |

| Figure 8.1  | Battery Charging External Power Supply    | 34  |

| Figure 9.1  | Supply Rise Time Model                    | 41  |

| Figure 9.2  | Power-On Configuration Strap Valid Timing | 44  |

| Figure 9.3  | RESET_N Configuration Strap Timing        | 45  |

| Figure 10.1 | 36-SQFN Package Drawing                   | 47  |

## **List of Tables**

| Table 3.1  | Pin Descriptions                                | 11 |

|------------|-------------------------------------------------|----|

| Table 3.2  | 36-SQFN Package Pin Assignments                 | 19 |

| Table 3.3  | Buffer Types                                    | 20 |

| Table 6.1  | Hub Configuration Selection                     | 26 |

| Table 6.2  | NON_REM[1:0] Configuration Definitions          | 29 |

| Table 6.3  | PRT_DIS_Mx/PRT_DIS_Px Configuration Definitions | 30 |

| Table 8.1  | Chargers Compatible with Upstream Detection     | 33 |

| Table 8.2  | Downstream Port Types                           | 35 |

| Table 8.3  | LPM State Definitions                           | 37 |

| Table 9.1  | Operational/Unconfigured Power Consumption      | 42 |

| Table 9.2  | Suspend/Standby Power Consumption               | 42 |

|            | DC Electrical Characteristics                   |    |

| Table 9.4  | Power-On Configuration Strap Valid Timing       | 44 |

| Table 9.5  | RESET_N Configuration Strap Timing              | 45 |

| Table 9.6  | Crystal Specifications                          | 46 |

| Table 11.1 | Revision History                                | 48 |

# **Chapter 1 General Description**

The USB2533 is a low-power, OEM configurable, MTT (Multi-Transaction Translator) USB 2.0 hub controller with 3 downstream ports and advanced features for embedded USB applications. The USB2533 is fully compliant with the USB 2.0 Specification, USB 2.0 Link Power Management Addendum and will attach to an upstream port as a Full-Speed hub or as a Full-/Hi-Speed hub. The 3-port hub supports Low-Speed, Full-Speed, and Hi-Speed (if operating as a Hi-Speed hub) downstream devices on all of the enabled downstream ports.

The USB2533 has been specifically optimized for embedded systems where high performance, and minimal BOM costs are critical design requirements. Standby mode power has been minimized and reference clock inputs can be aligned to the customer's specific application. Additionally, all required resistors on the USB ports are integrated into the hub, including all series termination and pull-up/pull-down resistors on the D+ and D- pins.

The USB2533 supports both upstream battery charger detection and downstream battery charging. The USB2533 integrated battery charger detection circuitry supports the USB-IF Battery Charging (BC1.2) detection method and most Apple devices. These circuits are used to detect the attachment and type of a USB charger and provide an interrupt output to indicate charger information is available to be read from the device's status registers via the serial interface. The USB2533 provides the battery charging handshake and supports the following USB-IF BC1.2 charging profiles:

- DCP: Dedicated Charging Port (Power brick with no data)

- CDP: Charging Downstream Port (1.5A with data)

- SDP: Standard Downstream Port (0.5A with data)

- Custom profiles loaded via SMBus or OTP

The USB2533 provides an additional USB endpoint dedicated for use as a USB to I<sup>2</sup>C interface, allowing external circuits or devices to be monitored, controlled, or configured via the USB interface. Additionally, the USB2533 includes many powerful and unique features such as:

**FlexConnect**, which provides flexible connectivity options. The USB2533's downstream port 1 can be swapped with the upstream port, allowing master capable devices to control other devices on the hub.

MultiTRAK<sup>™</sup> Technology, which utilizes a dedicated Transaction Translator (TT) per port to maintain consistent full-speed data throughput regardless of the number of active downstream connections. MultiTRAK<sup>™</sup> outperforms conventional USB 2.0 hubs with a single TT in USB full-speed data transfers.

**PortMap**, which provides flexible port mapping and disable sequences. The downstream ports of a USB2533 hub can be reordered or disabled in any sequence to support multiple platform designs with minimum effort. For any port that is disabled, the USB2533 hub controllers automatically reorder the remaining ports to match the USB host controller's port numbering scheme.

**PortSwap**, which adds per-port programmability to USB differential-pair pin locations. PortSwap allows direct alignment of USB signals (D+/D-) to connectors to avoid uneven trace length or crossing of the USB differential signals on the PCB.

**PHYBoost**, which provides programmable levels of Hi-Speed USB signal drive strength in the downstream port transceivers. PHYBoost attempts to restore USB signal integrity in a compromised system environment. The graphic on the right shows an example of Hi-Speed USB eye diagrams before and after PHYBoost signal integrity restoration.

**VariSense**, which controls the USB receiver sensitivity enabling programmable levels of USB signal receive sensitivity. This capability allows operation in a sub-optimal system environment, such as when a captive USB cable is used.

The USB2533 is available in commercial (0°C to +70°C) and industrial (-40°C to +85°C) temperature range versions.

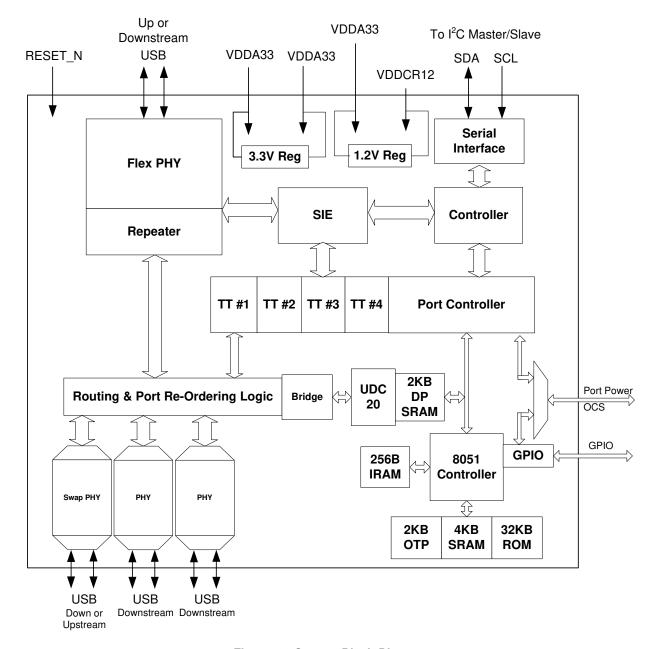

## 1.1 Block Diagram

Figure 1.1 details the internal block diagram of the USB2533.

Figure 1.1 System Block Diagram

# **Chapter 2 Acronyms and Definitions**

## 2.1 Acronyms

EOP: End of Packet

**EP:** Endpoint

FS: Full-Speed

**GPIO:** General Purpose I/O (that is input/output to/from the device)

HS: Hi-Speed

**HSOS:** High Speed Over Sampling

I<sup>2</sup>C<sup>®</sup>: Inter-Integrated Circuit

LS: Low-Speed

**OTP:** One Time Programmable

PCB: Printed Circuit Board

PCS: Physical Coding Sublayer

PHY: Physical Layer

SMBus: System Management Bus

UUID: Universally Unique IDentification

## 2.2 Reference Documents

- 1. UNICODE UTF-16LE For String Descriptors USB Engineering Change Notice, December 29th, 2004, http://www.usb.org

- 2. Universal Serial Bus Specification, Revision 2.0, April 27th, 2000, http://www.usb.org

- 3. Battery Charging Specification, Revision 1.2, Dec. 07, 2010, http://www.usb.org

- 4. \( \begin{aligned} \begin{aligned} 2C-Bus Specification, Version 1.1, \text{ http://www.nxp.com} \end{aligned} \)

- 5. System Management Bus Specification, Version 1.0, http://smbus.org/specs

# **Chapter 3 Pin Descriptions**

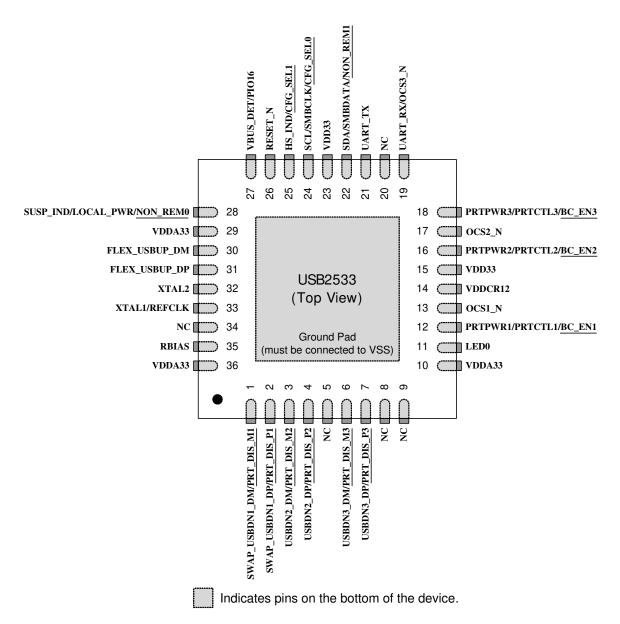

Figure 3.1 36-SQFN Pin Assignments

## 3.1 Pin Descriptions

This section provides a detailed description of each pin. The signals are arranged in functional groups according to their associated interface.

The "\_N" symbol in the signal name indicates that the active, or asserted, state occurs when the signal is at a low voltage level. For example, RESET\_N indicates that the reset signal is active low. When "\_N" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signals. The term assert, or assertion, indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation, indicates that a signal is inactive.

**Note:** The buffer type for each signal is indicated in the BUFFER TYPE column of Table 3.1. A description of the buffer types is provided in Section 3.3.

**Note:** Compatibility with the UCS100x family of USB port power controllers requires the UCS100x be connected on Port 1 of the USB2533. Additionally, both PRTPWR1 and OCS1\_N must be pulled high at Power-On Reset (POR).

**Table 3.1 Pin Descriptions**

| NUM PINS | NAME                                           | SYMBOL         | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                             |

|----------|------------------------------------------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                | USB/I          | HSIC INTERI    | FACES                                                                                                                                                                                                                                                                                   |

| 1        | Upstream<br>USB D+<br>(Flex Port 0)            | FLEX_USBUP_DP  | AIO            | Upstream USB Port 0 D+ data signal.  Note: The upstream Port 0 signals can be optionally swapped with the downstream Port 1 signals.                                                                                                                                                    |

| 1        | Upstream<br>USB D-<br>(Flex Port 0)            | FLEX_USBUP_DM  | AIO            | Upstream USB Port 0 D- data signal.  Note: The upstream Port 0 signals can be optionally swapped with the downstream Port 1 signals.                                                                                                                                                    |

|          | Downstream<br>USB D+<br>(Swap Port 1)          | SWAP_USBDN1_DP | AIO            | Downstream USB Port 1 D+ data signal.  Note: The downstream Port 1 signals can be optionally swapped with the upstream Port 0 signals.                                                                                                                                                  |

| 1        | Port 1 D+<br>Disable<br>Configuration<br>Strap | PRT_DIS_P1     | IS             | This strap is used in conjunction with PRT_DIS_M1 to disable USB Port 1.  0 = Port 1 D+ Enabled 1 = Port 1 D+ Disabled  Note: Both PRT_DIS_P1 and PRT_DIS_M1 must be tied to VDD33 at reset to disable the associated port.  See Note 3.4 for more information on configuration straps. |

Table 3.1 Pin Descriptions (continued)

| NUM PINS | NAME                                           | SYMBOL         | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                             |

|----------|------------------------------------------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Downstream<br>USB D-<br>(Swap Port 1)          | SWAP_USBDN1_DM | AIO            | Downstream USB Port 1 D- data signal.  Note: The downstream Port 1 signals can be optionally swapped with the upstream Port 0 signals.                                                                                                                                                  |

| 1        | Port 1 D-<br>Disable<br>Configuration<br>Strap | PRT DIS M1     | IS             | This strap is used in conjunction with PRT DIS P1 to disable USB Port 1.  0 = Port 1 D- Enabled 1 = Port 1 D- Disabled  Note: Both PRT DIS P1 and PRT DIS M1 must be tied to VDD33 at reset to disable the associated port.  See Note 3.4 for more information on configuration straps. |

|          | Downstream<br>USB D+<br>(Port 2)               | USBDN2_DP      | AIO            | Downstream USB Port 2 D+ data signal.                                                                                                                                                                                                                                                   |

| 1        | Port 2 D+<br>Disable<br>Configuration<br>Strap | PRT_DIS_P2     | IS             | This strap is used in conjunction with PRT_DIS_M2 to disable USB Port 2.  0 = Port 2 D+ Enabled 1 = Port 2 D+ Disabled  Note: Both PRT_DIS_P2 and PRT_DIS_M2 must be tied to VDD33 at reset to disable the associated port.  See Note 3.4 for more information on configuration straps. |

|          | Downstream<br>USB D-<br>(Port 2)               | USBDN2_DM      | AIO            | Downstream USB Port 2 D- data signal.                                                                                                                                                                                                                                                   |

| 1        | Port 2 D-<br>Disable<br>Configuration<br>Strap | PRT DIS M2     | IS             | This strap is used in conjunction with PRT DIS P2 to disable USB Port 2.  0 = Port 2 D- Enabled 1 = Port 2 D- Disabled  Note: Both PRT DIS P2 and PRT DIS M2 must be tied to VDD33 at reset to disable the associated port.  See Note 3.4 for more information on configuration straps. |

Table 3.1 Pin Descriptions (continued)

|          | T                                                   |                     | ı              |                                                                                                                                                                                                                                                                                         |

|----------|-----------------------------------------------------|---------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUM PINS | NAME                                                | SYMBOL              | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                             |

|          | Downstream<br>USB D+<br>(Port 3)                    | USBDN3_DP           | AIO            | Downstream USB Port 3 D+ data signal.                                                                                                                                                                                                                                                   |

| 1        | Port 3 D+<br>Disable<br>Configuration<br>Strap      | PRT_DIS_P3          | IS             | This strap is used in conjunction with PRT_DIS_M3 to disable USB Port 3.  0 = Port 3 D+ Enabled 1 = Port 3 D+ Disabled  Note: Both PRT_DIS_P3 and PRT_DIS_M3 must be tied to VDD33 at reset to disable the associated port.  See Note 3.4 for more information on configuration straps. |

|          | Downstream<br>USB D-<br>(Port 3)                    | USBDN3_DM           | AIO            | Downstream USB Port 3 D- data signal.                                                                                                                                                                                                                                                   |

| 1        | Port 3 D-<br>Disable<br>Configuration<br>Strap      | PRT DIS M3          | IS             | This strap is used in conjunction with PRT DIS P3 to disable USB Port 3.  0 = Port 3 D- Enabled 1 = Port 3 D- Disabled  Note: Both PRT DIS P3 and PRT DIS M3 must be tied to VDD33 at reset to disable the associated port.  See Note 3.4 for more information on configuration straps. |

|          |                                                     | I <sup>2</sup> C/SI | MBUS INTER     | RFACE                                                                                                                                                                                                                                                                                   |

|          | I <sup>2</sup> C Serial<br>Clock Input              | SCL                 | I_SMB          | I <sup>2</sup> C serial clock input                                                                                                                                                                                                                                                     |

|          | SMBus Clock                                         | SMBCLK              | I_SMB          | SMBus serial clock input                                                                                                                                                                                                                                                                |

| 1        | Configuration<br>Select 0<br>Configuration<br>Strap | CFG_SEL0            | I_SMB          | This strap is used in conjunction with <u>CFG SEL1</u> to set the hub configuration method. Refer to Section 6.3.2, "Configuration Select (CFG_SEL[1:0])," on page 29 for additional information.  See Note 3.4 for more information on configuration straps                            |

|          |                                                     |                     |                |                                                                                                                                                                                                                                                                                         |

Table 3.1 Pin Descriptions (continued)

| · · · ·  |                                                         |                        |                |                                                                                                                                                                                                                             |

|----------|---------------------------------------------------------|------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUM PINS | NAME                                                    | SYMBOL                 | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                 |

|          | I <sup>2</sup> C Serial<br>Data                         | SDA                    | IS/OD8         | I <sup>2</sup> C bidirectional serial data                                                                                                                                                                                  |

|          | SMBus Serial<br>Data                                    | SMBDATA                | IS/OD8         | SMBus bidirectional serial data                                                                                                                                                                                             |

| 1        | Non-<br>Removable<br>Device 1<br>Configuration<br>Strap | NON REM1<br>(Note 3.3) | IS             | This strap is used in conjunction with NON REMO to configure the downstream ports as non-removable devices. Refer to Section 6.3.1, "Non-Removable Device (NON_REM[1:0])," on page 29 for additional information.           |

|          |                                                         |                        |                | See Note 3.4 for more information on configuration straps.                                                                                                                                                                  |

|          |                                                         |                        | MISC.          |                                                                                                                                                                                                                             |

| 1        | Port 1 Over-<br>Current<br>Sense Input                  | OCS1_N                 | IS<br>(PU)     | This active-low signal is input from an external current monitor to indicate an over-current condition on USB Port 1.                                                                                                       |

| 1        | Port 2 Over-<br>Current<br>Sense Input                  | OCS2_N                 | IS<br>(PU)     | This active-low signal is input from an external current monitor to indicate an over-current condition on USB Port 2.                                                                                                       |

| 1        | UART<br>Receive Input                                   | UART_RX                | IS             | Internal UART receive input  Note: This is a 3.3V signal. For RS232 operation, an external 12V translator is required.                                                                                                      |

|          | Port 3 Over-<br>Current<br>Sense Input                  | OCS3_N                 | IS<br>(PU)     | This active-low signal is input from an external current monitor to indicate an over-current condition on USB Port 3.                                                                                                       |

| 1        | UART<br>Transmit<br>Output                              | UART_TX                | O8             | Internal UART transmit output  Note: This is a 3.3V signal. For RS232 operation, an external 12V driver is required.                                                                                                        |

| 1        | System Reset<br>Input                                   | RESET_N                | I_RST          | This active-low signal allows external hardware to reset the device.  Note: The active-low pulse must be at least 5us wide. Refer to Section 8.3.2, "External Chip Reset (RESET_N)," on page 36 for additional information. |

|          | Crystal Input                                           | XTAL1                  | ICLK           | External 24 MHz crystal input                                                                                                                                                                                               |

| 1        | Reference<br>Clock Input                                | REFCLK                 | ICLK           | Reference clock input. The device may be alternatively driven by a single-ended clock oscillator. When this method is used, XTAL2 should be left unconnected.                                                               |

| 1        | Crystal<br>Output                                       | XTAL2                  | OCLK           | External 24 MHz crystal output                                                                                                                                                                                              |

**Table 3.1 Pin Descriptions (continued)**

| NUM PINS | NAME                                         | SYMBOL   | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|----------------------------------------------|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | External USB<br>Transceiver<br>Bias Resistor | RBIAS    | Al             | A 12.0k $\Omega$ (+/- 1%) resistor is attached from ground to this pin to set the transceiver's internal bias settings.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1        | LED 0 Output                                 | LED0     | O8             | General purpose LED 0 output that is configurable to blink or "breathe" at various rates.  Note: LED0 must be enabled via the Protouch configuration tool.                                                                                                                                                                                                                                                                                                                                                                                               |

| 1        | Detect<br>Upstream<br>VBUS Power             | VBUS_DET | IS             | Detects state of upstream bus power. When designing a detachable hub, this pin must be connected to the VBUS power pin of the upstream USB port through a resistor divider ( $50k\Omega$ by $100k\Omega$ ) to provide 3.3V. For self-powered applications with a permanently attached host, this pin must be connected to either 3.3V or 5.0V through a resistor divider to provide 3.3V. In embedded applications, VBUS_DET may be controlled (toggled) when the host desires to renegotiate a connection without requiring a full reset of the device. |

Table 3.1 Pin Descriptions (continued)

|          |                                                         |                        | BUFFER |                                                                                                                                                                                                                   |

|----------|---------------------------------------------------------|------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUM PINS | NAME                                                    | SYMBOL                 | TYPE   | DESCRIPTION                                                                                                                                                                                                       |

|          | Remote<br>Wakeup<br>Indicator                           | SUSP_IND               | OD8    | Configurable sideband signal used to indicate Suspend status (default) or Remote Wakeup events to the Host.                                                                                                       |

|          |                                                         |                        |        | Suspend Indicator (default configuration): 0 = Unconfigured, or configured and in USB suspend mode 1 = Device is configured and is active (i.e., not in suspend)                                                  |

|          |                                                         |                        |        | For Remote Wakeup Indicator mode:<br>Refer to Section 8.5, "Remote Wakeup Indicator<br>(SUSP_IND)," on page 37.                                                                                                   |

|          |                                                         |                        |        | Refer to Section 6.3.1, "Non-Removable Device (NON_REM[1:0])," on page 29 for information on LED polarity when using this signal.                                                                                 |

| 1        | Local Power<br>Detect                                   | LOCAL_PWR              | IS     | Detects the availability of a local self-power source.                                                                                                                                                            |

|          |                                                         |                        |        | 0 = Self/local power source is NOT available.<br>(i.e., device must obtain all power from upstream<br>USB VBUS)<br>1 = Self/local power source is available                                                       |

|          |                                                         |                        |        | See Note 3.2 for more information on this pin.                                                                                                                                                                    |

|          | Non-<br>Removable<br>Device 0<br>Configuration<br>Strap | NON REMO<br>(Note 3.3) | IS     | This strap is used in conjunction with NON REM1 to configure the downstream ports as non-removable devices. Refer to Section 6.3.1, "Non-Removable Device (NON_REM[1:0])," on page 29 for additional information. |

|          |                                                         |                        |        | See Note 3.4 for more information on configuration straps.                                                                                                                                                        |

|          | High Speed<br>Indicator                                 | HS_IND                 | O8     | Indicates a high speed connection on the upstream port. The active state of the LED will be determined as follows:                                                                                                |

|          |                                                         |                        |        | If CFG_SEL1 = 0, HS_IND is active high. If CFG_SEL1 = 1, HS_IND is active low.                                                                                                                                    |

| 1        |                                                         |                        |        | Asserted = hub is connected at high speed<br>Negated = Hub is connected at full speed                                                                                                                             |

|          | Configuration<br>Select 1<br>Configuration<br>Strap     | CFG_SEL1               | IS     | This strap is used in conjunction with <u>CFG SEL0</u> to set the hub configuration method. Refer to Section 6.3.2, "Configuration Select (CFG_SEL[1:0])," on page 29 for additional information.                 |

|          |                                                         |                        |        | See Note 3.4 for more information on configuration straps.                                                                                                                                                        |

Table 3.1 Pin Descriptions (continued)

| NUM PINS | NAME                                                 | SYMBOL  | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                |

|----------|------------------------------------------------------|---------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Port 1 Power<br>Output                               | PRTPWR1 | O8             | Enables power to a downstream USB device attached to Port 1.                                                                                                                                                               |

|          |                                                      |         |                | 0 = Power disabled on downstream Port 1<br>1 = Power enabled on downstream Port 1                                                                                                                                          |

| 1        | Port 1 Control                                       | PRTCTL1 | OD8/IS<br>(PU) | When configured as PRTCTL1, this pin functions as both the Port 1 power enable output (PRTPWR1) and the Port 1 over-current sense input (OCS1_N). Refer to the PRTPWR1 and OCS1_N descriptions for additional information. |

| ·        | Port 1 Battery<br>Charging<br>Configuration<br>Strap | BC EN1  | IS             | This strap is used to indicate support of the battery charging protocol on Port 1. Enabling battery charging support allows a device on the port to draw currents per the USB battery charging specification.              |

|          |                                                      |         |                | 0 = Battery charging is not supported on Port 1<br>1 = Battery charging is supported on Port 1                                                                                                                             |

|          |                                                      |         |                | See Note 3.4 for more information on configuration straps.                                                                                                                                                                 |

|          | Port 2 Power<br>Output                               | PRTPWR2 | O8             | Enables power to a downstream USB device attached to Port 2.                                                                                                                                                               |

|          |                                                      |         |                | 0 = Power disabled on downstream Port 2<br>1 = Power enabled on downstream Port 2                                                                                                                                          |

| 1        | Port 2 Control                                       | PRTCTL2 | OD8/IS<br>(PU) | When configured as PRTCTL2, this pin functions as both the Port 2 power enable output (PRTPWR2) and the Port 2 over-current sense input (OCS2_N). Refer to the PRTPWR2 and OCS2_N descriptions for additional information. |

|          | Port 2 Battery<br>Charging<br>Configuration<br>Strap | BC EN2  | IS             | This strap is used to indicate support of the battery charging protocol on Port 2. Enabling battery charging support allows a device on the port to draw currents per the USB battery charging specification.              |

|          |                                                      |         |                | 0 = Battery charging is not supported on Port 2<br>1 = Battery charging is supported on Port 2                                                                                                                             |

|          |                                                      |         |                | See Note 3.4 for more information on configuration straps.                                                                                                                                                                 |

**Table 3.1 Pin Descriptions (continued)**

| NUM PINS                                   | NAME                                                 | SYMBOL  | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                |  |  |  |

|--------------------------------------------|------------------------------------------------------|---------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                                          | Port 3 Power<br>Output                               | PRTPWR3 | O8             | Enables power to a downstream USB device attached to Port 3.                                                                                                                                                                                                               |  |  |  |

|                                            |                                                      |         |                | 0 = Power disabled on downstream Port 3<br>1 = Power enabled on downstream Port 3                                                                                                                                                                                          |  |  |  |

|                                            | Port 3 Control                                       | PRTCTL3 | OD8/IS<br>(PU) | When configured as PRTCTL3, this pin functions as both the Port 3 power enable output (PRTPWR3) and the Port 3 over-current sense input (OCS3_N). Refer to the PRTPWR3 and OCS3_N descriptions for additional information.                                                 |  |  |  |

|                                            | Port 3 Battery<br>Charging<br>Configuration<br>Strap | BC EN3  | IS             | This strap is used to indicate support of the battery charging protocol on Port 3. Enabling battery charging support allows a device on the port to draw currents per the USB battery charging specification.                                                              |  |  |  |

|                                            |                                                      |         |                | 0 = Battery charging is not supported on Port 3<br>1 = Battery charging is supported on Port 3                                                                                                                                                                             |  |  |  |

|                                            |                                                      |         |                | See Note 3.4 for more information on configuration straps.                                                                                                                                                                                                                 |  |  |  |

| 5                                          | No Connect                                           | NC      | -              | These pins must be left floating for normal device operation.                                                                                                                                                                                                              |  |  |  |

|                                            | POWER                                                |         |                |                                                                                                                                                                                                                                                                            |  |  |  |

| 3                                          | +3.3V Analog<br>Power Supply                         | VDDA33  | Р              | +3.3V analog power supply. Refer to Chapter 4, "Power Connections," on page 21 for power connection information.                                                                                                                                                           |  |  |  |

| 2                                          | +3.3V Power<br>Supply                                | VDD33   | Р              | +3.3V power supply. These pins must be connected to VDDA33. Refer to Chapter 4, "Power Connections," on page 21 for power connection information.                                                                                                                          |  |  |  |

| 1                                          | +1.2V Core<br>Power Supply                           | VDDCR12 | Р              | +1.2V core power supply. A 1.0 $\mu$ F (<1 $\Omega$ ESR) capacitor to ground is required for regulator stability. The capacitor should be placed as close as possible to the device. Refer to Chapter 4, "Power Connections," on page 21 for power connection information. |  |  |  |

| Exposed Pad on package bottom (Figure 3.1) | Ground                                               | VSS     | Р              | Common ground. This exposed pad must be connected to the ground plane with a via array.                                                                                                                                                                                    |  |  |  |

Note 3.2 The LOCAL\_PWR pin is sampled during the configuration state, immediately after negation of reset, to determine whether the device is bus-powered or self-powered. When configuration is complete, the latched value will not change until the next reset assertion. To enable dynamic local power switching, the DYNAMIC\_POWER register at location 0x4134 must be programmed with 0x41. If dynamic power switching is not required, the DYNAMIC\_POWER register should be left at the default value of 0xC1. Programming may

- be performed through the SMBus interface, or permanently via OTP. Refer to the Protouch MPT User Manual for additional information.

- Note 3.3 If using the local power detect function (LOCAL\_PWR pin), the NON\_REM[1:0] configuration straps cannot be used to configure the non-removable state of the USB ports. In this case, the non-removable state of the ports must be configured in internal device registers via the Protouch tool or SMBus.

- Note 3.4 Configuration strap values are latched on Power-On Reset (POR) and the rising edge of RESET\_N (external chip reset). Configuration straps are identified by an underlined symbol name. Signals that function as configuration straps must be augmented with an external resistor when connected to a load. Refer to Section 6.3, "Device Configuration Straps," on page 28 for additional information.

## 3.2 Pin Assignments

Table 3.2 36-SQFN Package Pin Assignments

| PIN NAME                     | PIN<br>NUM                                                                                                                                                                                                                                             | PIN NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWAP_USBDN1_DM/PRT_DIS_M1    | 19                                                                                                                                                                                                                                                     | UART_RX/OCS3_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SWAP_USBDN1_DP/PRT_DIS_P1    | 20                                                                                                                                                                                                                                                     | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| USBDN2_DM/PRT_DIS_M2         | 21                                                                                                                                                                                                                                                     | UART_TX/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| USBDN2_DP/ <u>PRT_DIS_P2</u> | 22                                                                                                                                                                                                                                                     | SDA/SMBDATA/ <u>NON_REM1</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| NC                           | 23                                                                                                                                                                                                                                                     | VDD33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| USBDN3_DM/PRT_DIS_M3         | 24                                                                                                                                                                                                                                                     | SCL/SMBCLK/ <u>CFG_SEL0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| USBDN3_DP/ <u>PRT_DIS_P3</u> | 25                                                                                                                                                                                                                                                     | HS_IND/ <u>CFG_SEL1</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NC                           | 26                                                                                                                                                                                                                                                     | RESET_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NC                           | 27                                                                                                                                                                                                                                                     | VBUS_DET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VDDA33                       | 28                                                                                                                                                                                                                                                     | SUSP_IND/LOCAL_PWR/ <u>NON_REM0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LED0                         | 29                                                                                                                                                                                                                                                     | VDDA33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PRTPWR1/PRTCTL1/BC_EN1       | 30                                                                                                                                                                                                                                                     | FLEX_USBUP_DM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OCS1_N                       | 31                                                                                                                                                                                                                                                     | FLEX_USBUP_DP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDDCR12                      | 32                                                                                                                                                                                                                                                     | XTAL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VDD33                        | 33                                                                                                                                                                                                                                                     | XTAL1/REFCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PRTPWR2/PRTCTL2/BC_EN2       | 34                                                                                                                                                                                                                                                     | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OCS2_N                       | 35                                                                                                                                                                                                                                                     | RBIAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PRTPWR3/PRTCTL3/BC_EN3       | 36                                                                                                                                                                                                                                                     | VDDA33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                              | SWAP_USBDN1_DM/PRT_DIS_M1  SWAP_USBDN1_DP/PRT_DIS_P1  USBDN2_DM/PRT_DIS_M2  USBDN2_DP/PRT_DIS_P2  NC  USBDN3_DM/PRT_DIS_M3  USBDN3_DP/PRT_DIS_P3  NC  NC  VDDA33  LED0  PRTPWR1/PRTCTL1/BC_EN1  OCS1_N  VDDCR12  VDD33  PRTPWR2/PRTCTL2/BC_EN2  OCS2_N | PIN NAME         NUM           SWAP_USBDN1_DM/PRT_DIS_M1         19           SWAP_USBDN1_DP/PRT_DIS_P1         20           USBDN2_DM/PRT_DIS_M2         21           USBDN2_DP/PRT_DIS_P2         22           NC         23           USBDN3_DM/PRT_DIS_M3         24           USBDN3_DP/PRT_DIS_P3         25           NC         26           NC         27           VDDA33         28           LED0         29           PRTPWR1/PRTCTL1/BC_EN1         30           OCS1_N         31           VDDCR12         32           VDD33         33           PRTPWR2/PRTCTL2/BC_EN2         34           OCS2_N         35 |

# 3.3 Buffer Type Descriptions

**Table 3.3 Buffer Types**

| BUFFER TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IS          | Schmitt-triggered input                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| I_RST       | Reset Input                                                                                                                                                                                                                                                                                                                                                                                      |  |  |