# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 4th Generation USB 2.0 Flash Media Controller with Integrated Card Power FETs & HS Hub

#### **Hub Controller**

- Provides Three USB 2.0 Downstream Ports via internal USB 2.0 Hub

- Multi Transaction Translator for FS/LS devices attached

#### **Flash Media Controller**

- Complete System Solution for interfacing Smart-Media<sup>TM</sup> (SM) or xD Picture Card<sup>TM</sup> (xD)<sup>1</sup>, Memory Stick<sup>TM</sup> (MS), High Speed Memory Stick (HSMS), Memory Stick PRO (MSPRO), MS Duo<sup>TM</sup>, Secure Digital (SD), Mini-Secure Digital (Mini-SD), TransFlash (SD), MultiMediaCard<sup>TM</sup> (MMC), Reduced Size MultiMediaCard (RS-MMC), NAND Flash, Compact Flash<sup>TM</sup> (CF) and CF Ultra<sup>TM</sup> I & II, and CF form-factor ATA hard drives to USB 2.0 bus

- Supports USB Bulk Only Mass Storage Compliant Bootable BIOS

- Support for simultaneous operation of all above devices. (only one at a time of each of the following groups supported: CF or ATA drive, SM or XD or NAND, SD or MMC)

- On-Chip 4-Bit High Speed Memory Stick and MS PRO Hardware Circuitry

- On-Chip firmware reads and writes High Speed Memory Stick and MS PRO

- 1-bit ECC correction performed in hardware for maximum efficiency

- Hardware support for SD Security Command Extensions

- 3.3 Volt I/O with 5V input tolerance on VBUS, Port Power and Over-Current Sense pins

- On-chip power FETs for supplying flash media card power with minimum board components

- 8051 8 bit microprocessor

- Provides low speed control functions

- 30 MHz execution speed at 4 cycles per instruction average

- 12K Bytes of internal SRAM for general purpose scratchpad

- 768 Bytes of internal SRAM for general purpose scratchpad or program execution while re-flashing external ROM

- Double Buffered Bulk Endpoint

- Bi-directional 512 Byte Buffer for Bulk Endpoint

- 64 Byte RX Control Endpoint Buffer

- 64 Byte TX Control Endpoint Buffer

- Internal Program Memory Interface

64K Byte Internal Code Space

- On Board 24MHz Crystal Driver Circuit

- Can be clocked by an external 24MHz source

- On-Chip 1.8V Regulator for Low Power Core Operation

- Internal PLL for 480MHz USB 2.0 Sampling, Configurable MCU clock

- 11 GPIOs for special function use: LED indicators, button inputs, power control to memory devices, etc.

- Inputs capable of generating interrupts with either edge sensitivity

- Configuration of Hub and Flash Media features controlled either by internal defaults or via single external EEPROM. User configurable features:

- Full or Partial Card compliance checking

- LUN configuration and assignment

- Write Protect Polarity

- Cover Switch operation for xD compliance

- Inquiry Command operation

- SD Write Protect operation

- Older CF card support

- Force USB 1.1 reporting

- Internal or External Power FET operation

- Compatible with Microsoft WinXP, WinME, Win2K SP3&4, Apple OS10 and Linux Multi-LUN Mass Storage Class Drivers

- Win2K, Win98/98SE and Apple OS8.6 and OS9 Multi-LUN Mass Storage Class Drivers are available from Microchip

- 128-Pin TQFP Package (1.0mm height, 14mm x14mm footprint); RoHS compliant package also available

<sup>1.</sup>xD Picture Card not applicable to USB2601

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

- To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **Table of Contents**

# 1.0 INTRODUCTION

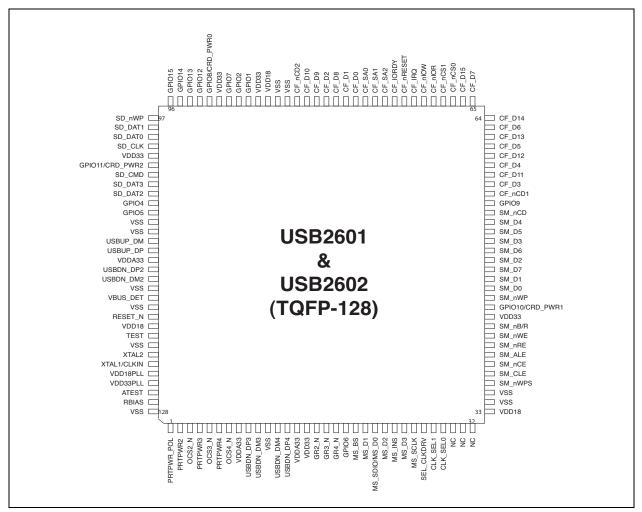

The USB2601/USB2602 is an Integrated "combo" High-Speed USB hub and Flash Media Controller. The Flash media controller permanently resides on Port 1 of the Integrated USB hub.

### 1.1 High-Speed Hub

The integrated Microchip Hub is fully compliant with the USB 2.0 Specification and will attach to a USB host as a Full-Speed Hub or as a Full-/High-Speed Hub. The Hub supports Low-Speed, Full-Speed, and High-Speed (if operating as a High-Speed Hub) downstream devices on all of the enabled downstream ports.

A dedicated Transaction Translator (TT) is available for each downstream facing port. This architecture ensures maximum USB throughput for each connected device when operating with mixed-speed peripherals.

The Hub works with an external USB power distribution switch device to control  $V_{BUS}$  switching to downstream ports, and to limit current and sense over-current conditions.

All required resistors on the USB ports are integrated into the Hub. This includes all series termination resistors on D+ and D– pins and all required pull-down and pull-up resistors on D+ and D– pins. The over-current sense inputs for the downstream facing ports have internal pull-up resistors.

Throughout this document the upstream facing port of the hub will be referred to as the upstream port, and the downstream facing ports will be called the downstream ports.

Three externally available ports are available for general USB device connectivity.

#### 1.2 Flash Media Controller

The Bulk Only Mass Storage Class Peripheral Controller intended for supporting CompactFlash (CF and CF Ultra I/II) in True IDE Mode only, SmartMedia (SM) and xD cards, Memory Stick (MS), Memory Stick DUO (MSDUO) and Memory Stick Pro (MSPRO), Secure Digital (SD), and MultiMediaCard (MMC) flash memory devices. It provides a single chip solution for the most popular flash memory cards in the market.

The device consists of buffers, Fast 8051 microprocessor with expanded scratchpad, and program SRAM, and CF, MS, SM and SD controllers. The SD controller supports both SD and MMC devices. SM controller supports both SM and xD cards.

12K bytes of scratchpad SRAM and 768 Bytes of program SRAM are also provided.

Eleven GPIO pins are provided for indicators, external serial EEPROM for OEM ID and system configuration information, and other special functions.

Internal power FETs are provided to directly supply power to the xD/SM, MMC/SD and MS/MSPro cards.

The internal ROM program is capable of implementing any combination of single or multi-LUN CF/SD/MMC/SM/MS reader functions with individual card power control and activity indication. Microchip also provides licenses\*\* for Win98 and Win2K drivers and setup utilities. Note: Please check with Microchip for precise features and capabilities for the current ROM code release.

#### 1.3 Acronyms

- SM: SmartMedia

- SMC: SmartMedia Controller

- FM: Flash Media

- FMC: Flash Media Controller

- CF: CompactFlash

- CFC: CompactFlash Controller

- SD: Secure Digital

- SDC: Secure Digital Controller

- MMC: MultiMediaCard

- MS: Memory Stick

- MSC: Memory Stick Controller

- **TPC:** Transport Protocol Code.

- **ECC:** Error Checking and Correcting

- **CRC:** Cyclic Redundancy Checking

#### 1.4 Reference Documents

- 1. SmartMedia<sup>TM</sup> Electrical Specification Version 1.30

- 2. SmartMedia<sup>TM</sup> Physical Format Specifications Version 1.30

- 3. SmartMedia<sup>TM</sup> Logical Format Specifications Version 1.20

- 4. SMIL (SmartMedia Interface Library) Software Edition Version 1.00, Toshiba Corporation, 01, July, 2000

- 5. SMIL (SmartMedia Interface Library) Hardware Edition Version 1.00, Toshiba Corporation, 01, July, 2000

- 6. MultiMediaCard System Specification Version 2.2

- 7. SD Memory Card Specifications, Part 1, Physical Layer Specification Version 1.10, April 2003, SD Group

- 8. SD Memory Card Specifications, Part 2, File System Specification Version 1.01, April 15<sup>th</sup>, 2001, SD Group

- 9. SD Memory Card Specifications, Part 3, Security Specification Version 1.01, April 15<sup>th</sup>, 2001, SD Group

- 10. SD Card Specification, Part E1, Secure Digital Input/Output (SDIO) card Specification, Version 1.00, October 2001, SD Group

- 11. Memory Stick Standard Excerpt from Format Specification v1.3, July, 2000, Sony Corporation.

- 12. Memory Stick Standard Format Specifications Version 2.0 (Memory Stick PRO) Tentative Release 0.81, February, 2002

- 13. CompactFlash Specification Rev. 1.4

- 14. CF+ & CF Specification Rev. ATA-5 Draft 0.2

- 15. Universal Serial Bus Specification Rev. 2.0

- 16. Samsung K9K2G08Q0M Data Sheet

- 17. xD Picture Card, Card Specification Version 1.10 (Jan 31, 2004)

- 18. xD Picture Card, Format Specification Version 1.10 (Jan 31, 2004)

- 19. xD Picture Card, Host Guideline Version 1.10 (Jan 31, 2004)

- 20. xD Picture Card, Compliance Guideline Version 1.10 (Jan 31, 2004)

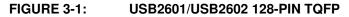

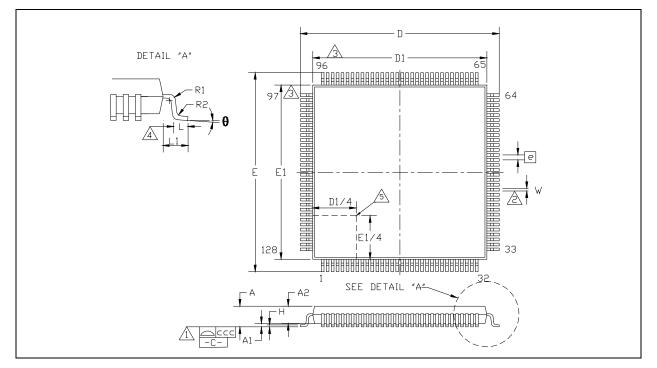

## 2.0 PIN TABLE

### 2.1 128-Pin TQFP Package

#### TABLE 2-1: USB2601/USB2602 128-PIN TQFP PACKAGE

|                 | UPSTREAM USB 2.0 IN | ITERFACE (3 PINS) |            |

|-----------------|---------------------|-------------------|------------|

| USBUP_DP        | USBUP_DM            | VBUS_DET          |            |

|                 | 3-PORT USB 2.0 INTE | ERFACE (16 PINS)  |            |

| USBDN_DP2       | USBDN_DM2           | USBDN_DP3         | USBDN_DM3  |

| USBDN_DP4       | USBDN_DM4           | PRTPWR2           | PRTPWR3    |

| PRTPWR4         | OCS2_N              | OCS4_N            |            |

| GR2_N           | GR3_N               | GR4_N             | PRTPWR_POL |

|                 | CompactFlash INTE   | RFACE (28 Pins)   |            |

| CF_D0           | CF_D1               | CF_D2             | CF_D3      |

| CF_D4           | CF_D5               | CF_D6             | CF_D7      |

| CF_D8           | CF_D9               | CF_D10            | CF_D11     |

| CF_D12          | CF_D13              | CF_D14            | CF_D15     |

| CF_nIOR         | CF_nIOW             | CF_IRQ            | CF_nRESET  |

| CF_IORDY        | CF_nCS0             | CF_nCS1           | CF_SA0     |

| CF_SA1          | CF_SA2              | CF_nCD1           | CF_nCD2    |

|                 | SmartMedia INTER    | FACE (17 Pins)    |            |

| SM_D0           | SM_D1               | SM_D2             | SM_D3      |

| SM_D4           | SM_D5               | SM_D6             | SM_D7      |

| SM_ALE          | SM_CLE              | SM_nRE            | SM_nWE     |

| SM_nWP          | SM_nB/R             | SM_nCE            | SM_nCD     |

| SM_nWPS         |                     |                   |            |

|                 | Memory Stick INTE   | RFACE (7 Pins)    |            |

| MS_BS           | MS_SDIO/MS_D0       | MS_SCLK           | MS_INS     |

| MS_D1           | MS_D2               | MS_D3             |            |

|                 | SD INTERFAC         | E (7 Pins)        |            |

| SD_CMD SD_CLK   |                     | SD_DAT0           | SD_DAT1    |

| SD_DAT2         | SD_DAT3             | SD_nWP            |            |

|                 | MISC (23            | Pins)             |            |

| GPIO1           | GPIO2               | GPIO4             | GPIO5      |

| GPIO6           | GPIO7               | GPIO8/CRD_PWR0    | GPIO9      |

| GPIO10/CRD_PWR1 | GPIO11/CRD_PWR2     | GPIO12            | GPIO13     |

| GPIO14          | GPIO15              | TEST              | RESET_N    |

| ATEST           | RBIAS               | XTAL1/CLKIN       | XTAL2      |

| CLK_SEL0        | CLK_SEL1            | SEL_CLKDRV        |            |

|                 | ANALOG POW          | ER (5 Pins)       |            |

| (3)VDDA33       | VDD33PLL            | VDD18PLL          |            |

|                 | DIGITAL, POWER & G  | ROUND (22 Pins)   |            |

| (5)VDD33        | (11)VSS             | (3)VDD18          | (3)NC      |

#### 2.2 128-Pin List Table

| Pin<br># | Name              | МА | Pin<br># | Name                | МА | Pin # | Name               | МА | Pin # | Name                | MA |

|----------|-------------------|----|----------|---------------------|----|-------|--------------------|----|-------|---------------------|----|

| 1        | PRTPWR_P<br>OL    | -  | 33       | VDD18               | -  | 65    | CF_D7              | 8  | 97    | SD_nWP              | -  |

| 2        | PRTPWR2           | 12 | 34       | VSS                 | -  | 66    | CF_D15             | 8  | 98    | SD_DAT1             | 8  |

| 3        | OCS2_N            | -  | 35       | VSS                 | -  | 67    | CF_nCS0            | 8  | 99    | SD_DAT0             | 8  |

| 4        | PRTPWR3           | 12 | 36       | SM_nWPS             | -  | 68    | CF_nCS1            | 8  | 100   | SD_CLK              | 8  |

| 5        | OCS3_N            | -  | 37       | SM_CLE              | 8  | 69    | CF_nIOR            | 8  | 101   | VDD33               | I  |

| 6        | PRTPWR4           | 12 | 38       | SM_nCE              | 8  | 70    | CF_nIOW            | 8  | 102   | GPIO11/<br>CRD_PWR2 | -  |

| 7        | OCS4_N            | -  | 39       | SM_ALE              | 8  | 71    | CF_IRQ             | 8  | 103   | SD_CMD              | 8  |

| 8        | VDDA33            | -  | 40       | SM_nRE              | 8  | 72    | CF_nRESET          | 8  | 104   | SD_DAT3             | 8  |

| 9        | USBDN_DP<br>3     |    | 41       | SM_nWE              | 8  | 73    | CF_IORDY           | 8  | 105   | SD_DAT2             | 8  |

| 10       | USBDN_DM<br>3     | -  | 42       | SM_nB/R             | -  | 74    | CF_SA2             | 8  | 106   | GPIO4               | 8  |

| 11       | VSS               | -  | 43       | VDD33               | -  | 75    | CF_SA1             | 8  | 107   | GPIO5               | 8  |

| 12       | USBDN_DM<br>4     | -  | 44       | GPIO10/<br>CRD_PWR1 | -  | 76    | CF_SA0             | 8  | 108   | VSS                 | -  |

| 13       | USBDN_DP<br>4     | -  | 45       | SM_nWP              | 8  | 77    | CF_D0              | 8  | 109   | VSS                 | -  |

| 14       | VDDA33            | -  | 46       | SM_D0               | 8  | 78    | CF_D1              | 8  | 110   | USBUP_DM            | I  |

| 15       | VDD33             | -  | 47       | SM_D1               | 8  | 79    | CF_D8              | 8  | 111   | USBUP_DP            | I  |

| 16       | GR2_N             | 8  | 48       | SM_D7               | 8  | 80    | CF_D2              | 8  | 112   | VDDA33              | -  |

| 17       | GR3_N             | 8  | 49       | SM_D2               | 8  | 81    | CF_D9              | 8  | 113   | USBDN_DP2           | -  |

| 18       | GR4_N             | 8  | 50       | SM_D6               | 8  | 82    | CF_D10             | 8  | 114   | USBDN_DM2           | -  |

| 19       | GPIO6             | 8  | 51       | SM_D3               | 8  | 83    | CF_nCD2            | -  | 115   | VSS                 | -  |

| 20       | MS_BS             | 8  | 52       | SM_D5               | 8  | 84    | VSS                | -  | 116   | VBUS_<br>DET        | 12 |

| 21       | MS_D1             | 8  | 53       | SM_D4               | 8  | 85    | VSS                | -  | 117   | VSS                 | -  |

| 22       | MS_SDIO/M<br>S_D0 | 8  | 54       | SM_nCD              | -  | 86    | VDD18              | -  | 118   | RESET_N             | -  |

| 23       | MS_D2             | 8  | 55       | GPIO9               | 8  | 87    | VDD33              | -  | 119   | VDD18               | -  |

| 24       | MS_INS            | -  | 56       | CF_nCD1             | -  | 88    | GPIO1              | 8  | 120   | TEST                | -  |

| 25       | MS_D3             | 8  | 57       | CF_D3               | 8  | 89    | GPIO2              | 8  | 121   | VSS                 | -  |

| 26       | MS_<br>SCLK       | 8  | 58       | CF_D11              | 8  | 90    | GPIO7              | 8  | 122   | XTAL2               | -  |

| 27       | SEL_CLKDR<br>V    | -  | 59       | CF_D4               | 8  | 91    | VDD33              | -  | 123   | XTAL1/<br>CLKIN     | -  |

| 28       | CLK_SEL1          | -  | 60       | CF_D12              | 8  | 92    | GPIO8/<br>CRD_PWR0 | -  | 124   | VDD18PLL            | -  |

| 29       | CLK_SEL0          | -  | 61       | CF_D5               | 8  | 93    | GPIO12             | 8  | 125   | VDD33PLL            | -  |

| 30       | NC                | -  | 62       | CF_D13              | 8  | 94    | GPIO13             | 8  | 126   | ATEST               | -  |

| 31       | NC                | -  | 63       | CF_D6               | 8  | 95    | GPIO14             | 8  | 127   | RBIAS               | -  |

| 32       | NC                | -  | 64       | CF_D14              | 8  | 96    | GPIO15             | 8  | 128   | VSS                 | -  |

TABLE 2-2: USB2601/USB2602 128-PIN TQFP

- Note 1: RBIAS is connected to the Analog Ground plane VSS via a resistor.

- 2: When the internal 1.8V regulators are enabled, VDD18 (Pin 86) & VDD18PLL (Pin 124), MUST have a 10uf +/- 20%, (equivalent series resistance (ESR) <0.1ohm) bypass capacitor to VSS. These capacitors must be as close to the pins as possible.

# 3.0 PIN CONFIGURATION

# 4.0 BLOCK DIAGRAM

FIGURE 4-1: USB2601/USB2602 BLOCK DIAGRAM

# 5.0 PIN DESCRIPTIONS

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface.

The "n" or "\_N" symbol in the signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "n" is not present before the signal name (or "\_N" after the signal name), the signal is asserted when at the high voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signal. The term assert, or assertion indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation indicates that a signal is inactive.

#### 5.1 **PIN Descriptions**

| Name                             | Symbol                                 | Buffer Type                                                 | Description                                                                                                                                                                                                                                                                           |

|----------------------------------|----------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |                                        | UPSTREAM U                                                  | SB INTERFACE                                                                                                                                                                                                                                                                          |

| USB Bus Data                     | USBUP_DM<br>USBUP_DP                   | IO-U These pins connect to the Upstream USB bus of signals. |                                                                                                                                                                                                                                                                                       |

| Detect Upstream<br>VBUS Power    | VBUS_DET                               | I/O12                                                       | Detects state of Upstream VBUS power. The Microchip<br>Hub monitors VBUS_DET to determine when to assert<br>the internal D+ pull-up resistor (signalling a connect<br>event).                                                                                                         |

|                                  |                                        |                                                             | When designing a detachable hub, this pin must be connected to the VBUS power pin of the USB port that is upstream of the hub.                                                                                                                                                        |

|                                  |                                        |                                                             | For self-powered applications with a permanently attached host, this pin must be pulled-up to either 3.3V or 5.0V (typically VDD33).                                                                                                                                                  |

|                                  |                                        | 3-PORT USE                                                  | B INTERFACE                                                                                                                                                                                                                                                                           |

| USB Bus Data                     | USBDN_DM<br>[4:2]<br>USBDN_DP<br>[4:2] | IO-U                                                        | These pins connect to the Downstream USB bus data signals.                                                                                                                                                                                                                            |

| USB Power Enable                 | PRTPWR[4:2]                            | I/O12                                                       | Enables power to USB peripheral devices (downstream).                                                                                                                                                                                                                                 |

|                                  |                                        |                                                             | The active signal level of the PRTPWR[4:2] pins is determined by the Power Polarity Strapping function of the PRTPWR_POL pin.                                                                                                                                                         |

| Port Power Polarity<br>Strapping | PRTPWR_POL                             | I/O12                                                       | Port Power Polarity strapping determination for the active signal polarity of the PRTPWR[4:2] pins.                                                                                                                                                                                   |

|                                  |                                        |                                                             | While RESET_N is asserted, the logic state of this pin will (though the use of internal combinatorial logic) determine the active state of the PRTPWR[4:2] pins in order to ensure that downstream port power is not inadvertently enabled to inactive ports during a hardware reset. |

|                                  |                                        |                                                             | <ul> <li>'1' = PRTPWR[4:2] pins have an active 'high' polarity</li> <li>'0' = PRTPWR[4:2] pins have an active 'low' polarity</li> </ul>                                                                                                                                               |

| Over Current Sense               | OCS[4:2]_N                             | IPU                                                         | Input from external current monitor indicating an over-<br>current condition. {Note: Contains internal pull-up to 3.3V<br>supply}                                                                                                                                                     |

| Green LED                        | GR[4:2]_N                              | I/O8                                                        | Green indicator LED for ports 2, 3 and 4. Will be active low when LED support is enabled via EEPROM or SMBus.                                                                                                                                                                         |

|                                  | Compact                                | · ·                                                         | IDE mode) INTERFACE                                                                                                                                                                                                                                                                   |

| CF Chip Select 1                 | CF_nCS1                                | O8PU                                                        | This pin is the active low chip select 1 signal for the CF ATA device                                                                                                                                                                                                                 |

| Name                     | Symbol     | Buffer Type                                                                                   | Description                                                                                                                                                                                                    |  |

|--------------------------|------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CF Chip Select 0         | CF_nCS0    | O8PU                                                                                          | This pin is the active low chip select 0 signal for the task file registers of CF ATA device in the True IDE mode.                                                                                             |  |

| CF Register Address<br>2 | CF_SA2     | O8                                                                                            | This pin is the register select address bit 2 for the CF A device.                                                                                                                                             |  |

| CF Register Address<br>1 | CF_SA1     | O8                                                                                            | This pin is the register select address bit 1 for the CF ATA device                                                                                                                                            |  |

| CF Register Address<br>0 | CF_SA0     | O8                                                                                            | This pin is the register select address bit 0 for the CF ATA device.                                                                                                                                           |  |

| CF Interrupt             | CF_IRQ     | IPD                                                                                           | This is the active high interrupt request signal from the CF device.                                                                                                                                           |  |

| CF Data [15:8]           | CF_D[15:8] | I/O8PD                                                                                        | The bi-directional data signals CF_D15-CF_D8 in True IDE mode data transfer.                                                                                                                                   |  |

|                          |            |                                                                                               | In the True IDE Mode, all of task file register operation occur on the CF_D[7:0], while the data transfer is on CF_D[15:0].                                                                                    |  |

|                          |            |                                                                                               | The bi-directional data signal has an internal weak pull-<br>down resistor.                                                                                                                                    |  |

| CF Data [7:0]            | CF_D[7:0]  | I/O8PD                                                                                        | The bi-directional data signals CF_D7-CF_D0 in the True IDE mode data transfer.<br>In the True IDE Mode, all of task file register operation occur on the CF_D[7:0], while the data transfer is on CF_D[15:0]. |  |

|                          |            |                                                                                               | The bi-directional data signal has an internal weak pull-<br>down resistor.                                                                                                                                    |  |

| IO Ready                 | CF_IORDY   | IPU                                                                                           | This pin is active high input signal.                                                                                                                                                                          |  |

|                          |            |                                                                                               | This pin has an internally controlled weak pull-up resistor.                                                                                                                                                   |  |

| CF<br>Card Detection2    | CF_nCD2    | IPU                                                                                           | This card detection pin is connected to the ground on the CF device, when the CF device is inserted.                                                                                                           |  |

|                          |            |                                                                                               | This pin has an internally controlled weak pull-up resistor.                                                                                                                                                   |  |

| CF<br>Card Detection1    | CF_nCD1    | IPU This card detection pin is connected to ground or device, when the CF device is inserted. |                                                                                                                                                                                                                |  |

|                          |            |                                                                                               | This pin has an internally controlled weak pull-up resistor.                                                                                                                                                   |  |

| CF<br>Hardware Reset     | CF_nRESET  | O8                                                                                            | This pin is an active low hardware reset signal to CF device.                                                                                                                                                  |  |

| CF<br>IO Read            | CF_nIOR    | O8                                                                                            | This pin is an active low read strobe signal for CF device.                                                                                                                                                    |  |

| CF<br>IO Write Strobe    | CF_nIOW    | O8                                                                                            | This pin is an active low write strobe signal for CF device.                                                                                                                                                   |  |

|                          |            | SmartMedia                                                                                    |                                                                                                                                                                                                                |  |

| SM<br>Write Protect      | SM_nWP     | O8PD                                                                                          | This pin is an active low write protect signal for the SM device.                                                                                                                                              |  |

|                          |            |                                                                                               | This pin has a weak pull-down resistor that is permanently enabled                                                                                                                                             |  |

| SM<br>Address Strobe     | SM_ALE     | O8PD                                                                                          | This pin is an active high Address Latch Enable signal for the SM device.                                                                                                                                      |  |

|                          |            |                                                                                               | This pin has a weak pull-down resistor that is permanently enabled                                                                                                                                             |  |

| SM<br>Command Strobe     | SM_CLE     | O8PD                                                                                          | This pin is an active high Command Latch Enable signal for the SM device.                                                                                                                                      |  |

|                          |            |                                                                                               | This pin has a weak pull-down resistor that is permanently enabled                                                                                                                                             |  |

| Name                       | Symbol       | Buffer Type | Description                                                                                                                                                                                               |

|----------------------------|--------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SM<br>Data[7:0]            | SM_D[7:0]    | I/O8PD      | These pins are the bi-directional data signal SM_D7-SM_D0.                                                                                                                                                |

|                            |              |             | The bi-directional data signal has an internal weak pull-<br>down resistor.                                                                                                                               |

| SM<br>Read Enable          | SM_nRE       | 08PU        | This pin is an active low read strobe signal for SM device.                                                                                                                                               |

| neau Enable                |              |             | When using the internal FET, this pin has an internal weak pull-up resistor that is tied to the output of the internal Power FET.                                                                         |

|                            |              | 08          | If an external FET is used (Internal FET is disabled), then<br>the internal pull-up is not available (external pull-ups must<br>be used, and should be connected to the applicable Card<br>Power Supply). |

| SM<br>Write Epoble         | SM_nWE       | O8PU        | This pin is an active low write strobe signal for SM device.                                                                                                                                              |

| Write Enable               |              |             | When using the internal FET, this pin has an internal weak pull-up resistor that is tied to the output of the internal Power FET.                                                                         |

|                            |              | 08          | If an external FET is used (Internal FET is disabled), then<br>the internal pull-up is not available (external pull-ups must<br>be used, and should be connected to the applicable Card<br>Power Supply). |

| SM<br>Write Protect Switch | SM_nWPS      | IPU         | A write-protect seal is detected, when this pin is low.                                                                                                                                                   |

| while Protect Switch       |              |             | This pin has an internally controlled weak pull-up resistor.                                                                                                                                              |

| SM<br>Busy or Data Ready   | SM_nB/R      | I           | This pin is connected to the BSY/RDY pin of the SM device.                                                                                                                                                |

|                            |              |             | An external pull-up resistor is required on this signal. The pull-up resistor must be pulled up to the same power source that powers the SM/NAND flash device.                                            |

| SM<br>Chip Enable          | SM_nCE       | O8PU        | This pin is the active low chip enable signal to the SM device.                                                                                                                                           |

|                            |              |             | When using the internal FET, this pin has an internal weak pull-up resistor that is tied to the output of the internal Power FET.                                                                         |

|                            |              | 08          | If an external FET is used (Internal FET is disabled), then<br>the internal pull-up is not available (external pull-ups must<br>be used, and should be connected to the applicable Card<br>Power Supply). |

| SM<br>Card Detection       | SM_nCD       | IPU         | This is the card detection signal from SM device to indicate if the device is inserted.                                                                                                                   |

|                            |              |             | This pin has an internally controlled weak pull-up resistor.                                                                                                                                              |

|                            |              | MEMORY STI  |                                                                                                                                                                                                           |

| MS<br>Bus State            | MS_BS        | 08          | This pin is connected to the BS pin of the MS device.                                                                                                                                                     |

|                            |              |             | It is used to control the Bus States 0, 1, 2 and 3 (BS0, BS1, BS2 and BS3) of the MS device.                                                                                                              |

| MS<br>System               | MS_SDIO/MS_D | I/O8PD      | This pin is a bi-directional data signal for the MS device.                                                                                                                                               |

| Data In/Out                | 0            |             | Most significant bit (MSB) of each byte is transmitted first by either MSC or MS device.                                                                                                                  |

|                            |              |             | The bi-directional data signal has an internal weak pull-<br>down resistor.                                                                                                                               |

| MS<br>System Data In/Out   | MS_D1        | I/O8PD      | This pin is a bi-directional data signal for the MS device.                                                                                                                                               |

| System Data In/Out         |              |             | This pin has internally controlled weak pull-up and pull-<br>down resistors for various operational modes.                                                                                                |

| Name                  | Symbol      | Buffer Type | Description                                                                                                                                                                                                                                                                          |

|-----------------------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MS                    | MS_D[3:2]   | I/O8PD      | This pin is a bi-directional data signal for the MS device.                                                                                                                                                                                                                          |

| System<br>Data In/Out |             |             | The bi-directional data signal has an internal weak pull-<br>down resistor.                                                                                                                                                                                                          |

| MS<br>Card Insertion  | MS_INS      | IPU         | This pin is the card detection signal from the MS device to indicate, if the device is inserted.                                                                                                                                                                                     |

|                       |             |             | This pin has an internally controlled weak pull-up resistor.                                                                                                                                                                                                                         |

| MS<br>System CLK      | MS_SCLK     | O8          | This pin is an output clock signal to the MS device.                                                                                                                                                                                                                                 |

| System OLK            |             |             | The clock frequency is software configurable.                                                                                                                                                                                                                                        |

|                       |             | SD INT      | ERFACE                                                                                                                                                                                                                                                                               |

| SD<br>Data [2:0]      | SD_DAT[3:0] | I/O8PU      | These are bi-directional data signals.                                                                                                                                                                                                                                               |

| Data [3:0]            |             |             | These pins have internally controlled weak pull-up resistors.                                                                                                                                                                                                                        |

| SD Clock              | SD_CLK      | O8          | This is an output clock signal to SD/MMC device.                                                                                                                                                                                                                                     |

|                       |             |             | The clock frequency is software configurable.                                                                                                                                                                                                                                        |

| SD Command            | SD_CMD      | I/O8PU      | This is a bi-directional signal that connects to the CMD signal of SD/MMC device.                                                                                                                                                                                                    |

|                       |             |             | This pin has an internally controlled weak pull-up resistor.                                                                                                                                                                                                                         |

| SD<br>Write Protected | SD_nWP      | IPD         | This pin is an input signal with an internal weak pull-<br>down.                                                                                                                                                                                                                     |

|                       |             |             | This pin has an internally controlled weak pull-down resistor.                                                                                                                                                                                                                       |

|                       |             | м           | ISC                                                                                                                                                                                                                                                                                  |

| General Purpose I/O   | GPIO1       | I/O8        | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                     |

| General Purpose I/O   | GPIO2       | I/O8        | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                     |

| General Purpose I/O   | GPIO4       | I/O8        | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                     |

| General Purpose I/O   | GPIO5       | I/O8        | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                     |

| GPIO6                 | GPIO6       | IPU         | This pin has an internal weak pull-up resistor that is<br>enabled or disabled by the state of RESET_N.<br>The pull-up is enabled when RESET_N is active.<br>The pull-up is disabled, when the RESET_N is inactive<br>(some clock cycles later, after the rising edge of<br>RESET_N). |

|                       |             |             | The state of this pin is latched internally on the rising edge of RESET_N to determine if internal or external program memory is used.<br>The state latched is stored in ROMEN bit of GPIO_IN1 register.                                                                             |

|                       |             | I/O8        | After the rising edge of RESET_N, this pin may be used<br>as GPIO6.<br>When this pin is left unconnected or pulled high by a<br>weak pull-up resistor, the USB2601/USB2602 uses the<br>internal ROM for program execution.                                                           |

|                       |             |             | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                     |

| General Purpose I/O   | GPIO7       | I/O8        | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                     |

| Name                                  | Symbol              | Buffer Type | Description                                                                                                                                                                                                                                                                                                  |

|---------------------------------------|---------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose I/O<br>Or             | GPIO8/<br>CRD_PWR0  | I/O8        | GPIO: This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                                       |

| Card Power                            |                     |             | CRD_PWR: Card Power drive of 3.3V @ 100mA.                                                                                                                                                                                                                                                                   |

| General Purpose I/O                   | GPIO9               | I/O8        | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                                             |

| General Purpose I/O<br>Or             | GPIO10/<br>CRD_PWR1 | I/O8        | GPIO: This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                                       |

| Card Power                            |                     |             | CRD_PWR: Card Power drive of 3.3V @ 100mA.                                                                                                                                                                                                                                                                   |

| General Purpose I/O<br>Or             | GPIO11/<br>CRD_PWR2 | I/O8        | GPIO: These pins may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                                                     |

| Card Power                            |                     |             | CRD_PWR: Card Power drive of 3.3V @ 200mA.                                                                                                                                                                                                                                                                   |

| General Purpose I/O                   | GPIO[15:12]         | I/O8        | These pins may be used either as input, or output.                                                                                                                                                                                                                                                           |

| RESET input                           | RESET_N             | IS          | This active low signal is used by the system to reset the chip. The active low pulse should be at least $1\mu$ s wide.                                                                                                                                                                                       |

| TEST Input                            | TEST                | IPD         | Used for testing the IC. User must treat either as a no-<br>connect, or connect to the ground.                                                                                                                                                                                                               |

| USB Transceiver Bias                  | RBIAS               | I           | A 12.0k $\Omega$ , $\pm$ 1.0% resistor is attached from VSS to this pin, in order to set the transceiver's internal bias currents.                                                                                                                                                                           |

| Analog Test                           | ATEST               | AIO         | This signal is used for testing the analog section of the chip and should be connected to VDDA33 for normal operation.                                                                                                                                                                                       |

| Crystal Input/External<br>Clock Input | XTAL1/<br>CLKIN     | ICLKx       | 24MHz Crystal or external clock input.<br>This pin can be connected to one terminal of the crystal<br>or can be connected to an external 24MHz clock when a<br>crystal is not used.<br><b>Note:</b> The 'SEL_CLKDRV and CLK_SEL[1:0]' pins                                                                   |

|                                       |                     |             | will be sampled while RESET_N is asserted,<br>and the value will be latched upon RESET_N<br>negation. This will determine the clock source<br>and value.                                                                                                                                                     |

| Crystal Output                        | XTAL2               | OCLKx       | 24MHz Crystal<br>This is the other terminal of the crystal, or left open when<br>an external clock source is used to drive XTAL1/CLKIN.<br>It may not be used to drive any external circuitry other<br>than the crystal circuit.                                                                             |

| Select Clock Drive                    | SEL_CLKDRV          | I/O8PD      | SEL_CLKDRV. During RESET_N assertion, this pin will<br>select the operating clock mode (crystal or externally<br>driven clock source), and a weak pull-down resistor is<br>enabled. When RESET_N is negated, the value will be<br>internally latched and the internal pull-down will be<br>disabled.         |

|                                       |                     |             | '0' = Crystal operation (24MHz)<br>'1' = Externally driven clock source (24MHz)                                                                                                                                                                                                                              |

| Clock Select                          | CLK_SEL[1:0]        | I/O8PD      | SEL[1:0]. During RESET_N assertion, these pins will<br>select the operating frequency of the external clock, and<br>the corresponding weak pull-down resistors are enabled.<br>When RESET_N is negated, the value on these pins will<br>be internal latched and the internal pull-downs will be<br>disabled. |

|                                       |                     |             | SEL[1:0] = '00'. 24MHz<br>SEL[1:0] = '01'. RESERVED<br>SEL[1:0] = '10'. RESERVED<br>SEL[1:0] = '11'. RESERVED                                                                                                                                                                                                |

|                                       |                     | ANALO       | G POWER                                                                                                                                                                                                                                                                                                      |

| 1.8V PLL Power                        | VDD18PLL            |             | 1.8V Output from the internal 1.8V PLL regulator                                                                                                                                                                                                                                                             |

| 3.3V PLL Power                        | VDD33PLL            |             | 3.3V Input to the internal 1.8V PLL regulator.                                                                                                                                                                                                                                                               |

| Name                                         | Symbol    | Buffer Type | Description                                                                                 |

|----------------------------------------------|-----------|-------------|---------------------------------------------------------------------------------------------|

| 3.3V Analog Power                            | VDDA33    |             | 3.3v Analog PHY Power                                                                       |

|                                              | DIGITAL P | OWER, GROU  | NDS, and NO CONNECTS                                                                        |

| 1.8V Digital Core<br>Power                   | VDD18     |             | +1.8V Core power<br>All VDD18 pins must be connected together on the circuit<br>board.      |

| 3.3v Power & &<br>Voltage Regulator<br>Input | VDD33     |             | 3.3V Power & Regulator Input.<br>Pin 87 supplies 3.3V power to the internal 1.8V regulator. |

| Ground                                       | VSS       |             | Ground Reference                                                                            |

| No Connect                                   | NC        |             | No Connect. No trace or signal should be routed/attached to these pins.                     |

**Note 1:** Hot-insertion capable card connectors are required for all flash media. It is required for SD connector to have Write Protect switch. This allows the chip to detect MMC card.

2: nMCE is normally asserted except when the 8051 is in standby mode.

### 5.2 Buffer Type Descriptions

#### TABLE 5-1: USB2601/USB2602 BUFFER TYPE DESCRIPTIONS

| Buffer | Description                                                                                 |

|--------|---------------------------------------------------------------------------------------------|

| I      | Input                                                                                       |

| IPU    | Input with internal weak pull-up resistor.                                                  |

| IPD    | Input with internal weak pull-down resistor.                                                |

| IS     | Input with Schmitt trigger                                                                  |

| I/O8   | Input/Output buffer with 8mA sink and 8mA source.                                           |

| I/O8PU | Input/Output buffer with 8mA sink and 8mA source, with an internal weak pull-up resistor.   |

| I/O8PD | Input/Output buffer with 8mA sink and 8mA source, with an internal weak pull-down resistor. |

| I/O12  | Input/Output, 12mA                                                                          |

| O8     | Output buffer with 8mA sink and 8mA source.                                                 |

| O8PU   | Output buffer with 8mA sink and 8mA source, with an internal weak pull-up resistor.         |

| O8PD   | Output buffer with 8mA sink and 8mA source, with an internal weak pull-down resistor.       |

| ICLKx  | XTAL clock input                                                                            |

| OCLKx  | XTAL clock output                                                                           |

| I/O-U  | Analog Input/Output Defined in USB specification                                            |

| AIO    | Analog Input/Output                                                                         |

# 6.0 DC PARAMETERS

#### 6.1 Maximum Ratings

| Operating Temperature Range*                                              | 0°C to +70°C                           |

|---------------------------------------------------------------------------|----------------------------------------|

| Storage Temperature Range                                                 | 55 <sup>o</sup> to +150 <sup>o</sup> C |

| Lead Temperature Range (soldering, 10 seconds)                            | +325°C                                 |

| Positive Voltage on GPIO3, with respect to Ground                         | 5.5V                                   |

| Positive Voltage on any signal pin, with respect to Ground                | 4.6V                                   |

| Positive Voltage on XTAL1, with respect to Ground                         | 4.0V                                   |

| Negative Voltage on GPIO8, 10 & 11, with respect to Ground (see Note 6-2) | 0.5V                                   |

| Negative Voltage on any pin, with respect to Ground                       | 0.5V                                   |

| Maximum V <sub>DD18</sub> , V <sub>DD18PLL</sub>                          | +2.5V                                  |

| Maximum V <sub>DD33</sub> , V <sub>DDA33</sub>                            | +4.6V                                  |

\* Stresses above the specified parameters could cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other condition above those indicated in the operation sections of this specification is not implied.

- **Note 6-1** When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes on their outputs when the AC power is switched on or off. In addition, voltage transients on the AC power line may appear on the DC output. When this possibility exists, it is suggested that a clamp circuit be used.

- **Note 6-2** When internal power FET operation of these pins is enabled, these pins may be simultaneously shorted to ground or any voltage up to 3.63V indefinitely, without damage to the device as long as  $V_{DD33}$  and  $V_{DDA33}$  are less than 3.63V and  $T_A$  is less than 70°C.

### 6.2 Operating Conditions

| Parameter             | Symbol                                     | MIN  | МАХ                | Units | Comments                                   |

|-----------------------|--------------------------------------------|------|--------------------|-------|--------------------------------------------|

| Operating Temperature | T <sub>A</sub>                             | 0    | 70                 | °C    | *Ambient temperature in still air.         |

| 1.8V supply voltage   | V <sub>DD18,</sub><br>V <sub>DD18PLL</sub> | 1.62 | 1.98               | V     |                                            |

| 3.3V supply voltage   | V <sub>DD33,</sub><br>V <sub>DDA33</sub>   | 3.0  | 3.6                | V     |                                            |

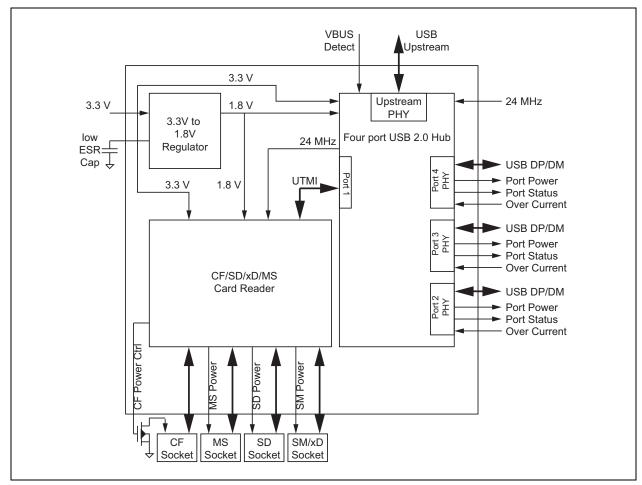

| 3.3V supply rise time | t <sub>RT</sub>                            | 0    | 400                | μS    | (See Figure 6-1, "Supply Rise Time Model") |

| Voltage on XTAL1      |                                            | -0.3 | V <sub>DDA33</sub> | V     |                                            |

FIGURE 6-1: SUPPLY RISE TIME MODEL

**Note 6-3** When powering the device, the maximum power supply ramp time should be set at a rate faster than 400 micro seconds. This speed is important to ensure that the device resets properly. Measure rise time at 10% and 90%.

### 6.3 DC Electrical Characteristics

| Parameter                               | Symbol            | MIN                        | ТҮР | MAX | Units | Comments                                               |

|-----------------------------------------|-------------------|----------------------------|-----|-----|-------|--------------------------------------------------------|

| I,IPU & IPD Type Input Buffer           |                   |                            |     |     |       |                                                        |

| Low Input Level                         | V <sub>ILI</sub>  |                            |     | 0.8 | V     | TTL Levels                                             |

| High Input Level                        | V <sub>IHI</sub>  | 2.0                        |     |     | V     |                                                        |

| Pull Down                               | PD                |                            | 72  |     | μA    |                                                        |

| Pull Up                                 | PU                |                            | 58  |     | μA    |                                                        |

| IS Type Input Buffer                    |                   |                            |     |     |       |                                                        |

| Low Input Level                         | V <sub>ILI</sub>  |                            |     | 0.8 | V     | TTL Levels                                             |

| High Input Level                        | V <sub>IHI</sub>  | 2.0                        |     |     | V     |                                                        |

| Hysteresis                              | V <sub>HYSI</sub> |                            | 500 |     | mV    |                                                        |

| ICLK Input Buffer                       |                   |                            |     |     |       |                                                        |

| Low Input Level                         | V <sub>ILCK</sub> |                            |     | 0.4 | V     |                                                        |

| High Input Level                        | VIHCK             | 2.2                        |     |     | V     |                                                        |

| Input Leakage<br>(All I and IS buffers) |                   |                            |     |     |       |                                                        |

| Low Input Leakage                       | I <sub>IL</sub>   | -10                        |     | +10 | μA    | V <sub>IN</sub> = 0                                    |

| High Input Leakage                      | I <sub>IH</sub>   | -10                        |     | +10 | mA    | V <sub>IN</sub> = V <sub>DD33</sub>                    |

| O8. O8PU & 08PD Type Buffer             |                   |                            |     |     |       |                                                        |

| Low Output Level                        | V <sub>OL</sub>   |                            |     | 0.4 | V     | I <sub>OL</sub> = 8 mA @ V <sub>DD33</sub> =<br>3.3V   |

| High Output Level                       | V <sub>OH</sub>   | V <sub>DD33</sub><br>- 0.4 |     |     | V     | I <sub>OH</sub> = -8mA @ V <sub>DD33</sub> =<br>3.3V   |

| Output Leakage                          | I <sub>OL</sub>   | -10                        |     | +10 | μΑ    | V <sub>IN</sub> = 0 to V <sub>DD33</sub><br>(Note 6-4) |

| Pull Down                               | PD                |                            | 72  |     | μA    |                                                        |

| Pull Up                                 | PU                |                            | 58  |     | μA    |                                                        |

| Parameter                                  | Symbol            | MIN                       | ТҮР | МАХ | Units | Comments                                               |

|--------------------------------------------|-------------------|---------------------------|-----|-----|-------|--------------------------------------------------------|

| I/O8, I/O8PU & I/O8PD Type<br>Buffer       |                   |                           |     |     |       |                                                        |

| Low Output Level                           | V <sub>OL</sub>   |                           |     | 0.4 | V     | I <sub>OL</sub> = 8 mA @ V <sub>DD33</sub> =<br>3.3V   |

| High Output Level                          | V <sub>OH</sub>   | V <sub>DD33</sub><br>-0.4 |     |     | V     | I <sub>OH</sub> = -8 mA @ V <sub>DD33</sub> =<br>3.3V  |

| Output Leakage                             | I <sub>OL</sub>   | -10                       |     | +10 | μA    | V <sub>IN</sub> = 0 to V <sub>DD33</sub><br>(Note 6-4) |

| Pull Down                                  | PD                |                           | 72  |     | μΑ    |                                                        |

| Pull Up                                    | PU                |                           | 58  |     | μA    |                                                        |

| I/O12 Type Buffer                          |                   |                           |     |     |       |                                                        |

| Low Output Level                           | V <sub>OL</sub>   |                           |     | 0.4 | v     | I <sub>OL</sub> = 12mA @ V <sub>DD33</sub> =           |

| High Output Level                          | V <sub>OH</sub>   | 2.4                       |     |     | v     | 3.3V                                                   |

| Output Leakage                             | I <sub>OL</sub>   |                           |     | +10 | uA    | I <sub>OH</sub> = -4mA @ V <sub>DD33</sub> =<br>3.3V   |

|                                            |                   |                           |     |     |       | V <sub>IN</sub> = 0 to V <sub>DD33</sub><br>(Note 1)   |

| <b>IO-U</b><br>(Note 6-5)                  |                   |                           |     |     |       |                                                        |

| Integrated Power FET for<br>GPI08 & GPI010 |                   |                           |     |     |       |                                                        |

| Output Current                             | I <sub>OUT</sub>  | 100                       |     |     | mA    | GPIO8, or 10;<br>Vdrop <sub>FET</sub> = 0.23V          |

| Short Circuit Current Limit                | I <sub>SC</sub>   |                           |     | 140 | mA    | GPIO8, or 10; Vout <sub>FET</sub><br>= 0V              |

| On Resistance                              | R <sub>DSON</sub> |                           |     | 2.1 | w     | GPIO8, or 10;<br>I <sub>FET</sub> = 70mA               |

| Output Voltage Rise Time                   | t <sub>DSON</sub> |                           |     | 800 | ms    | GPIO8, or 10;<br>C <sub>LOAD</sub> = 10mF              |