# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Hi-Speed USB Device PHY with UTMI Interface

### **PRODUCT FEATURES**

Available in a 36-pin lead-free RoHS compliant (6 x 6 x 0.90mm) QFN package

- Interface compliant with the UTMI specification (60MHz, 8-bit bidirectional interface)

- Only one required power supply (+3.3V)

- USB-IF "Hi-Speed" certified to USB 2.0 electrical specification

- Supports 480Mbps Hi-Speed (HS) and 12Mbps Full Speed (FS) serial data transmission rates

- Integrated 45Ω and 1.5kΩ termination resistors reduce external component count

- Internal short circuit protection of DP and DM lines

- On-chip oscillator operates with low cost 24MHz crystal

- Latch-up performance exceeds 150mA per EIA/JESD 78, Class II

- ESD protection levels of 5kV HBM without external protection devices

- SYNC and EOP generation on transmit packets and detection on receive packets

- NRZI encoding and decoding

- Bit stuffing and unstuffing with error detection

- Supports the USB suspend state, HS detection, HS Chirp, Reset and Resume

- Support for all test modes defined in the USB 2.0 specification

- 55mA Unconfigured Current (typical) ideal for bus powered applications.

- 83uA suspend current (typical) ideal for battery powered applications.

- Industrial Operating Temperature -40°C to +85°C

#### Applications

The USB3280 is the ideal companion to any ASIC, SoC or FPGA solution designed with a UTMI Hi-Speed USB device (peripheral) core.

Datasheet

The USB3280 is well suited for:

- Cell Phones

- MP3 Players

- Scanners

- External Hard Drives

- Digital Still and Video Cameras

- Portable Media Players

- Entertainment Devices

- Printers

#### **ORDER NUMBER(S):**

### USB3280-AEZG FOR 36-PIN, QFN LEAD-FREE ROHS COMPLIANT PACKAGE USB3280-AEZG-TR FOR 36-PIN, QFN LEAD-FREE ROHS COMPLIANT PACKAGE (TAPE AND REEL) Reel Size is 3000 pieces.

smsc°

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123

Copyright  $\circledast$  2007 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

## **Table of Contents**

|                                                                                              |                                                                                                                                                 | General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

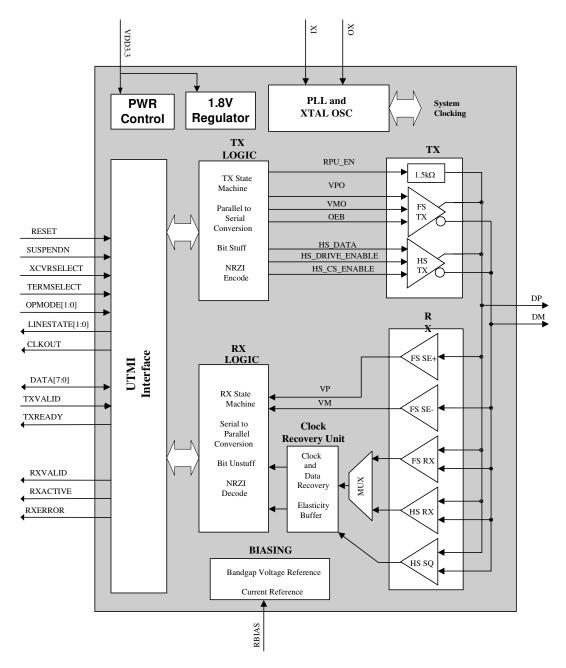

| Chap                                                                                         | ter 2                                                                                                                                           | Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 7                                                                  |

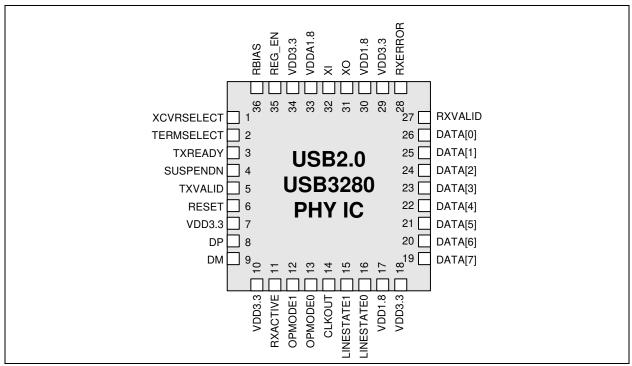

| Chap                                                                                         | ter 3                                                                                                                                           | Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 8                                                                  |

| Chap                                                                                         | ter 4                                                                                                                                           | Interface Signal Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 9                                                                  |

| Chap                                                                                         | ter 5                                                                                                                                           | Limiting Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12                                                                   |

|                                                                                              | Driver                                                                                                                                          | Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16                                                                   |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8                                                | Modes<br>System<br>Clock a<br>TX Log<br>RX Log<br>USB 2.<br>7.6.1<br>7.6.2<br>7.6.3<br>Crystal<br>Interna                                       | Functional Overview       for the second secon | 21<br>21<br>22<br>23<br>26<br>26<br>26<br>27<br>27<br>27             |

|                                                                                              | 7.8.1<br>7.8.2<br>7.8.3                                                                                                                         | Internal Regulators<br>Power On Reset (POR)<br>Reset Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27                                                                   |

| 8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>8.10<br>8.11<br>8.12<br>8.13<br>8.14 | Linesta<br>OPMO<br>Test M<br>SE0 Ha<br>Reset I<br>Susper<br>HS De<br>HS De<br>HS De<br>HS De<br>HS De<br>Asserti<br>Detecti<br>HS De<br>Asplica | Application Notes.         ate         DES         ode Support         andling         Detection         nd Detection         tection Handshake         tection Handshake – FS Downstream Facing Port         tection Handshake – HS Downstream Facing Port         tection Handshake – Suspend Timing         on of Resume         ion of Resume         vice Attach         ation Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28<br>29<br>20<br>30<br>31<br>32<br>34<br>36<br>38<br>39<br>39<br>41 |

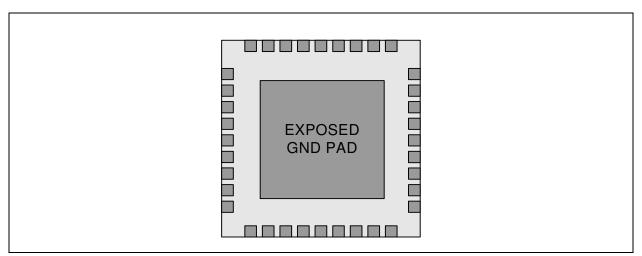

| Chapt                                                                                        | ter 9                                                                                                                                           | Package Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42                                                                   |

## List of Figures

| Figure 2.1     | USB3280 Block Diagram                                                               |

|----------------|-------------------------------------------------------------------------------------|

| Figure 3.1     | USB3280 Pinout - Top View                                                           |

| Figure 3.2     | USB3280 Pinout - Bottom View                                                        |

| Figure 6.1     | Full-Speed Driver VOH/IOH Characteristics for High-speed Capable Transceiver 17     |

| Figure 6.2     | Full-Speed Driver VOL/IOL Characteristics for High-speed Capable Transceiver 17     |

| Figure 6.3     | Eye Pattern Measurement Planes                                                      |

| Figure 6.4     | Eye Pattern for Transmit Waveform and Eye Pattern Definition                        |

| Figure 6.5     | Eye Pattern for Receive Waveform and Eye Pattern Definition                         |

| Figure 7.1     | FS CLK Relationship to Transmit Data and Control Signals                            |

| Figure 7.2     | FS CLK Relationship to Receive Data and Control Signals                             |

| Figure 7.3     | Transmit Timing for a Data Packet                                                   |

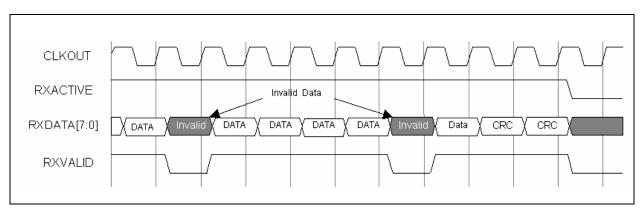

| Figure 7.4     | Receive Timing for Data with Unstuffed Bits                                         |

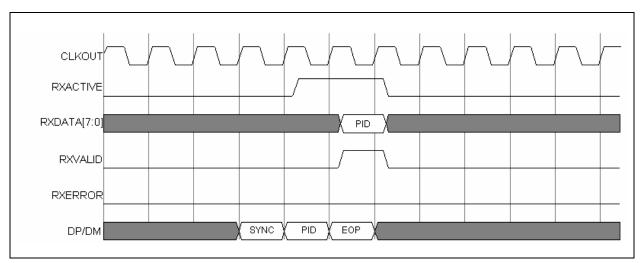

| Figure 7.5     | Receive Timing for a Handshake Packet (no CRC)                                      |

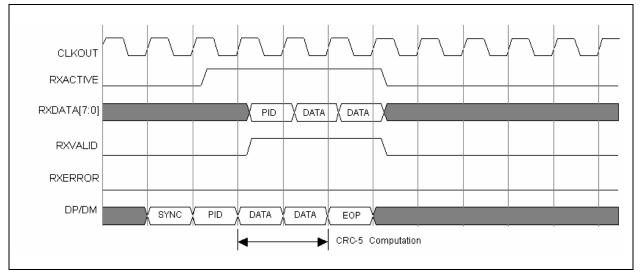

| Figure 7.6     | Receive Timing for Setup Packet                                                     |

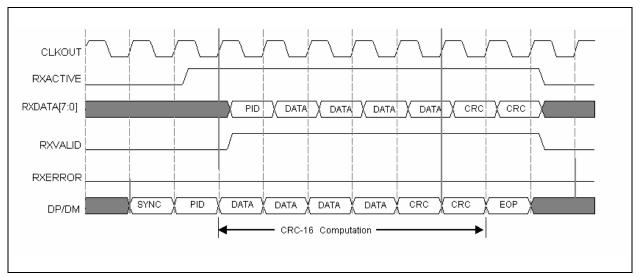

| Figure 7.7     | Receive Timing for Data Packet (with CRC-16)                                        |

| Figure 8.1     | Reset Timing Behavior (HS Mode)                                                     |

| Figure 8.2     | Suspend Timing Behavior (HS Mode) 31                                                |

| Figure 8.3     | HS Detection Handshake Timing Behavior (FS Mode)                                    |

| Figure 8.4     | Chirp K-J-K-J Sequence Detection State Diagram                                      |

| Figure 8.5     | HS Detection Handshake Timing Behavior (HS Mode)                                    |

| Figure 8.6     | HS Detection Handshake Timing Behavior from Suspend                                 |

| Figure 8.7     | Resume Timing Behavior (HS Mode) 38                                                 |

| Figure 8.8     | Device Attach Behavior                                                              |

| Figure 8.9     | USB3280 Application Diagram                                                         |

| Figure 9.1     | USB3280-AEZG 36-Pin QFN Package Outline and Parameters, 6 x 6 x 0.90 mm Body (Lead- |

| <b>F</b> ' 0.0 | Free RoHS Compliant) 42                                                             |

| Figure 9.2     | QFN, 6x6 Tape & Reel                                                                |

| Figure 9.3     | Reel Dimensions                                                                     |

## **List of Tables**

| Table 4.1  | System Interface Signals                                             |

|------------|----------------------------------------------------------------------|

| Table 4.2  | Data Interface Signals 10                                            |

| Table 4.3  | USB I/O Signals                                                      |

| Table 4.4  | Biasing and Clock Oscillator Signals 10                              |

| Table 4.5  | Power and Ground Signals 11                                          |

| Table 5.1  | Absolute Maximum Ratings 12                                          |

| Table 5.2  | Recommended Operating Conditions 12                                  |

| Table 5.3  | Recommended External Clock Conditions 12                             |

| Table 6.1  | Electrical Characteristics: Supply Pins (Note 6.1) 13                |

| Table 6.2  | DC Electrical Characteristics: Logic Pins (Note 6.2) 13              |

| Table 6.3  | DC Electrical Characteristics: Analog I/O Pins (DP/DM) (Note 6.3) 14 |

| Table 6.4  | Dynamic Characteristics: Analog I/O Pins (DP/DM) (Note 6.4)          |

| Table 6.5  | Dynamic Characteristics: Digital UTMI Pins (Note 6.5) 16             |

| Table 7.1  | DP/DM Termination vs. Signaling Mode 26                              |

| Table 8.1  | Linestate States                                                     |

| Table 8.2  | Operational Modes                                                    |

| Table 8.3  | USB 2.0 Test Modes                                                   |

| Table 8.4  | Reset Timing Values (HS Mode) 30                                     |

| Table 8.5  | Suspend Timing Values (HS Mode) 31                                   |

|            | HS Detection Handshake Timing Values (FS Mode)                       |

| Table 8.7  | Reset Timing Values                                                  |

|            | HS Detection Handshake Timing Values from Suspend 37                 |

|            | Resume Timing Values (HS Mode) 38                                    |

| Table 8.10 | Attach and Reset Timing Values 40                                    |

## **Chapter 1 General Description**

The USB3280 provides the Physical Layer (PHY) interface to a USB 2.0 Device Controller. The IC is available in a 36-pin lead-free RoHS compliant QFN package.

### 1.1 **Product Description**

The USB3280 is an industrial temperature USB 2.0 physical layer transceiver (PHY) integrated circuit. SMSC's proprietary technology results in low power dissipation, which is ideal for building a bus powered USB 2.0 peripheral. The PHY uses an 8-bit bidirectional parallel interface, which complies with the USB Transceiver Macrocell Interface (UTMI) specification. It supports 480Mbps transfer rate, while remaining backward compatible with USB 1.1 legacy protocol at 12Mbps.

All required termination and 5.25V short circuit protection of the DP/DM lines are internal to the chip. The USB3280 also has an integrated 1.8V regulator so that only a 3.3V supply is required.

While transmitting data, the PHY serializes data and generates SYNC and EOP fields. It also performs needed bit stuffing and NRZI encoding. Likewise, while receiving data, the PHY de-serializes incoming data, stripping SYNC and EOP fields and performs bit un-stuffing and NRZI decoding.

## **Chapter 2 Functional Block Diagram**

Figure 2.1 USB3280 Block Diagram

Figure 3.1 USB3280 Pinout - Top View

Figure 3.2 USB3280 Pinout - Bottom View

The flag of the QFN package must be connected to ground.

## Chapter 4 Interface Signal Definition

| Table 4.1 | System | Interface | Signals |

|-----------|--------|-----------|---------|

|-----------|--------|-----------|---------|

| NAME                             | DIRECTION | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|----------------------------------|-----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RESET<br>(RST)                   | Input     | High            | <b>Reset.</b> Reset all state machines. After coming out of reset, must wait 5 rising edges of clock before asserting TXValid for transmit. See Section 7.8.3                                                                                                                                                                                                                                         |  |  |  |

| XCVRSELECT<br>(XSEL)             | Input     | N/A             | <b>Transceiver Select.</b> This signal selects between the FS and HS transceivers:<br>0: HS transceiver enabled<br>1: FS transceiver enabled.                                                                                                                                                                                                                                                         |  |  |  |

| TERMSELECT<br>(TSEL)             | Input     | N/A             | <b>Termination Select.</b> This signal selects between the FS and HS terminations:<br>0: HS termination enabled<br>1: FS termination enabled                                                                                                                                                                                                                                                          |  |  |  |

| SUSPENDN<br>(SPDN)               | Input     | Low             | <b>Suspend.</b> Places the transceiver in a mode that draws minimal power from supplies. Shuts down all blocks not necessary for Suspend/Resume operation. While suspended, TERMSELECT must always be in FS mode to ensure that the $1.5k\Omega$ pull-up on DP remains powered. 0: Transceiver circuitry drawing suspend current 1: Transceiver circuitry drawing normal current                      |  |  |  |

| CLKOUT<br>(CLK)                  | Output    | Rising Edge     | <b>System Clock</b> . This output is used for clocking receive and transmit parallel data at 60MHz.                                                                                                                                                                                                                                                                                                   |  |  |  |

| OPMODE[1:0]<br>(OM1)<br>(OM0)    | Input     | N/A             | Operational Mode.         These signals select between the various operational modes:           [1]         [0]         Description           0         0         0: Normal Operation           0         1: Non-driving (all terminations removed)           1         0         2: Disable bit stuffing and NRZI encoding           1         1         3: Reserved                                 |  |  |  |

| LINESTATE[1:0]<br>(LS1)<br>(LS0) | Output    | N/A             | Line State. These signals reflect the current state of the USB data bus in FS mode, with [0] reflecting the state of DP and [1] reflecting the state of DM. When the device is suspended or resuming from a suspended state, the signals are combinatorial. Otherwise, the signals are synchronized to CLKOUT.<br>[1] [0] Description<br>0 0 0: SE0<br>0 1 1: J State<br>1 0 2: K State<br>1 1 3: SE1 |  |  |  |

| NAME              | DIRECTION     | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                         |  |  |  |  |

|-------------------|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DATA[7:0]         | Bidirectional | High            | Data bus. 8-bit Bidi                                                                                                                                                                                                                                                                                                                                                         | rectional mode.                                                                                                                         |  |  |  |  |

| (D7)              |               |                 | TXVALID                                                                                                                                                                                                                                                                                                                                                                      | DATA[7:0]                                                                                                                               |  |  |  |  |

|                   |               |                 | 0                                                                                                                                                                                                                                                                                                                                                                            | output                                                                                                                                  |  |  |  |  |

| (D0)              |               |                 | 1                                                                                                                                                                                                                                                                                                                                                                            | input                                                                                                                                   |  |  |  |  |

| TXVALID<br>(TXV)  | Input         | High            | assertion of TXVALID                                                                                                                                                                                                                                                                                                                                                         | ates that the DATA bus is valid for transmit. The<br>initiates the transmission of SYNC on the USB<br>TXVALID initiates EOP on the USB. |  |  |  |  |

|                   |               |                 | Control inputs (OPMODE[1:0], TERMSELECT,XCVRSELECT) must<br>not be changed on the de-assertion or assertion of TXVALID. The<br>PHY must be in a quiescent state when these inputs are changed.                                                                                                                                                                               |                                                                                                                                         |  |  |  |  |

| TXREADY<br>(TXR)  | Output        | High            | <b>Transmit Data Ready.</b> If TXVALID is asserted, the SIE must always have data available for clocking into the TX Holding Register on the rising edge of CLKOUT. TXREADY is an acknowledgement to the SIE that the transceiver has clocked the data from the bus and is ready for the next transfer on the bus. If TXVALID is negated, TXREADY can be ignored by the SIE. |                                                                                                                                         |  |  |  |  |

| RXVALID<br>(RXV)  | Output        | High            | <b>Receive Data Valid.</b> Indicates that the DATA bus has received valid data. The Receive Data Holding Register is full and ready to be unloaded. The SIE is expected to latch the DATA bus on the rising edge of CLKOUT.                                                                                                                                                  |                                                                                                                                         |  |  |  |  |

| RXACTIVE<br>(RXA) | Output        | High            | <b>Receive Active.</b> Indicates that the receive state machine has detected Start of Packet and is active.                                                                                                                                                                                                                                                                  |                                                                                                                                         |  |  |  |  |

| RXERROR<br>(RXE)  | Output        | High            |                                                                                                                                                                                                                                                                                                                                                                              | error has been detected.<br>with the same timing as the receive DATA lines<br>ime during a transfer.                                    |  |  |  |  |

#### Table 4.2 Data Interface Signals

#### Table 4.3 USB I/O Signals

| NAME | DIRECTION | ACTIVE<br>LEVEL | DESCRIPTION            |

|------|-----------|-----------------|------------------------|

| DP   | I/O       | N/A             | USB Positive Data Pin. |

| DM   | I/O       | N/A             | USB Negative Data Pin. |

#### Table 4.4 Biasing and Clock Oscillator Signals

| NAME          | DIRECTION | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                |

|---------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RBIAS<br>(RB) | Input     | N/A             | <b>External 1% bias resistor.</b> Requires a $12k\Omega$ resistor to ground. Used for setting HS transmit current level and on-chip termination impedance. |

| XI/XO         | Input     | N/A             | External crystal. 24MHz crystal connected from XI to XO.                                                                                                   |

#### Table 4.5 Power and Ground Signals

| NAME              | DIRECTION | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-------------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VDD3.3<br>(V33)   | N/A       | N/A             | <b>3.3V Supply.</b> Provides power for USB 2.0 Transceiver, UTMI+ Digital, Digital I/O, and Regulators.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| REG_EN<br>(REN)   | Input     | High            | <ul> <li>On-Chip 1.8V regulator enable. Connect to ground to disal both of the on chip (VDDA1.8 and VDD1.8) regulators. Whe regulators are disabled:</li> <li>External 1.8V must be supplied to VDDA1.8 and VDD1.8 p When the regulators are disabled, VDDA1.8 may be connect to VDD1.8 and a bypass capacitor (0.1µF recommended) should be connected to each pin.</li> <li>The voltage at VDD3.3 must be at least 2.64V (0.8 * 3.3V before voltage is applied to VDDA1.8 and VDD1.8.</li> </ul> |  |  |  |

| VDD1.8<br>(V18)   | N/A       | N/A             | <b>1.8V Digital Supply.</b> Supplied by On-Chip Regulator when REG_EN is active. Low ESR 4.7uF minimum capacitor requirement when using internal regulators. Do not connect VDD1.8 to VDDA1.8 when using internal regulators. When the regulators are disabled, VDD1.8 may be connected to VDD1.8A.                                                                                                                                                                                               |  |  |  |

| VSS<br>(GND)      | N/A       | N/A             | Common Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| VDDA1.8<br>(V18A) | N/A       | N/A             | <b>1.8V Analog Supply.</b> Supplied by On-Chip Regulator when REG_EN is active. Low ESR 4.7uF minimum capacitor requirement when using internal regulators. Do not connect VDD1.8A to VDD1.8 when using internal regulators. When the regulators are disabled, VDD1.8A may be connected to VDD1.8.                                                                                                                                                                                                |  |  |  |

Hi-Speed USB Device PHY with UTMI Interface

Datasheet

## **Chapter 5 Limiting Values**

| PARAMETER                                    | SYMBOL                | CONDITIONS            | MIN  | ТҮР | МАХ | UNITS |  |  |

|----------------------------------------------|-----------------------|-----------------------|------|-----|-----|-------|--|--|

| Maximum DP and DM voltage to Ground          | V <sub>MAX_5V</sub>   |                       | -0.3 |     | 5.5 | V     |  |  |

| Maximum VDD1.8 and VDDA1.8 voltage to Ground | V <sub>MAX_1.8V</sub> |                       | -0.3 |     | 2.5 | V     |  |  |

| Maximum 3.3V Supply<br>Voltage to Ground     | V <sub>MAX_3.3V</sub> |                       | -0.3 |     | 4.0 | V     |  |  |

| Maximum I/O Voltage to Ground                | VI                    |                       | -0.3 |     | 4.0 | V     |  |  |

| Storage Temperature                          | T <sub>STG</sub>      |                       | -55  |     | 150 | °C    |  |  |

| ESD PERFORMANCE                              |                       |                       |      |     |     |       |  |  |

| All Pins                                     | V <sub>HBM</sub>      | Human Body Model      | ±5   |     |     | kV    |  |  |

| LATCH-UP PERFORMANCE                         |                       |                       |      |     |     |       |  |  |

| All Pins                                     | I <sub>LTCH_UP</sub>  | EIA/JESD 78, Class II | 150  |     |     | mA    |  |  |

#### **Table 5.1 Absolute Maximum Ratings**

#### Note: In accordance with the Absolute Maximum Rating system (IEC 60134)

| PARAMETER                                    | SYMBOL              | CONDITIONS | MIN | ТҮР | МАХ                | UNITS |

|----------------------------------------------|---------------------|------------|-----|-----|--------------------|-------|

| 3.3V Supply Voltage<br>(VDD3.3 and VDDA3.3)  | V <sub>DD3.3</sub>  |            | 3.0 | 3.3 | 3.6                | V     |

| Input Voltage on Digital Pins                | VI                  |            | 0.0 |     | V <sub>DD3.3</sub> | V     |

| Input Voltage on Analog I/O<br>Pins (DP, DM) | V <sub>I(I/O)</sub> |            | 0.0 |     | V <sub>DD3.3</sub> | V     |

| Ambient Temperature                          | T <sub>A</sub>      |            | -40 |     | 85                 | °C    |

#### **Table 5.2 Recommended Operating Conditions**

#### **Table 5.3 Recommended External Clock Conditions**

| PARAMETER               | SYMBOL | CONDITIONS                                               | MIN | ТҮР             | MAX | UNITS |

|-------------------------|--------|----------------------------------------------------------|-----|-----------------|-----|-------|

| System Clock Frequency  |        | XO driven by the external clock; and no connection at XI |     | 24<br>(±100ppm) |     | MHz   |

| System Clock Duty Cycle |        | XO driven by the external clock; and no connection at XI | 45  | 50              | 55  | %     |

## **Chapter 6 Electrical Characteristics**

| PARAMETER            | SYMBOL                 | CONDITIONS                                                                          | MIN | ТҮР  | МАХ | UNITS |

|----------------------|------------------------|-------------------------------------------------------------------------------------|-----|------|-----|-------|

| Unconfigured Current | I <sub>AVG(UCFG)</sub> | Device Unconfigured                                                                 |     | 55   |     | mA    |

| FS Idle Current      | I <sub>AVG(FS)</sub>   | FS idle not data transfer                                                           |     | 55   |     | mA    |

| FS Transmit Current  | I <sub>AVG(FSTX)</sub> | FS current during data transmit                                                     |     | 60.5 |     | mA    |

| FS Receive Current   | I <sub>AVG(FSRX)</sub> | FS current during data receive                                                      |     | 57.5 |     | mA    |

| HS Idle Current      | I <sub>AVG(HS)</sub>   | HS idle not data transfer                                                           |     | 60.6 |     | mA    |

| HS Transmit Current  | I <sub>AVG(HSTX)</sub> | HS current during data transmit                                                     |     | 62.4 |     | mA    |

| HS Receive Current   | I <sub>AVG(HSRX)</sub> | HS current during data receive                                                      |     | 61.5 |     | mA    |

| Low Power Mode       | I <sub>DD(LPM)</sub>   | VBUS $15k\Omega$ pull-down and $1.5k\Omega$ pull-up resistor currents not included. |     | 83   |     | uA    |

#### Table 6.1 Electrical Characteristics: Supply Pins (Note 6.1)

Note 6.1  $V_{DD3.3}$  = 3.0 to 3.6V;  $V_{SS}$  = 0V;  $T_A$  = -40°C to 85°C; unless otherwise specified.

#### Table 6.2 DC Electrical Characteristics: Logic Pins (Note 6.2)

| PARAMETER                 | SYMBOL          | CONDITIONS             | MIN                         | ТҮР | МАХ                | UNITS |

|---------------------------|-----------------|------------------------|-----------------------------|-----|--------------------|-------|

| Low-Level Input Voltage   | V <sub>IL</sub> |                        | V <sub>SS</sub>             |     | 0.8                | V     |

| High-Level Input Voltage  | V <sub>IH</sub> |                        | 2.0                         |     | V <sub>DD3.3</sub> | V     |

| Low-Level Output Voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8mA  |                             |     | 0.4                | V     |

| High-Level Output Voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8mA | V <sub>DD3.3</sub><br>- 0.5 |     |                    | V     |

| Input Leakage Current     | ILI             |                        |                             |     | ± 1                | uA    |

| Pin Capacitance           | Cpin            |                        |                             |     | 4                  | pF    |

Note 6.2  $V_{DD3.3}$  = 3.0 to 3.6V;  $V_{SS}$  = 0V;  $T_A$  = -40°C to 85°C; unless otherwise specified.

| PARAMETER                                                           | SYMBOL             | CONDITIONS                                                   | MIN      | ТҮР  | МАХ   | UNITS |

|---------------------------------------------------------------------|--------------------|--------------------------------------------------------------|----------|------|-------|-------|

| FS FUNCTIONALITY                                                    |                    | l                                                            | 11       |      |       |       |

| Input levels                                                        |                    |                                                              |          |      |       |       |

| Differential Receiver Input<br>Sensitivity                          | V <sub>DIFS</sub>  | V(DP) - V(DM)                                                | 0.2      |      |       | V     |

| Differential Receiver<br>Common-Mode Voltage                        | V <sub>CMFS</sub>  |                                                              | 0.8      |      | 2.5   | V     |

| Single-Ended Receiver Low<br>Level Input Voltage                    | V <sub>ILSE</sub>  |                                                              |          |      | 0.8   | V     |

| Single-Ended Receiver High<br>Level Input Voltage                   | V <sub>IHSE</sub>  |                                                              | 2.0      |      |       | V     |

| Single-Ended Receiver<br>Hysteresis                                 | V <sub>HYSSE</sub> |                                                              | 0.050    |      | 0.150 | V     |

| Output Levels                                                       |                    |                                                              |          |      |       |       |

| Low Level Output Voltage                                            | V <sub>FSOL</sub>  | Pull-up resistor on DP; $R_L = 1.5 k\Omega$ to $V_{DD3.3}$   |          |      | 0.3   | V     |

| High Level Output Voltage                                           | V <sub>FSOH</sub>  | Pull-down resistor on DP,<br>DM;<br>$R_L = 15k\Omega$ to GND | 2.8      |      | 3.6   | V     |

| Termination                                                         |                    |                                                              | <u> </u> |      | 1     |       |

| Driver Output Impedance for<br>HS and FS                            | Z <sub>HSDRV</sub> | Steady state drive<br>(See Figure 6.1)                       | 40.5     | 45   | 49.5  | Ω     |

| Input Impedance                                                     | Z <sub>INP</sub>   | TX, RPU disabled                                             | 10       |      |       | MΩ    |

| Pull-up Resistor Impedance                                          | Z <sub>PU</sub>    | Bus Idle                                                     | 0.900    | 1.24 | 1.575 | kΩ    |

| Pull-up Resistor Impedance                                          | Z <sub>PURX</sub>  | Device Receiving                                             | 1.425    | 2.26 | 3.09  | kΩ    |

| Termination Voltage For Pull-<br>up<br>Resistor On Pin DP           | V <sub>TERM</sub>  |                                                              | 3.0      |      | 3.6   | V     |

| HS FUNCTIONALITY                                                    |                    |                                                              | <u> </u> |      | 1     |       |

| Input levels                                                        |                    |                                                              |          |      |       |       |

| HS Differential Input Sensitivity                                   | V <sub>DIHS</sub>  | V(DP) - V(DM)                                                | 100      |      |       | mV    |

| HS Data Signaling Common<br>Mode Voltage Range                      | V <sub>CMHS</sub>  |                                                              | -50      |      | 500   | mV    |

| HS Squelch Detection                                                | V <sub>HSSQ</sub>  | Squelch Threshold                                            |          |      | 100   | mV    |

| Threshold (Differential)                                            |                    | Unsquelch Threshold                                          | 150      |      |       | mV    |

| Output Levels                                                       |                    |                                                              |          |      |       |       |

| High Speed Low Level<br>Output Voltage (DP/DM<br>referenced to GND) | V <sub>HSOL</sub>  | 45Ω load                                                     | -10      |      | 10    | mV    |

| PARAMETER                                                            | SYMBOL              | CONDITIONS                                                                    | MIN  | ТҮР | МАХ  | UNITS |

|----------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------|------|-----|------|-------|

| High Speed High Level<br>Output Voltage (DP/DM<br>referenced to GND) | V <sub>HSOH</sub>   | 45Ω load                                                                      | 360  |     | 440  | mV    |

| High Speed IDLE Level<br>Output Voltage (DP/DM<br>referenced to GND) | V <sub>OLHS</sub>   | 45Ω load                                                                      | -10  |     | 10   | mV    |

| Chirp-J Output Voltage<br>(Differential)                             | V <sub>CHIRPJ</sub> | HS termination resistor<br>disabled, pull-up resistor<br>connected. 45Ω load. | 700  |     | 1100 | mV    |

| Chirp-K Output Voltage<br>(Differential)                             | V <sub>CHIRPK</sub> | HS termination resistor disabled, pull-up resistor connected. 45Ω load.       | -900 |     | -500 | mV    |

| Leakage Current                                                      |                     |                                                                               |      |     |      |       |

| OFF-State Leakage Current                                            | I <sub>LZ</sub>     |                                                                               |      |     | ± 1  | uA    |

| Port Capacitance                                                     |                     |                                                                               |      |     |      |       |

| Transceiver Input Capacitance                                        | C <sub>IN</sub>     | Pin to GND                                                                    |      | 5   | 10   | pF    |

Note 6.3  $V_{DD3.3}$  = 3.0 to 3.6V;  $V_{SS}$  = 0V;  $T_A$  = -40°C to 85°C; unless otherwise specified.

| PARAMETER                                           | SYMBOL           | CONDITIONS                                                             | MIN | ТҮР | МАХ               | UNITS |

|-----------------------------------------------------|------------------|------------------------------------------------------------------------|-----|-----|-------------------|-------|

| FS Output Driver Timing                             |                  |                                                                        |     |     |                   |       |

| Rise Time                                           | T <sub>FSR</sub> | $C_L$ = 50pF; 10 to 90% of $ V_{OH}$ - $V_{OL} $                       | 4   |     | 20                | ns    |

| Fall Time                                           | T <sub>FFF</sub> | $C_{L} = 50 pF; 10 \text{ to } 90\% \text{ of}$<br>$ V_{OH} - V_{OL} $ | 4   |     | 20                | ns    |

| Output Signal Crossover<br>Voltage                  | V <sub>CRS</sub> | Excluding the first transition from IDLE state                         | 1.3 |     | 2.0               | V     |

| Differential Rise/Fall Time<br>Matching             | FRFM             | Excluding the first transition from IDLE state                         | 90  |     | 111.1             | %     |

| HS Output Driver Timing                             |                  |                                                                        |     |     |                   |       |

| Differential Rise Time                              | T <sub>HSR</sub> |                                                                        | 500 |     |                   | ps    |

| Differential Fall Time                              | T <sub>HSF</sub> |                                                                        | 500 |     |                   | ps    |

| Driver Waveform<br>Requirements                     |                  | Eye pattern of Template 1 in USB 2.0 specification                     |     |     | See<br>Figure 6.2 |       |

| High Speed Mode Timing                              |                  |                                                                        |     |     |                   |       |

| Receiver Waveform<br>Requirements                   |                  | Eye pattern of Template 4 in USB 2.0 specification                     |     |     | See<br>Figure 6.2 |       |

| Data Source Jitter and<br>Receiver Jitter Tolerance |                  | Eye pattern of Template 4 in USB 2.0 specification                     |     |     | See<br>Figure 6.2 |       |

Note 6.4  $V_{DD3.3}$  = 3.0 to 3.6V;  $V_{SS}$  = 0V;  $T_A$  = -40°C to 85°C; unless otherwise specified.

🕈 smsc

| PARAMETER      | SYMBOL          | CONDITIONS                                       | MIN | ТҮР | МАХ | UNITS |

|----------------|-----------------|--------------------------------------------------|-----|-----|-----|-------|

| UTMI Timing    |                 |                                                  |     |     |     |       |

| DATA[7:0]      | T <sub>PD</sub> | Output Delay. Measured<br>from PHY output to the | 2   |     | 5   | ns    |

| RXVALID        |                 | rising edge of CLKOUT                            |     |     |     |       |

| RXACTIVE       |                 |                                                  |     |     |     |       |

| RXERROR        |                 |                                                  |     |     |     |       |

| LINESTATE[1:0] |                 |                                                  |     |     |     |       |

| TXREADY        |                 |                                                  |     |     |     |       |

| DATA[7:0]      | Τ <sub>SU</sub> | Setup Time. Measured<br>from PHY input to the    | 5   |     |     | ns    |

| TXVALID        |                 | rising edge of CLKOUT.                           |     |     |     |       |

| OPMODE[1:0]    |                 |                                                  |     |     |     |       |

| XCVRSELECT     |                 |                                                  |     |     |     |       |

| TERMSELECT     |                 |                                                  |     |     |     |       |

| DATA[7:0]      | Т <sub>Н</sub>  | Hold time. Measured from the rising egde of      | 0   |     |     | ns    |

| TXVALID        |                 | CLKOUT to the PHY input signal edge.             |     |     |     |       |

| OPMODE[1:0]    |                 | Signar Cayo.                                     |     |     |     |       |

| XCVRSELECT     |                 |                                                  |     |     |     |       |

| TERMSELECT     |                 |                                                  |     |     |     |       |

#### Table 6.5 Dynamic Characteristics: Digital UTMI Pins (Note 6.5)

Note 6.5  $V_{DD3.3}$  = 3.0 to 3.6V;  $V_{SS}$  = 0V;  $T_A$  = -40°C to 85°C; unless otherwise specified.

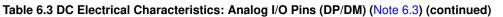

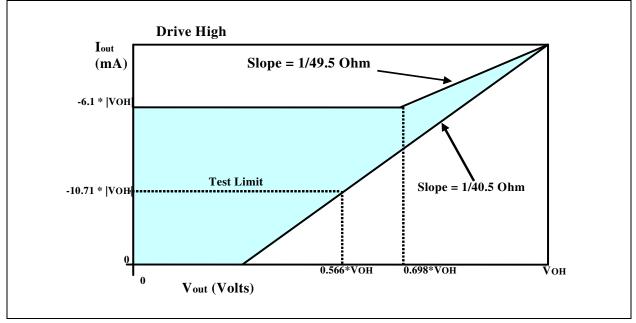

## 6.1 Driver Characteristics of Full-Speed Drivers in High-Speed Capable Transceivers

The USB3280 uses a differential output driver to drive the USB data signal onto the USB cable. Figure 6.1 Full-Speed Driver VOH/IOH Characteristics for High-speed Capable Transceiveron page 17 shows the V/I characteristics for a full-speed driver which is part of a high-speed capable transceiver. The normalized V/I curve for the driver must fall entirely inside the shaded region. The V/I region is bounded by the minimum driver impedance above (40.5 Ohm) and the maximum driver impedance below (49.5 Ohm). The output voltage must be within 10mV of ground when no current is flowing in or out of the pin.

Figure 6.1 Full-Speed Driver VOH/IOH Characteristics for High-speed Capable Transceiver

Figure 6.2 Full-Speed Driver VOL/IOL Characteristics for High-speed Capable Transceiver

## 6.2 High-speed Signaling Eye Patterns

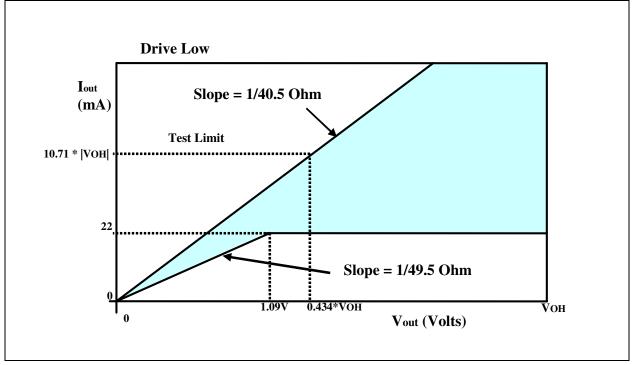

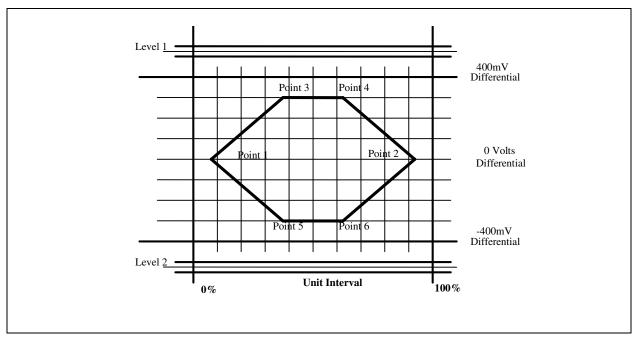

High-speed USB signals are characterized using eye patterns. For measuring the eye patterns 4 points have been defined (see Figure 6.3). The Universal Serial Bus Specification Rev.2.0 defines the eye patterns in several 'templates'. The two templates that are relevant to the PHY are shown below.

Figure 6.3 Eye Pattern Measurement Planes

The eye pattern in Figure 6.4 defines the transmit waveform requirements for a hub (measured at TP2 of Figure 6.3) or a device without a captive cable (measured at TP3 of Figure 6.3). The corresponding signal levels and timings are given in table below. Time is specified as a percentage of the unit interval (UI), which represents the nominal bit duration for a 480 Mbit/s transmission rate.

Figure 6.4 Eye Pattern for Transmit Waveform and Eye Pattern Definition

|         | VOLTAGE LEVEL (D+, D-)                                       | TIME (% OF UNIT INTERVAL) |

|---------|--------------------------------------------------------------|---------------------------|

| Level 1 | 525mV in UI following a transition,<br>475mV in all others   | N/A                       |

| Level 2 | -525mV in UI following a transition,<br>-475mV in all others | N/A                       |

| Point 1 | 0V                                                           | 7.5% UI                   |

| Point 2 | 0V                                                           | 92.5% UI                  |

| Point 3 | 300mV                                                        | 37.5% UI                  |

| Point 4 | 300mV                                                        | 62.5% UI                  |

| Point 5 | -300mV                                                       | 37.5% UI                  |

| Point 6 | -300mV                                                       | 62.5% UI                  |

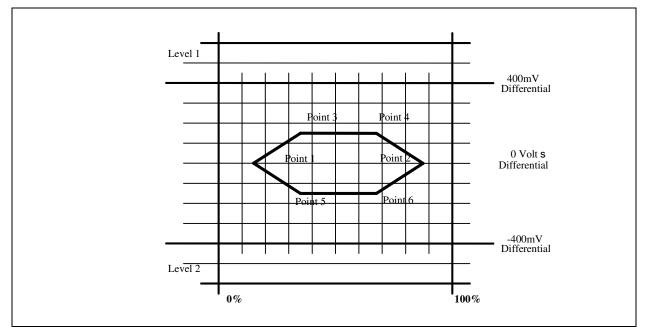

The eye pattern in Figure 6.5 defines the receiver sensitivity requirements for a hub (signal applied at test point TP2 of Figure 6.3) or a device without a captive cable (signal applied at test point TP3 of Figure 6.3). The corresponding signal levels and timings are given in the table below. Timings are given as a percentage of the unit interval (UI), which represents the nominal bit duration for a 480 Mbit/s transmission rate.

Figure 6.5 Eye Pattern for Receive Waveform and Eye Pattern Definition

|         | VOLTAGE LEVEL (D+, D-) | TIME (% OF UNIT INTERVAL) |

|---------|------------------------|---------------------------|

| Level 1 | 575mV                  | N/A                       |

| Level 2 | -575mV                 | N/A                       |

| Point 1 | 0V                     | 15% UI                    |

| Point 2 | 0V                     | 85% UI                    |

| Point 3 | 150mV                  | 35% UI                    |

| Point 4 | 150mV                  | 65% UI                    |

| Point 5 | -150mV                 | 35% UI                    |

| Point 6 | -150mV                 | 65% UI                    |

## Chapter 7 Functional Overview

Figure 2.1 on page 7 shows the functional block diagram of the USB3280. Each of the functions is described in detail below.

### 7.1 Modes of Operation

The USB3280 supports an 8-bit bi-directional parallel interface.

- CLKOUT runs at 60MHz

- The 8-bit data bus (DATA[7:0]) is used for transmit when TXVALID = 1

- The 8-bit data bus (DATA[7:0]) is used for receive when TXVALID = 0

### 7.2 System Clocking

This block connects to either an external 24MHz crystal or an external clock source and generates a 480MHz multi-phase clock. The clock is used in the CRC block to over-sample the incoming received data, resynchronize the transmit data, and is divided down to 60MHz (CLKOUT) which acts as the system byte clock. The PLL block also outputs a clock valid signal to the other parts of the transceiver when the clock signal is stable. All UTMI signals are synchronized to the CLKOUT output. The behavior of the CLKOUT is as follows:

- Produce the first CLKOUT transition no later than 5.6ms after negation of SUSPENDN. The CLKOUT signal frequency error is less than 10% at this time.

- The CLKOUT signal will fully meet the required accuracy of ±500ppm no later than 1.4ms after the first transition of CLKOUT.

In HS mode there is one CLKOUT cycle per byte time. The frequency of CLKOUT does not change when the PHY is switched between HS to FS modes. In FS mode there are 5 CLKOUT cycles per FS bit time, typically 40 CLKOUT cycles per FS byte time. If a received byte contains a stuffed bit then the byte boundary can be stretched to 45 CLKOUT cycles, and two stuffed bits would result in a 50 CLKOUT cycles.

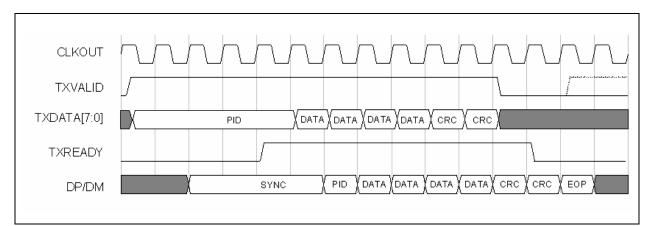

Figure 7.1 shows the relationship between CLKOUT and the transmit data transfer signals in FS mode. TXREADY is only asserted for one CLKOUT per byte time to signal the SIE that the data on the DATA lines has been read by the PHY. The SIE may hold the data on the DATA lines for the duration of the byte time. Transitions of TXVALID must meet the defined setup and hold times relative to CLKOUT.

| CLKOUT      |                                       |

|-------------|---------------------------------------|

| TXVALID     |                                       |

| TXDATA[7:0] | PID XDATA1 X DATA2 X DATA3 // X DATA4 |

| TXREADY     |                                       |

Figure 7.1 FS CLK Relationship to Transmit Data and Control Signals

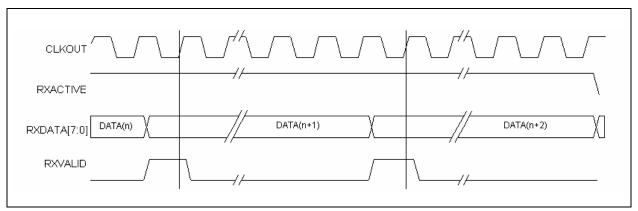

Figure 7.2 shows the relationship between CLKOUT and the receive data control signals in FS mode. RXACTIVE "frames" a packet, transitioning only at the beginning and end of a packet. However transitions of RXVALID may take place any time 8 bits of data are available. Figure 7.1 also shows how RXVALID is only asserted for one CLKOUT cycle per byte time even though the data may be presented for the full byte time. The XCVRSELECT signal determines whether the HS or FS timing relationship is applied to the data and control signals.

Figure 7.2 FS CLK Relationship to Receive Data and Control Signals

### 7.3 Clock and Data Recovery Circuit

This block consists of the Clock and Data Recovery Circuit and the Elasticity Buffer. The Elasticity Buffer is used to compensate for differences between the transmitting and receiving clock domains. The USB 2.0 specification defines a maximum clock error of  $\pm 1000$  ppm of drift.

## 7.4 TX Logic