# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# USB4715

# USB 2.0 Hi-Speed Hub Controller with FlexConnect on all Ports

## **Highlights**

- Single-chip USB 2.0 Hi-Speed hub controller with FlexConnect

- 1 upstream port for USB Host / OTG connection

- 4 downstream ports with FlexConnect capability on all ports

- USB Battery Charging, revision 1.2, support on downstream ports (DCP, CDP, SDP)

- Battery charging support for China and Apple<sup>®</sup> profiles

- USB to SMBus, I<sup>2</sup>S<sup>™</sup>, SPI, UART, and GPIO

- Apple authentication support

- I<sup>2</sup>S for audio support; Asynchronous In, Adaptive Out, 48KHz, two channels, 16-bits/channel

- Flexible I<sup>2</sup>S capabilities with firmware update

## **Target Applications**

- Media hubs

- Infotainment head units

- Automotive breakout boxes

- Docks

- Monitors

- Point of sale

- · Host switch for diagnostic mode

- · Host switch for field firmware upgrades

## **Product Features**

#### FlexConnect

Downstream port able to swap with upstream port, allowing USB host capable devices to control other devices on the hub

- MultiTRAK<sup>™</sup>

- Dedicated Transaction Translator per port

- PortMap

- Configurable port mapping and disable sequencing

- PortSwap

- Configurable differential intra-pair signal swapping

- PHYBoost

- Programmable USB transceiver drive strength for recovering signal integrity

- VariSense<sup>™</sup>

- Programmable USB receiver sensitivity

- · USB Link Power Management (LPM) support

- · Vendor Specific Messaging (VSM) support

- Architected for USB Power Delivery (PD) 3.0 support

- 32-bit embedded microcontroller in the hub executes PD stack and system policy manager

- Interfaces to Microchip UPD350 Power Delivery Interface device

- Power delivery stack runs from external SPI Flash

- SPI Flash provides flexibility for specification revisions and evolving system needs

- Enhanced OEM configuration options available through external straps, OTP configuration or SMBus Slave port

- 3.3 V supply voltage

- AEC-Q100 compliance

- Microchip parts are tested to meet or exceed the requirements of the AEC-Q100 automotive qualification standards

- · Packaging

- 48-pin VQFN (7 x 7 mm)

- Environmental

- Commercial temperature range (0°C to +70°C)

- Industrial temperature range (-40° to +85°C)

- Grade 3 Automotive temperature range (-40° to +85°C)

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 1.0 PREFACE

## 1.1 General Terms

#### TABLE 1-1: GENERAL TERMS

| Term                   | Description                                                                                                                                                                                                                                                                                              |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC                    | Analog-to-Digital Converter                                                                                                                                                                                                                                                                              |

| Byte                   | 8 bits                                                                                                                                                                                                                                                                                                   |

| CDC                    | Communication Device Class                                                                                                                                                                                                                                                                               |

| EOP                    | End of Packet                                                                                                                                                                                                                                                                                            |

| EP                     | Endpoint                                                                                                                                                                                                                                                                                                 |

| FIFO                   | First In First Out buffer                                                                                                                                                                                                                                                                                |

| FS                     | Full-Speed                                                                                                                                                                                                                                                                                               |

| GPIO                   | General Purpose I/O                                                                                                                                                                                                                                                                                      |

| HS                     | Hi-Speed                                                                                                                                                                                                                                                                                                 |

| Hub Feature Controller | The Hub Feature Controller, sometimes called a Hub Controller for short is the internal processor used to enable the unique features of the USB Controller Hub. This is not to be confused with the USB Hub Controller that is used to communicate the hub status back to the Host during a USB session. |

| l <sup>2</sup> C       | Inter-Integrated Circuit                                                                                                                                                                                                                                                                                 |

| LS                     | Low-Speed                                                                                                                                                                                                                                                                                                |

| lsb                    | Least Significant Bit                                                                                                                                                                                                                                                                                    |

| LSB                    | Least Significant Byte                                                                                                                                                                                                                                                                                   |

| msb                    | Most Significant Bit                                                                                                                                                                                                                                                                                     |

| MSB                    | Most Significant Byte                                                                                                                                                                                                                                                                                    |

| N/A                    | Not Applicable                                                                                                                                                                                                                                                                                           |

| NC                     | No Connect                                                                                                                                                                                                                                                                                               |

| ОТР                    | One Time Programmable                                                                                                                                                                                                                                                                                    |

| РСВ                    | Printed Circuit Board                                                                                                                                                                                                                                                                                    |

| РНҮ                    | Physical Layer                                                                                                                                                                                                                                                                                           |

| PLL                    | Phase Lock Loop                                                                                                                                                                                                                                                                                          |

| RESERVED               | Refers to a reserved bit field or address. Unless otherwise noted, reserved bits must<br>always be zero for write operations. Unless otherwise noted, values are not guaran-<br>teed when reading reserved bits. Unless otherwise noted, do not read or write to<br>reserved addresses.                  |

| SDK                    | Software Development Kit                                                                                                                                                                                                                                                                                 |

| SMBus                  | System Management Bus                                                                                                                                                                                                                                                                                    |

| UUID                   | Universally Unique IDentifier                                                                                                                                                                                                                                                                            |

| WORD                   | 16 bits                                                                                                                                                                                                                                                                                                  |

## 1.2 Buffer Types

## TABLE 1-2: BUFFER TYPE DESCRIPTIONS

| Buffer | Description                                                                                                                                                                                                                             |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | Input.                                                                                                                                                                                                                                  |

| IS     | Input with Schmitt trigger.                                                                                                                                                                                                             |

| 04     | Output buffer with 4mA sink and 4mA source.                                                                                                                                                                                             |

| 012    | Output buffer with 12mA sink and 12mA source.                                                                                                                                                                                           |

| OD12   | Open-drain output with 12mA sink.                                                                                                                                                                                                       |

| PU     | Internal pull-up. Unless otherwise noted in the pin description, internal pull-ups are always enabled.                                                                                                                                  |

|        | Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled high, an external resistor must be added.  |

| PD     | Internal pull-down. Unless otherwise noted in the pin description, internal pull-downs are always enabled.                                                                                                                              |

|        | Internal pull-down resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled low, an external resistor must be added. |

| ICLK   | Crystal oscillator input pin.                                                                                                                                                                                                           |

| OCLK   | Crystal oscillator output pin.                                                                                                                                                                                                          |

| I/O-U  | Analog input/output defined in USB specification.                                                                                                                                                                                       |

| I-R    | RBIAS.                                                                                                                                                                                                                                  |

| A      | Analog.                                                                                                                                                                                                                                 |

| Р      | Power pin.                                                                                                                                                                                                                              |

## 1.3 Pin Reset States

The pin reset state definitions are detailed in Table 1-3. Refer to Section 3.0, "Pin Descriptions and Configuration" for details on individual pin reset states.

TABLE 1-3: PIN RESET STATE LEGEND

| Symbol | Description                                      |

|--------|--------------------------------------------------|

| A/P    | Analog/Power Input                               |

| Z      | Hardware disables output driver (high impedance) |

| PD-15k | Hardware enables internal $15k\Omega$ pull-down  |

| PD-67k | Hardware enables internal $67k\Omega$ pull-down  |

| PU-67k | Hardware enables internal $67k\Omega$ pull-up    |

| USB    | USB line                                         |

### **1.4 Reference Documents**

- 1. Universal Serial Bus Revision 2.0 Specification, http://www.usb.org

- 2. AN2341 USB4715 FlexConnect Operation, http://www.microchip.com

- 3. AN2439 Configuration of the USB491x/USB492x/USB4715, http://www.microchip.com

- 4. AN2437 USB to GPIO Bridging with USB4715 and USB49xx, http://www.microchip.com

- 5. AN2438 USB to I<sup>2</sup>C Bridging with USB4715 and USB49xx, http://www.microchip.com

- 6. AN2430 USB to SPI Bridging with USB4715 and USB49xx, http://www.microchip.com

- 7. AN2426 USB to UART Bridging with Microchip USB4715, USB4916, and USB4927, http://www.microchip.com

- 8. Battery Charging Specification, Revision 1.2, Dec. 07, 2010, http://www.usb.org

- 9. I<sup>2</sup>C-Bus Specification, Version 1.1, http://www.nxp.com/documents/user\_manual/UM10204.pdf

- 10. I<sup>2</sup>S-Bus Specification, http://www.nxp.com/acrobat\_download/various/I2SBUS.pdf

- 11. System Management Bus Specification, Version 1.0, http://smbus.org/specs

# 2.0 INTRODUCTION

## 2.1 General Description

The Microchip USB4715 USB 2.0 Hi-Speed hub controller is a single-chip device targeted for automotive, industrial, and commercial applications. Primary functions of the device include: multiple downstream USB ports supporting USB 2.0 Low Speed/Full Speed, single USB 2.0 Hi-Speed upstream connection to a USB host / OTG port, battery charging support for BC1.2, Apple and China charging profiles, USB I/O bridging, and an on-chip microcontroller.

The USB4715 employs unique FlexConnect USB functionality, whereby one of the downstream ports can be reconfigured to become an upstream port, allowing the host or master capability to be switched to equipment on any of the other ports. This port/host becomes the master of the new USB bus, while the other ports can connect as USB devices, or become dedicated charging ports.

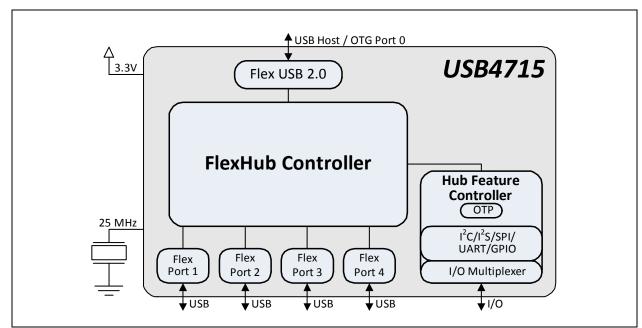

The USB4715 is available in commercial (0°C to +70°C), industrial and Automotive Grade 3 (-40°C to +85°C) temperature ranges. An internal block diagram of the USB4715 is shown in Figure 2-1.

## FIGURE 2-1: INTERNAL BLOCK DIAGRAM

## 3.0 PIN DESCRIPTIONS AND CONFIGURATION

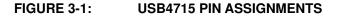

The pin assignments for the USB4715 are detailed in Section 3.1, "USB4715 Pin Assignments". Pin descriptions are provided in Section 3.2, "Pin Descriptions".

## 3.1 USB4715 Pin Assignments

The device pin diagram for the USB4715 can be seen in Figure 3-1. Table 3-1 provides a USB4715 pin assignments table. Pin descriptions are provided in Section 3.2, "Pin Descriptions".

**Note:** Configuration straps are identified by an underlined symbol name. Signals that function as configuration straps must be augmented with an external resistor when connected to a load.

| Pin                                            | Pin Name                          | Reset  | Pin | Pin Name                        | Reset  |

|------------------------------------------------|-----------------------------------|--------|-----|---------------------------------|--------|

| 1                                              | PORT_CTL_GANG                     | PD-67k | 25  | VDDIO33                         | A/P    |

| 2                                              | CONFIG STRAP 1                    | Z      | 26  | SQI_D2                          | Z      |

| 3                                              | CONFIG STRAP 2                    | Z      | 27  | SQI_D3                          | Z      |

| 4                                              | FLEX_USB_DP1/ <u>PRT_DIS_P1</u>   | PD-15k | 28  | PROG_FUNC6                      | Z      |

| 5                                              | FLEX_USB_DM1/PRT_DIS_M1           | PD-15k | 29  | PROG_FUNC5                      | Z      |

| 6                                              | FLEX_USB_DP2/ <u>PRT_DIS_P2</u>   | PD-15k | 30  | PROG_FUNC4                      | Z      |

| 7                                              | FLEX_USB_DM2/PRT_DIS_M2           | PD-15k | 31  | VDDIO33                         | A/P    |

| 8                                              | FLEX_USB_DP4/ <u>PRT_DIS_P4</u>   | PD-15k | 32  | PROG_FUNC3                      | Z      |

| 9                                              | FLEX_USB_DM4/PRT_DIS_M4           | PD-15k | 33  | PROG_FUNC2                      | Z      |

| 10                                             | PRT_CTL4/OCS4                     | PD-67k | 34  | RESET_N                         | PD-67k |

| 11                                             | PROG_FUNC7                        | PD-67k | 35  | VBUS_DET                        | Z      |

| 12                                             | VDDIO33                           | A/P    | 36  | VDDIO33                         | A/P    |

| 13                                             | TEST1                             | Z      | 37  | PROG_FUNC1                      | Z      |

| 14                                             | TEST2                             | Z      | 38  | PROG_FUNC8                      | Z      |

| 15                                             | TEST3                             | Z      | 39  | VDDIO33                         | A/P    |

| 16                                             | PRT_CTL3/OCS3                     | PD-67k | 40  | FLEX_USB_DP3/ <u>PRT_DIS_P3</u> | PD-15k |

| 17                                             | PRT_CTL2/OCS2                     | PD-67k | 41  | FLEX_USB_DM3/ <u>PRT_DIS_M3</u> | PD-15k |

| 18                                             | PRT_CTL1/OCS1                     | PD-67k | 42  | USBH_DP0                        | USB    |

| 19                                             | VDDCR12                           | A/P    | 43  | USBH_DM0                        | USB    |

| 20                                             | VDDIO33                           | A/P    | 44  | TESTEN/ATEST                    | A/P    |

| 21                                             | SPI_CLK/SQI_CLK                   | Z      | 45  | XTALO                           | A/P    |

| 22                                             | SPI_DO/SQI_D0                     | PD-67k | 46  | XTALI/CLK_IN                    | A/P    |

| 23                                             | SPI_DI/SQI_D1/ <u>CFG_BC_EN</u>   | Z      | 47  | VDDPLLREF33                     | A/P    |

| 24                                             | SPI_CE_N/SQI_CE_N/<br>CFG_NON_REM | PU-67k | 48  | RBIAS                           | A/P    |

| Exposed Pad (VSS) must be connected to ground. |                                   |        |     |                                 |        |

### TABLE 3-1: USB4715 PIN ASSIGNMENTS

## 3.2 Pin Descriptions

## TABLE 3-2:PIN DESCRIPTIONS

| Name                                  | Symbol           | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|---------------------------------------|------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| _                                     | USB Interface    |                |                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| USB Upstream<br>D+                    | USBH_DP0         | I/O-U          | Upstream USB 2.0 Data Plus (D+)                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| USB Upstream<br>D-                    | USBH_DM0         | I/O-U          | Upstream USB 2.0 Data Minus (D-)                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| USB<br>Downstream<br>Ports 4-1 D+     | FLEX_USB_DP[4:1] | I/O-U          | Downstream USB 2.0 Ports 4-1 Data Plus (D+)                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| USB<br>Downstream<br>Ports 4-1 D-     | FLEX_USB_DM[4:1] | I/O-U          | Downstream USB 2.0 Ports 4-1 Data Minus (D-)                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                                       |                  | USB Port C     | Control Pins                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

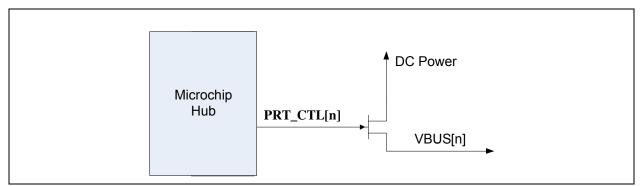

| USB Ports 4-1<br>Power Enable         | PRT_CTL[4:1]     | I/O12          | When the downstream port is enabled, this pin is set as<br>an input with an internal pull-up resistor applied. The<br>internal pull-up enables power to the downstream port<br>while the pin monitors for an active low overcurrent sig-<br>nal assertion from an external current monitor on USB<br>port 4. This pin will change to an output and be driven<br>low when the port is disabled by configuration or by the<br>host control. |  |  |  |

| USB Ports 4-1<br>Overcurrent<br>Sense | OCS[4:1]         | I/O12          | Overcurrent sense for ports 4-1.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Gang Power                            | PRT_CTL_GANG     | I/O12          | This pin becomes the port control pin for all downstream<br>ports when the hub is configured for ganged port power<br>control mode. All port power controllers are controlled<br>from this pin when the hub is configured for ganged port<br>power mode.                                                                                                                                                                                  |  |  |  |

|                                       |                  | SPI Inter      | face Pins                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| SPI Clock                             | SPI_CLK          | I/O4           | SPI clock.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| SPI Data Out                          | SPI_DO           | I/O4           | SPI output data. If the SPI interface is enabled, this signal is the data out for the SPI port.                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| SPI Data In                           | SPI_DI           | I/O4           | <ul> <li>SPI input data. If the SPI interface is enabled, this signal must have a weak pull-down applied at all times to prevent floating.</li> <li>Note: If SPI interface is not utilized, this pin cannot be left floating. It must be connected per the CFG_BC_EN pin description.</li> </ul>                                                                                                                                          |  |  |  |

## TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

| Name                             | Symbol         | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI Chip<br>Enable               | SPI_CE_EN      | I/O4           | Active low SPI chip enable input. If the SPI interface is<br>enabled, this pin must be driven high in powerdown<br>states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                  |                |                | <b>Note:</b> If SPI interface is not utilized, this pin cannot be left floating. It must be connected per the CFG_NON_REM pin description.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                  |                | SQI Inter      | face Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SQI Clock                        | SQI_CLK        | I/O4           | SQI clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SQI Data 0-3                     | SQI_D[0:3]     | I/O4           | SQI Data 0-3. If the SQI interface is enabled, these signals function as Data 0 through 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SQI Chip<br>Enable               | SQI_CE_EN      | I/O4           | Active low SQI chip enable input. If the SQI interface is enabled, this pin requires an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                  |                |                | <b>Note:</b> If SQI interface is not utilized, this pin cannot be left floating. It must be connected per the CFG_NON_REM pin description.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                  |                | Miscell        | aneous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Programmable<br>Functions 8-1    | PROG_FUNC[8:1] | I/O12          | These selectable function pins can be assigned a role<br>via the <u>CONFIG STRAP [2:1]</u> pins, OTP configuration,<br>or SMBus configuration. Refer to Section 3.3.4,<br>"PROG_FUNC[8:1] Configuration (CON-<br>FIG_STRAP_[2:1])" for additional information.                                                                                                                                                                                                                                                                                                                                   |

| VBUS<br>Detection                | VBUS_DET       | I              | This signal detects the state of the upstream bus power. When designing a detachable hub, this pin must be connected to the VBUS power pin of the upstream USB port through a resistor divider (50 k $\Omega$ by 100 k $\Omega$ ) to provide 3.3 V.<br>For self-powered applications with a permanently attached host, this pin must be connected to either 3.3 V or 5.0 V through a resistor divider to provide 3.3 V.<br>In embedded applications, <b>VBUS_DET</b> may be controlled (toggled) when the host desires to renegotiate a connection without requiring a full reset of the device. |

| Reset Input                      | RESET_N        | I              | This active low signal is used by the system to reset the device. The active low pulse should be at least 1 $\mu s$ wide.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Bias Resistor                    | RBIAS          | I-R            | A 12.0 k $\Omega \pm 1.0\%$ resistor is attached from ground to this<br>pin to set the transceiver's internal bias settings. Place<br>the resistor as close to the device as possible with a<br>dedicated, low impedance connection to the GND plane.                                                                                                                                                                                                                                                                                                                                            |

| External 25 MHz<br>Crystal Input | XTALI          | ICLK           | External 25 MHz crystal input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Name                                             | Symbol                | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------|-----------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External 25 MHz<br>Reference Clock<br>Input      | CLK_IN                | ICLK           | External reference clock input.<br>The device may alternatively be driven by a single-<br>ended clock oscillator. When this method is used,<br>XTALO should be left unconnected.                                                                                                                                                                     |

| External 25 MHz<br>Crystal Output                | XTALO                 | OCLK           | External 25 MHz crystal output.                                                                                                                                                                                                                                                                                                                      |

| Test                                             | TESTEN                | A              | Test pin.<br>This signal is used for test purposes and must always<br>be connected to ground.                                                                                                                                                                                                                                                        |

| Analog Test                                      | ATEST                 | A              | Analog test pin.<br>This signal is used for test purposes and must always<br>be connected to ground.                                                                                                                                                                                                                                                 |

| Test 1                                           | TEST1                 | A              | Test 1 pin. This signal is used for test purposes and must always be pulled-up to $3.3V$ via a $4.7$ k $\Omega$ resistor.                                                                                                                                                                                                                            |

| Test 2                                           | TEST2                 | A              | Test 2 pin. This signal is used for test purposes and must always be pulled-down to ground via a 4.7 k $\Omega$ resistor.                                                                                                                                                                                                                            |

| Test 3                                           | TEST3                 | A              | Test 3 pin. This signal is used for test purposes and must always be pulled-down to ground via a 4.7 k $\Omega$ resistor.                                                                                                                                                                                                                            |

|                                                  |                       | Configurat     | tion Straps                                                                                                                                                                                                                                                                                                                                          |

| Device Mode<br>Configuration<br>Straps 2-1       | CONFIG STRAP [2:1]    | I              | Device mode configuration straps 2-1.<br>These configuration straps are used to select the<br>device's mode of operation. See Note 3-1.<br>Refer to Section 3.3.4, "PROG_FUNC[8:1] Configura-<br>tion (CONFIG_STRAP_[2:1])" for additional information.                                                                                              |

| Port 4-1 D+<br>Disable<br>Configuration<br>Strap | <u>PRT DIS P[4:1]</u> | I              | <ul> <li>Port 4-1 D+ Disable configuration strap.</li> <li>These configuration straps are used in conjunction with the corresponding <u>PRT DIS M[4:1]</u> straps to disable the related port (5-1). See Note 3-1.</li> <li>Both USB data pins for the corresponding port must be tied to 3.3V to disable the associated downstream port.</li> </ul> |

## TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

| Name                                             | Symbol                | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                   |  |

|--------------------------------------------------|-----------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Port 4-1 D-<br>Disable<br>Configuration<br>Strap | <u>PRT DIS M[4:1]</u> | I              | Port 4-1 D- Disable configuration strap.<br>These configuration straps are used in conjunction with<br>the corresponding <u>PRT DIS P[4:1]</u> straps to disable the<br>related port (5-1). See Note 3-1.<br>Both USB data pins for the corresponding port must be<br>tied to 3.3V to disable the associated downstream port. |  |

| Non-Removable<br>Ports<br>Configuration<br>Strap | CFG NON REM           | I              | Non-Removable Ports Configuration Strap.<br>This configuration strap controls the number of reported non-removable ports. See Note 3-1.                                                                                                                                                                                       |  |

| Battery Charging<br>Configuration<br>Strap       | <u>CFG BC EN</u>      | I              | Battery Charging Configuration Strap.<br>This configuration strap controls the number of BC 1.2<br>enabled downstream ports. See Note 3-1.                                                                                                                                                                                    |  |

|                                                  | Power/Ground          |                |                                                                                                                                                                                                                                                                                                                               |  |

| +3.3V I/O Power<br>Supply Input                  | VDDIO33               | Р              | +3.3V I/O power supply input.                                                                                                                                                                                                                                                                                                 |  |

| +3.3V Analog<br>Power Supply<br>Input            | VDDPLLREF33           | Р              | +3.3V master bias / PLL regulator supply input.                                                                                                                                                                                                                                                                               |  |

| +1.2V Core<br>Power Supply<br>Output             | VDDCR12               | Р              | +1.2V digital core power supply output.<br><b>Note:</b> This signal requires connection of a 1uF low-<br>ESR capacitor to ground.                                                                                                                                                                                             |  |

| Ground                                           | VSS                   | Р              | Ground pins.                                                                                                                                                                                                                                                                                                                  |  |

**Note 3-1** Configuration strap values are latched on Power-On Reset (POR) and the rising edge of **RESET\_N** (external chip reset). Configuration straps are identified by an underlined symbol name. Signals that function as configuration straps must be augmented with an external resistor when connected to a load. For additional information, refer to Section 3.3, "Configuration Straps and Programmable Functions".

## 3.3 Configuration Straps and Programmable Functions

Configuration straps are multi-function pins that are used during Power-On Reset (POR) or external chip reset (**RESET\_N**) to determine the default configuration of a particular feature. The state of the signal is latched following deassertion of the reset. Configuration straps are identified by an underlined symbol name. This section details the various device configuration straps and associated programmable pin functions.

**Note:** The system designer must guarantee that configuration straps meet the timing requirements specified in Section 9.6.2, "Power-On and Configuration Strap Timing" and Section 9.6.3, "Reset and Configuration Strap Timing". If configuration straps are not at the correct voltage level prior to being latched, the device may capture incorrect strap values.

#### 3.3.1 PORT DISABLE CONFIGURATION (<u>PRT DIS P[4:1]</u> / <u>PRT DIS M[4:1]</u>)

The <u>PRT DIS P[4:1]</u> / <u>PRT DIS M[4:1]</u> configuration straps are used in conjunction to disable the related port (4-1).

For <u>**PRT DIS P**x</u> (where *x* is the corresponding port 4-1):

**0** = Port *x* D+ Enabled

1 = Port *x* D+ Disabled

For <u>**PRT DIS M**</u>*x* (where *x* is the corresponding port 4-1):

0 = Port x D- Enabled

**1** = Port *x* D- Disabled

**Note:** Both <u>**PRT DIS P**</u>*x* and <u>**PRT DIS M**</u>*x* (where *x* is the corresponding port) must be tied to 3.3 V to disable the associated downstream port.

#### 3.3.2 NON-REMOVABLE PORT CONFIGURATION (CFG NON REM)

The <u>CFG NON REM</u> configuration strap is used to configure the non-removable port settings of the device to one of five settings. These modes are selected by the configuration of an external resistor on the <u>CFG NON REM</u> pin. The resistor options are a 200 k $\Omega$  pull-down, 200 k $\Omega$  pull-up, 10 k $\Omega$  pull-down, 10 k $\Omega$  pull-up, and 10  $\Omega$  pull-down, as shown in Table 3-3.

| CFG NON REM Resistor Value | Setting                       |

|----------------------------|-------------------------------|

| 200 kΩ Pull-Down           | Port 1- removable             |

| 200 kΩ Pull-Up             | Port 1 non-removable          |

| 10 kΩ Pull-Down            | Port 1, 2 non-removable       |

| 10 kΩ Pull-Up              | Port 1, 2, 3 non-removable    |

| 10 Ω Pull-Down             | Port 1, 2, 3, 4 non-removable |

## TABLE 3-3: CFG NON REM RESISTOR ENCODING

#### 3.3.3 BATTERY CHARGING CONFIGURATION (<u>CFG\_BC\_EN</u>)

The <u>CFG BC EN</u> configuration strap is used to configure the battery charging port settings of the device to one of five settings. These modes are selected by the configuration of an external resistor on the <u>CFG BC EN</u> pin. The resistor options are a 200 k $\Omega$  pull-down, 200 k $\Omega$  pull-up, 10 k $\Omega$  pull-down, 10 k $\Omega$  pull-up, and 10  $\Omega$  pull-down, as shown in Table 3-4.

| CFG NON REM Resistor Value | Setting                          |

|----------------------------|----------------------------------|

| 200 kΩ Pull-Down           | No battery charging              |

| 200 kΩ Pull-Up             | Port 1 battery charging          |

| 10 kΩ Pull-Down            | Port 1, 2 battery charging       |

| 10 kΩ Pull-Up              | Port 1, 2, 3 battery charging    |

| 10 Ω Pull-Down             | Port 1, 2, 3, 4 battery charging |

## TABLE 3-4:CFG BC ENRESISTOR ENCODING

#### 3.3.4 PROG\_FUNC[8:1] CONFIGURATION (CONFIG STRAP [2:1])

The USB4715 provides 8 programmable function pins (PROG\_FUNC[8:1]). These pins can be configured to 6 predefined configurations via the <u>CONFIG STRAP [2:1]</u> pins. These configurations are selected via external resistors on the <u>CONFIG STRAP [2:1]</u> pins, as detailed in Table 3-5. Resistor values and combinations not detailed in Table 3-5 are reserved and should not be used.

| Mode            | <u>CONFIG STRAP 2</u><br>Resistor Value | <u>CONFIG STRAP 1</u><br>Resistor Value |

|-----------------|-----------------------------------------|-----------------------------------------|

| Configuration 1 | 200 kΩ Pull-Down                        | 200 kΩ Pull-Down                        |

| Configuration 2 | 200 kΩ Pull-Down                        | 200 kΩ Pull-Up                          |

| Configuration 3 | 200 kΩ Pull-Down                        | 10 kΩ Pull-Down                         |

| Configuration 4 | 200 kΩ Pull-Down                        | 10 kΩ Pull-Up                           |

| Configuration 5 | 200 kΩ Pull-Down                        | 10 Ω Pull-Down                          |

| Configuration 6 | 200 kΩ Pull-Down                        | 10 Ω Pull-Up                            |

### TABLE 3-5: CONFIG\_STRAP\_[2:1] RESISTOR ENCODING

A summary of the configuration pin assignments for each of the 6 configurations is provided in Table 3-6. For details on behavior of each programmable function, refer to Table 3-7.

### TABLE 3-6: PROG\_FUNC[8:1] FUNCTION ASSIGNMENT

| Pin         | Configuration<br>1 | Configuration 2 | Configuration 3 | Configuration<br>4 | Configuration 5 | Configuration<br>6 |

|-------------|--------------------|-----------------|-----------------|--------------------|-----------------|--------------------|

| PROG_FUNC_1 | SMB1_DAT           | SMB1_DAT        | SMB1_DAT        | SMB1_DAT           | SMB1_DAT        | SMB1_DAT           |

| PROG_FUNC_2 | I2S_LRCK           | UART_TX         | CONNECT_IND1    | UART_TX            | UART_TX         | I2S_LRCK           |

| PROG_FUNC_3 | I2S_SDOUT          | UART_RX         | CONNECT_IND2    | UART_RX            | UART_RX         | I2S_SDOUT          |

| PROG_FUNC_4 | I2S_SDIN           | GPIO6           | CONNECT_IND3    | GPIO6              | GPIO6           | I2S_SDIN           |

| PROG_FUNC_5 | I2S_MCLK           | GPIO8           | GPIO8           | GPIO8              | SMB2_DAT        | I2S_MCLK           |

| PROG_FUNC_6 | I2S_SCK            | GPIO10          | GPIO10          | GPIO10             | SMB2_CLK        | I2S_SCK            |

| PROG_FUNC_7 | MIC_DET            | GPIO11          | CONNECT_IND4    | GPIO11             | GPIO11          | GPIO11             |

| PROG_FUNC_8 | SMB1_CLK           | SMB1_CLK        | SMB1_CLK        | SMB1_CLK           | SMB1_CLK        | SMB1_CLK           |

#### TABLE 3-7: PROGRAMMABLE FUNCTIONS DESCRIPTIONS

| Function               | Buffer<br>Type | Description                                                                                     |  |

|------------------------|----------------|-------------------------------------------------------------------------------------------------|--|

| UART Interface         |                |                                                                                                 |  |

| UART_TX                | O12            | UART Transmit                                                                                   |  |

| UART_RX                | I              | UART Receive                                                                                    |  |

| SMBus Master Interface |                |                                                                                                 |  |

| SMB1_CLK               | I/OD12         | SMBus Master Clock                                                                              |  |

| SMB1_DAT               | I/OD12         | SMBus Master Data                                                                               |  |

| SMBus Slave Interface  |                |                                                                                                 |  |

| SMB2_CLK               | I/OD12         | SMBus Slave Clock                                                                               |  |

|                        |                | For proper SMBus slave operation, an external 10 $k\Omega$ resistor is required on this signal. |  |

## TABLE 3-7: PROGRAMMABLE FUNCTIONS DESCRIPTIONS (CONTINUED)

| Function  | Buffer<br>Type | Description                                                                                     |

|-----------|----------------|-------------------------------------------------------------------------------------------------|

| SMB2_DAT  | I/OD12         | SMBus Slave Data                                                                                |

|           |                | For proper SMBus slave operation, an external 10 $k\Omega$ resistor is required on this signal. |

|           |                | I <sup>2</sup> S Interface                                                                      |

| I2S_SCK   | O12            | I <sup>2</sup> S Continuous Serial Clock                                                        |

| I2S_LRCK  | O12            | I <sup>2</sup> S Word Select / Left-Right Clock                                                 |

| I2S_MCLK  | O12            | I <sup>2</sup> S Master Clock                                                                   |

| I2S_SDOUT | O12            | I <sup>2</sup> S Serial Data Out                                                                |

| I2S_SDIN  | I              | I <sup>2</sup> S Serial Data In                                                                 |

| MIC_DET   | I              | I <sup>2</sup> S MIC Plug Detect                                                                |

|           |                | 0 = No microphone plugged into the audio jack<br>1 = Microphone plugged into the audio jack     |

| Miscellaneous    |       |                                                                                                                     |  |

|------------------|-------|---------------------------------------------------------------------------------------------------------------------|--|

| GPIOx            | I/O12 | General Purpose Inputs/Outputs<br>( <i>x</i> = 6, 8, 10-11)                                                         |  |

| CONNECT_IND[4:1] | O12   | Downstream Port 4-1 Connect Indicator<br>1 = USB 2.0 or USB 1.1 connection to port<br>0 = Nothing connected to port |  |

# 4.0 DEVICE CONNECTIONS

## 4.1 **Power Connections**

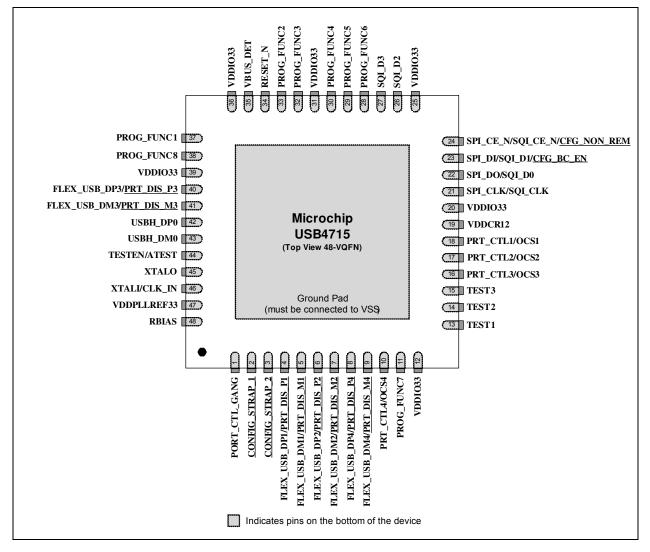

Figure 4-1 illustrates the device power connections.

### FIGURE 4-1: POWER CONNECTIONS

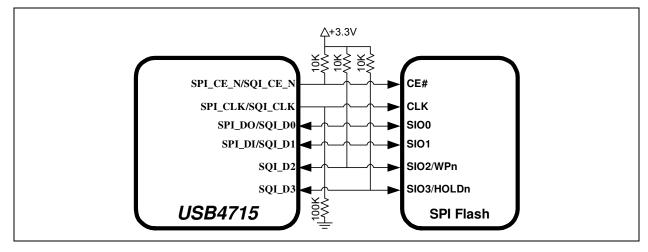

## 4.2 SPI Flash Connections

Figure 4-2 illustrates the device SPI Flash connections.

## FIGURE 4-2: SPI FLASH CONNECTIONS

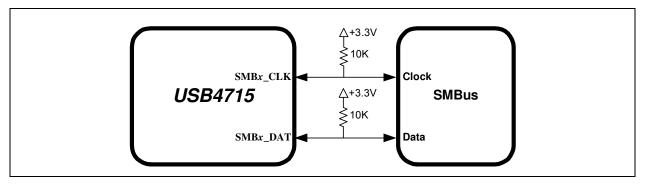

## 4.3 SMBus Connections

Figure 4-3 illustrates the device SMBus Connections.

## FIGURE 4-3: SMBUS CONNECTIONS

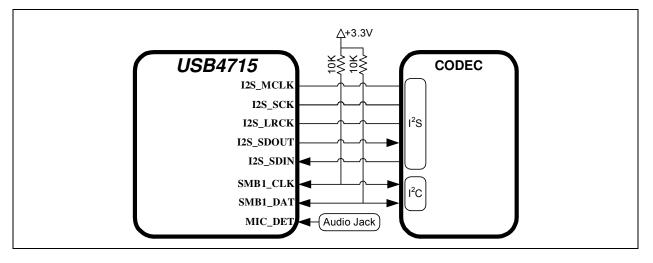

## 4.4 I<sup>2</sup>S Connections

Figure 4-4 illustrates the device I<sup>2</sup>S connections.

## FIGURE 4-4: I<sup>2</sup>S CONNECTIONS

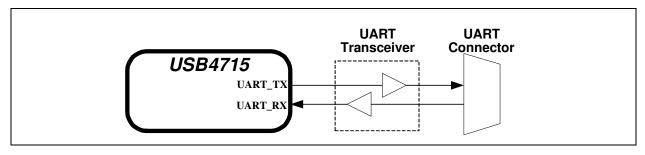

## 4.5 UART Connections

Figure 4-5 illustrates the device UART connections.

## FIGURE 4-5: UART CONNECTIONS

## 5.0 MODES OF OPERATION

The device provides two main modes of operation: Standby Mode and Hub Mode. These modes are controlled via the **RESET\_N** pin, as shown in Table 5-1.

## TABLE 5-1: MODES OF OPERATION

| RESET_N Input | Summary                                                                                                                                                                                                                                                                                |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | <b>Standby Mode</b> : This is the lowest power mode of the device. No functions are active other than monitoring the <b>RESET_N</b> input. All port interfaces are high impedance and the PLL is halted. Refer to Section 8.9, "Resets" for additional information on <b>RESET_N</b> . |

| 1             | <b>Hub (Normal) Mode</b> : The device operates as a configurable USB hub. This mode has various sub-modes of operation, as detailed in Figure 5-1. Power consumption is based on the number of active ports, their speed, and amount of data received.                                 |

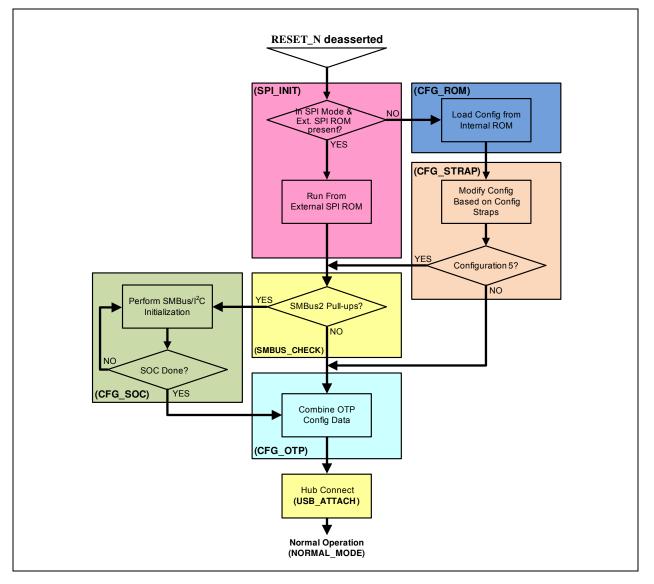

The flowchart in Figure 5-1 details the modes of operation and details how the device traverses through the Hub Mode stages (shown in bold). The remaining sub-sections provide more detail on each stage of operation.

## FIGURE 5-1: HUB MODE FLOWCHART

## 5.1 Boot Sequence

### 5.1.1 STANDBY MODE

If the **RESET\_N** pin is asserted, the hub will be in Standby Mode. This mode provides a very low power state for maximum power efficiency when no signaling is required. This is the lowest power state. In Standby Mode all downstream ports are disabled, the USB data pins are held in a high-impedance state, all transactions immediately terminate (no states saved), all internal registers return to their default state, the PLL is halted, and core logic is powered down in order to minimize power consumption. Because core logic is powered off, no configuration settings are retained in this mode and must be re-initialized after **RESET\_N** is negated high.

### 5.1.2 SPI INITIALIZATION STAGE (SPI\_INIT)

The first stage, the initialization stage, occurs on the deassertion of **RESET\_N**. In this stage, the internal logic is reset, the PLL locks if a valid clock is supplied, and the configuration registers are initialized to their default state. The internal firmware then checks for an external SPI ROM. The firmware looks for an external SPI flash device that contains a valid signature of "2DFU" (device firmware upgrade) beginning at address 0xFFFA. If a valid signature is found, then the SPI Firmware/external SPI ROM is enabled and the code execution begins at address 0x0000 in the external SPI device. If a valid signature is not found, then execution continues from internal ROM (CFG\_ROM stage).

When using an external SPI ROM, a minimum of 2.2 Mbit is required, and 60 MHz or faster SPI ROM must be used. Both 1- and 2-bit SPI ROM are supported. For optimum throughput, a 2-bit SPI ROM is recommended. Both mode 0 and mode 3 SPI flashes are supported.

If the system is not strapped for SPI Mode, code execution will continue from internal ROM (CFG\_ROM stage).

#### 5.1.3 CONFIGURATION FROM INTERNAL ROM STAGE (CFG\_ROM)

In this stage, the internal firmware loads the default values from the internal ROM. Most of the hub configuration registers, USB descriptors, electrical settings, etc. will be initialized in this state even when running from SPI.

#### 5.1.4 CONFIGURATION STRAP READ STAGE (CFG\_STRAP)

In this stage, the firmware reads the following configuration straps to override the default values:

- CONFIG STRAP [2:1]

- PRT DIS P[4:1]

- PRT DIS M[4:1]

- CFG NON REM

- <u>CFG BC EN</u>

If the <u>CONFIG STRAP [2:1]</u> pins are set to Configuration 5, the device will move to the SMBUS\_CHECK stage, otherwise it move to the CFG\_OTP stage. Refer to Section 3.3, "Configuration Straps and Programmable Functions" for information on usage of the various device configuration straps.

#### 5.1.5 SMBUS CHECK STAGE (SMBUS\_CHECK)

Based on the **PROG\_FUNC[8:1]** configuration selected (refer to Section 3.3.4, "PROG\_FUNC[8:1] Configuration (CON-FIG\_STRAP\_[2:1])"), the firmware will check for the presence of external pull up resistors on the SMBus slave programmable function pins. If 10K pull-ups are detected on both pins, the device will be configured as an SMBus slave, and the next state will be CFG\_SOC. If a pull-up is not detected in either of the pins, the next state is CFG\_OTP.

## 5.1.6 SOC CONFIGURATION STAGE (CFG\_SOC)

In this stage, the SOC can modify any of the default configuration settings specified in the integrated ROM, such as USB device descriptors, port electrical settings, and control features such as downstream battery charging.

In this stage the firmware will wait indefinitely for the SMBus/I<sup>2</sup>C configuration there is no time limit on this stage. The external SMBus master writes to register 0xFF, to end the configuration in legacy mode. In non-legacy mode, the SMBus command USB\_ATTACH (opcode 0xAA55) or USB\_ATTACH\_WITH\_SMBUS (opcode 0xAA56) will finish the configuration.

## 5.1.7 OTP CONFIGURATION STAGE (CFG\_OTP)

Once the SOC has indicated that it is done with configuration, all configuration data is combined in this stage. The default data, the SOC configuration data, and the OTP data are all combined in the firmware and the device is programmed.

© 2017 Microchip Technology Inc.

**Note:** Changes to hub registers made in OTP memory space are not visible via SMBus during CFG\_SOC stage. Any register which is modified via SMBus during SOC\_CFG and also modified in the OTP memory will exit the configuration stages with the value as programmed in the OTP memory.

#### 5.1.8 HUB CONNECT STAGE (USB\_ATTACH)

Once the hub registers are updated through default values, SMBus master, and OTP, the device firmware will enable attaching the USB host by setting the USB\_ATTACH bit in the HUB\_CMD\_STAT register. The device will remain in the Hub Connect stage indefinitely until the VBUS function is deasserted/assertion of external RESET\_N pin.

#### 5.1.9 NORMAL MODE (NORMAL\_MODE)

Lastly, the hub enters Normal Mode of operation. In this stage full USB operation is supported under control of the USB Host on the upstream port. The device will remain in the normal mode until the operating mode is changed by the USB Host.

If **RESET\_N** is asserted low, then Standby Mode is entered. The device may then be placed into any of the designated hub stages. Asserting a soft disconnect on the upstream port will cause the hub to return to the Hub Connect stage until the soft disconnect is negated.

# 6.0 DEVICE CONFIGURATION

The device supports a large number of features (some mutually exclusive), and must be configured in order to correctly function when attached to a USB host controller. The hub can be configured either internally or externally depending on the implemented interface.

Microchip provides a comprehensive software programming tool, MPLAB Connect (formerly ProTouch2), for OTP configuration of various USB4715 functions and registers. All configuration is to be performed via the MPLAB Connect Configurator programming tool. For additional information on this tool, refer to th MPLAB Connect Configurator programming tool product page at http://www.microchip.com/design-centers/usb/mplab-connect-configurator.

Additional information on configuring the USB4715 via SMBus is provided in the *AN2439* - *Configuration of the USB491x/USB492x/USB4715*" application note, which contains details on the hub operational mode, SOC configuration stage, OTP configuration, USB configuration, and configuration register definitions. This application note, along with other USB4715 resources, can be found on the Microchip USB4715 product page at www.microchip.com/USB4715.

**Note:** Device configuration straps and programmable pins are detailed in Section 3.3, "Configuration Straps and Programmable Functions," on page 12. Refer to Section 7.0, "Device Interfaces" for detailed information on each device interface.

## 7.0 DEVICE INTERFACES

The USB4715 provides multiple interfaces for configuration, external memory access, etc.. This section details the various device interfaces and their usage:

- SPI/SQI Master Interface

- SMBus/I2C Master/Slave Interfaces

- I2S Interface

- UART Interface

**Note:** For details on how to enable each interface, refer to Section 3.3, "Configuration Straps and Programmable Functions".

For information on device connections, refer to Section 4.0, "Device Connections". For information on device configuration, refer to Section 6.0, "Device Configuration".

Microchip provides a comprehensive software programming tool, MPLAB Connect (formerly ProTouch2), for configuring the USB4715 functions, registers and OTP memory. All configuration is to be performed via the MPLAB Connect Configurator programming tool. For additional information on this tool, refer to th MPLAB Connect Configurator programming tool product page at http://www.microchip.com/design-centers/usb/mplab-connect-configurator.

## 7.1 SPI/SQI Master Interface

The SPI/SQI controller has two basic modes of operation: execution of an external hub firmware image, or the USB to SPI bridge. On power up, the firmware looks for an external SPI flash device that contains a valid signature of 2DFU (device firmware upgrade) beginning at address 0xFFFA. If a valid signature is found, then the external ROM mode is enabled and the code execution begins at address 0x0000 in the external SPI device. If a valid signature is not found, then execution continues from internal ROM and the SPI interface can be used as a USB to SPI bridge.

The second mode of operation is the USB to SPI bridge operation. Additional details on this feature can be found in Section 8.5, "USB to SPI Bridging" as well as the AN2430 - USB to SPI Bridging with USB4715 and USB49xx application note.

Table 7-1 details how the associated pins are mapped in SPI vs. SQI mode

| SPI Mode | SQI Mode | Description                      |

|----------|----------|----------------------------------|

| SPI_CE_N | SQI_CE_N | SPI/SQI Chip Enable (Active Low) |

| SPI_CLK  | SQI_CLK  | SPI/SQI Clock                    |

| SPI_DO   | SQI_D0   | SPI Data Out; SQI Data I/O 0     |

| SPI_DI   | SQI_D1   | SPI Data In; SQI Data I/O 1      |

| -        | SQI_D2   | SQI Data I/O 2                   |

| -        | SQI_D3   | SQI Data I/O 3                   |

TABLE 7-1:SPI/SQI PIN USAGE

Note: For SPI timing information, refer to Section 9.6.8, "SPI/SQI Timing".

## 7.2 SMBus/I<sup>2</sup>C Master/Slave Interfaces

The USB4715 provides two independent SMBus/I<sup>2</sup>C controllers SMBus 1 and SMBus 2, which can be used to access internal device run time registers or program the internal OTP memory. SMBus 1 is used as the USB to SMBus/I<sup>2</sup>C bridge, and SMBus 2 is used as the slave interface. The device contains two 128 byte buffers to enable simultaneous master/slave operation and to minimize firmware overhead in processed SMBus/I<sup>2</sup>C packets.

The SMBus 1 and SMBus 2 interfaces are assigned to programmable pins (PROG\_FUNC\_x) and therefore the device must be programmed into specific configurations to enable both interfaces. SMBus 1 is available in all CON-FIG\_STRAP[1:2] settings. SMBus 2 is available only with specific CONFIG\_STRAP[1:2] settings. Refer to Section 3.3.4, "PROG\_FUNC[8:1] Configuration (CONFIG\_STRAP\_[2:1])" for additional information.

**Note:** For SMBus/I<sup>2</sup>C timing information, refer to Section 9.6.5, "SMBus Timing" and Section 9.6.6, "I2C Timing".

## 7.3 I<sup>2</sup>S Interface

The USB4715 provides an integrated  $I^2S$  interface to facilitate the connection of digital audio devices. The  $I^2S$  interface conforms to the voltage, power, and timing characteristics/specifications as set forth in the  $I^2S$ -Bus Specification, and consists of the following signals:

- I2S\_SDIN: Serial Data Input

- I2S\_SDOUT: Serial Data Output

- I2S\_SCK: Serial Clock

- I2S\_LRCK: Left/Right Clock (SS/FSYNC)

- I2S\_MCLK: Master Clock

Each audio connection is half-duplex, so **I2S\_SDOUT** exists only on the transmit side and **I2S\_SDIN** exists only on the receive side of the interface. Some codecs refer to the Serial Clock (**I2S\_SCK**) as Baud/Bit Clock (BCLK). Also, the Left/ Right Clock is commonly referred to as LRC or LRCK. The I<sup>2</sup>S and other audio protocols refer to LRC as Word Select (WS).

The following codec is supported by default:

Analog Devices ADAU1961 (24-bit 96KHz)