Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **VINCULUM**

**BINDING USB TECHNOLOGIES**

# **VDrive2**

**Vinculum VNC1L Module**

http://www.vinculum.com

### 1. Introduction and Features

#### 1.1 Introduction

The VDrive2 module provides an easy solution for adding a USB Flash disk interface to an existing product. Only four signal lines plus 5V supply and ground are required to be connected. Using the Vinculum VDAP firmware the VNC1L's I/O interface can be selected between the serial UART or SPI using the on-board jumper pins. Not only is the VDrive2 ideal for evaluation and development of VNC1L designs, but also its neat enclosure and attractive quantity discount structure makes this module suitable for incorporation into finished product designs. The VDrive2 is ideal for commercial products such as domestic goods, set top box, etc., as well as industrial products such as data loggers, software upgradable products, etc.

The Vinculum VNC1L is the first of F.T.D.I.'s Vinculum family of Embedded SoC USB host controller integrated circuit devices. Not only is it able to handle the USB Host Interface, and data transfer functions but owing to the inbuilt MCU and embedded Flash memory, Vinculum can encapsulate the USB device classes as well. When interfacing to mass storage devices such as USB Flash drives, Vinculum also transparently handles the FAT file structure communicating via UART, SPI or parallel FIFO interfaces via a simple to implement command set. Vinculum provides a new cost effective solution for providing USB Host capability into products that previously did not have the hardware resources available.

#### 1.2 Features

- Uses F.T.D.I.'s VNC1L embedded USB host controller I.C. device.

- USB 'A' type socket to connect USB Flash disk.

- Traffic indicator LED.

- 2 mm (0.08") pitch 8 pin connector.

- 8-way header interconnect cable provided.

- Only four signals to connect, excluding power and ground.

- Jumper selectable UART or SPI interfaces.

- Single 5V supply input.

- Uses Vinculum VDAP firmware and command set.

- Enclosure with snap in place clips allows for easy front panel mounting.

- Program or update firmware via USB Flash disk or via UART interface.

- VNC1L firmware programming control pins PROG# and RESET# brought out onto internal jumper interface (only accessible on internal module PCB)

- VDrive2 is a Pb-free, RoHS complaint development module.

- Schematics, and firmware files available for download from the Vinculum website.

## 2. Pin Out

### 2.1 VDrive2 Pin Out

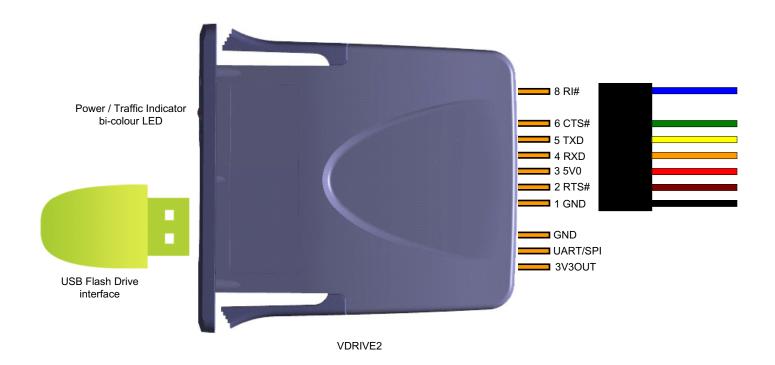

Figure 1 - VDrive2 Pin Out - UART interface.

Table 1 - Port Selection Jumper Pins

| UART/SPI  | I/O Mode    |  |  |

|-----------|-------------|--|--|

| Pull-Up   | Serial UART |  |  |

| Pull-Down | SPI         |  |  |

### 2.2 UART Interface Signal Descriptions

Table 2 - Data and Control Bus Signal Mode Options - UART Interface

| Pin No. | Name | Туре   | Description                                                             |  |

|---------|------|--------|-------------------------------------------------------------------------|--|

| 1       | GND  | PWR    | Signal ground                                                           |  |

| 2       | RTS# | Output | equest To Send Control Output / Handshake signal                        |  |

| 3       | 5V0  | PWR    | 5V supply input                                                         |  |

| 4       | RXD  | Input  | Receive asynchronous data input                                         |  |

| 5       | TXD  | Output | Transmit asynchronous data output                                       |  |

| 6       | CTS# | Input  | Clear To Send Control Input / Handshake signal                          |  |

| 7       | NC   | -      | No Connect                                                              |  |

| 8       | RI#  | Input  | Ring Indicator Control Input. Used to resume the Vinculum from suspend. |  |

Table 3 - Data and Control Bus Signal Mode Options - SPI Interface

| Pin No. | Name | Туре   | Description                     |

|---------|------|--------|---------------------------------|

| 5       | SCLK | Input  | SPI Clock input, 12MHz maximum. |

| 4       | SDI  | Input  | SPI Serial Data Input           |

| 2       | SDO  | Output | SPI Serial Data Output          |

| 6       | CS   | Input  | SPI Chip Select Input           |

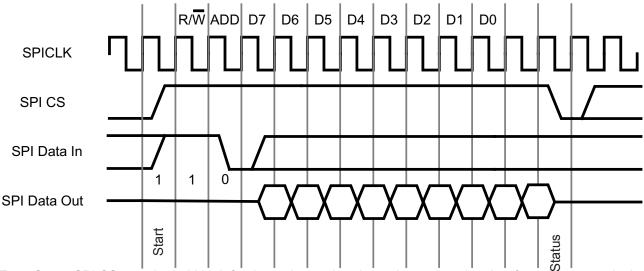

Figure 2 - SPI Slave Data Read Cycle

From Start - SPI CS must be held high for the entire read cycle, and must be taken low for at least one clock period after the read is completed. The first bit on SPI Data In is the R/W bit - inputting a '1' here allows data to be read from the chip. The next bit is the address bit, ADD, which is used to indicate whether the data register ('0') or the status register ('1') is read from. During the SPI read cycle a byte of data will start being output on SPI Data Out on the next clock cycle after the address bit, MSB first. After the data has been clocked out of the chip, the status of SPI Data Out should be checked to see if the data read is new data. A '0' level here on SPI Data Out means that the data read is new data. A '1' indicates that the data read is old data, and the read cycle should be repeated to get new data. Remember that CS must be held low for at least one clock period before being taken high again to continue with the next read or write cycle.

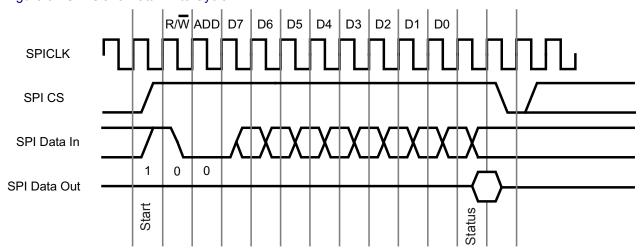

Figure 3 - SPI Slave Data Write Cycle

From Start - SPI CS must be held high for the entire write cycle, and must be taken low for at least one clock period after the write is completed. The first bit on SPI Data In is the R/W bit - inputting a '0' here allows data to be written to the chip. The next bit is the address bit, ADD, which is used to indicate whether the data register ('0') or the status register ('1') is written to. During the SPI write cycle a byte of data can be input to SPI Data In on the next clock cycle after the address bit, MSB first. After the data has been clocked in to the chip, the status of SPI Data Out should be

checked to see if the data read was accepted. A '0' level on SPI Data Out means that the data write was accepted. A '1' indicates that the internal buffer is full, and the write should be repeated. Remember that CS must be held low for at least one clock period before being taken high again to continue with the next read or write cycle.

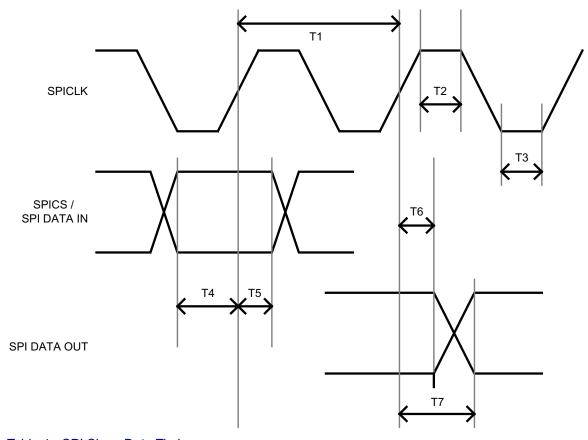

Figure 4 - SPI Slave Data Timing Diagrams

Table 4 - SPI Slave Data Timing

| Time | Description       | Min | Typical | Max | Unit |

|------|-------------------|-----|---------|-----|------|

| T1   | SPICLK Period     | 83  | -       | -   | ns   |

| T2   | SPICLK High       | 20  | -       | -   | ns   |

| Т3   | SPICLK Low        | 20  | -       | -   | ns   |

| T4   | Input Setup Time  | 10  | -       | -   | ns   |

| T5   | Input Hold Time   | 10  | -       | -   | ns   |

| Т6   | Output Hold Time  | 2   | -       | -   | ns   |

| T7   | Output Valid Time | -   | -       | 20  | ns   |

Table 5 - Status Register (ADD = '1')

| Bit | Description |

|-----|-------------|

| 0   | RXF#        |

| 1   | TXE#        |

| 2   | -           |

| 3   | -           |

| 4   | RXF IRQEn   |

| 5   | TXE IRQEn   |

| 6   | -           |

| 7   | -           |

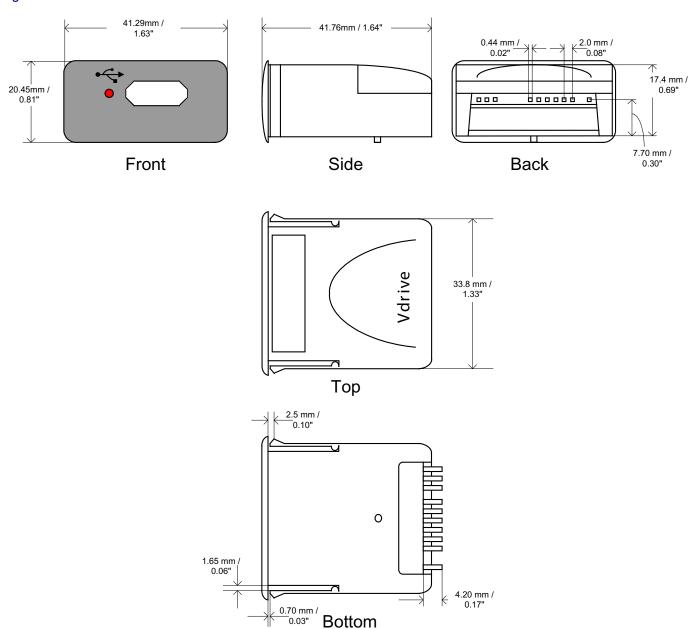

## 3. VDRIVE2 Dimensions

Figure 5 - VDRIVE2 mechanical dimensions

Fully detailed mechanical drawings for the VDrive2 enclosure are available on request from FTDI technical support.

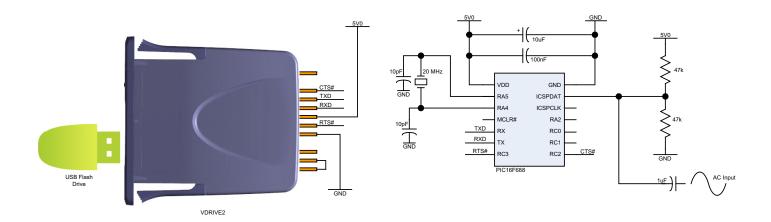

## 4. Application Example - VDRIVE2 to PIC Micro Interface

Figure 6 - Datalogging to a USB Flash disk with the VDrive2

By adding a PIC microcontroller and a few other components, the VDRIVE2 module can be turned into a Flash disk based data logger. Fig 5 shows the schematic of this simple application. The AC signal input is connected to the 10-bit analogue to digital converter on board the Microchip PIC. The PIC code takes a pre-defined number of samples and then writes the corresponding ASCII values to a comma separated value (CSV) file on the USB flash disk attached to the VDRIVE2 module. Vinculum's DOS like ASCII commands simplify the task of file handling. An extended ASCII command set is designed for use with a terminal whilst a shortened hexadecimal version is used with a microcontroller.

Consult the Vinculum VDAP firmware datasheet for full details of the command set used by the VDrive2.

#### Copyright © Future Technology Devices International Limited, 2007.

Version 0.95 - Initial Datasheet Created August 2006 Version 0.99 - Update March 2007

Neither the whole nor any part of the information contained in, or the product described in this manual, may be adapted or reproduced in any material or electronic form without the prior written consent of the copyright holder.

This product and its documentation are supplied on an as-is basis and no warranty as to their suitability for any particular purpose is either made or implied.

Future Technology Devices International Ltd. will not accept any claim for damages howsoever arising as a result of use or failure of this product. Your statutory rights are not affected.

This product or any variant of it is not intended for use in any medical appliance, device or system in which the failure of the product might reasonably be expected to result in personal injury.

This document provides preliminary information that may be subject to change without notice.

#### **Contact FTDI**

#### **Head Office -**

**Future Technology Devices International Ltd.**

373 Scotland Street, Glasgow G5 8QB, United Kingdom

Tel.: +(44) 141 429 2777 Fax.: +(44) 141 429 2758

E-Mail (Sales) : sales1@ftdichip.com

E-Mail (Support) : support1@ftdichip.com

E-Mail (General Enquiries): admin1@ftdichip.com

#### **Regional Sales Offices -**

## Future Technology Devices International Ltd. (Taiwan)

4F, No 18-3,

Sec. 6 Mincyuan East Road,

Neihu District, Taipei 114, Taiwan, R.o.C.

Tel.: +886 2 8791 3570 Fax: +886 2 8791 3576

E-Mail (Sales): tw.sales1@ftdichip.com

E-Mail (Support): tw.support@ftdichip.com

E-Mail (General Enquiries): tw.admin@ftdichip.com

## Future Technology Devices International Ltd.

(USA

7235 NW Evergreen Parkway Suite 600 Hillsboro, OR 97124-5803

USA

Tel.: +1 (503) 547-0988 Fax: +1 (503) 547-0987

E-Mail (Sales): us.sales@ftdichip.com

E-Mail (Support): us.support@ftdichip.com

E-Mail (General Enquiries): us.admin@ftdichip.com

Website URL: http://www.ftdichip.com