Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

US Headquarters 2950 Red Hill Ave, Costa Mesa California, USA 92626 Office: 714.913.2200 Fax: 714.913.2202 www.vikingtechnology.com

# **Datasheet for:**

# MicroSD Card 3.0

**PSFUSDxxxxQxxxx**

# **Legal Information**

Copyright© 2017 Sanmina Corporation. All rights reserved. The information in this document is proprietary and confidential to Sanmina Corporation. No part of this document may be reproduced in any form or by any means or used to make any derivative work (such as translation, transformation, or adaptation) without written permission from Sanmina. Sanmina reserves the right to revise this documentation and to make changes in content from time to time without obligation on the part of Sanmina to provide notification of such revision or change.

Sanmina provides this documentation without warranty, term or condition of any kind, either expressed or implied, including, but not limited to, expressed and implied warranties of merchantability, fitness for a particular purpose, and non-infringement. While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made. In no event will Sanmina be liable for damages arising directly or indirectly from any use of or reliance upon the information contained in this document. Sanmina may make improvements or changes in the product(s) and/or the program(s) described in this documentation at any time.

Sanmina, Viking Technology, Viking Modular Solutions, and the Viking logo are trademarks of Sanmina Corporation. Other company, product or service names mentioned herein may be trademarks or service marks of their respective owners.

# **Revision History**

| Date    | Revision | Description                                                                     | Checked by |

|---------|----------|---------------------------------------------------------------------------------|------------|

| 1/23/17 | А        | Initial release based on PSFSD3xxxxQxxxx_B (change PN'S and mechanical drawing) |            |

|         |          |                                                                                 |            |

|         |          |                                                                                 |            |

|         |          |                                                                                 |            |

# **Ordering Information**

| Spec   | Viking P/N        | Grade | NAND Process | Density GB | Temperature |

|--------|-------------------|-------|--------------|------------|-------------|

| SD 3.0 | VPFUSD0512QI7STH  | С     | TSB 24nm SLC | 0.512      | -25 to 85°C |

| SD 3.0 | VPFUSD10242QIESTH | С     | TSB 24nm SLC | 1          | -25 to 85°C |

| SD 3.0 | VPFUSD2048QIFSTH  | С     | TSB 24nm SLC | 2          | -25 to 85°C |

| SD 3.0 | VPFUSD4096QIQSTH  | С     | TSB 24nm SLC | 4          | -25 to 85°C |

| SD 3.0 | VPFUSD8192QIWSTH  | С     | TSB 24nm SLC | 8          | -25 to 85°C |

# **Table of Contents**

| 1 IN7                                                       | RODUCTION                                                                                                                                                                                      | 8                                            |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1.1 F                                                       | Features                                                                                                                                                                                       | 8                                            |

| 1.2                                                         | General Description                                                                                                                                                                            | 9                                            |

| 1.3.1                                                       | Flash Management Error Correction Code (ECC) Wear Leveling Bad Block Management                                                                                                                | <b>9</b><br>9<br>9<br>10                     |

| 2 PR                                                        | ODUCT SPECIFICATIONS                                                                                                                                                                           | 11                                           |

| 2.1                                                         | Summary                                                                                                                                                                                        | 11                                           |

| 2.2 E                                                       | Block Diagram                                                                                                                                                                                  | 12                                           |

| 2.3 N                                                       | MicroSD CARD COMPARISON                                                                                                                                                                        | 13                                           |

| 3 EN                                                        | VIRONMENTAL SPECIFICATIONS                                                                                                                                                                     | 14                                           |

| 3.1 E 3.1.1 3.1.2 3.1.1 3.1.2 3.1.3 3.1.4 3.1.5 3.1.6 3.1.7 | Environmental Conditions  Temperature and Humidity Shock and Vibration Electromagnetic Immunity and EMI Compliance Drop Bend Toque Switch Card Socket Insertions Electrostatic Discharge (ESD) | 14<br>14<br>14<br>14<br>15<br>15<br>15<br>15 |

| 3.2 F                                                       | Power Consumption                                                                                                                                                                              | 16                                           |

| 3.3.1<br>3.3.2<br>3.3.3<br>3.3.4                            | OC Characteristic  Bus Operation Conditions for 3.3V Signaling  Bus Signal Line Load  Power Up Time of Host  Power Up Time of Card                                                             | 16<br>16<br>18<br>19<br>21                   |

| 3.4.1<br>3.4.2<br>3.4.3                                     | AC Characteristic  MicroSD Interface Timing (Default)  MicroSD Interface Timing (High-Speed Mode)  MicroSD Interface Timing (SDR12, SDR25 and SDR50 Modes)                                     | <b>22</b><br>22<br>25<br>27                  |

| 3.4.4 MicroSD Interface Timing (DDR50 Mode)                          | 31              |

|----------------------------------------------------------------------|-----------------|

| 4 INTERFACE                                                          | 34              |

| 4.1 Pad Assignment and Descriptions 4.1.1 MicroSD Bus Pin Assignment | <b>34</b><br>34 |

| 5 MECHANICAL INFORMATION                                             | 36              |

# **Table of Tables**

| Table 2-1: Comparing SD3.0 Standard, SD3.0 SDHC and SD3.0 SDXC                 | 13         |

|--------------------------------------------------------------------------------|------------|

| Table 2-2: Comparing UHS Speed Grade Symbols                                   | 13         |

| Table 3-1: Temperature Specifications                                          |            |

| Table 3-2: Shock and Vibration Specifications                                  |            |

| Table 3-3: Drop Specifications                                                 |            |

| Table 3-4: Bend Specifications                                                 |            |

| Table 3-5: Torque Specifications                                               |            |

| Table 3-6: Switch Specifications                                               |            |

| Table 3-7: Card Socket Insertions                                              |            |

| Table 3-8: Electrostatic Discharge (ESD)                                       |            |

| Table 3-9: Power Consumption                                                   | 16         |

| Table 3-10: Threshold Level for High Voltage Range                             | 16         |

| Table 3-11: Peak Voltage and Leakage Current                                   | 17         |

| Table 3-12: Threshold Level for 1.8V Signaling                                 | 17         |

| Table 3-13: Input Leakage Current for 1.8V Signaling                           | 17         |

| Table 3-14: Bus Operation Conditions – Signal Line's Load                      |            |

| Table 3-14. Bus Operation Conditions – Signal Line's Load                      | 10         |

|                                                                                | 24         |

| Table 3-16: Card Output Timing (High Speed Card)                               |            |

| Table 3-17: Clock Signal Timing                                                | 2/         |

| Table 3-18: SDR50 and SDR104 Card Input Timing                                 | 28         |

| Table 3-19: Output Timing of Fixed Data Window (SDR12, SDR25, SDR50)           | 29         |

| Table 3-20: Output Timing of Variable Window (SDR104)                          |            |

| Table 3-21: Clock Signal Timing                                                | 31         |

| Table 3-22: Bus Timings – Parameters Values (DDR50 Mode)                       | <i>3</i> 3 |

| Table 4-1: MicroSD Bus Pin Assignment                                          |            |

| Table 4-2: Registers                                                           | 35         |

|                                                                                |            |

|                                                                                |            |

| Table of Figures                                                               |            |

| 1 table 51 1 1gal 55                                                           |            |

| Figure 2.1, High Lavel Block Diagram                                           | 10         |

| Figure 2-1: High-Level Block Diagram                                           |            |

| Figure 3-1: Bus Circuitry Diagram                                              |            |

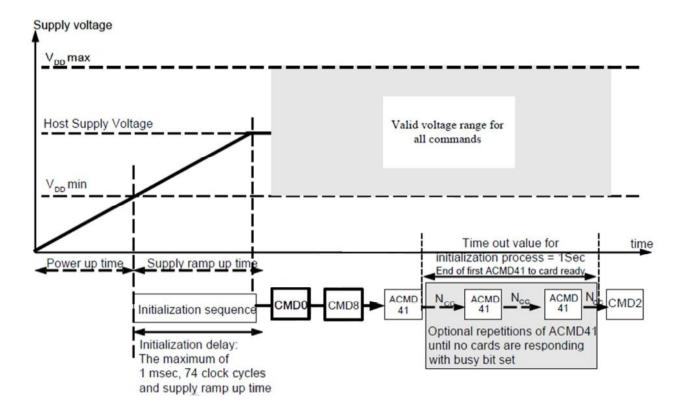

| Figure 3-2: Power Up Time of Host                                              | 19         |

| Figure 3-3: Power Up Time of Card                                              | 21         |

| Figure 3-4: Voltage Levels                                                     | 22         |

| Figure 3-5: Card Input Timing (Default Speed Card)                             | 22         |

| Figure 3-6: Card Output Timing (Default Speed Card)                            | 23         |

| Figure 3-7: Card Input Timing (High Speed Card)                                |            |

| Figure 3-8: Card Output Timing (High Speed Card)                               | 25         |

| Figure 3-9: Clock Signal Timing (Input)                                        | 27         |

| Figure 3-10: SDR50 and SDR104 Card Input Timing                                | 28         |

| Figure 3-11: Clock Signal Timing (Output Timing of Fixed Data)                 |            |

| Figure 3-12: Output Timing of Variable Window (SDR104)                         |            |

| Figure 3-13: Clock Signal Timing                                               | 31         |

| Figure 3-14: Timing Diagram DAT Inputs/Outputs Referenced to CLK in DDR50 Mode | 32         |

| Figure 4-1: MicroSD Pin Assignment 9Back View of the Card)                     | 34         |

| Figure 5-1: MicroSD Case Dimensions                                            | 36         |

| . Igare o T. Mileroop eace Elimenoione                                         |            |

## 1 Introduction

Viking SSD's offer the highest flash storage reliability and performance as well as support for many functional features.

### 1.1 Features

- Flash Type

- o Toshiba 24nm SLC

- o Toshiba 32nm SLC

- o Spansion 32nm SLC

- Bus Speed Mode

- o UHS-I

- o Non-UHS

- Speed Class

- o Class 2/6/10

- Power Consumption Note

- o Power Up Current < 250uA

- o Standby Current < 1000uA

- o Read Current < 400mA

- Write Current < 400mA

- CPRM (Content Protection for Recordable Media)

NOTE: Please see Chapter on Power Consumption for details

- Advanced Flash Management

- Static and Dynamic Wear Leveling

- Bad Block Management

- Write Protect with mechanical switch

- Supply Voltage 2.7 ~ 3.6V

- Temperature Range

- o Operation: -25°C ~ 85°C

- Storage: -25°C ~ 85°C

- RoHS compliant

- EMI compliant

Datasheet: PSFUSDxxxxQxxxx MicroSD Card 3.0 Page 8

#### Performance Overview

|          |       |                 |          | Flash   |                  |                | trix Test<br>600MB |

|----------|-------|-----------------|----------|---------|------------------|----------------|--------------------|

| Capacity | Class | UHS-I           | Density  | Process | Bit-per-<br>cell | Read<br>(MB/s) | Write<br>(MB/s)    |

| 0.512GB  | CL6   | Non-UHS         | .512Gb*1 | 24nm    | SLC              | 23             | 17                 |

| 1GB      | CL6   | Non-UHS         | .512Gb*2 | 24nm    | SLC              | 23             | 22                 |

| 2GB      | CL6   | Non-UHS         | .512Gb*4 | 24nm    | SLC              | 23             | 22                 |

| 4GB      | CL10  | UHS-I (Grade 1) | 4Gb*1    | 24nm    | SLC              | 35             | 35                 |

| 8GB      | CL10  | UHS-I (Grade 1) | 4Gb*2    | 24nm    | SLC              | 35             | 35                 |

# 1.2 General Description

The Micro Secure Digital (MicroSD) card version 3.0 is fully compliant with the standards released by the SD Card Association. The Command List supports [Part 1 Physical Layer Specification Ver3.01 Final] definitions. Card capacities of non-secure area and secure area support [Part 3 Security Specification Ver3.0 Final]

The MicroSD 3.0 card has a 9-pin interface, designed to operate at a maximum frequency of 208MHz. It can alternate communication protocol between the SD mode and SPI mode. It performs data error detection and correction with very low power consumption. The Card capacity could be more than 64GB and up to 2TB in the future with ex-FAT file system, which is called SDXC (Extended Capacity SD Memory Card). Secure Digital 3.0 cards are one of the most popular cards today due to its high performance, good reliability and wide compatibility.

# 1.3 Flash Management

# 1.3.1 Error Correction Code (ECC)

Flash memory cells will deteriorate with use, which might generate random bit errors in the stored data. Thus, Viking MicroSD cards apply the BCH ECC Algorithm, which can detect and correct errors occur during Read process, ensure data been read correctly, as well as protect data from corruption.

# 1.3.2 Wear Leveling

NAND Flash devices can only undergo a limited number of program/erase cycles, and in most cases, the flash media are not used evenly. If some area get updated more frequently than others, the lifetime of the device would be reduced significantly. Thus, Wear Leveling technique is applied to extend the lifespan of NAND Flash by evenly distributing write and erase cycles across the media.

Viking provides advanced Wear Leveling algorithm, which can efficiently spread out the flash usage through the whole flash media area. Moreover, by implementing both dynamic and static Wear Leveling algorithms, the life expectancy of the NAND Flash is greatly improved.

### 1.3.3 Bad Block Management

Bad blocks are blocks that include one or more invalid bits, and their reliability is not guaranteed. Blocks that are identified and marked as bad by the manufacturer are referred to as "Initial Bad Blocks". Bad blocks that are developed during the lifespan of the flash are named "Later Bad Blocks". Viking implements an efficient bad block management algorithm to detect the factory-produced bad blocks and manages any bad blocks that appear with use. This practice further prevents data being stored into bad blocks and improves the data reliability.

### 2 PRODUCT SPECIFICATIONS

# 2.1 Summary

- Support MicroSD system specification version 3.0

- Card capacity of non-secure area and secure area support [Part 3 Security Specification Ver3.0 Final] Specifications

- Support MicroSD SPI mode

- Designed for read-only and read/write cards

- Bus Speed Mode (use 4 parallel data lines)

- Non-UHS Mode

- Default speed mode: 3.3V signaling, frequency up to 25MHz, up to 12.5 MB/sec

- ➤ High speed mode: 3.3V signaling, frequency up to 50MHz, up to 25 MB/sec

- UHS Mode

- ➤ SDR12: SDR up to 25MHz, 1.8V signaling

- > SDR25: SDR up to 50MHz, 1.8V signaling

- > SDR50: 1.8V signaling, frequency up to 100MHz, up to 50 MB/sec

- ➤ SDR104: 1.8V signaling, frequency up to 208MHz, up to 104MB/sec

- DDR50: 1.8V signaling, frequency up to 50MHz, sampled on both clock edges, up to 50MB/sec

#### NOTES:

- 1. Timing in 1.8V signaling is different from that of 3.3V signaling.

- 2. To properly run the UHS mode, please ensure the device supports UHS-I mode.

- The command list supports [Part 1 Physical Layer Specification Ver3.1 Final] definitions

- Copyrights Protection Mechanism

- Compliant with the highest security of DPRM standard

- Support CPRM (Content Protection for Recordable Media) of MicroSD Card

- · Card removal during read operation will never harm the content

- Password Protection of cards (optional)

- Write Protect feature using mechanical switch

- Built-in write protection features (permanent and temporary)

- Electrostatic Discharge (ESD)

- ESD protection in contact pads (contact discharge)

- ESD protection in non-contact pads (air discharge)

- Operation voltage range: 2.7 ~ 3.6V

- Support Dynamic and Static Wear Leveling

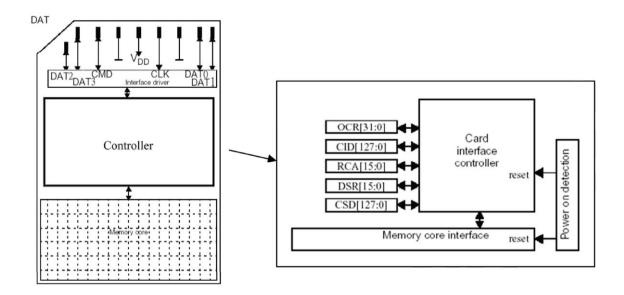

# 2.2 Block Diagram

Figure 2-1: High-Level Block Diagram

## 2.3 MicroSD CARD COMPARISON

Table 2-1: Comparing SD3.0 Standard, SD3.0 SDHC and SD3.0 SDXC

|                                            | SD3.0 SDSC (Backward compatible to 2.0 host) | SD3.0 SDHC (Backward compatible to 2.0 host)     | SD3.0 SDXC                          |

|--------------------------------------------|----------------------------------------------|--------------------------------------------------|-------------------------------------|

| File System                                | FAT 12/16                                    | FAT32                                            | exFAT                               |

| Addressing Mode Byte (1 byte unit)         |                                              | Block (512 byte unit)                            | Block (512 byte unit)               |

| HCS/CCS bits of ACMD41                     | Support                                      | Support                                          | Support                             |

| CMD8<br>(SEND_IF_COND)                     | Support                                      | Support                                          | Support                             |

| CMD16<br>(SET_BLOCKLEN)                    | Support                                      | Support (Only CMD42)                             | Support (Only<br>CMD42)             |

| Partial Read                               | Support                                      | Not Support                                      | Not Support                         |

| Lock/Unlock Function                       | Mandatory                                    | Mandatory                                        | Mandatory                           |

| Write Protect Groups Optional              |                                              | Not Support                                      | Not Support                         |

| Supply Voltage 2.7v – 3.6v (for operation) | Support                                      | Support                                          | Support                             |

| Total Bus Capacitance for each signal line | 40pF                                         | 40pF                                             | 40pF                                |

| CSD Version<br>(CSD_STRUCTURE              |                                              | 2.0 (0v1)                                        | 2.0 (0x1)                           |

| Value) Speed Class                         | 1.0 (0x0) Optional                           | 2.0 (0x1)<br>Mandatory (Class 2 / 4 / 6 /<br>10) | Mandatory (Class<br>2 / 4 / 6 / 10) |

**Table 2-2: Comparing UHS Speed Grade Symbols**

|                   | U1 ( UHS Speed Grade 1)                                     | U3 ( UHS Speed Grade 3)   |

|-------------------|-------------------------------------------------------------|---------------------------|

| Operable<br>Under | *UHS-I Bus I/F, UHS-II Bus I/F                              |                           |

| MicroSD           |                                                             |                           |

| Memory            |                                                             |                           |

| Card              | SDHC UHS-I and UHS-II, SDXC UHS-I and UHS-II                |                           |

|                   |                                                             | 30 MB/s minimum write     |

| Performance       | 10 MB/s minimum write speed                                 | speed                     |

|                   | Full higher potential of recording real-time broadcasts and | Capable of recording 4K2K |

| Applications      | capturing large-size HD videos.                             | video.                    |

<sup>\*</sup>UHS (Ultra High Speed), , defines bus-interface speeds up to 312 Megabytes per second for greater device performance. It is available on SDXC and SDHC memory cards and devices.

# 3 ENVIRONMENTAL SPECIFICATIONS

### 3.1 Environmental Conditions

# 3.1.1 Temperature and Humidity

**Table 3-1: Temperature Specifications**

| Conditions                | Operating     | Shipping      | Storage       |

|---------------------------|---------------|---------------|---------------|

| Temperature- Ambient      | -25 to 85°C   | -40 to 85°C   | -40 to 85°C   |

| Humidity (non-condensing) | 95% under 25C | 93% under 40C | 93% under 40C |

### 3.1.2 Shock and Vibration

**Table 3-2: Shock and Vibration Specifications**

| Stimulus  | Description                                                         |

|-----------|---------------------------------------------------------------------|

| Shock     | 1500G, 0.5ms                                                        |

| Vibration | 20 - 80 Hz/1.52mm, 80 - 2000 Hz/20G, (X,Y,Z axis / 30 min for each) |

# 3.1.1 Electromagnetic Immunity and EMI Compliance

FCC: CISPR22CE: EN55022BSMI 13438

# 3.1.2 Drop

**Table 3-3: Drop Specifications**

|         | Height of Drop  | Number of Drop                 |

|---------|-----------------|--------------------------------|

| MicroSD |                 |                                |

| card    | 150cm free fall | Direction: 6 face; 1 time/face |

Result: No any abnormality is detected when power on

### 3.1.3 Bend

# **Table 3-4: Bend Specifications**

|              | Force | Action                        |

|--------------|-------|-------------------------------|

| MicroSD card | ≥ 10N | Hold for 1min; total 5 times. |

Result: No any abnormality is detected when power on

# 3.1.4 Toque

# **Table 3-5: Torque Specifications**

|              | Force               | Action                                   |

|--------------|---------------------|------------------------------------------|

| MicroSD card | 0.15N-m or ±2.5 deg | Hold 30 second/direction, Total 5 cycles |

Result: No any abnormality is detected when power on

### 3.1.5 Switch

**Table 3-6: Switch Specifications**

|              | Force       | Number of Switch Cycle |

|--------------|-------------|------------------------|

| MicroSD card | 0.4N-m~5N-m | 1000 cycles            |

Result: No any abnormality is detected when power on

### 3.1.6 Card Socket Insertions

**Table 3-7: Card Socket Insertions**

|              | Number of Mating Cycles | Result |

|--------------|-------------------------|--------|

| MicroSD card | 10000 cycles            | Pass   |

# 3.1.7 Electrostatic Discharge (ESD)

## **Table 3-8: Electrostatic Discharge (ESD)**

|              | Condition                    | Result |

|--------------|------------------------------|--------|

|              | Contact: ±4KV; 5 times/Pin   | Pass   |

| MicroSD card | Air: ±15KV; 5 times/Position | Pass   |

# 3.2 Power Consumption

The table below is the power consumption of MicroSD card with different bus speed modes.

**Table 3-9: Power Consumption**

| Bus Speed Mode     | Max. Power Up<br>Current (uA) | Max. Standby<br>Current (uA) | Max. Read Current<br>(mA) | Max. Write Current<br>(mA) |

|--------------------|-------------------------------|------------------------------|---------------------------|----------------------------|

| Default Speed Mode | 250                           | 1000                         | 150 @ 3.6V                | 150 @ 3.6V                 |

| High Speed Mode    | 250                           | 1000                         | 200 @ 3.6V                | 200 @ 3.6V                 |

#### NOTES:

## 3.3 DC Characteristic

# 3.3.1 Bus Operation Conditions for 3.3V Signaling

Table 3-10: Threshold Level for High Voltage Range

| Parameter           | Symbol          | Min.      | Max       | Unit | Condition                     |

|---------------------|-----------------|-----------|-----------|------|-------------------------------|

| Supply Voltage      | VDD             | 2.7       | 3.6       | V    |                               |

| Output High Voltage | $V_{OH}$        | 0.75*VDD  |           | V    | I <sub>OH</sub> =-2mA VDD Min |

| Output Low Voltage  | $V_{OL}$        |           | 0.125*VDD | V    | I <sub>OL</sub> =2mA VDD Min  |

| Input High Voltage  | V <sub>IH</sub> | 0.625*VDD | VDD+0.3   | V    |                               |

| Input Low Voltage   | V <sub>IL</sub> | VSS-0.3   | 0.25*VDD  | V    |                               |

| Power Up Time       |                 |           | 250       | ms   | From 0V to VDD min            |

<sup>1)</sup> Power consumptions are measured at room temperature (25C). Standby current might rise to 1600 under 85C.

<sup>2)</sup> Power consumption of Max. Standby Current is for MicroSD cards under and including 64GB only. For 128GB and 256GB, the power consumption is to be determined.

Table 3-11: Peak Voltage and Leakage Current

| Parameter                 | Symbol | Min  | Max.    | Unit | Remarks |

|---------------------------|--------|------|---------|------|---------|

| Peak voltage on all lines |        | -0.3 | VDD+0.3 | ٧    |         |

| All Inputs                |        |      |         |      |         |

| Input Leakage Current     |        | -10  | 10      | uA   |         |

| All Outputs               |        |      |         |      |         |

| Output Leakage Current    |        | -10  | 10      | uA   |         |

Table 3-12: Threshold Level for 1.8V Signaling

| Parameter           | Symbol           | Min.    | Max  | Unit | Condition                    |

|---------------------|------------------|---------|------|------|------------------------------|

| Supply Voltage      | $V_{	extsf{DD}}$ | 2.7     | 3.6  | V    |                              |

| Regulator Voltage   | $V_{DDIO}$       | 1.7     | 1.95 | V    | Generated by V <sub>DD</sub> |

| Output High Voltage | $V_{OH}$         | 1.4     | -    | V    | I <sub>OH</sub> =-2mA        |

| Output Low Voltage  | $V_{OL}$         | -       | 0.45 | V    | I <sub>OL</sub> =2mA         |

| Input High Voltage  | $V_{IH}$         | 1.27    | 2    | V    |                              |

| Input Low Voltage   | $V_{IL}$         | Vss-0.3 | 0.58 | V    |                              |

Table 3-13: Input Leakage Current for 1.8V Signaling

| Parameter             | Symbol | Min | Max. | Unit | Remarks                      |

|-----------------------|--------|-----|------|------|------------------------------|

| Input Leakage Current |        | -2  | 2    | uA   | DAT3 pull-up is disconnected |

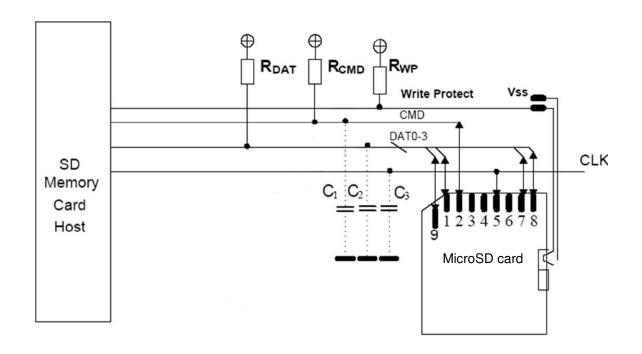

# 3.3.2 Bus Signal Line Load

Figure 3-1: Bus Circuitry Diagram

Table 3-14: Bus Operation Conditions - Signal Line's Load

| Parameter                                  | Symbol                               | Min | Max | Unit | Remark                                                               |

|--------------------------------------------|--------------------------------------|-----|-----|------|----------------------------------------------------------------------|

| Pull-up resistance                         | R <sub>CMD</sub><br>R <sub>DAT</sub> | 10  | 100 | kΩ   | To prevent bus floating                                              |

| Total bus capacitance for each signal line | C <sub>L</sub>                       |     | 40  | pF   | 1 card C <sub>HOST</sub> +C <sub>BUS</sub> shall not exceed<br>30 pF |

| Card Capacitance for each signal pin       | C <sub>CARD</sub>                    |     | 10  | рF   |                                                                      |

| Maximum signal line inductance             |                                      |     | 16  | nΗ   |                                                                      |

| Pull-up resistance inside card (pin1)      | R <sub>DAT3</sub>                    | 10  | 90  | kΩ   | May be used for card detection                                       |

| Capacity Connected to Power Line           | C <sub>C</sub>                       |     | 5   | uF   | To prevent inrush current                                            |

Notes:

Total Bus Capacitance =  $C_{HOST} + C_{BUS} + N C_{CARD}$

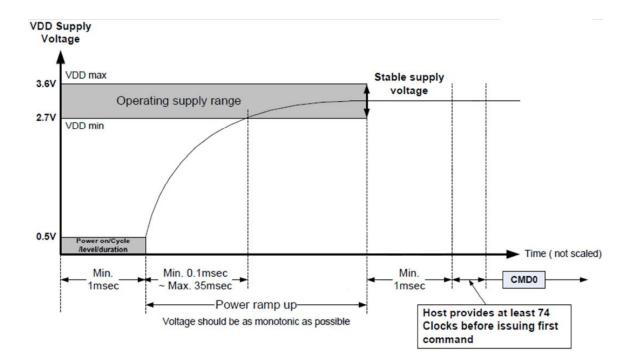

# 3.3.3 Power Up Time of Host

Host needs to keep power line level less than 0.5V and more than 1ms before power ramp up.

Figure 3-2: Power Up Time of Host

#### **Power On or Power Cycle**

Followings are requirements for Power on and Power cycle to assure a reliable MicroSD Card hard reset.

- 1. Voltage level shall be below 0.5V

- 2. Duration shall be at least 1ms.

### **Power Supply Ramp Up**

The power ramp up time is defined from 0.5V threshold level up to the operating supply voltage which is stable between VDD (min.) and VDD (max.) and host can supply SDCLK.

Followings are recommendations of Power ramp up:

- 1. Voltage of power ramp up should be monotonic as much as possible.

- 2. The minimum ramp up time should be 0.1ms.

- 3. The maximum ramp up time should be 35ms for 2.7-3.6V power supply.

- 4. Host shall wait until VDD is stable.

- 5. After 1ms VDD stable time, host provides at least 74 clocks before issuing the first command.

#### **Power Down and Power Cycle**

- 1. When the host shuts down the power, the card VDD shall be lowered to less than 0.5Volt for a minimum period of 1ms. During power down, DAT, CMD, and CLK should be disconnected or driven to logical 0 by the host to avoid a situation that the operating current is drawn through the signal lines.

- 2. If the host needs to change the operating voltage, a power cycle is required. Power cycle means the power is turned off and supplied again. Power cycle is also needed for accessing cards that are already in Inactive State. To create a power cycle the host shall follow the power down description before power up the card (i.e. the card VDD shall be once lowered to less than 0.5Volt for a minimum period of 1ms).

# 3.3.4 Power Up Time of Card

A device shall be ready to accept the first command within 1ms from detecting VDD min. Device may use up to 74 clocks for preparation before receiving the first command.

Figure 3-3: Power Up Time of Card

## 3.4 AC Characteristic

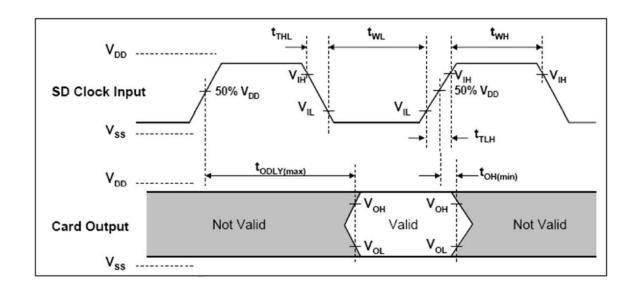

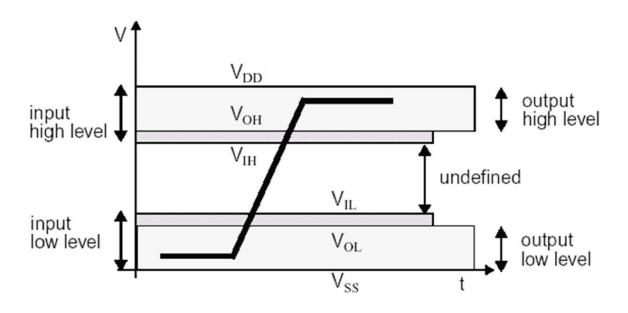

Figure 3-4: Voltage Levels

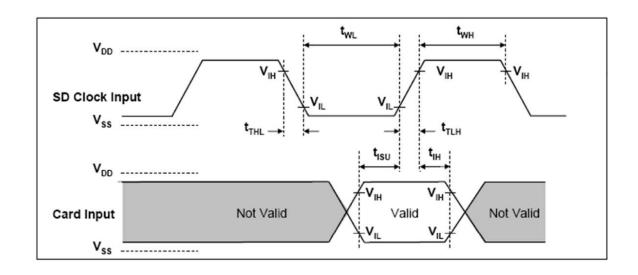

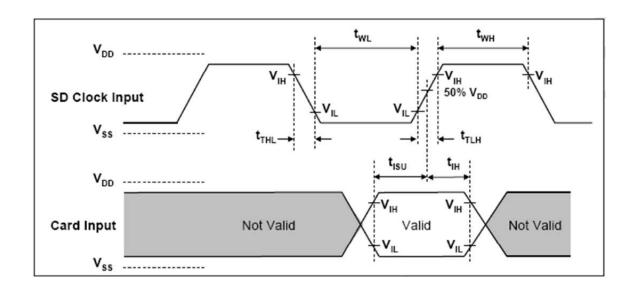

# 3.4.1 MicroSD Interface Timing (Default)

Figure 3-5: Card Input Timing (Default Speed Card)

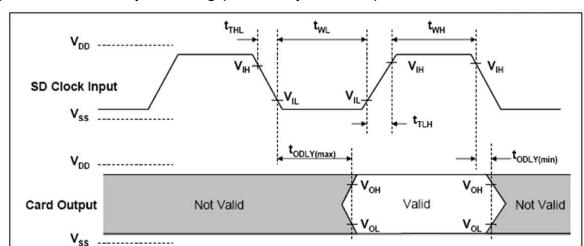

**Figure 3-6: Card Output Timing (Default Speed Card)**

**Table 3-15: Timing Specifications**

| Parameter                                                   | Symbol            | Min       | Max | Unit | Remark                            |  |  |  |  |  |

|-------------------------------------------------------------|-------------------|-----------|-----|------|-----------------------------------|--|--|--|--|--|

| Clock CLK (All values are referred to min(VIH) and max(VIL) |                   |           |     |      |                                   |  |  |  |  |  |

| Clock frequency Data Transfer Mode                          | fPP               | 0         | 25  | MHz  | C <sub>card</sub> ≤10 pF (1 card) |  |  |  |  |  |

| Clock frequency Identification Mode                         | f <sub>OD</sub>   | 0(1)/100  | 400 | kHz  | C <sub>card</sub> ≤10 pF (1 card) |  |  |  |  |  |

| Clock low time                                              | t <sub>WL</sub>   | 10        |     | ns   | C <sub>card</sub> ≤10 pF (1 card) |  |  |  |  |  |

| Clock high time                                             | t <sub>WH</sub>   | 10        |     | ns   | C <sub>card</sub> ≤10 pF (1 card) |  |  |  |  |  |

| Clock rise time                                             | t <sub>TLH</sub>  |           | 10  | ns   | C <sub>card</sub> ≤10 pF (1 card) |  |  |  |  |  |

| Clock fall time                                             | t <sub>THL</sub>  |           | 10  | ns   | C <sub>card</sub> ≤10 pF (1 card) |  |  |  |  |  |

| Inputs CMD, DA                                              | T (referen        | ced to Cl | _K) |      |                                   |  |  |  |  |  |

| Input set-up time                                           | t <sub>ISU</sub>  | 5         |     | ns   | C <sub>card</sub> ≤10 pF (1 card) |  |  |  |  |  |

| Input hold time                                             | t <sub>IH</sub>   | 5         |     | ns   | C <sub>card</sub> ≤10 pF (1 card) |  |  |  |  |  |

| Outputs CMD, DAT (referenced to CLK)                        |                   |           |     |      |                                   |  |  |  |  |  |

| Output Delay time during Data Transfer Mode                 | t <sub>ODLY</sub> | 0         | 14  | ns   | C <sub>card</sub> ≤40 pF (1 card) |  |  |  |  |  |

| Output Delay time during Identification Mode                | t <sub>ODLY</sub> | 0         | 50  | ns   | C <sub>card</sub> ≤40 pF (1 card) |  |  |  |  |  |

|                                                             |                   |           |     |      |                                   |  |  |  |  |  |

### Notes:

<sup>1) 0</sup>Hz means to stop the clock. The given minimum frequency range is for cases where continuous clock is required.

# 3.4.2 MicroSD Interface Timing (High-Speed Mode)

Figure 3-7: Card Input Timing (High Speed Card)

Figure 3-8: Card Output Timing (High Speed Card)