Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **ENT-AN0098 Application Note Magnetics Guide**

Power Matters.\*

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo,

CA 92656 USA

Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Sales: +1 (949) 380-6136

Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

www.microsemi.com

© 2006–2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revisi | tory     | 1                                         |   |

|---|--------|----------|-------------------------------------------|---|

|   | 1.1    |          | 12.1                                      |   |

|   | 1.2    | Revision | 12.0                                      | 1 |

|   | 1.3    |          | n 1.2                                     |   |

|   | 1.4    | Revision | i 1.1                                     | 1 |

|   | 1.5    | Revision | n 1.0                                     | 1 |

| 2 | Using  | Magne    | etics                                     | 2 |

|   | 2.1    | •        | e of Magnetics in Ethernet Systems        |   |

|   |        | 2.1.1    | Electrical Isolation                      |   |

|   |        | 2.1.2    | Signal Balancing/Common-Mode Rejection    | 2 |

|   | 2.2    | EMC Im   | provement                                 | 2 |

|   |        | 2.2.1    | Electromagnetic Interference Minimization | 3 |

|   |        | 2.2.2    | Electromagnetic Interference Containment  | 3 |

|   | 2.3    | Magneti  | cs Guide                                  | 4 |

|   |        | 2.3.1    | Magnetic Types                            |   |

|   |        | 2.3.2    | Integrated or Discrete?                   | 6 |

|   | 2.4    | Test Da  | ta                                        | 7 |

|   |        | 2.4.1    | EMC Test Data                             | 7 |

|   |        | 2.4.2    | IEEE Return Loss Data                     | 8 |

|   | 2.5    | Suggest  | ed Magnetics                              | 9 |

# **Figures**

| Figure 1 | 12-Core Magnetic (One Pair Shown)                                      |

|----------|------------------------------------------------------------------------|

| -        | Intrinsic Characteristic Impedance Between Each Pair of the Four Pairs |

| Figure 3 | 8-Core Magnetic with CMC on Cable Side (One Pair Shown)                |

| Figure 4 | 8-Core Magnetic with Classic 2-Wire CMC on PHY Side (One Pair Shown)   |

| Figure 5 | Modern 8-Core Magnetic with 3-Wire CMC on PHY Side (One Pair Shown)    |

| Figure 6 | EMC Emissions – VSC8601/8641 PHY Family                                |

| Figure 7 | Return Loss Specification, Recommended and Measured                    |

# **Tables**

| Table 1 | EMC Test Data                                                  |   |

|---------|----------------------------------------------------------------|---|

| Table I | Livo rest bata                                                 | • |

| Table 2 | IEEE Minimum Return Loss for Reference Impedance of 100 O +15% |   |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

#### 1.1 **Revision 2.1**

The following is a summary of the changes in revision 2.1 of this document.

- Return loss data was updated. For more information, see IEEE Return Loss Data, page 8.

- Magnetic suggestions were added. For more information, see Suggested Magnetics, page 9.

#### 1.2 **Revision 2.0**

The following is a summary of the changes in revision 2.0 of this document.

- Text regarding CMC on the PHY side was updated. For more information, see 8-Core Magnetics, page 5.

- EMC Test Data was simplified. For more information, see Table 1, page 7.

#### 1.3 **Revision 1.2**

In revision 1.2 of this document, 12-port (2x6) Power-over-Ethernet (PoE) magnetic modules were added. For more information, see 12-Core Magnetics, page 4.

#### 1.4 **Revision 1.1**

The following is a summary of the changes in revision 1.1 of this document.

- EMC test results for the VSC8601/8641 family were added. For more information, see EMC Test Data, page 7.

- 8-core 3-wire CMC on PHY side was added. For more information, see Figure 5, page 6.

#### 1.5 **Revision 1.0**

Revision 1.0 was the first publication of this document.

# 2 Using Magnetics

This application note provides a designer with the basic knowledge of magnetic modules as well as some test data. The proper understanding of features of the magnetic module to be used with Microsemi PHY and integrated Switch/PHY devices is very important to ensure the best Electromagnetic Compatibility (EMC) and IEEE conformance of the finished product.

Reference IEEE 802.3-2012 - CSMA/CD Access Method and Physical Layer Specification and FCC—Part 15: Radio Frequency Devices for additional information.

## 2.1 The Role of Magnetics in Ethernet Systems

While not explicitly required by IEEE 802.3, magnetics are the most commonly used method of meeting the requirements of the 10/100/1000BASE-T PMA electrical interface. However, there is no one standard configuration that meets all objectives for all designs at the lowest cost. Magnetics offer a straightforward solution to many functions of this interface, including electrical isolation, signal balancing, common mode rejection, impedance matching, and EMC improvement. The following is a brief description of each of these areas.

#### 2.1.1 Electrical Isolation

For human safety, the IEEE specification requires a 10/100/1000BASE-T port to be able to withstand 1,500 VAC at 50 Hz to 60 Hz for 1 minute between ports or from each port to the chassis ground. Transformers can easily and inexpensively meet this isolation requirement and are commonly used for this purpose.

### 2.1.2 Signal Balancing/Common-Mode Rejection

Each 10/100/1000BASE-T network cable consists of four sets of twisted pairs connected in a balanced configuration. While there are various circuit topologies that can provide the necessary balanced operation without magnetics, transformers simply and easily provide the balanced connection to each pair of a cable and can also provide a very effective rejection of common-mode signals.

The common-mode rejection of a transformer functions in both of the signal directions of a port. This common-mode rejection attenuates common-mode signals coming both from the cable to the PHY and also from the PHY (and its surrounding system) to the cable. This common mode attenuation is beneficial for the following reasons:

- Reduction of the common-mode signals picked up by the cable from its environment improves the signal-to-noise ratio of the system. This allows the PHY DSP to more easily recover the data signal and achieve the desired bit error rate. This is also known as electromagnetic immunity.

- The noise from the board circuits can couple to the sensitive signal traces going from the PHY to the

magnetics, but due to the nature of this noise, most of it will couple equally to both differential

signals, thus creating common mode noise. This noise will be attenuated by the magnetics and

improves the EMC performance. Because 10/100/1000BASE-T uses unshielded twisted pair cables,

the cables radiate any common-mode noise that is coupled through the magnetics and onto the

cables.

# 2.2 EMC Improvement

All high-speed digital devices create and use radio frequency (RF) energy. If this energy is allowed to escape into the device's environment it can become a source of electromagnetic interference.

The PHY devices are high-speed mixed-design (digital and analog) devices but their EMC can be significantly improved if a few important guidelines are met.

It is necessary to carefully design the systems to minimize the amount of RF energy reaching the 10/100/1000BASE-T ports, since this energy can be easily radiated from the unshielded CAT5 cables. Designers use multiple techniques to control RF emissions. While there is no single technique or

component guaranteeing a successful EMC design, generally the measures involved fall into one of the two categories: minimization and containment.

#### 2.2.1 Electromagnetic Interference Minimization

Minimization involves addressing the parasitic RF energy sources causing EMC problems. If this energy is minimized, there will be less need for additional minimization measures. It is not the purpose of this Application Note to cover all aspects of EMC improvement but it is important to list some of the major rules used to minimize the energy emitted from interference sources. These rules are as follows:

- Use the slowest practical rise and fall times on digital signals, especially clocks. These edges can

often be slowed sufficiently by inserting a series resistor of a few tens of Ohms close to the signal

source.

- Keep high-speed digital lines, especially clocks, as short as possible. Route them over unbroken

ground or power planes. This will help to avoid turning these signal lines into efficient antenna.

- Avoid routing high-speed lines near lines going off-board. This is especially important for the 10/100/1000BASE-T signals. Capacitive and inductive coupling between traces can couple RF energy onto the off-board lines and into any cables connected to them.

- When high-speed lines on a circuit board must cross over off-board lines, ensure they do so at right

angles. Where the lines must run parallel to one another, maximize the spacing between them and

minimize the length of the parallel section. This will help to reduce the coupling between the lines.

For integrated Switch/PHY devices (e.g. SparX family) all the logic is integrated into a single device, and there are no external busses connected that can generate noise. This significantly improves the EMC performance of the systems.

#### 2.2.2 Electromagnetic Interference Containment

Containment measures serve to prevent RF energy from escaping into the environment. The three basic techniques of containment are power filtering, signal filtering, and shielding.

#### 2.2.2.1 Power Filtering

Power filtering means that all the high-speed digital and high-power analog modules are provided with local decoupling capacitors and, where necessary, either series resistors or ferrite beads are provided for the power rails. This way the noise generated locally is filtered 'on the spot' and not spread all over the entire board to eventually escape into environment. Since high value capacitors are efficient at low frequencies and vice versa, each power rail should have a combination of high capacitance and low capacitance ones.

#### 2.2.2.2 Signal Filtering

Signal filtering involves passing signals that must exit a chassis through frequency selective circuits that attenuate the RF energy sufficiently well to meet EMC requirements. There is often a tradeoff between providing adequate attenuation of the interference energy and maintaining the integrity of the desired signal. This is where the distinction between common-mode and differential signals becomes advantageous.

In 10/100/1000BASE-T systems, differential signals are used to convey the data in each port. Fortunately, most of the interference energy present on these same ports is in the form of a common-mode signal. Magnetic devices such as transformers with common-mode chokes do an excellent job of strongly attenuating common-mode signals while passing differential signals nearly unchanged.

#### 2.2.2.3 Shielding

Shielding makes use of the fact that no electromagnetic field can pass through a perfect electrical conductor. If a source of RF energy can be completely enclosed within an unbroken conducting container, then none of that energy will exist outside of the container. If there are holes, seams, connectors, etc. passing through the container, or if the container is made of a poorly conducting material, then energy can escape and create interference.

Various shielding methods are used in system design. The primary method is to enclose the circuitry within a conductive housing or chassis. This can be made of either metal or plastic that has been treated to have a conductive surface. Individual pieces of the chassis must be in good conductive contact with

one another. Conductive gasket material, multi-fingered leaf springs, and closely spaced screws are some of the techniques often used to ensure good conduction between chassis sections.

Another way of shielding is local shielding of noisy traces or busses inside the PCB; it is done by placing them in the inner layers and surrounding with copper planes, usually ground and power ones. For clock bearing traces, the positive side effect of this isolation measure is that it also keeps these signals clean from the induced noise causing clock jitter.

For integrated Switch/PHY devices (e.g. SparX family) all the logic is build into a single device, and there are no external busses and clock lines connected that can generate noise. As a result, these systems can often be made using an inexpensive 2-layer PCB and a plastic housing without shielding.

## 2.3 Magnetics Guide

## 2.3.1 Magnetic Types

Several different magnetic types are available, all conforming IEEE requirements. Only those containing a common-mode choke (CMC) are described in the document.

They can be split into two groups:

- 1. 12-core magnetics that consist of transformer, a common mode choke, and an autotransformer,

- 8-core magnetics that consist of a transformer and a common mode choke.

Their advantages and disadvantages are described below.

#### 2.3.1.1 12-Core Magnetics

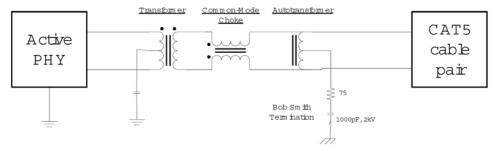

A 12-core magnetic module (see Figure 1, page 4) consists of a transformer, CMC, and an autotransformer (i.e. 3 separate magnetic cores) for each of the 4 twisted pairs in the cable.

Figure 1 • 12-Core Magnetic (One Pair Shown)

The purpose of the transformer with ratio of 1:1 is to create galvanic isolation between the cable and the system. The PHY side center tap of the transformer should connect through a capacitor to ground.

The purpose of CMC is to attenuate common-mode noise in the twisted pair: both noise coming from the system itself, where the CMC decreases the electromagnetic emission (i.e. doing the signal filtering for the entire customer's system as described above), and noise coming from the outside, where the CMC improves the electromagnetic immunity.

The autotransformer presents high impedance to the differential signal in the twisted pair, thus as though not existing for it, but very low impedance to the common-mode currents flowing to a circuit referred to as a Bob Smith termination.

#### 2.3.1.2 Bob Smith Termination

Robert W. (Bob) Smith's patented idea proposes the way to reduce the common mode currents on a multi-pair system (e.g. CAT5 network cable). It is based on the fact that the pair-to-pair relationships of a CAT5 cable form transmission lines in themselves (see Figure 2, page 5). Due to the approximate symmetry in the construction of the CAT5 cable, each pair has the same relation with any other pair.

Z23

Figure 2 · Intrinsic Characteristic Impedance Between Each Pair of the Four Pairs

Providing those pair-to-pair transmission lines with termination matching their characteristic impedance in order to absorb the reflected wave and prevent standing wave from occurring significantly lowers parasitic interference radiation.

Pair 3

The high voltage capacitor between the common point of all the four resistors and the Chassis ground is not a part of Bob Smith termination but helps in filtering the noise residue managing to leak out through the transformer.

#### 2.3.1.3 8-Core Magnetics

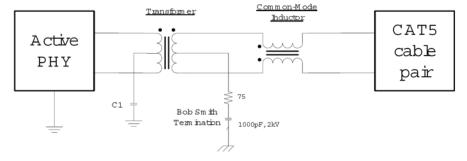

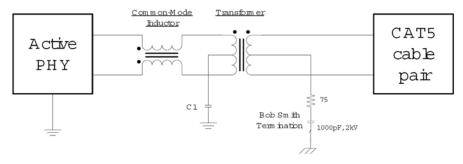

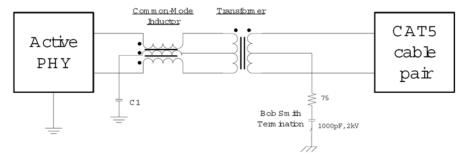

The 8-core magnetic only has a transformer and a CMC placed on either the cable side (see Figure 3, page 5) or the PHY side (see Figure 1, page 4 and Figure 5, page 6) of the transformer.

Placing the CMC on the cable side has the following advantages:

- It also attenuates any common-mode noise that is generated by either the center taps noise of the transformer.

- Or by the transformer windings imbalance,

Pair 2

Filters the noise in the systems where the Chassis ground is connected to the digital ground (which is often the case for computer motherboards) and, even being connected to Earth ground through the power supply circuit, is still noisy enough to inject noise through the high voltage capacitor (in this case removing the capacitor might be better EMC-wise).

The disadvantage, though, is that the Bob Smith termination becomes less effective for common mode noise due to the high impedance inserted between the cable and the impedance-matching resistor. The 12-core version and the 8-core version with CMC on PHY side do not have this disadvantage but require really quiet Chassis ground.

Figure 3 • 8-Core Magnetic with CMC on Cable Side (One Pair Shown)

Using an 8-core magnetic with the classic 2-wire CMC on the PHY side (see Figure 1, page 4) is also not ideal due to the possible noise coupling from the ground plane to the cable through the transformer's center tap capacitor.

In addition, based on a limited tests conducted with transformers having CMC on the PHY side, the margin within the template has been somewhat reduced. We therefore recommend that future designs not to use this transformer configuration (that is, with CMC on the PHY side).

For older designs where this configuration has been used successfully, and passed all system level applicable standard tests, they may continue using these transformers.

#### Figure 4 · 8-Core Magnetic with Classic 2-Wire CMC on PHY Side (One Pair Shown)

Figure 5 · Modern 8-Core Magnetic with 3-Wire CMC on PHY Side (One Pair Shown)

#### 2.3.1.4 8-Core Versus 12-Core

Generally speaking, there is no universal advice on what is the best, but the right magnetic selection should be made depending on conditions in every specific case.

The 8-core magnetics are cheaper, thus more attractive, but riskier in many cases and cautiously recommended to skilled. The 12-core ones make the design process much easier without demanding extreme experience in the layout art, especially if the Ethernet module is a part of a system with a big digital section generating a lot of interference noise.

#### 2.3.1.5 Other Factors

Although the schematic representation of different magnetic modules looks alike, there might be a lot of difference in their electrical and EMC performance. The coupling between the signals on each side of the transformer and common-mode chokes can couple noise and thereby reduce the effect of the common mode chokes.

## 2.3.2 Integrated or Discrete?

To minimize the component count and the product size, some manufacturers deliver magnetic modules, where the magnetic block is build into the RJ45-type connector block. As any compromise, this has both advantages and disadvantages.

#### Advantages:

- Lower component count -> lower production (assembly) cost,

- · Potentially better EMC shielding of the sensitive cable side signals by the metal shield,

Smaller footprint than separate magnetics and a connector.

Disadvantages:

- Harder to rework if a magnetic/connector is failing during production test -> Higher production cost,

- Due to the space limitations, the magnetics cores are smaller and closer to each other thus degrading crosstalk and EMC characteristics, increasing nonlinear distortion and losses.

Especially the electromagnetic emission performance can be either better or worse, depending on the product they are used in. The integrated magnetic/connector modules have a metal shield placed around the whole part; it effectively screens the part from any noise that is present inside the system box. However, due to the small size of the magnetic part of the module, there is a high risk that the noise is coupled between the cable side and the PHY side of the magnetics, thereby limiting the common-mode choke effect. The sizes of the magnetic cores used in the magnetic/connector combinations are also normally smaller than those used in separate magnetics, and the performance is thereby lower.

Using separate magnetics and connectors has an advantage of lower coupling between the different parts inside the magnetics, and this results in better common-mode filtering. The disadvantage is that, once the signals have been filtered by the magnetics, they are routed to the connector on the PCB, and if the box contains a lot on noisy logic, this can couple to these lines and create EMC problems.

The designer needs to balance these advantages and disadvantages against each other when deciding what to use in his board design but much more often the best EMC performance is reached by using 12-core discrete magnetics.

#### 2.4 Test Data

#### 2.4.1 EMC Test Data

The table below summarizes the different magnetics and magnetic/connector combinations that have been tested with the SparX customer evaluation boards (EVBs).

Experiment has been conducted with and without a closed metal chassis and, as no noisy circuits exist on the SparX-G8 (VSC7388) and SparX-G5 (VSC7385) EVBs, the EMC results did not differ significantly.

Table 1 • EMC Test Data

| Vendor | Part Number | Configuration   | Test Setup                | EMC Class<br>(FCC, Part 15) | Margin | Comment         |

|--------|-------------|-----------------|---------------------------|-----------------------------|--------|-----------------|

| Pulse  | H5008       | Single, 12-core | SparX-G8 Managed EVB      | В                           | 9.2 dB | Without chassis |

| Pulse  | H5009       | Single, 8-core  | SparX-G8 Managed EVB      | В                           | 1.3 dB | Without chassis |

| Pulse  | H5007       | Single, 12-core | VSC8641/VSC8601 EMC Board | В                           | 2.1 dB | Without chassis |

| Pulse  | H5004       | Single, 8-core  | VSC8641/VSC8601 EMC Board | В                           | 1.0 dB | Without chassis |

| Pulse  | LF9207A     | Single, 12-core | SparX-G8 Managed EVB      | В                           | 2.0 dB | Without chassis |

Emissions 30 to 1030 MHz 3 Meter FCC B Scan

80.0

70.0

60.0

50.0

20.0

130.00M 230.00M 330.00M 430.00M 530.00M 630.00M 730.00M 830.00M 930.00M 1,03G

Frequency

Figure 6 • EMC Emissions – VSC8601/8641 PHY Family

## 2.4.2 IEEE Return Loss Data

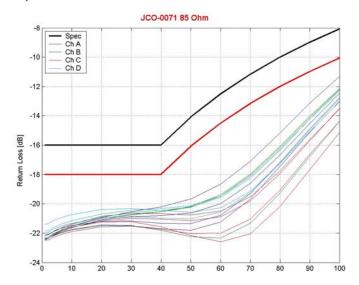

Return loss is specified and maintained for all impedances from 85  $\Omega$  to 115  $\Omega$ . Measurement data presented at a nominal 100  $\Omega$  load is inadequate for assessing specification compliance.

The IEEE 802.3 standard, paragraph 40.8.3.1, states the following:

The differential impedance at the MDI for each channel shall be such that any reflection due to differential signals incident upon the MDI from a balanced cabling having an impedance of  $100~\Omega\pm15\%$  is attenuated, relative to the incident signal, at least 16 dB over the frequency range of 1.0 MHz to 40 MHz and at least 10-20log(f/80) dB over the frequency range 40 MHz to 100 MHz (f in MHz). This return loss shall be maintained at all times when the PHY is transmitting.

This standard is summarized in the following table.

Table 2 • IEEE Minimum Return Loss for Reference Impedance of 100  $\Omega$  ±15%

| Return Loss, dB                                                 | Frequency, MHz |  |  |

|-----------------------------------------------------------------|----------------|--|--|

| 16                                                              | 1-40           |  |  |

| 10-20 *log <sub>10</sub> (f/80) where f is the frequency in MHz | 40-100         |  |  |

The specification is plotted in black in the following representative return loss plot, along with measurement data from a Microsemi PHY.

Figure 7 • Return Loss Specification, Recommended and Measured

There are two key points to emphasize about the return loss plot:

- For a real system with output impedance contributions from both PHY output and a magnetic

transformer to satisfy the IEEE specification, magnetics with a return loss margin of at least 2 dB

(versus the IEEE 802.3 specification at the MDI) are recommended. The red curve in the plot

reflects a 2 dB back-off from the IEEE 802.3 limit.

- The measured return loss is flat to within 3 dB up to 40 MHz–50 MHz. That flatness is a key aspect in maintaining signal integrity.

## 2.5 Suggested Magnetics

This section lists the suggested characteristics when selecting a magnetics product compatible with Microsemi 1000BASE-T Ethernet PHYs. Use the magnetic vendor's datasheet or lot-sample test data to check for the following characteristics.

- Return loss as specified in IEEE Return Loss Data, page 8

- Turns ratio tolerance: (1:1) ± 2%

- · Common mode choke on the line side for all applications that permit line-side CMC

- · Center-tap isolation between each pair A, B, C, D of the magnetic

- Line-side center-taps that can be individually terminated with Bob Smith termination

Contact your Microsemi representative for more information about specific magnetics proven successful with Microsemi Ethernet PHYs.