Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## VSC8541-01 Datasheet Single Port Gigabit Ethernet Copper PHY with GMII/RGMII/MII/RMII Interfaces

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo,

CA 92656 USA

Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com

www.microsemi.com

© 2017 Microsemi Corporation. All

© 2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

# **Contents**

| 1 |        |                | tory                                                  |     |

|---|--------|----------------|-------------------------------------------------------|-----|

|   | 1.1    | Revision       | า 4.0                                                 | . 1 |

| 2 | Overv  | iew            |                                                       | . 2 |

|   | 2.1    | Kev Fea        | atures                                                | . 2 |

|   |        | 2.1.1          | Superior PHY and Interface Technology                 |     |

|   |        | 2.1.2          | Synchronous Ethernet and IEEE 1588 Time Stamp Support |     |

|   |        | 2.1.3          | Fast Link Up/Link Drop Modes                          |     |

|   |        | 2.1.4          | Best-in-Class Power Consumption                       | . 3 |

|   |        | 2.1.5          | Key Specifications                                    | . 3 |

|   | 2.2    | Block D        | iagram                                                | . 3 |

| 3 | Functi | onal D         | escriptions                                           | . 4 |

|   | 3.1    |                | ng Modes                                              |     |

|   | 3.2    | •              | terface                                               |     |

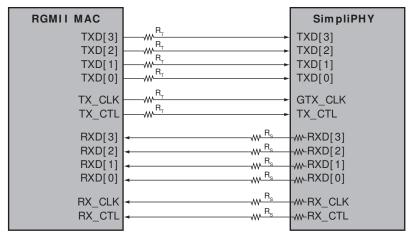

|   | 0.2    | 3.2.1          | RGMII MAC Interface Mode                              |     |

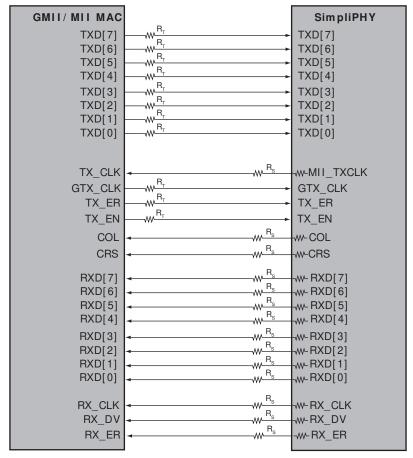

|   |        | 3.2.2          | GMII/MII Interface Mode                               |     |

|   |        | 3.2.3          | RMII Mode                                             | . 6 |

|   |        | 3.2.4          | MAC Interface Edge Rate Control                       | . 7 |

|   | 3.3    | Hardwa         | re Mode Strapping and PHY Addressing                  | . 8 |

|   |        | 3.3.1          | CLKOUT Signal Configuration                           |     |

|   |        | 3.3.2          | Managed Mode                                          |     |

|   |        | 3.3.3          | Unmanaged Mode                                        |     |

|   |        | 3.3.4          | GMII/MII or RGMII/RMII MAC Interface Mode             |     |

|   |        | 3.3.5<br>3.3.6 | CLKOUT Frequency Selection                            |     |

|   | 0.4    |                |                                                       |     |

|   | 3.4    | 3.4.1          | visted Pair Media Interface                           |     |

|   |        | 3.4.1          | Cat5 Auto-Negotiation and Parallel Detection          |     |

|   |        | 3.4.3          | Automatic Crossover and Polarity Detection            |     |

|   |        | 3.4.4          | Manual MDI/MDIX Setting                               |     |

|   |        | 3.4.5          | Link Speed Downshift                                  |     |

|   |        | 3.4.6          | Energy-Efficient Ethernet                             |     |

|   |        | 3.4.7          | Ring Resiliency                                       | 14  |

|   | 3.5    | Referen        | ce Clock                                              | 14  |

|   | 3.6    | Etherne        | t Inline-Powered Devices                              | 15  |

|   | 3.7    | IEEE 80        | 2.3af Power-over-Ethernet Support                     | 17  |

|   | 3.8    |                | Power Management                                      |     |

|   |        | 3.8.1          | Low Power State                                       |     |

|   |        | 3.8.2          | Link Partner Wake-Up State                            | 18  |

|   |        | 3.8.3          | Normal Operating State                                | 18  |

|   | 3.9    | Media F        | Recovered Clock Output                                | 18  |

|   |        | 3.9.1          | Clock Output Squelch                                  | 18  |

|   | 3.10   | Serial M       | lanagement Interface                                  |     |

|   |        | 3.10.1         | SMI Frames                                            |     |

|   |        | 3.10.2         | SMI Interrupt                                         | 20  |

|   | 3.11   |                | erface                                                |     |

|   |        | 3.11.1         | LED Modes                                             |     |

|   |        | 3.11.2         | Basic Serial LED Mode                                 |     |

|   |        | 3.11.3         | Extended LED Modes                                    |     |

|   |        | 3.11.4         | LED Behavior                                          | 22  |

|   | 3.12  | Wake-C           | On-LAN and SecureOn                             | 23   |

|---|-------|------------------|-------------------------------------------------|------|

|   | 3.13  | Fast Lir         | nk Failure Indication                           | 24   |

|   | 3.14  | Fast Lin         | nk Failure 2™ (FLF2™) Indication                | 24   |

|   | 3.15  |                  | Frame (SOF) Indication (VSC8541-04 Only)        |      |

|   | 3.16  |                  | Speed Mode Link-Up Timing                       |      |

|   |       |                  | Features                                        |      |

|   | 3.17  | 3.17.1           | Ethernet Packet Generator                       |      |

|   |       | 3.17.1           | Far-End Loopback                                |      |

|   |       | 3.17.2           | Near-End Loopback                               |      |

|   |       | 3.17.4           | Connector Loopback                              |      |

|   |       | 3.17.5           | VeriPHY Cable Diagnostics                       |      |

|   | 3.18  |                  | ration                                          |      |

|   | 3.10  | 3.18.1           | Managed Applications                            |      |

|   |       | 3.18.2           | Unmanaged Applications                          |      |

|   |       | 3.18.3           | Initialization                                  |      |

|   |       | 0.10.0           |                                                 | 0    |

| 4 | Regis | ters             |                                                 | . 29 |

|   | 4.1   |                  | r and Bit Conventions                           |      |

|   | 4.2   | •                | 02.3 and Main Registers                         |      |

|   | 4.2   | 4.2.1            | Mode Control                                    |      |

|   |       | 4.2.1            | Mode Status                                     |      |

|   |       | 4.2.3            | Device Identification                           |      |

|   |       | 4.2.4            | Auto-Negotiation Advertisement                  |      |

|   |       | 4.2.5            | Link Partner Auto-Negotiation Capability        |      |

|   |       | 4.2.6            | Auto-Negotiation Expansion                      |      |

|   |       | 4.2.7            | Transmit Auto-Negotiation Next Page             |      |

|   |       | 4.2.8            | Auto-Negotiation Link Partner Next Page Receive |      |

|   |       | 4.2.9            | 1000BASE-T Control                              |      |

|   |       | 4.2.10           | 1000BASE-T Status                               |      |

|   |       | 4.2.11           | MMD Access Control Register                     |      |

|   |       | 4.2.12           | MMD Address or Data Register                    |      |

|   |       | 4.2.13           | 1000BASE-T Status Extension 1                   |      |

|   |       | 4.2.14           | 100BASE-TX Status Extension                     |      |

|   |       | 4.2.15           | 1000BASE-T Status Extension 2                   |      |

|   |       | 4.2.16           | Bypass Control                                  |      |

|   |       | 4.2.17           | Error Counter 1                                 |      |

|   |       | 4.2.18           | Error Counter 2                                 |      |

|   |       | 4.2.19           | Error Counter 3                                 |      |

|   |       | 4.2.20<br>4.2.21 | Extended Control and Status                     |      |

|   |       | 4.2.21           | Extended PHY Control 2                          |      |

|   |       | 4.2.23           | Interrupt Mask                                  |      |

|   |       | 4.2.24           | Interrupt Status                                |      |

|   |       | 4.2.25           | Device Auxiliary Control and Status             |      |

|   |       | 4.2.26           | LED Mode Select                                 |      |

|   |       | 4.2.27           | LED Behavior                                    |      |

|   |       | 4.2.28           | Extended Page Access                            |      |

|   | 4.3   | Extende          | ed Page 1 Registers                             |      |

|   |       | 4.3.1            | VeriPHY Status 1                                |      |

|   |       | 4.3.2            | VeriPHY Status 2                                |      |

|   |       | 4.3.3            | Cu Media CRC Good Counter                       |      |

|   |       | 4.3.4            | Extended Mode Control                           |      |

|   |       | 4.3.5            | ActiPHY Control                                 |      |

|   |       | 4.3.6            | PoE and Miscellaneous Functionality             | 48   |

|   |       | 4.3.7            | VeriPHY Control 1                               |      |

|   |       | 4.3.8            | VeriPHY Control 2                               |      |

|   |       | 4.3.9            | VeriPHY Control 3                               | 49   |

|   |               | 4.3.10<br>4.3.11                                                                                                                                                                                                                               | Ethernet Packet Generator (EPG) Control 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                              |

|---|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 4.4           |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              |

|   | 4.4           |                                                                                                                                                                                                                                                | ed Page 2 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                              |

|   |               | 4.4.1                                                                                                                                                                                                                                          | Cu PMD Transmit Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                              |

|   |               | 4.4.2                                                                                                                                                                                                                                          | EEE Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                              |

|   |               | 4.4.3                                                                                                                                                                                                                                          | RGMII Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                              |

|   |               | 4.4.4                                                                                                                                                                                                                                          | Wake-on-LAN MAC Address [15:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |

|   |               | 4.4.5                                                                                                                                                                                                                                          | Wake-on-LAN MAC Address [31:16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              |

|   |               | 4.4.6<br>4.4.7                                                                                                                                                                                                                                 | Wake-on-LAN MAC Address [47:32]                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              |

|   |               | 4.4.7<br>4.4.8                                                                                                                                                                                                                                 | Secure-On Password [15:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                              |

|   |               | 4.4.8<br>4.4.9                                                                                                                                                                                                                                 | Secure-On Password [31:16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                              |

|   |               | 4.4.9<br>4.4.10                                                                                                                                                                                                                                | Secure-On Password [47:32]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                              |

|   |               | 4.4.11                                                                                                                                                                                                                                         | Extended Interrupt Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                              |

|   |               | 4.4.11                                                                                                                                                                                                                                         | Extended Interrupt Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                              |

|   |               | 4.4.13                                                                                                                                                                                                                                         | Ring Resiliency Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                              |

|   | 4.5           | _                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              |

|   | 4.5           |                                                                                                                                                                                                                                                | Purpose Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              |

|   |               | 4.5.1                                                                                                                                                                                                                                          | CLKOUT Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |

|   |               | 4.5.2<br>4.5.3                                                                                                                                                                                                                                 | GPIO Control 2  Fast Link Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                              |

|   |               | 4.5.4<br>4.5.4                                                                                                                                                                                                                                 | Recovered Clock Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                              |

|   |               | 4.5.5                                                                                                                                                                                                                                          | Enhanced LED Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                              |

|   | 4.0           |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              |

|   | 4.6           | 4.6.1                                                                                                                                                                                                                                          | 45 Registers to Support Energy-Efficient Ethernet and 802.3bf                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                              |

|   |               | 4.6.1                                                                                                                                                                                                                                          | PCS Status 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                              |

|   |               | 4.6.3                                                                                                                                                                                                                                          | EEE Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |

|   |               | 4.6.4                                                                                                                                                                                                                                          | EEE Wake Error Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                              |

|   |               | 4.6.5                                                                                                                                                                                                                                          | EEE Advertisement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              |

|   |               | 4.6.6                                                                                                                                                                                                                                          | EEE Link Partner Advertisement                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |

|   |               |                                                                                                                                                                                                                                                | LLE Link rathor havorboomont                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                              |

|   |               |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              |

| 5 | Electr        | ical Sp                                                                                                                                                                                                                                        | ecifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65                                                                                                                                                           |

| 5 | Electr<br>5.1 |                                                                                                                                                                                                                                                | ecifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                              |

| 5 |               |                                                                                                                                                                                                                                                | racteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 65                                                                                                                                                         |

| 5 |               | DC Cha                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 65<br>. 65                                                                                                                                                 |

| 5 |               | DC Cha<br>5.1.1                                                                                                                                                                                                                                | racteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 65<br>. 65<br>. 65                                                                                                                                         |

| 5 |               | DC Cha<br>5.1.1<br>5.1.2                                                                                                                                                                                                                       | vacteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 65<br>. 65<br>. 65                                                                                                                                         |

| 5 |               | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3                                                                                                                                                                                                              | VDDMAC, VDDIO, and VDDMDIO (2.5 V) VDDMAC, VDDIO, and VDDMDIO (3.3 V) VDDMAC and VDDMDIO (1.5 V) VDDMAC and VDDMDIO (1.8 V) VDDMDIO (1.2 V)                                                                                                                                                                                                                                                                                                                                                                  | . 65<br>. 65<br>. 66<br>. 66                                                                                                                                 |

| 5 |               | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4                                                                                                                                                                                                     | VDDMAC, VDDIO, and VDDMDIO (2.5 V) VDDMAC, VDDIO, and VDDMDIO (3.3 V) VDDMAC and VDDMDIO (1.5 V) VDDMAC and VDDMDIO (1.8 V) VDDMDIO (1.2 V) XTAL1                                                                                                                                                                                                                                                                                                                                                            | . 65<br>. 65<br>. 66<br>. 66<br>. 66                                                                                                                         |

| 5 |               | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5                                                                                                                                                                                            | VDDMAC, VDDIO, and VDDMDIO (2.5 V) VDDMAC, VDDIO, and VDDMDIO (3.3 V) VDDMAC and VDDMDIO (1.5 V) VDDMAC and VDDMDIO (1.8 V) VDDMDIO (1.2 V) XTAL1 LED                                                                                                                                                                                                                                                                                                                                                        | . 65<br>. 65<br>. 66<br>. 66<br>. 67                                                                                                                         |

| 5 |               | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6                                                                                                                                                                                   | VDDMAC, VDDIO, and VDDMDIO (2.5 V) VDDMAC, VDDIO, and VDDMDIO (3.3 V) VDDMAC and VDDMDIO (1.5 V) VDDMAC and VDDMDIO (1.8 V) VDDMDIO (1.2 V) XTAL1                                                                                                                                                                                                                                                                                                                                                            | . 65<br>. 65<br>. 66<br>. 66<br>. 67                                                                                                                         |

| 5 |               | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9                                                                                                                                                        | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC, VDDIO, and VDDMDIO (3.3 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption                                                                                                                                                                                                                                                                      | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67                                                                                                                 |

| 5 |               | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8                                                                                                                                                                 | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC, VDDIO, and VDDMDIO (3.3 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors                                                                                                                                                                                                                                                                                           | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67                                                                                                                 |

| 5 |               | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10                                                                                                                                              | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC, VDDIO, and VDDMDIO (3.3 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption                                                                                                                                                                                                                                                                      | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67                                                                                                         |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1                                                                                                                           | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC, VDDIO, and VDDMDIO (3.3 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption  Thermal Diode                                                                                                                                                                                                                                                       | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67                                                                                                         |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2                                                                                                                  | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC, VDDIO, and VDDMDIO (3.3 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption  Thermal Diode  racteristics  Reference Clock  Recovered Clock                                                                                                                                                                                                       | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67<br>. 69<br>. 69                                                                                         |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2<br>5.2.3                                                                                                         | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC, VDDIO, and VDDMDIO (3.3 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption  Thermal Diode  racteristics  Reference Clock  Recovered Clock  CLKOUT                                                                                                                                                                                               | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67<br>. 69<br>. 70                                                                                         |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                                                                                                | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC, VDDIO, and VDDMDIO (3.3 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption  Thermal Diode  racteristics  Reference Clock  Recovered Clock  CLKOUT  RMII_CLKOUT                                                                                                                                                                                  | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67<br>. 69<br>. 70<br>. 71                                                                                 |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                                                                                       | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC, VDDIO, and VDDMDIO (3.3 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption  Thermal Diode  racteristics  Reference Clock  Recovered Clock  CLKOUT  RMII_CLKOUT  Basic Serial LEDs                                                                                                                                                               | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 69<br>. 70<br>. 71                                                                                         |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6                                                                              | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC, VDDIO, and VDDMDIO (3.3 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption  Thermal Diode  racteristics  Reference Clock  Recovered Clock  CLKOUT  RMII_CLKOUT  Basic Serial LEDs  RMII AC Characteristics                                                                                                                                      | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 69<br>. 70<br>. 71<br>. 71                                                                                 |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7                                                                     | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC, VDDIO, and VDDMDIO (3.3 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption  Thermal Diode  racteristics  Reference Clock Recovered Clock CLKOUT  RMII_CLKOUT  Basic Serial LEDs  RMII AC Characteristics  GMII Transmit                                                                                                                         | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67<br>. 69<br>. 70<br>. 71<br>. 71<br>. 72                                                                 |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8                                                            | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC, VDDIO, and VDDMDIO (3.3 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption  Thermal Diode  racteristics  Reference Clock Recovered Clock CLKOUT  RMII_CLKOUT Basic Serial LEDs  RMII AC Characteristics  GMII Transmit GMII Receive                                                                                                             | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67<br>. 69<br>. 70<br>. 71<br>. 72<br>. 72<br>. 72                                                         |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9                                                   | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC, VDDIO, and VDDMDIO (3.3 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption  Thermal Diode  racteristics  Reference Clock  Recovered Clock  CLKOUT  RMII_CLKOUT  Basic Serial LEDs  RMII AC Characteristics  GMII Transmit  GMII Receive  MII Transmit                                                                                           | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67<br>. 69<br>. 70<br>. 71<br>. 71<br>. 72<br>. 72<br>. 73<br>. 74                                         |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>5.2.10                                         | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC, VDDIO, and VDDMDIO (3.3 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption  Thermal Diode  racteristics  Reference Clock  Recovered Clock  CLKOUT  RMII_CLKOUT  Basic Serial LEDs  RMII AC Characteristics  GMII Transmit  GMII Receive  MII Transmit  MII Receive                                                                              | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67<br>. 69<br>. 71<br>. 71<br>. 72<br>. 72<br>. 73<br>. 74                                                 |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>5.2.10<br>5.2.11                               | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption  Thermal Diode  racteristics  Reference Clock  Recovered Clock  CLKOUT  RMII_CLKOUT  Basic Serial LEDs  RMII AC Characteristics  GMII Transmit  GMII Receive  MII Transmit  MII Receive  Uncompensated RGMII                                                                 | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67<br>. 69<br>. 70<br>. 71<br>. 72<br>. 72<br>. 73<br>. 74<br>. 74                                         |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>5.2.10<br>5.2.11<br>5.2.12                     | racteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption  Thermal Diode  racteristics  Reference Clock  Recovered Clock  CLKOUT  RMII_CLKOUT  Basic Serial LEDs  RMII AC Characteristics  GMII Transmit  GMII Receive  MII Transmit  MII Receive  Uncompensated RGMII  Compensated RGMII                                              | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67<br>. 68<br>. 69<br>. 70<br>. 71<br>. 71<br>. 72<br>. 72<br>. 74<br>. 75<br>. 76                         |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>5.2.10<br>5.2.11<br>5.2.12<br>5.2.13           | VDDMAC, VDDIO, and VDDMDIO (2.5 V) VDDMAC, VDDIO, and VDDMDIO (3.3 V) VDDMAC and VDDMDIO (1.5 V) VDDMAC and VDDMDIO (1.8 V) VDDMDIO (1.2 V) XTAL1 LED Internal Pull-Up or Pull-Down Resistors Current Consumption Thermal Diode racteristics Reference Clock Recovered Clock CLKOUT RMII_CLKOUT Basic Serial LEDs RMII AC Characteristics GMII Transmit GMII Receive MII Transmit MII Receive Uncompensated RGMII Compensated RGMII Compensated RGMII Start of Frame Indication                              | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67<br>. 71<br>. 72<br>. 72<br>. 72<br>. 73<br>. 74<br>. 75<br>. 76<br>. 77                                 |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>5.2.10<br>5.2.11<br>5.2.12<br>5.2.13<br>5.2.14 | vracteristics  VDDMAC, VDDIO, and VDDMDIO (2.5 V)  VDDMAC and VDDMDIO (1.5 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMAC and VDDMDIO (1.8 V)  VDDMDIO (1.2 V)  XTAL1  LED  Internal Pull-Up or Pull-Down Resistors  Current Consumption  Thermal Diode  racteristics  Reference Clock  Recovered Clock  CLKOUT  RMII_CLKOUT  Basic Serial LEDs  RMII AC Characteristics  GMII Transmit  GMII Transmit  GMII Receive  Uncompensated RGMII  Compensated RGMII  Start of Frame Indication  Serial Management Interface | . 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 71<br>. 72<br>. 72<br>. 72<br>. 73<br>. 74<br>. 75<br>. 76<br>. 77<br>. 77<br>. 77         |

| 5 | 5.1           | DC Cha<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>AC Cha<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>5.2.10<br>5.2.11<br>5.2.12<br>5.2.13           | VDDMAC, VDDIO, and VDDMDIO (2.5 V) VDDMAC, VDDIO, and VDDMDIO (3.3 V) VDDMAC and VDDMDIO (1.5 V) VDDMAC and VDDMDIO (1.8 V) VDDMDIO (1.2 V) XTAL1 LED Internal Pull-Up or Pull-Down Resistors Current Consumption Thermal Diode racteristics Reference Clock Recovered Clock CLKOUT RMII_CLKOUT Basic Serial LEDs RMII AC Characteristics GMII Transmit GMII Receive MII Transmit MII Receive Uncompensated RGMII Compensated RGMII Compensated RGMII Start of Frame Indication                              | . 65<br>. 65<br>. 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 71<br>. 72<br>. 72<br>. 72<br>. 73<br>. 75<br>. 75<br>. 75<br>. 75<br>. 75<br>. 75<br>. 75<br>. 75 |

|   | 5.3   | Operating Conditions                                                                | 79 |

|---|-------|-------------------------------------------------------------------------------------|----|

|   | 5.4   | Stress Ratings                                                                      |    |

| 6 | Pin [ | Descriptions                                                                        | 81 |

|   | 6.1   | Pin Identifications                                                                 |    |

|   | 6.2   | Pin Diagram                                                                         |    |

|   | 6.3   | Pins by Function                                                                    |    |

| 7 | Pack  | age Information                                                                     | 87 |

| • | 7.1   | Package Drawing                                                                     |    |

|   | 7.1   | Thermal Specifications                                                              |    |

|   | 7.3   | Moisture Sensitivity                                                                |    |

| 8 | Desi  | gn Considerations                                                                   | 90 |

|   | 8.1   | Link status LED remains on while COMA_MODE pin is asserted high                     |    |

|   | 8.2   | LED pulse stretch enable turns off LED pins                                         |    |

|   | 8.3   | Forced 1000BASE-T mode blocks some SMI register writes                              |    |

|   | 8.4   | Forced 1000BASE-T mode incorrectly reports interrupt status and PCS status counters |    |

|   | 8.5   | 10BASE-T signal amplitude                                                           |    |

|   | 8.6   | Receive error counter only clears when NRESET applied in RMII mode                  |    |

|   | 8.7   | Anomalous PCS error indications in Energy Efficient Ethernet mode                   |    |

|   | 8.8   | 10BASE-T half-duplex linkup after initial reset from power up                       |    |

| 9 | Orde  | ring Information                                                                    | 92 |

# **Figures**

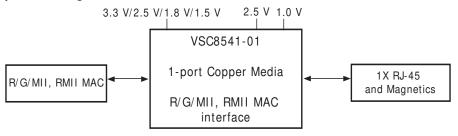

| Figure 1  | Application Diagram                                | 2  |

|-----------|----------------------------------------------------|----|

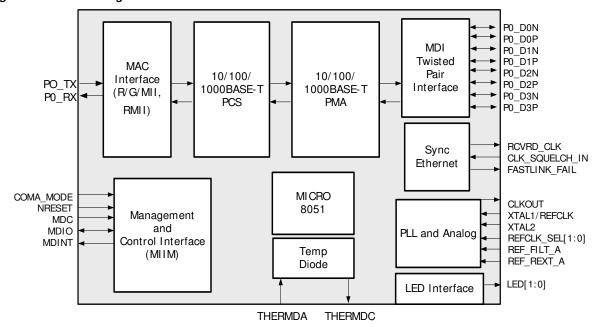

| Figure 2  | Block Diagram                                      |    |

| Figure 3  | RGMII MAC Interface                                | Ę  |

| Figure 4  | GMII/MII MAC Interface                             | Ę  |

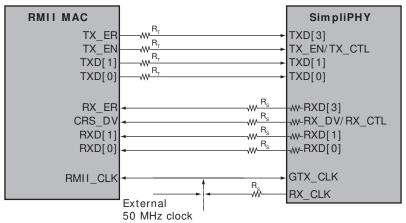

| Figure 5  | RMII MAC Interface                                 | 6  |

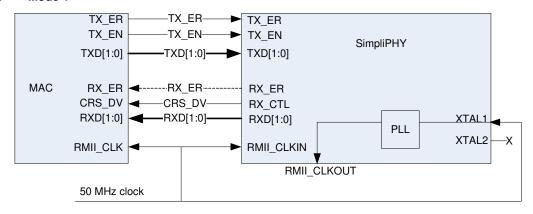

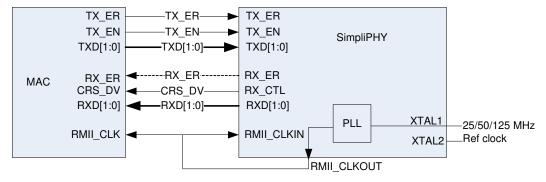

| Figure 6  | Mode 1                                             | 7  |

| Figure 7  | Mode 2                                             | 7  |

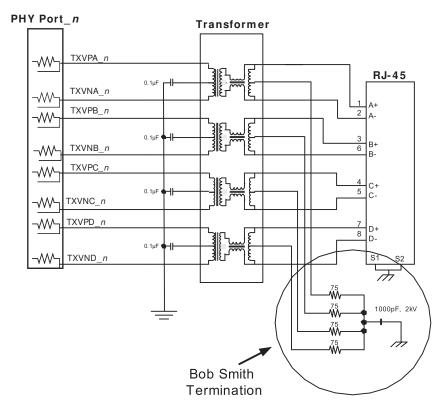

| Figure 8  | Cat5 Media Interface                               | 2  |

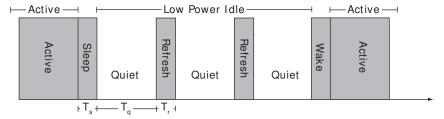

| Figure 9  | Low Power Idle Operation 1                         | 3  |

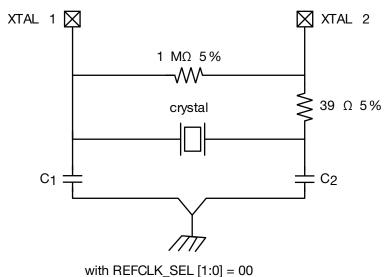

| Figure 10 | XTAL Reference Clock                               | 4  |

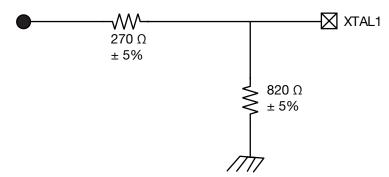

| Figure 11 | External 3.3 V Reference Clock                     |    |

| Figure 12 | Inline-Powered Ethernet Switch Diagram             | 6  |

| Figure 13 | ActiPHY State Diagram                              | 7  |

| Figure 14 | SMI Read Frame1                                    | ζ  |

| Figure 15 | SMI Write Frame                                    | ζ  |

| Figure 16 | MDINT Configured as an Open-Drain (Active-Low) Pin | (  |

| Figure 17 | Wake-on-LAN Functionality                          | 2  |

| Figure 18 | SOF Indication                                     | )[ |

| Figure 19 | Far-End Loopback Diagram                           | 26 |

| Figure 20 | Near-End Loopback Diagram                          |    |

| Figure 21 | Connector Loopback Diagram                         | 26 |

| Figure 22 | Register Space Diagram                             | į  |

| Figure 23 | Thermal Diode6                                     |    |

| Figure 24 | Test Circuit for Recovered Clock Outputs Signal    |    |

| Figure 25 | Basic Serial LED Timing                            |    |

| Figure 26 | GMII Transmit Timing                               | "  |

| Figure 27 | GMII Receive Timing                                | ′∠ |

| Figure 28 | MII Transmit Timing                                | ′∠ |

| Figure 29 | MII Receive Timing                                 |    |

| Figure 30 | Uncompensated RGMII Timing                         | '( |

| Figure 31 | Compensated Input RGMII Timing                     |    |

| Figure 32 | Compensated Output RGMII Timing                    | 7  |

| Figure 33 | SOF Indication Timing                              |    |

| Figure 34 | Serial Management Interface Timing                 |    |

| Figure 35 | Pin Diagram 8                                      |    |

| Figure 36 | Package Drawing                                    | 38 |

# **Tables**

| Table 1              | Operating Modes                                         | . 4 |

|----------------------|---------------------------------------------------------|-----|

| Table 2              | Recommended Values for R <sub>S</sub> (± 5%)            |     |

| Table 3              | RMII Pin Allocation                                     |     |

| Table 4              | Recommended Edge Rate Settings                          |     |

| Table 5              | MAC Interface Edge Rate Control                         |     |

| Table 6              | Hardware Mode Strapping and PHY Addressing              |     |

| Table 7              | Managed Mode                                            |     |

| Table 8              | Signals A and B                                         | 10  |

| Table 9              | Signals C and D                                         |     |

| Table 10             | CLKOUT Frequency Selection                              |     |

| Table 11             | Supported MDI Pair Combinations                         |     |

| Table 12             | REFCLK Frequency Selection                              |     |

| Table 13             | LED Drive State                                         |     |

| Table 13             | LED Mode and Function Summary                           |     |

| Table 14             | LED Serial Bitstream Order                              |     |

|                      |                                                         |     |

| Table 16<br>Table 17 | Extended LED Mode and Function Summary                  |     |

|                      | SOF Indication                                          |     |

| Table 18             | Forced Speed Mode Link-Up Timing                        |     |

| Table 19             | IEEE 802.3 Registers                                    |     |

| Table 20             | Main Registers                                          |     |

| Table 21             | Mode Control, Address 0 (0x00)                          |     |

| Table 22             | Mode Status, Address 1 (0x01)                           |     |

| Table 23             | Identifier 1, Address 2 (0x02)                          |     |

| Table 24             | Identifier 2, Address 3 (0x03)                          |     |

| Table 25             | Device Auto-Negotiation Advertisement, Address 4 (0x04) |     |

| Table 26             | Auto-Negotiation Link Partner Ability, Address 5 (0x05) | 33  |

| Table 27             | Auto-Negotiation Expansion, Address 6 (0x06)            |     |

| Table 28             | Auto-Negotiation Next Page Transmit, Address 7 (0x07)   | 34  |

| Table 29             | Auto-Negotiation LP Next Page Receive, Address 8 (0x08) |     |

| Table 30             | 1000BASE-T Control, Address 9 (0x09)                    |     |

| Table 31             | 1000BASE-T Status, Address 10 (0x0A)                    |     |

| Table 32             | MMD EEE Access, Address 13 (0x0D)                       |     |

| Table 33             | MMD Address or Data Register, Address 14 (0x0E)         |     |

| Table 34             | 1000BASE-T Status Extension 1, Address 15 (0x0F)        |     |

| Table 35             | 100BASE-TX Status Extension, Address 16 (0x10)          |     |

| Table 36             | 1000BASE-T Status Extension 2, Address 17 (0x11)        |     |

| Table 37             | Bypass Control, Address 18 (0x12)                       |     |

| Table 38             | Extended Control and Status, Address 19 (0x13)          |     |

| Table 39             | Extended Control and Status, Address 20 (0x14)          | 39  |

| Table 40             | Extended Control and Status, Address 21 (0x15)          | 39  |

| Table 41             | Extended Control and Status, Address 22 (0x16)          | 39  |

| Table 42             | Extended PHY Control 1, Address 23 (0x17)               | 40  |

| Table 43             | Extended PHY Control 2, Address 24 (0x18)               | 41  |

| Table 44             | Interrupt Mask, Address 25 (0x19)                       |     |

| Table 45             | Interrupt Status, Address 26 (0x1A)                     |     |

| Table 46             | Auxiliary Control and Status, Address 28 (0x1C)         |     |

| Table 47             | LED Mode Select, Address 29 (0x1D)                      |     |

| Table 48             | LED Behavior, Address 30 (0x1E)                         |     |

| Table 49             | Extended/GPIO Register Page Access, Address 31 (0x1F)   | 45  |

| Table 50             | Extended Registers Page 1 Space                         |     |

| Table 51             | VeriPHY Status Register 1, Address 16E1 (0x10)          | 45  |

| Table 52             | VeriPHY Status Register 2, Address 17E1 (0x11)          |     |

| Table 53             | Cu Media CRC Good Counter, Address 18E1 (0x12)          |     |

| Table 54             | Extended Mode Control, Address 19E1 (0x13)              |     |

| Table 55  | Extended PHY Control 3, Address 20E1 (0x14)                             |    |

|-----------|-------------------------------------------------------------------------|----|

| Table 56  | Extended PHY Control 4, Address 23E1 (0x17)                             |    |

| Table 57  | VeriPHY Control Register 1, Address 24E1 (0x18)                         | 48 |