Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

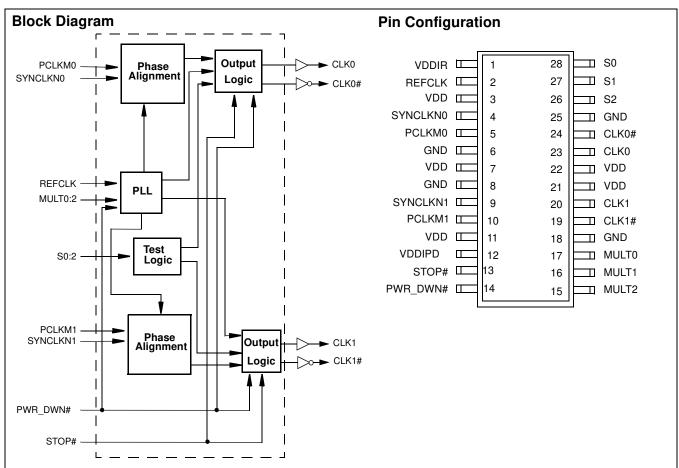

# Dual Direct Rambus™ Clock Generator

#### **Features**

- Differential clock source for Direct Rambus<sup>™</sup> memory subsystem for up to 1.6-Gb/s serial data transfer rate

- Provide synchronization flexibility: the Rambus<sup>®</sup> Channel can optionally be synchronous to an external system or processor clock

- Power managed output allows Rambus Channel clock to be turned off to minimize power consumption for mobile applications

- Works with Cypress CY2210-2, CY2210-3, CY2215, W133, W158, W159, W161, and W167B to support Intel<sup>®</sup> architecture platforms

- Low-power CMOS design packaged in a 28-pin, 173-mil TSSOP package

#### Overview

The Cypress W234 provides dual channel differential clock signals for a Direct Rambus memory subsystem. It includes signals to synchronize the Direct Rambus Channel clock to an external system clock but can also be used in systems that do not require synchronization of the Rambus clock.

#### **Key Specifications**

| Supply Voltage:          | $V_{DD} = 3.3V \pm 0.165V$   |

|--------------------------|------------------------------|

| Operating Temperature:   | 0°C to +70°C                 |

| Input Threshold:         | 1.5V typical                 |

| Maximum Input Voltage:   | V <sub>DD</sub> + 0.5V       |

| Maximum Input Frequency: | 100 MHz                      |

| Output Duty Cycle:       | 40/60% worst case            |

| Output Type:I            | Rambus signaling level (RSL) |

Direct Rambus is a trademark and Rambus is a registered trademark of Rambus Inc. Intel is a registered trademark of Intel Corporation.

## **Pin Definitions**

| Pin Name                    | Pin<br>No.          | Pin<br>Type |                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                       | Pin Descript                                  | ion                                            |                                                                               |  |

|-----------------------------|---------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------|--|

| REFCLK                      | 2                   | I           |                                                                                                                                                                                                                                                                                                                          | <b>Reference Clock Input:</b> Reference clock input, normally supplied by a system frequency synthesizer (Cypress W133).                                                                                                                                                                                              |                                               |                                                |                                                                               |  |

| PCLKM0:1                    | 5, 10               | I           | Phase Detector Input 0:1: The phase difference between this signal and SYN-CLKN is used to synchronize the Rambus Channel Clock with the system clock. Both PCLKM and SYNCLKN are provided by the Gear Ratio Logic in the memory controller. If the Gear Ratio Logic is not used, this pin would be connected to ground. |                                                                                                                                                                                                                                                                                                                       |                                               |                                                |                                                                               |  |

| SYNCLKN0:1                  | 4, 9                | I           | is used to synchror<br>PCLKM and SYNC<br>troller. If the Gear F                                                                                                                                                                                                                                                          | Phase Detector Input 0:1: The phase difference between this signal and PCLKM is used to synchronize the Rambus Channel Clock with the system clock. Both PCLKM and SYNCLKN are provided by the Gear Ratio Logic in the memory controller. If the Gear Ratio Logic is not used, this pin would be connected to ground. |                                               |                                                |                                                                               |  |

| STOP#                       | 13                  | I           | Clock Output Ena<br>differential Rambus                                                                                                                                                                                                                                                                                  | <b>ble:</b> When t<br>Channel cl                                                                                                                                                                                                                                                                                      | his input is driv<br>ocks.                    | en to active L                                 | OW, it disables the                                                           |  |

| PWR_DWN#                    | 14                  | I           | Active LOW Power-Down: When this input is driven to active LOW, it disables the differential Rambus Channel clocks and places the W234 in Power-Down mode.                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                       |                                               |                                                |                                                                               |  |

| MULT 0:2                    | 17, 16, 15          | I           | <b>PLL Multiplier Select:</b> These inputs select the PLL prescaler and feedback dividers to determine the multiply ratio for the PLL for the input REFCLK.                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                       |                                               |                                                |                                                                               |  |

|                             |                     |             | MULTO 0 0 0 1 1 1 1                                                                                                                                                                                                                                                                                                      | MULT1<br>0<br>0<br>1<br>1<br>0<br>0<br>0                                                                                                                                                                                                                                                                              | MULT2<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | A<br>4<br>9<br>6<br>TBD<br>8<br>16<br>8<br>TBD | B<br>1<br>2<br>1<br>TBD<br>3<br>3<br>1<br>TBD                                 |  |

| CLK0, CLK0#,<br>CLK1, CLK1# | 23, 24, 20,<br>19   | 0           | Complementary C                                                                                                                                                                                                                                                                                                          | Output Cloc                                                                                                                                                                                                                                                                                                           | <b>k:</b> Differential F                      | Rambus Char                                    | nnel clock outputs.                                                           |  |

| S0, S1, S2                  | 28, 27, 26          | I           | Mode Control Inp.  S0  0  1  1  0  1  0                                                                                                                                                                                                                                                                                  | <b>ut:</b> These in                                                                                                                                                                                                                                                                                                   | puts control the                              | S2<br>0<br>0<br>0<br>1<br>1                    | MODE Normal Bypass Test Vendor Test A Vendor Test B Reserved Output Test (OE) |  |

| VDDIR                       | 1                   | RefV        | Reference for Ref                                                                                                                                                                                                                                                                                                        | •                                                                                                                                                                                                                                                                                                                     |                                               | •                                              |                                                                               |  |

| VDDIPD                      | 12                  | RefV        | STOP#.                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                       | J                                             | •                                              | se detector inputs and                                                        |  |

| VDD                         | 3, 7, 11, 21,<br>22 | Р           | <b>Power Connection:</b> Power supply for core logic and output buffers. Connected to 3.3V supply.                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                       |                                               |                                                |                                                                               |  |

| GND                         | 6, 8, 18, 25        | G           | Ground Connection plane.                                                                                                                                                                                                                                                                                                 | <i>on:</i> Connect                                                                                                                                                                                                                                                                                                    | all ground pin                                | s to the comm                                  | non system ground                                                             |  |

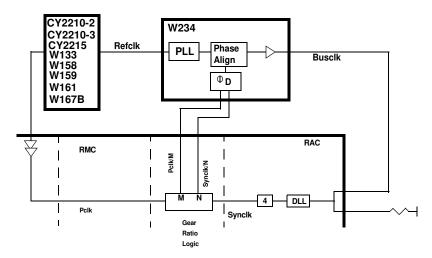

Figure 1. DDLL System Architecture.

#### **DDLL System Architecture and Gear Ratio Logic**

Figure 1 shows the Distributed Delay Lock Loop (DDLL) system architecture, including the main system clock source, the Direct Rambus clock generator (DRCG), and the core logic that contains the Rambus Access Cell (RAC), the Rambus Memory Controller (RMC), and the Gear Ratio Logic. (This diagram abstractly represents the differential clocks as a single Busclk wire.)

The purpose of the DDLL is to frequency-lock and phase-align the core logic and Rambus clocks (PCLK and SYNCLK) at the RMC/RAC boundary in order to allow data transfers without incurring additional latency. In the DDLL architecture, a PLL is used to generate the desired Busclk frequency, while a distributed loop forms a DLL to align the phase of Pclk and Synclk at the RMC/RAC boundary.

The main clock source drives the system clock (Pclk) to the core logic, and also drives the reference clock (Refclk) to the DRCG. For typical Intel architecture platforms, Refclk will be half the CPU front side bus frequency. A PLL inside the DRCG multiplies Refclk to generate the desired frequency for Busclk, and Busclk is driven through a terminated transmission line (Rambus Channel). At the mid-point of the channel, the RAC senses Busclk using its own DLL for clock alignment, followed by a fixed divide-by-4 that generates Synclk.

Pclk is the clock used in the memory controller (RMC) in the core logic, and Synclk is the clock used at the core logic inter-

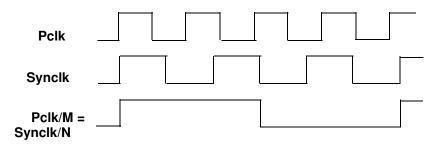

face of the RAC. The DDLL together with the Gear Ratio Logic enables users to exchange data directly from the Pclk domain to the Synclk domain without incurring additional latency for synchronization. In general, Pclk and Synclk can be of different frequencies, so the Gear Ratio Logic must select the appropriate M and N dividers such that the frequencies of Pclk/M and Synclk/N are equal. In one interesting example, Pclk=133 MHz, Synclk=100 MHz, and M=4 while N=3, giving Pclk/M=Synclk/N=33 MHz. This example of the clock waveforms with the Gear Ratio Logic is shown in Figure 2.

The output clocks from the Gear Ratio Logic, Pclk/M, and Synclk/N, are output from the core logic and routed to the DRCG Phase Detector  $(\phi_D)$  inputs. The routing of Pclk/M and Synclk/N must be matched in the core logic as well as on the board.

After comparing the phase of Pclk/M vs. Synclk/N, the DRCG Phase Detector  $(\phi_D)$  drives a phase aligner that adjusts the phase of the DRCG output clock, Busclk. Since everything else in the distributed loop is fixed delay, adjusting Busclk adjusts the phase of Synclk and thus the phase of Synclk/N. In this manner the distributed loop adjusts the phase of Synclk/N to match that of Pclk/M, nulling the phase error at the input of the DRCG Phase Detector  $(\phi_D)$ . When the clocks are aligned, data can be exchanged directly from the Pclk domain to the Synclk domain.

Figure 2. Gear Ratio Timing Diagram.

Document #: 38-07232 Rev. \*B Page 3 of 14

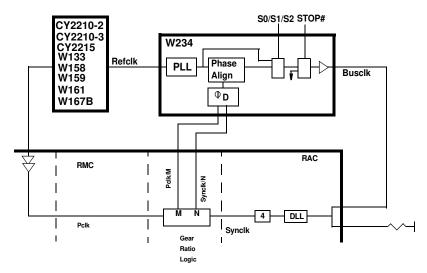

Figure 3. DDLL Including Details of DRCG.

#### **Phase Detector Signals**

The DRCG Phase Detector  $(\varphi_D)$  receives two inputs from the core logic, PCLKM (Pclk/M) and SYNCLKN (Synclk/N). The M and N dividers in the core logic are chosen so that the frequencies of PCLKM and SYNCLKN are identical. The Phase Detector  $(\varphi_D)$  detects the phase difference between the two input clocks, and drives the DRCG Phase Aligner to null the input phase error through the distributed loop. When the loop is locked, the input phase error between PCLKM and SYNCLKN is within the specification  $t_{ERR,PD}$  given in Table 13 after the lock time given in the State Transition Section.

The Phase Detector  $(\phi_D)$  aligns the rising edge of PCLKM to the rising edge of SYNCLKN. The duty cycle of the phase detector input clocks will be within the specification  $DC_{IN,PD}$  given in *Table 12*. Because the duty cycles of the two phase detector input clocks will not necessarily be identical, the falling edges of PCLKM and SYNCLKN may not be aligned when the rising edges are aligned.

The voltage levels of the PCLKM and SYNCLKN signals are determined by the controller. The pin VDDIPD is used as the voltage reference for the phase detector inputs and should be connected to the output voltage supply of the controller. In some applications, the DRCG PLL output clock will be used directly, by bypassing the Phase Aligner. If PCLKM and SYNCLKN are not used, those inputs must be grounded.

#### **Selection Logic**

Table 1 shows the logic for selecting the PLL prescaler and feedback dividers to determine the multiply ratio for the PLL from the input Refclk. Divider A sets the feedback and divider B sets the prescaler, so the PLL output clock frequency is set by: PLLClk=Refclk\*A/B.

Table 1. PLL Divider Selection

| MULT0 | MULT1 | MULT2 | Α   | В  |  |

|-------|-------|-------|-----|----|--|

| 0     | 0     | 0     | 4   | 1  |  |

| 0     | 0     | 1     | 9   | 2  |  |

| 0     | 1     | 0     | 6   | 1  |  |

| 0     | 1     | 1     | TBD |    |  |

| 1     | 0     | 0     | 8   | 3  |  |

| 1     | 0     | 1     | 16  | 3  |  |

| 1     | 1     | 0     | 8   | 1  |  |

| 1     | 1     | 1     | TE  | 3D |  |

Table 2 shows the logic for enabling the clock outputs, using the STOP# input signal. When STOP# is HIGH, the DRCG is in its normal mode, and CLK and CLK# are complementary outputs following the Phase Aligner output (PAclk). When STOP# is LOW, the DRCG is in the Clk Stop mode, the output clock drivers are disabled (set to Hi-Z), and the CLK and CLK# settle to the DC voltage  $V_{X,STOP}$  as given in Table 13. The level of  $V_{X,STOP}$  is set by an external resistor network.

Table 2. Clk Stop Mode Selection

| Mode     | STOP# | CLK          | CLK#         |  |

|----------|-------|--------------|--------------|--|

| Normal   | 1     | PACLK        | PACLK#       |  |

| Clk Stop | 0     | $V_{X,STOP}$ | $V_{X,STOP}$ |  |

Table 3 shows the logic for selecting the Bypass and Test modes. The select bits, S0, S1, and S2 control the selection of these modes. The Bypass mode brings out the full-speed PLL output clock, bypassing the Phase Aligner. The Test mode brings the REFCLK input all the way to the output, bypassing both the PLL and the Phase Aligner. In the Output Test mode (OE), both the CLK and CLK# outputs are put into a high-impedance state (Hi-Z). This can be used for component testing and for board-level testing.

Table 3. Bypass and Test Mode Selection

| Mode                | S0      | S1 | S2 | By Pclk<br>(int.) | CLK    | CLK#    |

|---------------------|---------|----|----|-------------------|--------|---------|

| Normal              | 0       | 0  | 0  | Gnd               | PACIk  | PACIk#  |

| Bypass              | 1       | 0  | 0  | PLLCIk            | PLLCIk | PLLCIk# |

| Test                | 1       | 1  | 0  | RefClk            | RefClk | RefClk# |

| Vendor Test<br>A    | 0       | 0  | 1  | -                 | -      | -       |

| Vendor Test<br>B    | 1 0 1 - |    | -  | -                 |        |         |

| Reserved            | 1       | 1  | 1  | =                 | -      | =       |

| Output Test<br>(OE) | 0       | 1  | Х  | -                 | Hi-Z   | RefClk# |

Table 4 shows the logic for selecting the Power-Down mode, using the PWR\_DWN# input signal. PWR\_DWN# is active LOW (enabled when 0). When PWR\_DWN# is disabled, the DRCG is in its normal mode. When PWR\_DWN# is enabled, the DRCG is put into a powered-off state, and the CLK and CLK# outputs are three-stated.

Table 4. PWR DWN# Mode Selection

| Mode       | PWR_DWN# | CLK   | CLK#   |  |

|------------|----------|-------|--------|--|

| Normal     | 1        | PACIk | PACIk# |  |

| Power-Down | 0        | GND   | GND    |  |

#### **Table of Frequencies and Gear Ratios**

Table 5 shows several supported Pclk and Busclk frequencies, the corresponding A and B dividers required in the DRCG PLL,

and the corresponding M and N dividers in the gear ratio logic. The column Ratio gives the Gear Ratio as defined Pclk/Synclk (same as M and N). The column F@PD gives the divided down frequency (in MHz) at the Phase Detector  $(\phi_D)$ , where F@PD = PCLK/M = SYNCLK/N.

#### **State Transitions**

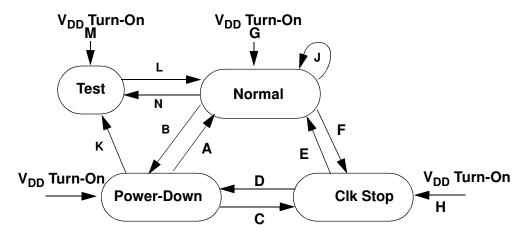

The clock source has three fundamental operating states. *Figure 4* shows the state diagram with each transition labelled A through H. Note that the clock source output may NOT be glitch-free during state transitions.

Upon powering up the device, the device can enter any state, depending on the settings of the control signals, PWR\_DWN# and STOP#.

In Power-Down mode, the clock source is powered down with the control signal, PWR\_DWN#, equal to 0. The control signals S0, S1 and S2 must be stable before power is applied to the device, and can only be changed in Power-Down mode (PWR\_DWN#=0). The reference inputs, VDDIR and VDDIPD, may remain on or may be grounded during the Power-Down mode.

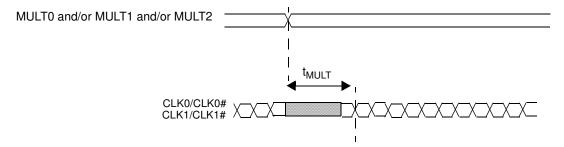

The control signals MULT0, MULT1, and MULT2 can be used in two ways. If they are changed during Power-Down mode, then the Power-Down transition timings determine the settling time of the DRCG. However, the MULT0, MULT1, and MULT2 control signals can also be changed during Normal mode. When the MULT control signals are "hot swapped" in this manner, the MULT transition timings determine the settling time of the DRCG.

Table 5. Frequencies, Dividers, and Gear Ratios

| Pclk | Refclk | Busclk | Synclk | Α | В | М | N | Ratio | F@PD |

|------|--------|--------|--------|---|---|---|---|-------|------|

| 67   | 33     | 267    | 67     | 8 | 1 | 2 | 2 | 1.0   | 33   |

| 100  | 50     | 300    | 75     | 6 | 1 | 8 | 6 | 1.33  | 12.5 |

| 100  | 50     | 400    | 100    | 8 | 1 | 4 | 4 | 1.0   | 25   |

| 133  | 67     | 267    | 67     | 4 | 1 | 4 | 2 | 2.0   | 33   |

| 133  | 67     | 400    | 100    | 6 | 1 | 8 | 6 | 1.33  | 16.7 |

Document #: 38-07232 Rev. \*B Page 5 of 14

Figure 4. Clock Source State Diagram.

In Clk Stop mode, the clock source is on, but the output is disabled (STOP# asserted). The VDDIPD reference input may remain on or may be grounded during the Clk Stop mode. The VDDIR reference input must remain on during the Clk Stop mode.

In Normal mode, the clock source is on, and the output is enabled.

Table 6 lists the control signals for each state.

Table 6. Control Signals for Clock Source States

| State      | PWR_DWN# | STOP# | Clock<br>Source | Output<br>Buffer |  |

|------------|----------|-------|-----------------|------------------|--|

| Power-Down | 0        | Х     | OFF             | Ground           |  |

| Clk Stop   | 1        | 0     | ON              | Disabled         |  |

| Normal     | 1        | 1     | ON              | Enabled          |  |

Figure 5 shows the timing diagrams for the various transitions between states, and Table 7 specifies the latencies of each state transition. Note that these transition latencies assume the following:

- REFCLK input has settled and meets specification shown in *Table 12*.

- MULT0, MULT1, MULT2, S0, S1, and S2 control signals are stable.

# **Timing Diagrams**

# PWR\_DWN# CLK0/CLK0# CLK1/CLK1# Output Enable Control STOP# output clock clock enabled not specified and glitch free glitches may occur. clock output settled within 50 ps of the phase before disabled

Figure 5. State Transition Timing Diagrams.

Figure 6. Multiply Transition Timing.

**Table 7. State Transition Latency Specifications**

| Transi- |                    |              | Transition Latency   |           |                                                                                                                   |

|---------|--------------------|--------------|----------------------|-----------|-------------------------------------------------------------------------------------------------------------------|

| tion    | From               | То           | Symbol               | Max.      | Description                                                                                                       |

| А       | Power-Down         | Normal       | t <sub>POWERUP</sub> | 3 ms      | Time from PWR_DWN# to rising edge CLK/CLK# output settled (excluding t <sub>DISTLOCK</sub> )                      |

| С       | Power-Down         | Clk Stop     | t <sub>POWERUP</sub> | 3 ms      | Time from PWR_DWN# rising edge until the internal PLL and clock has turned ON and settled.                        |

| К       | Power-Down         | Test         | t <sub>POWERUP</sub> | 3 ms      | Time from PWR_DWN# rising edge to CLK/CLK# output settled (excluding t <sub>DISTLOCK</sub> ).                     |

| G       | VDD ON             | Normal       | t <sub>POWERUP</sub> | 3 ms      | Time from VDD is applied and settled until CLK/CLK# output settled (excluding t <sub>DISTLOCK</sub> ).            |

| Н       | VDD ON             | Clk Stop     | t <sub>POWERUP</sub> | 3 ms      | Time from VDD is applied and settled until internal PLL and clock has turned ON and settled.                      |

| М       | VDD ON             | Test         | t <sub>POWERUP</sub> | 3 ms      | Time from VDD is applied and settled until internal PLL and clock has turned ON and settled.                      |

| J       | Normal             | Normal       | t <sub>MULT</sub>    | 1 ms      | Time from when MULT0, MULT1, or MULT2 changed until CLK/CLK# output resettled (excluding tolors).                 |

| E       | Clk Stop           | Normal       | t <sub>CLKON</sub>   | 10 ns     | Time from STOP# rising edge until CLK/CLK# provides glitch-free clock edges.                                      |

| E       | Clk Stop           | Normal       | <sup>†</sup> CLKSETL | 20 cycles | Time from STOP# rising edge to CLK/CLK# output settled to within 50 ps of the phase before CLK/CLK# was disabled. |

| F       | Normal             | Clk Stop     | t <sub>CLKOFF</sub>  | 5 ns      | Time from STOP# falling edge to CLK/CLK# output disabled.                                                         |

| L       | Test               | Normal       | <sup>t</sup> CTL     | 3 ms      | Time from when S0, S1, or S2 is changed until CLK/CLK# output has resettled (excluding tDISTLOCK).                |

| N       | Normal             | Test         | <sup>t</sup> CTL     | 3 ms      | Time from when S0, S1, or S2 is changed until CLK/CLK# output has resettled (excluding tDISTLOCK).                |

| B,D     | Normal or Clk Stop | PWR_DWN<br># | t <sub>POWERDN</sub> | 1 ms      | Time from PWR_DWN# falling edge to the device in PWR_DWN#.                                                        |

Figure 5 shows that the CLK Stop to Normal transition goes through three phases. During  $t_{\rm CLKON}$ , the clock output is not specified and can have glitches. For  $t_{\rm CLKON}$ <t< $t_{\rm CLKSETL}$ , the clock output is enabled and must be glitch-free. For t> $t_{\rm CLKSETL}$ , the clock output phase must be settled to within

50 ps of the phase before the clock output was disabled. At this time, the clock output must also meet the voltage and timing specifications of *Table 13*. The outputs are in a high-impedance state during the Clk Stop mode.

Table 8. Distributed Loop Lock Time Specification

| Symbol                | Min. | Max. | Unit | Description                                                                                                                                                |

|-----------------------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>DISTLOCK</sub> |      | 5    | ms   | Time from when CLK/CLK# output is settled to when the phase error between SYNCLKN and PCLKM falls within the t <sub>ERR,PD</sub> spec in <i>Table 13</i> . |

Document #: 38-07232 Rev. \*B Page 8 of 14

Table 9. Supply and Reference Current Specification

| Parameter              | Description                                                                         | Min. | Max. | Unit |

|------------------------|-------------------------------------------------------------------------------------|------|------|------|

| I <sub>POWERDOWN</sub> | "Supply" current in Power-Down state (PWR_DWN# = 0)                                 |      | 1.2  | mA   |

| I <sub>CLKSTOP</sub>   | "Supply" current in Clk Stop state (STOP# = 0)                                      |      | 175  | mA   |

| I <sub>NORMAL</sub>    | "Supply" current in Normal state<br>(STOP# = 1,PWR_DWN# = 1)                        |      | 225  | mA   |

| I <sub>REF,PWDN</sub>  | Current at VDDIR or VDDIPD reference pin in PWR_DWN# state (PWR_DWN# = 0)           |      | 50   | μΑ   |

| I <sub>REF,NORM</sub>  | Current at VDDIR or VDDIPD reference pin in Normal or Clk Stop state (PWR_DWN# = 1) |      | 4    | mA   |

Table 10 represents stress ratings only, and functional operation at the maximums is not guaranteed.

Table 10. Absolute Maximum Ratings

| Parameter            | Description                                    | Min. | Max.    | Unit |

|----------------------|------------------------------------------------|------|---------|------|

| VDD <sub>, ABS</sub> | Max. voltage on VDD with respect to ground     | -0.5 | 4.0     | V    |

| V <sub>I, ABS</sub>  | Max. voltage on any pin with respect to ground | -0.5 | VDD+0.5 | V    |

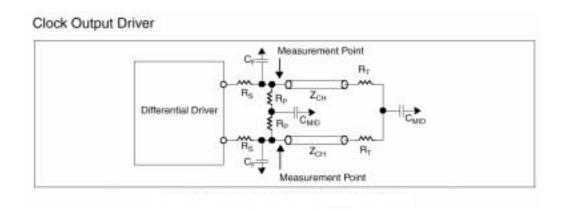

Table 11 gives the nominal values of the external components and their maximum acceptable tolerance, assuming  $Z_{CH}=28\Omega$ .

**Table 11. External Component Values**

| Parameter        | Description                | Test Load | Recommended<br>Value | Tolerance | Unit |

|------------------|----------------------------|-----------|----------------------|-----------|------|

| R <sub>S</sub>   | Serial Resistor            | 47        | 39                   | ±5%       | Ω    |

| R <sub>P</sub>   | Parallel Resistor          | 47        | 51                   | ±5%       | Ω    |

| C <sub>F</sub>   | Edge Rate Filter Capacitor | Note 1    | Note 1               | ±10%      | pF   |

| C <sub>MID</sub> | AC Ground Capacitor        | 100 pF    | 0.1                  | ±20%      | μF   |

#### Note:

#### **Clock Output Driver**

Figure 7. Example System Clock Driver Equivalent Circuit

Document #: 38-07232 Rev. \*B Page 9 of 14

<sup>1.</sup> Do not populate  $C_{F}$  Leave pads for future use.

## Table 12. Operating Conditions<sup>[2]</sup>

| Parameter                       | Description                                                                           | Min.  | Max.               | Unit                  |  |

|---------------------------------|---------------------------------------------------------------------------------------|-------|--------------------|-----------------------|--|

| $V_{DD}$                        | Supply Voltage                                                                        | 3.135 | 3.465              | V                     |  |

| T <sub>A</sub>                  | Ambient Operating Temperature                                                         | 0     | 70                 | °C                    |  |

| t <sub>CYCLE,IN</sub>           | Refclk Input Cycle Time                                                               | 10    | 40                 | ns                    |  |

| $t_{J,IN}$                      | Input Cycle-to-Cycle Jitter <sup>[3]</sup>                                            | _     | 250                | ps                    |  |

| DC <sub>IN</sub>                | Input Duty Cycle over 10,000 Cycles                                                   | 40    | 60                 | %t <sub>CYCLE</sub>   |  |

| FM <sub>IN</sub>                | Input Frequency of Modulation                                                         | 30    | 33                 | kHz                   |  |

| PM <sub>IN</sub> <sup>[4]</sup> | Modulation Index for Triangular Modulation                                            | _     | 0.6                | %                     |  |

|                                 | Modulation Index for Non-Triangular Modulation                                        | _     | 0.5 <sup>[5]</sup> | %                     |  |

| t <sub>CYCLE,PD</sub>           | Phase Detector Input Cycle Time at PCLKM & SYNCLKN                                    | 30    | 100                | ns                    |  |

| t <sub>ERR,INIT</sub>           | Initial Phase error at Phase Detector Inputs                                          | -0.5  | 0.5                | t <sub>CYCLE,PD</sub> |  |

| DC <sub>IN,PD</sub>             | Phase Detector Input Duty Cycle over 10,000 Cycles                                    | 25    | 75                 | t <sub>CYCLE,PD</sub> |  |

| t <sub>I,SR</sub>               | Input Slew Rate (measured at 20%-80% of input voltage) for PCLKM, SYNCLKN, and REFCLK | 1     | 4                  | V/ns                  |  |

| C <sub>IN,PD</sub>              | Input Capacitance at PCLKM, SYNCLKN, and REFCLK <sup>[6]</sup>                        | _     | 7                  | pF                    |  |

| $\Delta C_{IN,PD}$              | Input Capacitance matching at PCLKM and SYNCLKN <sup>[6]</sup>                        | _     | 0.5                | pF                    |  |

| C <sub>IN,CMOS</sub>            | Input Capacitance at CMOS pins (excluding PCLKM, SYNCLKN, and REFCLK) $^{[6]}$        | -     | 10                 | pF                    |  |

| V <sub>IL</sub>                 | Input (CMOS) Signal Low Voltage                                                       | _     | 0.3                | VDD                   |  |

| V <sub>IH</sub>                 | Input (CMOS) Signal High Voltage                                                      | 0.7   | -                  | VDD                   |  |

| $V_{IL,R}$                      | Refclk Input Low Voltage                                                              | -     | 0.3                | $V_{DDIR}$            |  |

| V <sub>IH,R</sub>               | Refclk Input High Voltage                                                             | 0.7   | _                  | $V_{DDIR}$            |  |

| $V_{\rm IL,PD}$                 | Input Signal Low Voltage for PD Inputs and STOP#                                      | _     | 0.3                | $V_{\mathrm{DDIPD}}$  |  |

| V <sub>IH,PD</sub>              | Input Signal High Voltage for PD Inputs and STOP#                                     | 0.7   | _                  | V <sub>DDIPD</sub>    |  |

| V <sub>DDIR</sub>               | Input Supply Reference for REFCLK                                                     | 1.235 | 3.465              | V                     |  |

| $V_{\rm DDIPD}$                 | Input Supply Reference for PD Inputs                                                  | 1.235 | 2.625              | V                     |  |

#### Notes:

Multiple Supplies: The voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required. Refclk jitter measured at V<sub>DDIR</sub> (nom)/2.

If input modulation is used: input modulation is allowed but not required.

The amount of allowed spreading for any non-triangular modulation is determined by the induced downstream tracking skew, which cannot exceed the skew generated by the specified 0.6% triangular modulation. Typically, the amount of allowed non-triangular modulation is about 0.5%.

Capacitance measured at Freq = 1 MHz, DC bias = 0.9V and V<sub>AC</sub> < 100 mV.

**Table 13. Device Characteristics**

| Parameter            | Description                                                                                | Min. | Max. | Unit                |

|----------------------|--------------------------------------------------------------------------------------------|------|------|---------------------|

| t <sub>CYCLE</sub>   | Clock Cycle Time                                                                           | 2.5  | 3.75 | ns                  |

| t <sub>J</sub>       | Cycle-to-Cycle Jitter at CLK/CLK# <sup>[7]</sup>                                           | -    | 60   | ps                  |

|                      | Total Jitter over 2, 3, or 4 Clock Cycles <sup>[7]</sup>                                   | -    | 75   | ps                  |

|                      | 266-MHz Cycle-to-Cycle Jitter <sup>[8]</sup>                                               | -    | 60   | ps                  |

|                      | 266-MHz Total Jitter over 2, 3, or 4 Clock Cycles <sup>[8]</sup>                           | -    | 75   | ps                  |

| $V_{X,STOP}$         | Output Voltage during Clk Stop (STOP#=0)                                                   | 1.1  | 2.0  | V                   |

| V <sub>X</sub>       | Differential Output Crossing-Point Voltage                                                 | 1.3  | 1.8  | V                   |

| V <sub>COS</sub>     | Output Voltage Swing (p-p single-ended) <sup>[9]</sup>                                     | 1.1  | 1.5  | V                   |

| V <sub>OH</sub>      | Output High Voltage                                                                        | -    | 2.5  | V                   |

| V <sub>OL</sub>      | Output Low voltage                                                                         | 0.6  | -    | V                   |

| I <sub>OZ,STOP</sub> | Output Current during Clk Stop (STOP# = 0)                                                 | -    | 500  | μΑ                  |

| DC                   | Output Duty Cycle over 10,000 Cycles                                                       | 40   | 60   | %t <sub>CYCLE</sub> |

| t <sub>DC,ERR</sub>  | Output Cycle-to-Cycle Duty Cycle Error                                                     | -    | 50   | ps                  |

| $t_{R,t_F}$          | Output Rise and Fall Times (measured at 20%–80% of output voltage)                         | 300  | 550  | ps                  |

| t <sub>CR,CF</sub>   | Difference between Output Rise and Fall Times on the Same Pin of a Single Device (20%–80%) | -    | 100  | ps                  |

- Output Jitter spec measured at t<sub>CYCLE</sub> = 2.5 ns.

Output Jitter Spec measured at t<sub>CYCLE</sub> = 3.75 ns.

V<sub>COS</sub> = V<sub>OH</sub>-V<sub>OL</sub>.

# **Ordering Information**

| Ordering Code | Package<br>Name | Package Type            |

|---------------|-----------------|-------------------------|

| W234          | Х               | 28-pin TSSOP (173 mils) |

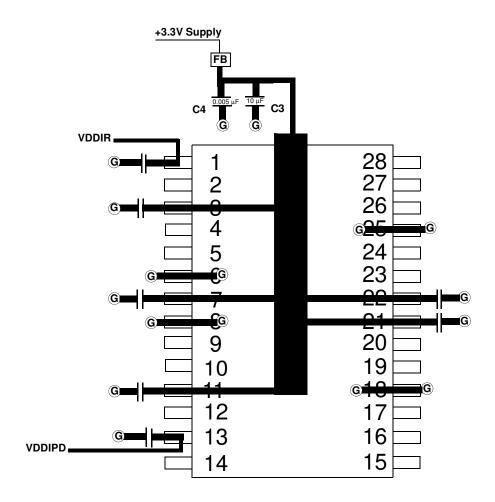

# **Layout Example**

#### **Internal Power Supply Plane**

FB = Dale ILB1206 - 300 (300 $\Omega$  @ 100 MHz) © = VIA to GND plane layer All Bypass cap = 0.1 Ceramic XR7

# **Package Diagram**

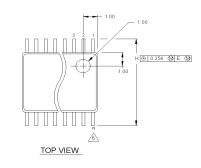

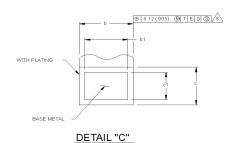

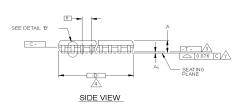

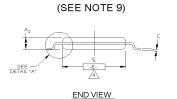

### 28-Pin Thin Small Shrink Outline Package (TSSOP, 173 mils)

- 1. DIE THICKNESS ALLOWABLE IS 0.279±0.0127 (.0110±.0005 INCHES)

2. DIMENSIONING & TOLERANCES PER ANSI.Y14.5M-1982.

1. T'' IS A REFERENCE DATUM.

- 1 TO A REFERENCE DATUMS AND DO NOT INCLIDE MOLD FLASH OR PROTRISIONS, AND ARE INCLIDE MOLD FLASH OR PROTRISIONS, AND ARE REASURED AT THE PARTING LINE, MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 155mm PER SIDE. DIMENSION IS THE LENGTH OF TERMINAL, POST INCLIDENCE AS SUBSTRATE.

FOR SOLDERING TO A SUBSTRATE.

#### THIS TABLE IN MILLIMETERS

| S              | COMMON           |          |                    |                | NOTE   | 4    |      |      | 6  |

|----------------|------------------|----------|--------------------|----------------|--------|------|------|------|----|

| M<br>B         | DIMENSIONS       |          | N <sub>O</sub> T E | VARI-          |        | D    |      | N    |    |

| 2              | MIN.             | NOM.     | MAX.               | T <sub>E</sub> | ATIONS | MIN. | NOM. | MAX. |    |

| Α              |                  |          | 1.10               |                | AA     | 2.90 | 3.00 | 3.10 | 8  |

| A <sub>1</sub> | 0.05             | 0.10     | 0.15               |                | AB     | 4.90 | 5.00 | 5.10 | 14 |

| A2             | 0.85             | 0.90     | 0.95               |                | AC     | 4.90 | 5.00 | 5.10 | 16 |

| b              | 0.19             | -        | 0.30               | 8              | AD     | 6.40 | 6.50 | 6.60 | 20 |

| b1             | 0.19             | 0.22     | 0.25               |                | AE     | 7.70 | 7.80 | 7.90 | 24 |

| С              | 0.090            | -        | 0.20               |                | AF     | 9.60 | 9.70 | 9.80 | 28 |

| c1             | 0.090            | 0.127    | 0.135              |                |        |      |      |      |    |

| D              | D SEE VARIATIONS |          | 4                  |                |        |      |      |      |    |

| E              | 4.30             | 4.40     | 4.50               | 4              |        |      |      |      |    |

| е              |                  | 0.65 BSC |                    |                |        |      |      |      |    |

| H              | 6.25             | 6.40     | 6.50               |                |        |      |      |      |    |

| L              | 0.50             | 0.60     | 0.70               | 5              |        |      |      |      |    |

| Ŋ              | N SEE VARIATIONS |          |                    | 6              |        |      |      |      |    |

| œ              | 0°               | 4°       | 8°                 |                |        |      |      |      |    |

#### THIS TABLE IN INCHES

|                |                  |            |       |                |        |      |      |      | _  |

|----------------|------------------|------------|-------|----------------|--------|------|------|------|----|

| S              | COMMON           |            |       |                | NOTE   | 4    |      |      | 6  |

| M<br>B         | DI               | DIMENSIONS |       | N <sub>O</sub> | VARI-  |      | D    |      | N  |

| 1 %            | MIN.             | NOM.       | MAX.  | T <sub>E</sub> | ATIONS | MIN. | NOM. | MAX. |    |

| Α              |                  |            | .0433 |                | AA     | .114 | .118 | .122 | 8  |

| A <sub>1</sub> | .002             | .004       | .006  |                | AB     | .193 | .197 | .201 | 14 |

| A2             | .0335            | .0354      | .0374 |                | AC     | .193 | .197 | .201 | 16 |

| b              | .0075            | -          | .0118 | 8              | AD     | .252 | .256 | .260 | 20 |

| b1             | .0075            | .0087      | .0098 |                | AE     | .303 | .307 | .311 | 24 |

| С              | .0035            | -          | .0079 |                | AF     | .378 | .382 | .386 | 28 |

| c1             | .0035            | .0050      | .0053 |                |        |      |      |      |    |

| D              | SEE              | VARIATION  | IS    | 4              |        |      |      |      |    |

| E              | .169             | .173       | .177  | 4              |        |      |      |      |    |

| е              |                  | .0256 BSC  |       |                |        |      |      |      |    |

| Н              | .246             | .252       | .256  |                |        |      |      |      |    |

| L              | .020             | .024       | .028  | 5              |        |      |      |      |    |

| Ŋ              | N SEE VARIATIONS |            |       | 6              |        |      |      |      |    |

| œ              | 0°               | 4°         | 8°    |                |        |      |      |      |    |

\*VARIATION AF IS DESIGNED BUT NOT TOOLED\*

| Document Title: W234 Dual Direct Rambus™ Clock Generator<br>Document Number: 38-07232 |         |               |                 |                                                               |  |  |  |  |

|---------------------------------------------------------------------------------------|---------|---------------|-----------------|---------------------------------------------------------------|--|--|--|--|

| REV.                                                                                  | ECN NO. | Issue<br>Date | Orig. of Change | Description of Change                                         |  |  |  |  |

| **                                                                                    | 110497  | 10/21/01      | SZV             | Change from Spec number: 38-00921 to 38-07232                 |  |  |  |  |

| *A                                                                                    | 111647  | 02/07/02      | IKA             | Changed Table 11, added Clock Output diagram, page 8          |  |  |  |  |

| *B                                                                                    | 122846  | 12/21/02      | RBI             | Add Power up Requirements to Operating Conditions Information |  |  |  |  |