# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# High-Performance Internet Connectivity Solution

# W5300

Version 1.2.5

© 2008 WIZnet Co., Inc. All Rights Reserved. For more information, visit our website at <u>http://www.wiznet.co.kr</u>

# WIZnet

# **Document History Information**

| Version    | Date          | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ver. 1.0.0 | Mar. 11, 2008 | Release with W5300 launching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Ver. 1.1.0 | May. 15, 2008 | <ul> <li>Correct a number of typing errors</li> <li>4.4 SOCKET Register &gt;&gt; Sn_DPORTR<br/>R/W → WO, Modify the description, Refer to P.77</li> <li>4.4 SOCKET Register &gt;&gt; Sn_MSSR<br/>In the MSS Table, Modified the PPPoE MSS value of<br/>MACRAW(1502 → 1514), Refer to P.79</li> <li>5.2.1.1 TCP SERVER &gt;&gt; • ESTABLISHED : Receiving<br/>process<br/>At the <notice> phase, Modified the example code<br/>Replace 'SEND' with 'SEND_KEEP'. Refer to P.93~94</notice></li> <li>5.2.4 MACRAW &gt;&gt; • Receiving process<br/>At the <notice> phase, Modified the free size and CRC<br/>Free size 1526 → 1528, CRC(2) → CRC(4), Refer to P.111</notice></li> </ul> |  |  |

| Ver. 1.1.1 | July 4, 2008  | <ul> <li>Correct a number of typing errors</li> <li>Add PIN "BRDYn" description to "1.3 Host Interface signal"</li> <li>5.2.1.1 TCP SERVER &gt;&gt; • ESTABLISHED : Receiving process</li> <li>At the <notice> phase, Modified the example code Replace 'SEND_KEEP' with 'SEND'. Refer to P.93~94</notice></li> </ul>                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Ver 1.2    | Dec. 30, 2008 | <ul> <li>1. PIN Description<br/>Add to '8' Symbol</li> <li>1.2 Configuration Signals<br/>Modify ADDR type (ID → I), No Internal Pulled-down<br/>Modify DATA[15:0] type (IO → IO8)</li> <li>6.2. Indirect Address Mode<br/>ADDR[9:0] has no internal pulled-down resister. So,<br/>ADDR[9:3] should be connected to ground for using indirect<br/>address mode.</li> </ul>                                                                                                                                                                                                                                                                                                            |  |  |

|           |               | Modify the description & figures.                             |

|-----------|---------------|---------------------------------------------------------------|

| Ver 1.2.1 | Jan. 22, 2009 | <ul> <li>Modify the Figure 2.</li> </ul>                      |

|           |               | Ferrite Bead 0.1uF → 1uH                                      |

| Ver 1.2.2 | Feb. 16, 2009 | <ul> <li>1.7 Clock Signals.</li> </ul>                        |

|           |               | Delete XTLP/XTLN Pin Type                                     |

|           |               | <ul> <li>7. Electrical Specifications</li> </ul>              |

|           |               | - DC Characteristics                                          |

|           |               | : Modify the Test Condition of $V_{\text{OH}}, V_{\text{OL}}$ |

|           |               | : $V_{OH}$ - Min (2.0(2.4), Delete Typical and Max value      |

|           |               | : $V_{OL}$ – Delete Min and Typical value                     |

| V1.2.3    | Feb.11, 2010  | ∘ Change Figure 2                                             |

|           |               | - Change W5300 Power Supply Signal schemati                   |

| V1.2.4    | Aug. 19, 2010 | - Change Temperature condition (p.119)                        |

| V1.2.5    | Sep. 29, 2010 | - Modify Table 1.8 Power Supply Signal (p.19)                 |

|           |               | 1V8O: 1.8V regulator output voltage                           |

|           |               | Capacitor value: 0.1uF -> 10Uf                                |

|           |               | - Modified Fig.2 Power Design (p.21)                          |

# WIZnet's online Technical Support

If you have something to ask about WIZnet Products, write down your question on <u>Q&A Board</u> of 'Support' menu in WIZnet website (<u>www.wiznet.co.kr</u>). WIZnet Engineer will give an answer as soon as possible.

# W5300

W5300 is a 0.18 µm CMOS technology single chip into which 10/100 Ethernet controller, MAC, and TCP/IP are integrated. W5300 is designed for Internet embedded applications where easy implementation, stability, high performance, and effective cost are required.

W5300's target application is the embedded internet solution requiring high performance such as multi-media streaming service. Comparing to existing WIZnet chip solution, W5300 has been improved in memory and data process. W5300 is the most appropriate to the products of IPTV, IP-STB and DTV transferring multi-media data with high-capacity.

The Internet connectivity can be implemented easily and quickly only with single chip having TCP/IP protocol and 10/100 Ethernet MAC & PHY.

#### High-Performance Hardware TCP/IP single chip solutions

WIZnet retains the technology of full hardware logic of communication protocols such as TCP, UDP, IPv4, ICMP, IGMP, ARP and PPPoE. In order to provide high-performing data communication, the data communication memory is extended to 128Kbyte and 16bit bus interface is supported in W5300. Users can utilize independent 8 hardware SOCKETs for high-speed data communication.

#### More flexible memory allocation for various applications

The memory for data communication can be allocated to each SOCKET in the range of 0~64Kbytes. It is more flexible for users to utilize the memory according to their application. Users can develop more efficient system by concentrating on the application of high performance.

#### Easy to implements for beginners

W5300 supports BUS interface as the host interface. By using direct and indirect access methods, W5300 can easily interfaced to the host as like SRAM memory. The data communication memory of W5300 can be accessed through TX/RX FIFO registers that exist in each SOCKET. With these features, even beginners can implement Internet connectivity by using W5300.

# **Target Applications**

The W5300 is well-suited for many embedded applications, including:

- Home Network Devices: Set-Top Boxes, PVRs, Digital Media Adapters

- Serial-to-Ethernet: Access Controls, LED displays, etc.

- Parallel-to-Ethernet: POS / Mini Printers, Copiers

- USB-to-Ethernet: Storage Devices, Network Printers

- GPIO-to-Ethernet: Home Network Sensors

- Security Systems: DVRs, Network Cameras, Kiosks

- Factory and Building Automation

- Medical Monitoring Equipment

- Embedded Servers

### Features

- Supports hardwired TCP/IP protocols : TCP,UDP,ICMP,IPv4,ARP,IGMPv2,PPPoE,Ethernet

- Supports 8 independent SOCKETs simultaneously

- High network performance : Up to 50Mbps

- Supports hybrid TCP/IP stack(software and hardware TCP/IP stack)

- Supports PPPoE connection (with PAP/CHAP Authentication mode)

- IP Fragmentation is not supported

- Internal 128Kbytes memory for data communication(Internal TX/RX memory)

- More flexible allocation internal TX/RX memory according to application throughput

- Supports memory-to-memory DMA (only 16bit Data bus width & slave mode)

- Embedded 10BaseT/100BaseTX Ethernet PHY

- Supports auto negotiation (Full-duplex and half duplex)

- Supports auto MDI/MDIX(Crossover)

- Supports network Indicator LEDs (TX, RX, Full/Half duplex, Collision, Link, Speed)

- Supports a external PHY instead of the internal PHY

- Supports 16/8 bit data bus width

- Supports 2 host interface mode(Direct address mode & Indirect address mode)

- External 25MHz operation frequency (For internal PLL logic, period=40ns)

- Internal 150MHz core operation frequency (PLL\_CLK, period=about 6.67ns)

- Network operation frequency (NIC\_CLK : 25MHz(100BaseTX) or 2.5MHz(10BaseT))

- 3.3V operation with 5V I/O signal tolerance

- Embedded power regulator for 1.8V core operation

- 0.18 µm CMOS technology

- 100LQFP 14X14 Lead-Free Package

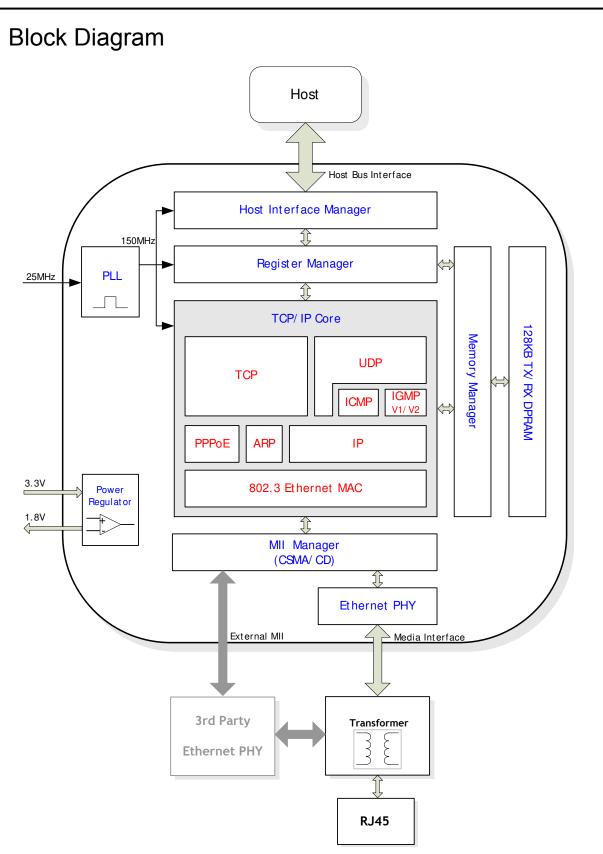

#### PLL(Phase-Locked Loop)

It creates a 150MHz clock signal by multiplying 25MHz clock source by six. The 150MHz clock is used for operating internal blocks such as TCP/IP core block, 'Host Interface Manager' and 'Register Manager'. PLL is locked-in after reset and it supplies a stable clock.

#### **Power Regulator**

With 3.3V power input, the power regulator creates 1.8V/150mA power. This power regulator supplies the power for core operation of W5300. It is not required to add other power regulators, but recommended to add a capacitor for more stable 1.8V power supplying.

#### Host Interface Manager

It detects host bus signal, and manages read/write operations of the host according to data bus width or host interface mode.

#### **Register Manager**

It manages Mode register, COMMON Register, and SOCKET Register.

#### Memory Manager

It manages internal data memory of 128KBytes – TX/RX memory allocated in each SOCKET by the host. The host can access the memory only through TX/RX FIFO Register of each SOCKET.

#### 128KB TX/RX DPRAM

It is the 128KByte memory for data communication and composed of 16 DPRAM(Dual-Port RAM) of 8KBytes. It is allocated flexibly to each SOCKET by the host.

#### MII(Media Independent Interface) Manager

It manages MII interface. MII interface can be switched to internal PHY or external PHY(3<sup>rd</sup> party PHY) according to the configuration of TEST\_MODE[3:0].

#### Internal Ethernet PHY

W5300 includes 10BaseT/100BaseTX Ethernet PHY. Internal PHY supports half-duplex/full duplex, auto-negotiation and auto MDI/MDIX. It also supports 6 network indicator LED output such as Link status, speed and duplex.

#### TCP/IP Core

TCP/IP Core is the fully hardwired logic based on network protocol processing technology of WIZnet.

#### - 802.3 Ethernet MAC(Media Access Control)

It controls Ethernet access of CSMA/CD(<u>Carrier Sense Multiple Access with Collision</u> <u>Detect</u>). It is the protocol technology based on a 48-bit source/destination MAC address. It also allows the host to control MAC layer through its 0<sup>th</sup> SOCKET. So, it is possible to implement software TCP/IP stack together with hardware TCP/IP stack.

#### PPPoE(Point-To-Point Protocol over Ethernet)

It is the protocol technology to use PPP service at the Ethernet. It encapsulates the payload(data) part of Ethernet frame as the PPP frame and transmits it. When receiving, it de-capsulates the PPP frame. PPPoE supports PPP communication with PPPoE server and PAP/CHAP authentication methods.

#### ARP(Address Resolution Protocol)

ARP is the MAC address resolution protocol by using IP address. It transmits the ARPreply to the ARP-request from the peer. It also sends ARP-request to find the MAC address of the peer and processes the ARP-reply to the request.

#### IP(Internet Protocol)

IP is the protocol technology to support data communication at the IP layer. IP fragmentation is not supported. It is not possible to receive the fragmented packets. Except for TCP or UDP, all protocol number is supported. In case of TCP or UDP, use the hardwired stack.

#### ICMP(Internet Control Message Protocol)

It receives the ICMP packets such as the fragment MTU, unreachable destination, and notifies the host. After receiving Ping-request ICMP packet, it transmits Ping-reply ICMP packet. It supports maximum 119 Byte as Ping-request size. If the size is over 119Bytes, it is not supported.

#### IGMPv1/v2(Internet Group Management Protocol version 1/2)

It processes IGMP such as IGMP Join/Leave, Report at the UDP multicasting mode. Only version 1 and 2 of IGMP logic is supported. When using upper version of IGMP, it should be manually implemented by using IP layer.

#### UDP(User Datagram Protocol)

It is the protocol technology to support data communication at the UDP layer. It supports user datagram such as unicast, multicast, and broadcast.

#### - TCP(Transmission Control Protocol)

It is the protocol technology to support data communication at the TCP layer. It supports "TCP SERVER" and "TCP CLIENT" communication.

W5300 internally processes all protocol communication without intervention of the host. W5300 is based on TOE(<u>TCP/IP Offload Engine</u>) that can maximize the host performance by reducing the host overhead in processing TCP/IP stack.

# Table of Contents

| 1. PIN Description                        | 12  |

|-------------------------------------------|-----|

| 1.1 PIN Layout                            | 12  |

| 1.2 Configuration Signals                 | 13  |

| 1.3 Host Interface Signals                | 14  |

| 1.4 Media Interface Signals               | 16  |

| 1.5 MII interface signal for external PHY | 17  |

| 1.6 Network Indicator LED Signals         | 19  |

| 1.7 Clock Signals                         | 19  |

| 1.8 Power Supply Signals                  | 20  |

| 2. System Memory Map                      | 22  |

| 3. W5300 Registers                        | 24  |

| 3.1 Mode Register                         | 25  |

| 3.2 Indirect Mode Registers               | 25  |

| 3.3 COMMON registers                      | 25  |

| 3.4 SOCKET registers                      | 29  |

| 4. Register Description                   | 45  |

| 4.1 Mode Register                         |     |

| 4.2 Indirect Mode Registers               | 49  |

| 4.3 COMMON Registers                      | 50  |

| 4.4 SOCKET Registers                      | 66  |

| 5. Functional Description                 | 88  |

| 5.1 Initialization                        | 88  |

| 5.2 Data Communication                    |     |

| 5.2.1 TCP                                 |     |

| 5.2.2 UDP                                 | 100 |

| 5.2.3 IPRAW                               | 107 |

| 5.2.4 MACRAW                              | 109 |

| 6. External Interface                     | 115 |

| 6.1 Direct Address Mode                   | 115 |

| 6.1.1 16 Bit Data Bus Width               | 115 |

| 6.1.2 8 Bit Data Bus Width                | 115 |

| 6.2 Indirect Address Mode                 | 116 |

| 6.2.1 16 Bit Data Bus Width               | 116 |

| 6.2.2 8 Bit Data Bus Width                | 116 |

| 6.3 Internal PHY Mode                        | 117 |

|----------------------------------------------|-----|

| 6.4 External PHY Mode                        | 118 |

| 7. Electrical Specifications                 | 119 |

| 8. IR Reflow Temperature Profile (Lead-Free) |     |

| 9. Package Descriptions                      |     |

# List of Figures

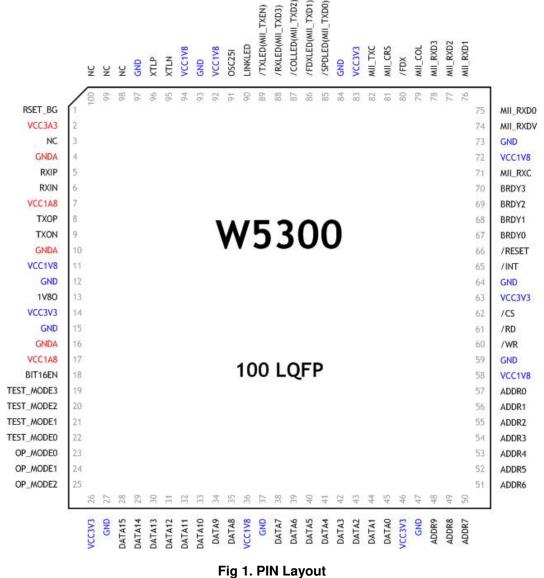

| Fig 1. PIN Layout                                  | 12  |

|----------------------------------------------------|-----|

| Fig 2. Power Design                                | 21  |

| Fig 3. Memory Map                                  |     |

| Fig 4. 'BRDYn' Timing                              | 65  |

| Fig 5. SOCKETn Status Transition                   | 77  |

| Fig 6. Access to Internal TX Memory                |     |

| Fig 7. Access to Internal RX Memory                |     |

| Fig 8. Allocation Internal TX/RX memory of SOCKETn |     |

| Fig 9. "TCP SERVER" & "TCP CLIENT"                 |     |

| Fig 10. "TCP SERVER" Operation Flow                | 91  |

| Fig 11. The received TCP data format               |     |

| Fig 12. "TCP CLIENT" Operation Flow                |     |

| Fig 13. UDP Operation Flow                         | 100 |

| Fig 14. The received UDP data format               | 101 |

| Fig 15. IPRAW Operation Flow                       | 107 |

| Fig 16. The received IPRAW data format             | 108 |

| Fig 17. MACRAW Operation Flow                      | 109 |

| Fig 18. The received MACRAW data format            | 110 |

| Fig 19. Internal PHY & LED Signals                 | 117 |

|                                                    |     |

## 1. PIN Description

| Тур<br>е | Description                                  | Туре | Description                                    |

|----------|----------------------------------------------|------|------------------------------------------------|

| I        | Input                                        | D    | Internal pulled-down with $75K\Omega$ resistor |

| 0        | Output with driving current 2mA              | М    | Multi-function                                 |

| 10       | Input/Output (Bidirectional)                 | Н    | Active high                                    |

| U        | Internal pulled-up with $75K\Omega$ resistor | L    | Active low                                     |

| O8       | Output with driving current 8mA              |      |                                                |

<Notation> IUL : Input PIN with 75K $\Omega$  pull-up resistor. Active low

OM : Multi-functional Output PIN

1.1 PIN Layout

| 1.2 Configuration Signals |      |                                                                                                                                             |      |       |             |      |                                                                                   |

|---------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------|------|-----------------------------------------------------------------------------------|

| Symbol                    | Туре | Description                                                                                                                                 |      |       |             |      |                                                                                   |

| TEST_MODE[3:0]            | ID   | W5300 mode select<br>It configures PHY mode and factory test mode of W5300.                                                                 |      |       |             |      |                                                                                   |

|                           |      | TEST_MODE Description                                                                                                                       |      |       |             |      |                                                                                   |

|                           |      | 3                                                                                                                                           | 2    | 2     | 1           | 0    |                                                                                   |

|                           |      | 0                                                                                                                                           | C    | )     | 0           | 0    | Internal PHY Mode (Normal Operation)                                              |

|                           |      | 0                                                                                                                                           | C    |       | 0           | 1    | External PHY Mode with Crystal clock                                              |

|                           |      | 0                                                                                                                                           | C    | )     | 1           | 0    | External PHY Mode with Oscillator clock                                           |

|                           |      |                                                                                                                                             | (    | Other | S           |      | Reserved (Factory Test Mode)                                                      |

| OP_MODE[2:0]              | ID   | source. Refer to "1.7 Clock Signals".         Internal PHY operation control mode         It configures the operation mode of internal PHY. |      |       |             |      |                                                                                   |

|                           |      | OP_MODE Description                                                                                                                         |      |       | Description |      |                                                                                   |

|                           |      |                                                                                                                                             | 0    | 0     | 0           |      | ormal Operation Mode, Recommended<br>uto-negotiation enable with all capabilities |

|                           |      |                                                                                                                                             | 0    | 0     | 1           | Aı   | uto-negotiation with 100 BASE-TX FDX/HDX ability                                  |

|                           |      |                                                                                                                                             | 0    | 1     | 0           | A    | uto-negotiation with 10 BASE-T FDX/HDX ability                                    |

|                           |      |                                                                                                                                             | 0    | 1     | 1           | R    | eserved                                                                           |

|                           |      |                                                                                                                                             | 1    | 0     | 0           | М    | anual selection of 100 BASE-TX FDX                                                |

|                           |      |                                                                                                                                             | 1    | 0     | 1           | М    | anual selection of 100 BASE-TX HDX                                                |

|                           |      |                                                                                                                                             | 1    | 1     | 0           | М    | anual selection of 10 BASE-T FDX                                                  |

|                           |      |                                                                                                                                             | 1    | 1     | 1           | M    | anual selection of 10 BASE-T HDX                                                  |

|                           |      | cf> FDX : Full-duplex, HDX : Half-duplex                                                                                                    |      |       |             |      |                                                                                   |

|                           |      | The                                                                                                                                         | sett | ing \ | alue        | e is | latched after hardware reset.                                                     |

|            |      | face Signals                                                                    |

|------------|------|---------------------------------------------------------------------------------|

| Symbol     | Туре | Description                                                                     |

| /RESET     | IL   | RESET                                                                           |

|            |      | Hardware Reset Signal.                                                          |

|            |      | It initializes W5300. RESET should be held at least 2us after low assert,       |

|            |      | and wait for at least 10ms after high de-assert in order for PLL logic to       |

|            |      | be stable.                                                                      |

|            |      | Refer to RESET timing of "7 Electrical Specification"                           |

|            |      | W5300 does not support Power-On-Reset. Therefore, it should be                  |

|            |      | manually designed in the target system.                                         |

| BIT16EN    | IU   | 16/8 BIT DATA BUS SELECT                                                        |

|            |      | High : 16 bit data bus                                                          |

|            |      | Low : 8 bit data bus                                                            |

|            |      | It determinates data bus width of W5300.                                        |

|            |      | At reset time, it is latched in 15 <sup>th</sup> Bit('BW')of Mode register(MR). |

|            |      | After reset, its change is ignored. It means data bus width can't be            |

|            |      | changed after reset. When using 8 bit data bus, it should be connected          |

|            |      | to ground.                                                                      |

| ADDR9-0    | I    | ADDRESS                                                                         |

|            |      | System address bus.                                                             |

|            |      | These are selected by host interface mode and data bus width of                 |

|            |      | W5300. When using 16 bit data bus, ADDR0 is internally ignored.                 |

|            |      | Refer to "6.External Interface".                                                |

| DATA[15:8] | IO   | DATA                                                                            |

| r1         |      | System high data bus.                                                           |

|            |      |                                                                                 |

|            |      | These are used for read/write operation of W5300 register.                      |

|            |      | In case of using 8 bit data bus, These are driven as High-Z.                    |

| DATA[7:0]  | IO8  | DATA                                                                            |

|            |      | System low data bus.                                                            |

|            |      | These are used for read/write operation of W5300 register.                      |

| /CS        | IL   | CHIP SELECT                                                                     |

|            |      | Chip select signal.                                                             |

|           |    | Host selects W5300 at the W5300 read/write operation.                     |

|-----------|----|---------------------------------------------------------------------------|

|           |    | When /CS is de-asserted high, DATA[15:0] are driven as High-Z.            |

| /WR       | IL | WRITE ENABLE                                                              |

|           |    | Write enable signal.                                                      |

|           |    |                                                                           |

|           |    | Host writes W5300 register addressed by ADDR[9:0] to DATA[15:0].          |

|           |    | DATA[15:0] are latched in the W5300 register according to the             |

|           |    | configuration of the Write-data-fetch-timing.                             |

|           |    | Refer to 13-11 <sup>th</sup> bit(WDF[2:0] of MR).                         |

| /RD       | IL | READ ENABLE                                                               |

|           |    | Read enable signal.                                                       |

|           |    |                                                                           |

|           |    | Host reads W5300 register addressed by ADDR[9:0] through                  |

|           |    | DATA[15:0].                                                               |

| /INT      | OL | INTERRUPT                                                                 |

|           |    | Interrupt Request Signal.                                                 |

|           |    |                                                                           |

|           |    | It is asserted low when interrupt(connected, disconnected, data           |

|           |    | received, data sent or timeout) occurs on operating.                      |

|           |    | When interrupt service is completed by host and Interrupt register(IR) is |

|           |    | cleared by host, it is de-asserted high.                                  |

|           |    | Refer to IR, Interrupt Mask Register(IMR), SOCKETn Interrupt              |

|           |    | Register(Sn_IR), SOCKETn Interrupt Mask Register(Sn_IMR).                 |

| BRDY[3:0] | 0  | Buffer Ready Indicator                                                    |

|           |    |                                                                           |

|           |    | These PIN are configured with SOCKET number, memory Type, and             |

|           |    | buffer depth by user. When TX free or RX received size of the specified   |

|           |    | SOCKET is same or greater than the configured buffer depth, these PIN     |

|           |    | signals asserts high or low.                                              |

|           |    | Refer to Pn_BRDYR & Pn_DPTHR in "4.3 COMMON Registers".                   |

### 1.4 Media Interface Signals

Media(10Mbps/100Mbps) interface signals are used in internal PHY mode (TEST\_Mode[3:0] = "0000"). Refer to "1.2 Configuration Signals".

| Symbol  | Туре | Description                                                              |

|---------|------|--------------------------------------------------------------------------|

| RXIP    | I    | RXIP/RXIN Signal Pair                                                    |

|         |      | Differential receive Input signal pair.                                  |

|         |      |                                                                          |

| RXIN    | I    | Receive data from the media. This signal pair needs 2 termination        |

|         |      | resistors $50\Omega(\pm 1\%)$ and 1 capacitor 0.1uF for better impedance |

|         |      | matching, and this resistor/capacitor pair is located near               |

|         |      | magnetic(transformer). If not used, connect to ground.                   |

| TXOP    | 0    | TXOP/TXON Signal Pair                                                    |

|         |      | Differential transmit output signal pair.                                |

|         |      |                                                                          |

|         |      | Transmits data to the media. This signal pair needs 2 termination        |

| TXON    | 0    | resistors $50\Omega(\pm 1\%)$ and 1 capacitor 0.1uF for better impedance |

|         |      | matching, and this resistor/capacitor pair should be located near        |

|         |      | W5300. If not used, just let them float.                                 |

| RSET_BG | 0    | Off-chip Resistor                                                        |

|         |      |                                                                          |

|         |      | This pin should be pulled-down with 12.3 $k\Omega \pm 1\%$ resistor.     |

For the better performance,

- 1. Make the length of RXIP/RXIN signal pair (RX) same if possible.

- 2. Make the length of TXOP/TXON signal pail (TX) same if possible.

- 3. Locate the RXIP and RXIN signal as near as possible.

- 4. Locate the TXOP and TXON signal as near as possible.

- 5. Locate the RX and TX signal pairs far from noisy signals such as bias resistor or crystal.

For the detailed information refer to "W5100 Layout Guide.pdf"

### 1.5 MII interface signal for external PHY

MII interface signals are for interfacing to external PHY instead of the internal PHY of W5300. These signals can be used at the external PHY mode (TEST\_Mode[3:0] = "0001" or "0010"). Refer to "1.2 Configuration Signals".

At the internal PHY mode, just let them float because the pins except for multi-function pins are internal pulled-down.

| Symbol                     | Туре | Description                                                                                                       |

|----------------------------|------|-------------------------------------------------------------------------------------------------------------------|

| /TXLED(MII_TXEN)           | ОМН  | Transmit Act LED / Transmit Enable                                                                                |

|                            |      |                                                                                                                   |

|                            |      | This signal indicates the presence of transmit packet on the                                                      |

|                            |      | MII_TXD[3:0]. It is asserted high when the first nibble data of                                                   |

|                            |      | transmit packet is valid on MII_TXD[3:0] and is de-asserted low                                                   |

|                            |      | after the last nibble data of transmit packet is clocked out on                                                   |

|                            |      | MII_TXD[3:0].                                                                                                     |

| /RXLED( <b>MII_TXD3</b> )  | OM   | /RXLED,/COLLED,/LEDFDX,/SPDLED / Transmit data output                                                             |

| /COLLED(MII_TXD2)          |      |                                                                                                                   |

| /FDXLED( <b>MII_TXD1</b> ) |      | The transmit packet is synchronized with MII_TXC clock and                                                        |

| /SPDLED( <b>MII TXD0</b> ) |      | output to external PHY in nibble unit.                                                                            |

|                            |      | MII_TXD3 is the Most Significant Bit (MSB).                                                                       |

| MII_TXC                    | ID   | Transmit Clock Input                                                                                              |

|                            |      |                                                                                                                   |

|                            |      | It is a continuous transmit clock from the external PHY. It is 25MHz at the 100BaseTX and 2.5MHz at the 10 BaseT. |

|                            |      | Transmit clock is used as timing reference of MII_TXD[3:0] and                                                    |

|                            |      | used for network operation clock (NIC_CLK).                                                                       |

|                            |      | Rising Edge Sensitive.                                                                                            |

| MII_CRS                    | IDH  | Carrier Sense                                                                                                     |

|                            |      |                                                                                                                   |

|                            |      | It is signal to notify the link traffic of the media. If carrier of                                               |

|                            |      | media is not idle (carrier present), it is asserted high.                                                         |

| MII_COL                    | IDH  | Collision Detect                                                                                                  |

| —                          |      |                                                                                                                   |

|                            |      | When collision is detected on the media, it is asserted high.                                                     |

|                            |      | It is valid at the half-duplex and ignored at the full-duplex.                                                    |

|                            |      | Asynchronous signal.                                                                                              |

| MII_RXD3 | ID  | Receive Data Input                                                 |

|----------|-----|--------------------------------------------------------------------|

| MII_RXD2 |     |                                                                    |

| MII_RXD1 |     | When MII_RXDV is high, the received packet is synchronized         |

|          |     | with MII_RXC and inputs in nibble unit.                            |

| MII_RXD0 |     | MII_RXD3 is MSB.                                                   |

| MII_RXDV | ID  | Receive Data Valid                                                 |

|          |     |                                                                    |

|          |     | This signal indicates the presence of received packet from         |

|          |     | MII_RXD[3:0].                                                      |

|          |     | It is asserted high when the first nibble data of the received     |

|          |     | packet is valid on MII_RXD[3:0] and is de-asserted low after       |

|          |     | the last nibble data of receive packet clocked in on               |

|          |     | MII_RXD[3:0].                                                      |

|          |     | It is valid when MII_RXC is at rising edge.                        |

| MII_RXC  | ID  | Receive Clock Input                                                |

|          |     |                                                                    |

|          |     | It is continuous receive clock from the external PHY. It is        |

|          |     | 25MHz at the 100Base TX and 2.5MHz at the 10BaseT.                 |

|          |     | Receive clock is used for timing reference of MII_RXD[3:0] and     |

|          |     | MII_RXDV.                                                          |

|          |     | Rising Edge Sensitive.                                             |

| /FDX     | IDL | Full-Duplex Select                                                 |

|          |     | 0 : Full-duplex                                                    |

|          |     | 1 : Half-duplex                                                    |

|          |     |                                                                    |

|          |     | It is input signal from PHY that indicates link status of external |

|          |     | PHY. Most of PHYs support auto-negotiation and notifies the        |

|          |     | result to network indicator LED or other signals. It can be        |

|          |     | connected to those signals and also it can be configurable         |

|          |     | manually by connecting high or low.                                |

Recommend for the better performance.

- 1. MII interface signal line length should not be more than 25cm if possible.

- 2. The length of MII\_TXD[3:0] should be same if possible.

- 3. The length of MII\_RXD[3:0] should be same if possible.

- 4. The length of MII\_TXC should not be longer than MII\_TXD[3:0] signal line by 2.5cm.

- 5. The length of MII\_RXC should not be longer than MII\_RXD[3:0] signal line by 2.5cm.

## 1.6 Network Indicator LED Signals

The signals except for LINKLED, are used as multi-function PIN according to the configuration of TEST\_MODE[3:0]. When using those signals as network indicator signals, internal PHY mode(TEST\_MODE[3:0]="0000") should be configured.

| Symbol            | Tuno | Description                                                     |

|-------------------|------|-----------------------------------------------------------------|

| Symbol            | Туре | Description                                                     |

| LINKLED           | OL   | Link LED                                                        |

|                   |      |                                                                 |

|                   |      | It indicates the link status of media(10/100M).                 |

| /TXLED(MII_TXEN)  | OML  | Transmit activity LED/Transmit Enable                           |

|                   |      |                                                                 |

|                   |      | It notifies the output of transmit data through TXOP/TXON       |

|                   |      | (Transmit Activity).                                            |

| /RXLED(MII_TXD3)  | OML  | Receive activity LED/Transmit Data                              |

|                   | -    |                                                                 |

|                   |      | It notifies the input of receive data from RXIP/RXIN (Receive   |

|                   |      | Activity)                                                       |

|                   |      |                                                                 |

|                   |      | of Dy hinding (TYLED and (DYLED aignale with (AND) gate, it     |

|                   |      | cf> By binding /TXLED and /RXLED signals with 'AND' gate, it    |

|                   |      | can be used for network activity LED.                           |

| /COLLED(MII_TXD2) | OML  | Collision LED/Transmit Data                                     |

|                   |      |                                                                 |

|                   |      | It notifies when collisions occur.                              |

|                   |      | It is valid at half-duplex, and is ignored at full-duplex.      |

| /FDXLED(MII_TXD1) | OML  | Full duplex LED/Transmit Data                                   |

|                   |      |                                                                 |

|                   |      | It outputs low at the full-duplex and outputs high at the half- |

|                   |      | duplex according to auto-negotiation or manual configuration    |

|                   |      | of OP_MODE[2:0].                                                |

| /SPDLED(MII_TXD0) | OML  | Link speed LED/Transmit Data                                    |

| ,                 |      |                                                                 |

|                   |      | It is asserted low at the 100Mbps and high at the 10Mbps        |

|                   |      | according to auto-negotiation or manual configuration of        |

|                   |      | OP_MODE[2:0].                                                   |

|                   |      |                                                                 |

## 1.7 Clock Signals

For the clock source of W5300, either a crystal or an oscillator may be used. 25MHz frequency from the clock source is created to 150MHz frequency using internal PLL logic. This 150MHz

frequency is used for PLL\_CLK(Period 6.67ns) and W5300 core operation clock. Symbol Туре Description **XTLP** 25MHz crystal input/output 25MHz parallel-resonant crystal is used with matching capacitor for internal oscillator stabilization. XTLN Refer to "Clock Characteristic" of "7. Electrical Specifications" These can be used for internal PHY mode(TEST\_MODE[3:0]="0000") or external PHY mode with crystal clock (TEST\_MODE[3:0]="0001"). When using oscillator at the internal PHY mode, be sure to use 1.8V level oscillator and connect only to XTLP. And let be float XTLN. OSC25I L 25MHz Oscillator input used only in external PHY mode with oscillator clock lt is (TEST MODE[3:0]="0010"). In order to prevent the leakage current, be sure to keep XTLP high and float XTLN, and use 1.8v level oscillator.

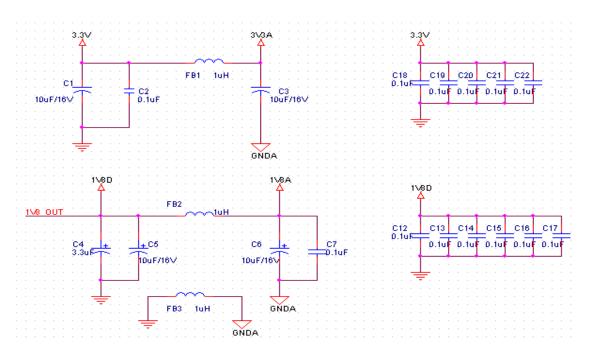

### 1.8 Power Supply Signals

| Symbol | Туре   | Description                                                      |  |  |

|--------|--------|------------------------------------------------------------------|--|--|

| VCC3A3 | Power  | 3.3V power supply for Analog part                                |  |  |

|        |        | Be sure to connect 10uF tantalum capacitor between VCC343 and    |  |  |

|        |        | GNDA in order to prevent power compensation.                     |  |  |

| VCC3V3 | Power  | 3.3V power supply for Digital part                               |  |  |

|        |        | Between each VCC and GND, 0.1uF decoupling capacitor can be      |  |  |

|        |        | selectively connected. VCC3V3 can be separated to 1uH ferrite    |  |  |

|        |        | bead and connected to VCC3A3.                                    |  |  |

| VCC1A8 | Power  | 1.8V power supply for Analog part                                |  |  |

|        |        | Be sure to connect a 10uF tantalum capacitor and 0.1uF capacitor |  |  |

|        |        | between VCC1A8 and GNDA for core power noise filtering.          |  |  |

| VCC1V8 | Power  | 1.8V power supply for Digital part                               |  |  |

|        |        | Between each VCC and GND, 0.1uF decoupling capacitor can be      |  |  |

|        |        | selectively connected.                                           |  |  |

| GNDA   | Ground | Analog ground                                                    |  |  |

|        |        | Make analogue ground plane as wide as possible when designing    |  |  |

|        |        | the PCB layout.                                                  |  |  |

| GND    | Ground | Digital ground                                                   |  |  |

|        |        | Make digital ground plane as wide as possible when designing the |  |  |

© Copyright 2008-2010 WIZnet Co., Inc. All rights reserved.

|      |   | PCB layout.                                                             |  |

|------|---|-------------------------------------------------------------------------|--|

| 1V8O | 0 | 1.8V regulator output voltage                                           |  |

|      |   | 1.8V/150mA power created by internal power regulator, is used for       |  |

|      |   | core operation power (VCC1A8, VCC1V8).                                  |  |

|      |   | Be sure to connect 3.3uF tantalum capacitor between 1V8O and            |  |

|      |   | GND for output frequency compensation, and selectively connect          |  |

|      |   | 10uF capacitor for high frequency noise decoupling. 1V8O is             |  |

|      |   | connected to VCC1V8, separated to 1uH ferrite bead and                  |  |

|      |   | connected to VCC1A8.                                                    |  |

|      |   |                                                                         |  |

|      |   | <notice> 1V8O is the power for W5300 core operation. It should</notice> |  |

|      |   | not be connected to the power of other devices.                         |  |

Fig 2. Power Design

Recommend for power design.

- 1. Locate decoupling capacitor as close as possible to W5300.

- 2. Use ground plane as wide as possible.

- 3. If ground plane width is adequate, having a separate analog ground plane and digital ground plane is good practice.

If ground plane is not wide, design analog and digital ground planes as a single ground plane, rather than separate them.

# 2. System Memory Map

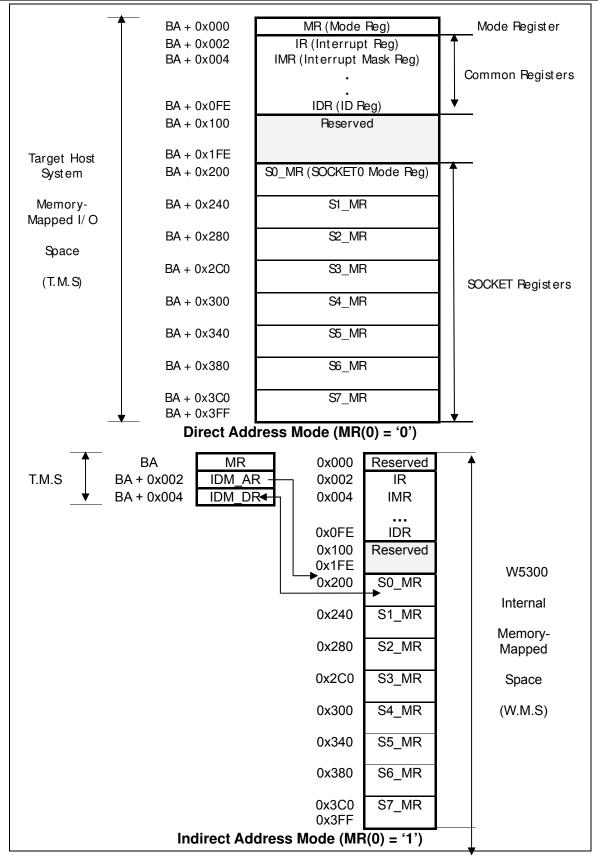

According to the host interface, W5300 supports direct address mode and indirect address mode.

The direct address mode is that the target host system can directly access W5300 registers after mapping the registers to T.M.S( $\underline{T}$  arget host system  $\underline{M}$  emory-mapped I/O  $\underline{S}$  pace).

Direct address mode memory map is composed of Mode register(MR), COMMON registers, and SOCKET registers. Those registers are mapped in T.M.S sequentially increasing by 2bytes from the BA(<u>Base Address</u>) of T.M.S. Using the mapping address, the target host system can directly access MR, COMMON registers and SOCKET registers. To use the direct address mode, total 0x400 bytes are required for memory space.

In indirect address mode, target host system indirectly accesses COMMON registers and SOCKET registers by using IDM\_AR(Indirect Mode Address Register) and IDM\_DR(Indirect Mode Data Register) which are just only directly mapped in T.M.S together with MR.

Indirect address mode memory map is composed of direct accessible MR, IDM\_AR, IDM\_DR and indirect accessible COMMON & SOCKET registers. Only MR, IDM\_AR and IDM\_DR are mapped in T.M.S sequentially increasing by 2Bytes from BA of T.M.S, but COMMON & SOCKET registers are not mapped in T.M.S because those register can be accessed indirectly using IDM\_AR & IDM\_DR. To use the indirect address mode, just 0x06 bytes are required for memory space.

When target host system access Interrupt register(IR) of COMMON registers at the indirect address mode, it is processed as below:

Host Write : Set IDM\_AR to 0x0002, IR address(IDM\_AR = 0x0002)Set IDM\_DR to 0xFFFF(IDM\_DR = 0xFFFF)Host Read : Set IDM\_AR to 0x0002, IR address(IDM\_AR = 0x0002)Read IDM\_DR and save as Value(Value = IDM\_DR)

The host interface mode of W5300 is decided according to the value of 'IND' bit (0<sup>th</sup> bit) of MR.

MR(0) = '0' => Direct address mode

MR(0) = '1' => Indirect address mode

The memory map of each address mode is as below:

Fig 3. Memory Map

### 3. W5300 Registers

W5300 register is composed of MR(to decide direct or indirect address mode), IDM\_AR & IDM\_DR(only used at the indirect address mode) and COMMON registers and SOCKET registers.

MR, IDM\_AR, and IDM\_DR register are mapped in T.M.S. COMMON & SOCKET registers are mapped in T.M.S or W.M.S (<u>W5300</u> internal <u>Memory Space</u>) according to address mode.

All W5300 registers are 1Byte, 2Bytes, 4Bytes or 6Bytes. According to data bus width of target host system, the access is processed – 2bytes address offset at the 16bit data bus and 1 byte address offset at the 8bit data bus.

When mapping W5300 registers in T.M.S, the physical T.M.S address of W5300 register is calculated as below.

Physical Address of W5300 Reg = Base Address of T.M.S + Address offset of W5300 Reg

The byte ordering of W5300 registers is big-endian – low address byte is used as the most significant byte.

#### [Register Notation]

MR : MR register MR0 : Low address register of MR (Address offset - 0x000 ), Most significant byte MR1 : High address register of MR (Address offset - 0x001), Least significant byte MR(15:5) : 11 bit (from 15<sup>th</sup> bit to 5<sup>th</sup> bit of MR register) MR(0) : 0<sup>th</sup> bit of MR register, 0<sup>th</sup> bit of MR1 MR(13) : 13<sup>th</sup> bit of MR register, 5<sup>th</sup> bit of MR0 MR0(7) : 15<sup>th</sup> bit of MR register, Most significant bit of MR0 MR(DWB) : MR <sup>Q</sup>] DWB bit (DWB : Bit Symbol) SHAR : Source Hardware Address Register SHAR0 : 1<sup>ST</sup> address register of SHAR (Address offset – 0x008) SHAR1 : 2<sup>nd</sup> address register of SHAR (Address offset – 0x009) SHAR2 : 3<sup>rd</sup> address register of SHAR (Address offset – 0x008) SHAR3 : 4<sup>th</sup> address register of SHAR (Address offset – 0x008) SHAR4 : 5<sup>th</sup> Address register of SHAR (Address offset – 0x008)

### 3.1 Mode Register

| Addre   | Address offset Sym |       | nbol | Description   |  |

|---------|--------------------|-------|------|---------------|--|

| 16Bit   | 8Bit               | 16Bit | 8Bit | Description   |  |

| 0x000 — | 0x000              | MR    | MR0  | Mode Register |  |

|         | 0x001              |       | MR1  | Mode Register |  |

## 3.2 Indirect Mode Registers

| Address offset |       | Symbol |         | Description                    |

|----------------|-------|--------|---------|--------------------------------|

| 16Bit          | 8Bit  | 16Bit  | 8Bit    | Description                    |

| 0,000          | 0x002 |        | IDM_AR0 | Indirect Mode Address Register |

| 0x002          | 0x003 | IDM_AR | IDM_AR1 |                                |

| 0x004          | 0x004 | IDM_DR | IDM_DR0 | Indirect Mode Data Register    |

| 0x004          | 0x005 |        | IDM_DR1 |                                |

## 3.3 COMMON registers

| Address offset |                   | Symbol |       | Description                      |

|----------------|-------------------|--------|-------|----------------------------------|

| 16Bit          | 8Bit              | 16Bit  | 8Bit  | Description                      |

| 0×002          | 0x002 0x002 0x003 | IR     | IR0   | Interrupt Register               |

| 0X002          |                   |        | IR1   |                                  |

| 0x004          | 0x004             |        | IMR0  | Interrupt Mask Register          |

| 0X004          | 0x005             | IMR    | IRM1  |                                  |

| 0x006          | 0x006             |        |       | Reserved                         |

| 00000          | 0x007             |        |       |                                  |

| 0x008          | 0x008             | SHAR   | SHAR0 | Source Hardware Address Register |

| 00000          | 0x009             | SHAR   | SHAR1 |                                  |

| 0x00A          | 0x00A             | SHAR2  | SHAR2 |                                  |

|                | 0x00B             |        | SHAR3 |                                  |

| 0x00C          | 0x00C             | SHAR4  | SHAR4 |                                  |

|                | 0x00D             |        | SHAR5 |                                  |

| 0x00E          | 0x00E             |        |       | Reserved                         |

|                | 0x00F             |        |       |                                  |

| 0x010          | 0x010             | - GAR  | GAR0  | Gateway Address Register         |

|                | 0x011             |        | GAR1  |                                  |

| 0x12           | 0x012             | - GAR2 | GAR2  |                                  |

|                | 0x013             | GAR3   |       |                                  |