# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### W78ERD2/W78ERD2A Data Sheet

## nuvoTon

## **8-BIT MICROCONTROLLER**

| Tabl | le of C | ontents-                                              |    |

|------|---------|-------------------------------------------------------|----|

| 1.   | GENE    | ERAL DESCRIPTION                                      |    |

| 2.   | FEAT    | URES                                                  |    |

| 3.   | PIN C   | ONFIGURATIONS                                         | 4  |

| 4.   | PIN D   | ESCRIPTION                                            | 5  |

| 5.   | FUNC    | TIONAL DESCRIPTION                                    | 6  |

|      | 5.1     | RAM                                                   | 6  |

|      | 5.2     | Timers/Counters                                       | 6  |

|      | 5.3     | Clock                                                 | 7  |

|      | 5.4     | Power Management                                      |    |

|      | 5.5     | Reduce EMI Emission                                   | 7  |

|      | 5.6     | Reset                                                 | 7  |

| 6.   | SPEC    | IAL FUNCTION REGISTER                                 |    |

| 7.   | PORT    | 4 AND BASE ADDRESS REGISTERS                          |    |

| 8.   | INTE    | RUPTS                                                 | 32 |

|      | 8.1     | External Interrupts 2 and 3                           | 32 |

|      | 8.2     | Interrupt Priority                                    | 32 |

| 9.   | PROC    | GRAMMABLE TIMERS/COUNTERS                             |    |

|      | 9.1     | Timer 0 and Timer 1                                   |    |

|      | 9.2     | Timer/Counter 2                                       | 35 |

| 10.  | ENHA    | NCED FULL DUPLEX SERIAL PORT                          |    |

|      | 10.1    | MODE 0                                                |    |

|      | 10.2    | MODE 1                                                |    |

|      | 10.3    | MODE 2                                                | 40 |

|      | 10.4    | MODE 3                                                | 41 |

|      | 10.5    | Framing Error Detection                               | 42 |

|      | 10.6    | Multi-Processor Communications                        | 42 |

| 11.  | PROC    | GRAMMABLE COUNTER ARRAY (PCA)                         | 44 |

|      | 11.1    | PCA Capture Mode                                      | 47 |

|      | 11.2    | 16-bit Software Timer Comparator Mode                 | 47 |

|      | 11.3    | High Speed Output Mode                                | 48 |

|      | 11.4    | Pulse Width Modulator Mode                            | 49 |

|      | 11.5    | Watchdog Timer                                        | 49 |

| 12.  | HARD    | WARE WATCHDOG TIMER (ONE-TIME ENABLED WITH RESET-OUT) | 50 |

## nuvoTon

| 13. | DUAL   | DPTR                                          | 50 |

|-----|--------|-----------------------------------------------|----|

| 14. | TIMED  | -ACCESS PROTECTION                            | 51 |

| 15. | IN-SYS | STEM PROGRAMMING (ISP) MODE                   | 53 |

| 16. | H/W R  | EBOOT MODE (BOOT FROM LDROM)                  | 57 |

| 17. |        | N BITS REGISTER                               |    |

| 18. | ELECT  | FRICAL CHARACTERISTICS                        | 60 |

|     | 18.1   | Absolute Maximum Ratings                      | 60 |

|     | 18.2   | D.C. Characteristics                          | 60 |

|     | 18.3   | A.C. Characteristics                          | 62 |

| 19. | TIMIN  | G WAVEFORMS                                   | 64 |

| 20. | TYPIC  | AL APPLICATION CIRCUITS                       |    |

|     | 20.1   | External Program Memory and Crystal           |    |

|     | 20.2   | Expanded External Data Memory and Oscillator  | 67 |

| 21. | PACK   | AGE DIMENSIONS                                | 68 |

| 22. | APPLI  | CATION NOTE                                   | 70 |

|     | 22.1   | In-System Programming (ISP) Software Examples | 70 |

|     | 22.2   | How to Use Programmable Counter Array         | 74 |

| 23. | REVIS  | ION HISTORY                                   | 75 |

Publication Release Date: March 2, 2009 Revision A12

### **1. GENERAL DESCRIPTION**

The W78ERD2 is an 8-bit microcontroller which is pin- and instruction-set-compatible with the standard 80C52. The W78ERD2 contains a 64-KB Flash EPROM whose contents may be updated in-system by a loader program stored in an auxiliary, 4-KB Flash EPROM. Once the contents are confirmed, it can be protected for security.

The W78ERD2 also contains 256 bytes of on-chip RAM; 1 KB of auxiliary RAM; four 8-bit, bidirectional and bit-addressable I/O ports; an additional 4-bit port P4; three 16-bit timer/counters; and a serial port. These peripherals are all supported by nine interrupt sources with 4 levels of priority.

The W78ERD2 has two power-reduction modes: idle mode and power-down mode, both of which are software-selectable. Idle mode turns off the processor clock but allows peripherals to continue operating, while power-down mode stops the crystal oscillator for minimum power consumption. Power-down mode can be activated at any time and in any state without affecting the processor.

### 2. FEATURES

- 8-bit CMOS microcontroller

- Pin-compatible with standard 80C52

- Instruction-set compatible with 80C52

- Four 8-bit I/O ports; Port 0 has internal pull-up resisters enabled by software.

- One extra 4-bit I/O port with interrupt and chip-select functions

- Three 16-bit timers

- Programmable clock out

- Programmable Counter Array (PCA) with PWM, Capture, Compare and Watchdog functions

- 9 interrupt sources with 4 levels of priority

- Full-duplex serial port with framing-error detection and automatic address recognition

- 64-KB, in-system-programmable, Flash EPROM (AP Flash EPRAOM)

- 4-KB auxiliary Flash EPROM for loader program (LD Flash EPROM)

- 256-byte on-chip RAM

- 1-KB auxiliary RAM, software-selectable

- Software Reset

- 12 clocks per machine cycle operation (default). Speed up to 40 MHz.

- 6 clocks per machine cycle operation set by the writer. Speed up to 20 MHz.

- 2 DPTR registers

- Low EMI (inhibit ALE)

- Built-in power management with idle mode and power down mode

- Code protection

- Packages:

- Lead Free (RoHS) DIP 40: W78ERD2A40DL

- Lead Free (RoHS) PLCC 44: W78ERD2A40PL

- Lead Free (RoHS) PQFP 44: W78ERD2A40FL

- 3 -

## nuvoTon

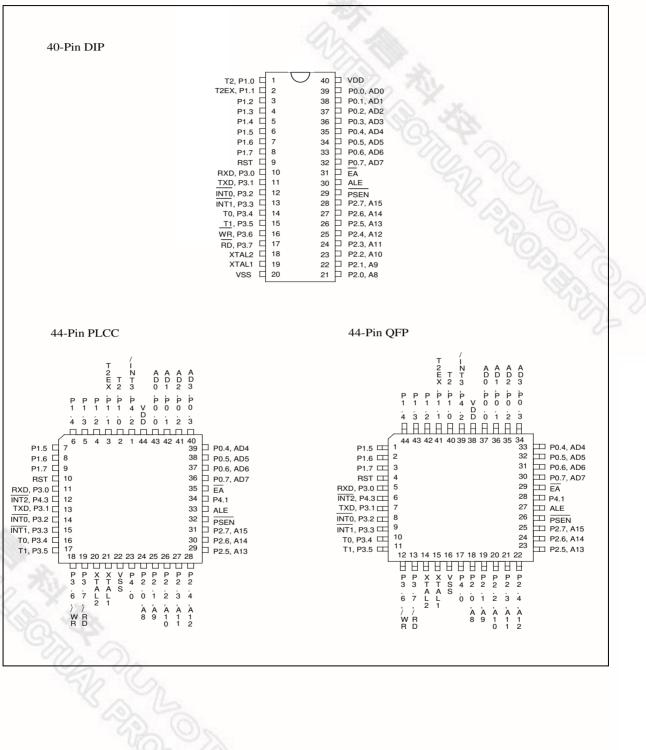

#### 3. PIN CONFIGURATIONS

Publication Release Date: March 2, 2009 Revision A12

### 4. PIN DESCRIPTION

| r               |       |                                                                                                                                                                                          |

|-----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL          | TYPE* | DESCRIPTIONS                                                                                                                                                                             |

| ĒĀ              | Ι     | EXTERNAL ACCESS ENABLE: This pin forces the processor to execute instructions in external ROM. The ROM address and data are not presented on the bus if the $\overline{EA}$ pin is high. |

| PSEN            | ОН    | PROGRAM STORE ENABLE: PSEN indicates external ROM data is on the Port 0 address/data bus. If internal ROM is accessed, no PSEN strobe signal is present on this pin.                     |

| ALE             | ОН    | ADDRESS LATCH ENABLE: ALE is used to enable the address latch that separates the address from the data on Port 0. ALE runs at 1/6th of the oscillator frequency.                         |

| RST             | ΙL    | RESET: If this pin is set high for two machine cycles while the oscillator is running, the W78ERD2 is reset.                                                                             |

| XTAL1           |       | CRYSTAL 1: Crystal oscillator input or external clock input.                                                                                                                             |

| XTAL2           | 0     | CRYSTAL 2: Crystal oscillator output.                                                                                                                                                    |

| V <sub>SS</sub> |       | GROUND: ground potential.                                                                                                                                                                |

| V <sub>DD</sub> | Ι     | POWER SUPPLY: Supply voltage for operation.                                                                                                                                              |

| P0.0 – P0.7     | I/O D | PORT 0: 8-bit, bi-directional I/O port, the same as that of the standard 80C52.                                                                                                          |

| PU.U - PU.7     | 1/U D | Port 0 has internal pull-up resisters enabled by software.                                                                                                                               |

| P1.0 – P1.7     | I/O H | PORT 1: 8-bit, bi-directional I/O port, the same as that of the standard 80C52.                                                                                                          |

| P2.0 – P2.7     | I/O H | PORT 2: 8-bit, bi-directional I/O port with internal pull-ups. This port also provides the upper address bits when accessing external memory.                                            |

| P3.0 – P3.7     | I/O H | PORT 3: 8-bit, bi-directional I/O port, the same as that of the standard 80C52.                                                                                                          |

| P4.0 – P4.3     | I/O H | PORT 4: 4-bit, bi-directional I/O port with chip-select functions.                                                                                                                       |

\* Note: TYPE I: input, O: output, I/O: bi-directional, H: pull-high, L: pull-low, D: open drain

Publication Release Date: March 2, 2009 Revision A12

### 5. FUNCTIONAL DESCRIPTION

The W78ERD2 architecture consists of a core processor that supports 111 different op-codes and references 64 KB of program space and 64 KB of data space. It is surrounded by various registers; four general-purpose I/O ports; one special-purpose, programmable, 4-bit I/O port; 256 bytes of RAM; 1 KB of auxiliary RAM (AUX-RAM); three timer/counters; a serial port; and an internal 74373 latch and 74244 buffer which can be switched to port 2.

This section introduces the RAM, Timers/Counters, Clock, Power Management, Reduce EMI Emission, and Reset.

### 5.1 RAM

The W78ERD2 has two banks of RAM: 256 bytes of RAM and 1 KB of AUX-RAM. AUX-RAM is enabled by clearing bit 1 in the AUXR register, and it is enabled after reset. Different addresses in RAM are addressed in different ways.

- RAM 00H 7FH can be addressed directly or indirectly, as in the 8051. The address pointers are R0 and R1 of the selected bank.

- RAM 80H FFH can only be addressed indirectly, as in the 8051. The address pointers are R0 and R1 of the selected bank.

- AUX-RAM 00H –3FFH is addressed indirectly in the same way external data memory is accessed with the MOVX instruction. The address pointers are R0 and R1 of the selected bank and the DPTR register.

- Addresses higher than 3FFH are stored in external memory and are accessed indirectly with the MOVX instruction, as in the 8051.

When AUX-RAM is enabled, the instruction "MOVX @Ri" always accesses AUX-RAM. When the W78ERD2 is executing instructions from internal program memory, accessing AUX-RAM does not affect ports P0, P2,  $\overline{WR}$  or  $\overline{RD}$ .

For example,

| ANL  | AUXR,#11111101B | ; | Enable AUX-RAM                                |

|------|-----------------|---|-----------------------------------------------|

| MOV  | DPTR,#1234H     |   |                                               |

| MOV  | A,#56H          |   |                                               |

| MOVX | @DPTR,A         | ; | Write 56h to address 1234H in external memory |

| MOV  | XRAMAH,#02H     | ; | Only 2 LSB effective                          |

| MOV  | R0,#34H         |   |                                               |

| MOV  | A,@R0           | ; | Read AUX-RAM data at address 0234H            |

|      |                 |   |                                               |

#### 5.2 Timers/Counters

The W78ERD2 has three timers/counters called Timer 0, Timer 1, and Timer 2. Each timer/counter consists of two 8-bit data registers: TL0 and TH0 for Timer 0, TL1 and TH1 for Timer 1, and TL2 and TH2 for Timer 2.

The operations of Timer 0 and Timer 1 are similar to those in the W78C52, and these timers are controlled by the TCON and TMOD registers.

Timer 2 is controlled by the T2CON register. Like Timers 0 and 1, Timer 2 can operate as either an external event counter or an internal timer, depending on the setting of bit C/T2 in T2CON. Timer 2 has three operating modes: capture, auto-reload, and baud rate generator. In capture or auto-reload mode, RCAP2H and RCAP2L are the reload / capture registers and the clock speed is the same as that of Timers 0 and 1.

#### 5.3 Clock

The W78ERD2 is designed for either a crystal oscillator or an external clock.

The W78ERD2 incorporates a built-in crystal oscillator. To make the oscillator work, a crystal must be connected across pins XTAL1 and XTAL2, and a load capacitor may be connected from each pin to ground. In addition, if the crystal frequency is higher than 24 MHz, a resistor should be connected between XTAL1 and XTAL2 to provide a DC bias.

An external clock is connected to pin XTAL1, while pin XTAL2 should be left disconnected. The XTAL1 input is a CMOS-type input, as required by the crystal oscillator. As a result, the logic-1 voltage should be higher than 3.5 V.

#### **Power Management** 5.4

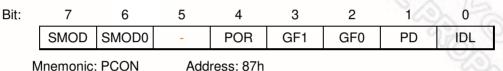

The W78ERD2 provides two modes, idle mode and power-down mode, to reduce power consumption. Both modes are entered by software.

The W78ERD2 enters Idle mode when the IDL bit in the PCON register is set. In Idle mode, the internal clock for the processor stops while the internal clock for the peripherals and interrupt logic continues to run. The W78ERD2 leaves Idle mode when an interrupt or a reset occurs.

The W78ERD2 enters Power-Down mode when the PD bit in the PCON register is set. In Power-Down mode, all of the clocks are stopped, including the oscillator. The W78ERD2 leaves Power-Down mode when there is a hardware reset or by external interrupts  $\overline{INT0}$  or  $\overline{INT1}$ , if enabled.

#### 5.5 **Reduce EMI Emission**

If the crystal frequency is less than 25 MHz, set bit 7 in the option register to 0 to reduce EMI emissions. Please see Option Bits for more information.

#### 5.6 Reset

The external RESET signal is sampled at S5P2. To take effect, it must be held high for at least two machine cycles while the oscillator is running, as the W78ERD2 has a special glitch-removal circuit that ignores glitches on the reset line.

During reset, the ports are initialized to FFH, the stack pointer to 07H, and all of the other SFR to 00H, with two exceptions—SBUF does not change, and bit 4 in PCON is not cleared. ALL COLOCION

Publication Release Date: March 2, 2009 Revision A12

- 7 -

### 6. SPECIAL FUNCTION REGISTER

The following table identifies the Special Function Registers (SFRs) in the W78ERD2, as well as each of their addresses and reset values.

|     |          | CH       | CCAP0H   | CCAP1H   | CCAP2H   | CCAP3H   | CCAP4H   |          |   |

|-----|----------|----------|----------|----------|----------|----------|----------|----------|---|

| F8  |          |          |          |          |          |          |          |          | F |

|     |          | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 |          |   |

| F0  | +B       |          |          |          |          | X/A      | CHPENR   |          | F |

|     | 00000000 |          | 00450    | 00454    | 00450    | 0.04.501 | 00000000 |          | _ |

| E8  | +P4      | CL       | CCAP0L   | CCAP1L   | CCAP2L   | CCAP3L   | CCAP4L   | <i></i>  | E |

|     | xxxx1111 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 0        |   |

| E0  | +ACC     |          |          |          |          |          |          | Ca       | I |

|     | 00000000 |          |          |          |          |          |          | ×1       |   |

| D8  | CCON     | CMOD     | CCAPM0   | CCAPM1   | CCAPM2   | CCAPM3   | CCAPM4   | CKCON    | 1 |

|     | x0000000 | 00xxx000 | x0000000 | x0000000 | x0000000 | x0000000 | x0000000 | xx000xx1 |   |

| D0  | +PSW     |          |          |          |          |          |          | 10h      | 6 |

| -   | 00000000 |          |          |          |          |          |          | age -    |   |

| C8  | +T2CON   | T2MOD    | RCAP2L   | RCAP2H   | TL2      | TH2      |          | S.       |   |

|     | 00000000 | xxxxxx00 | 00000000 | 00000000 | 00000000 | 00000000 |          | 1        |   |

| C0  | XICON    | XICONH   | P4CONA   | P4CONB   | SFRAL    | SFRAH    | SFRFD    | SFRCN    |   |

| 00  | 00000000 | 0xxx0xxx | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 |   |

| B8  | +IP      | SADEN    |          |          |          |          |          | CHPCON   |   |

| DO  | x0000000 | 00000000 |          |          |          |          |          | 000xx000 |   |

| B0  | +P3      |          |          |          | P43AL    | P43AH    |          | IPH      |   |

| DU  | 11111111 |          |          |          | 00000000 | 00000000 |          | x0000000 |   |

| A8  | +IE      | SADDR    |          |          | P42AL    | P42AH    | P4CSIN   |          |   |

| Ao  | 00000000 | 00000000 |          |          | 00000000 | 00000000 | 00000000 |          | 4 |

| • • | +P2      | XRAMAH   | AUXR1    |          |          |          | WDTRST   |          |   |

| A0  | 11111111 | 00000000 | xxxxx0x0 |          |          |          | 00000000 |          |   |

|     | +SCON    | SBUF     |          |          |          |          | P2EAL    | P2EAH    |   |

| 98  | 00000000 | xxxxxxxx |          |          |          |          | 00000000 | 00000000 | 1 |

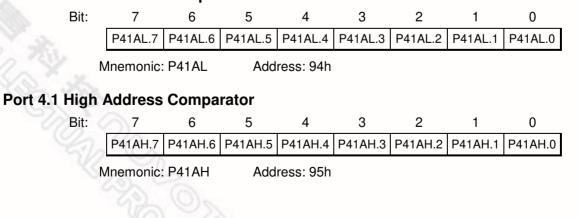

| 00  | +P1      |          |          |          | P41AL    | P41AH    |          |          |   |

| 90  | 11111111 |          |          |          | 00000000 | 00000000 |          |          |   |

| 00  | +TCON    | TMOD     | TL0      | TL1      | TH0      | TH1      | AUXR     |          |   |

| 88  | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 |          |   |

| -   | +P0      | SP       | DPL      | DPH      | P40AL    | P40AH    | PORT     | PCON     |   |

| 80  | 11111111 | 00000111 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00110000 | - |

Notes:

- 1. SFRs marked with a plus sign (+) are both byte- and bit-addressable.

- 2. The text of SFR with bold type characters are extension function registers.

The rest of this section explains each SFR, starting with the lowest address.

## nuvoTon

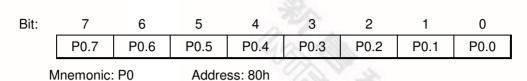

#### Port 0

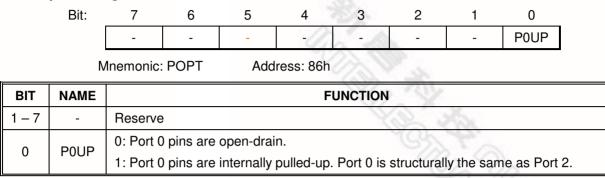

Port 0 is an open-drain, bi-directional I/O port after chip is reset. Besides, it has internal pull-up resisters enabled by setting P0UP of POPT (86H) to high. This port also provides a multiplexed, low-order address/data bus when the W78IRD2 accesses external memory.

#### **Stack Pointer**

| Bit: | 7          | 6    | 5    | 4         | 3    | 2    | 525                                     | 0    |

|------|------------|------|------|-----------|------|------|-----------------------------------------|------|

|      | SP.7       | SP.6 | SP.5 | SP.4      | SP.3 | SP.2 | SP.1                                    | SP.0 |

| Ν    | /Inemonic: | SP   | Add  | ress: 81h |      |      | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 20   |

The Stack Pointer stores the RAM address (scratchpad RAM, not AUX-RAM) where the stack begins. It always points to the top of the stack.

#### **Data Pointer Low**

| Bit: | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

|      | DPL.7 | DPL.6 | DPL.5 | DPL.4 | DPL.3 | DPL.2 | DPL.1 | DPL.0 |

|      |       |       |       |       |       |       |       |       |

Mnemonic: DPL Address: 82h

This is the low byte of the standard-8052 16-bit data pointer.

#### **Data Pointer High**

| Bit: | 7          | 6     | 5     | 4         | 3     | 2     | 1     | 0     |

|------|------------|-------|-------|-----------|-------|-------|-------|-------|

|      | DPH.7      | DPH.6 | DPH.5 | DPH.4     | DPH.3 | DPH.2 | DPH.1 | DPH.0 |

| Ν    | /Inemonic: | : DPH | Add   | ress: 83h |       |       |       |       |

This is the high byte of the standard-8052 16-bit data pointer.

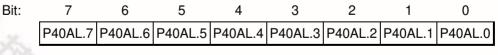

#### Port 4.0 Low-Address Comparator

Mnemonic: P40AL Address: 84h

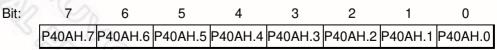

### Port 4.0 High-Address Comparator

Mnemonic: P40AH Address: 85h

## nuvoTon

### **Port Option Register**

#### **Power Control**

Mnemonic: PCON

| BIT | NAME    | FUNCTION                                                                                          |

|-----|---------|---------------------------------------------------------------------------------------------------|

| 7   | SMOD    | 1: Double the serial-port baud rate in serial port modes 1, 2, and 3.                             |

| 6   | SMOD0   | 0: Framing Error Detection Disable. SCON.7 acts as per the standard 8052 function.                |

| 0   | 3101000 | 1: Framing Error Detection Enable. SCON.7 indicates a Frame Error and acts as the FE (FE_1) flag. |

| 5   | -       | Reserved                                                                                          |

| 4   | POF     | This bit is set to 1 when a power-on reset has occurred. It can be cleared by software.           |

| 3   | GF1     | General-purpose flag.                                                                             |

| 2   | GF0     | General-purpose flag.                                                                             |

| 1   | PD      | Set this bit to 1 to go into POWER DOWN mode.                                                     |

| 0   | IDL     | Set this bit to 1 to go into IDLE mode.                                                           |

### **Timer Control**

| Bit: | 7        | 6      | 5   | 4         | 3   | 2   | 1   | 0   |

|------|----------|--------|-----|-----------|-----|-----|-----|-----|

|      | TF1      | TR1    | TF0 | TR0       | IE1 | IT1 | IE0 | IT0 |

|      | Mnemonic | : TCON | Add | ress: 88h |     |     |     |     |

Publication Release Date: March 2, 2009 Revision A12

- 10 -

| BIT | NAME | FUNCTION                                                                                                                                                                                                                                                                          |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1  | Timer 1 overflow flag: This bit is set when Timer 1 overflows. It is cleared automatically when the program does a timer 1 interrupt service routine. It can also be set or cleared by software.                                                                                  |

| 6   | TR1  | 1: Turn on Timer 1.                                                                                                                                                                                                                                                               |

| Ŭ   |      | 0: Turn off Timer 1.                                                                                                                                                                                                                                                              |

| 5   | TF0  | Timer 0 overflow flag: This bit is set when Timer 0 overflows. It is cleared automatically when the program does a timer 0 interrupt service routine. It can also be set or cleared by software.                                                                                  |

| 4   | TR0  | 1: Turn on Timer 0.                                                                                                                                                                                                                                                               |

| 4   | INU  | 0: Turn off Timer 0.                                                                                                                                                                                                                                                              |

| 3   | IE1  | Interrupt 1 Edge Detect: This bit is set by the hardware when a falling-edge / low-<br>level is detected on INT1. If INT1 is edge-triggered, this bit is cleared by the<br>hardware when the interrupt service routine begins. Otherwise, it follows the pin.                     |

|     |      | Interrupt 1 type control                                                                                                                                                                                                                                                          |

| 2   | IT1  | 1: Interrupt 1 is triggered by a falling-edge on INT1.                                                                                                                                                                                                                            |

|     |      | 0: Interrupt 1 is triggered by a low-level on INT1.                                                                                                                                                                                                                               |

| 1   | IE0  | Interrupt 0 Edge Detect: This bit is set by the hardware when a falling-edge / low-level is detected on $\overline{INT0}$ . If $\overline{INT0}$ is edge-triggered, this bit is cleared by the hardware when the interrupt service routine begins. Otherwise, it follows the pin. |

|     |      | Interrupt 0 type control                                                                                                                                                                                                                                                          |

| 0   | IT0  | 1: Interrupt 0 is triggered by a falling-edge on INT0.                                                                                                                                                                                                                            |

|     |      | 0: Interrupt 0 is triggered by a low-level on $\overline{INTO}$ .                                                                                                                                                                                                                 |

### **Timer Mode Control**

| GATE C/T M1 M0 GATE | C/T | M1 | MO |

|---------------------|-----|----|----|

| Inne   | r Mode (  | Jontrol            |                                                                                                                                                                                                                        |                        |                          |           |     |    |             |        |

|--------|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------|-----------|-----|----|-------------|--------|

|        | Bit:      | 7                  | 6                                                                                                                                                                                                                      | 5                      | 4                        | 3         | 2   | 1  | 0           |        |

|        |           | GATE               | C/T                                                                                                                                                                                                                    | M1                     | M0                       | GATE      | C/T | M1 | M0          |        |

|        |           | Mnemonic:          | TMOD                                                                                                                                                                                                                   | Add                    | ress: 89h                |           |     |    |             |        |

| BIT    | NAME      |                    |                                                                                                                                                                                                                        |                        | FL                       | JNCTION   |     |    |             |        |

| 7      | GATE      | pin is high        | Gating control: When this bit is set, Timer/Counter 1 is enabled only while the INT1 pin is high and the TR1 control bit is set. When cleared, the INT1 pin has no effect, and Timer 1 is enabled whenever TR1 is set. |                        |                          |           |     |    |             |        |

|        |           |                    |                                                                                                                                                                                                                        |                        |                          | 13 301.   |     |    |             |        |

| 6      | C/T       | Timer or clock. Wh |                                                                                                                                                                                                                        | Select: W              | hen clea                 | red, Time |     |    | d by the ir | nterna |

| 6<br>5 | C/T<br>M1 |                    | en set, Ti                                                                                                                                                                                                             | Select: W<br>mer 1 cou | hen clea<br>Ints falling | red, Time |     |    | d by the ir | nterna |

Continued

| BIT | NAME | FUNCTION                                                                                                                                                                                                                                         |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | GATE | Gating control: When this bit is set, Timer/Counter 0 is enabled only while the $\overline{INT0}$ pin is high and the TR0 control bit is set. When cleared, the $\overline{INT0}$ pin has no effect, and Timer 0 is enabled whenever TR0 is set. |

| 2   | C/T  | Timer or Counter Select: When cleared, Timer 0 is incremented by the internal clock. When set, Timer 0 counts falling edges on the T0 pin.                                                                                                       |

| 1   | M1   | Timer 0 Mode Select bits: See below.                                                                                                                                                                                                             |

| 0   | MO   | Timer 0 Mode Select bits: See below.                                                                                                                                                                                                             |

M1, M0: Mode Select bits:

- M1 M0 Mode

- 0 0 Mode 0: 8048 timer, TLx serves as 5-bit pre-scale.

- 0 Mode 1: 16-bit timer/counter, no pre-scale. 1

- Mode 2: 8-bit timer/counter with auto-reload from THx 1 0

1 Mode 3: (Timer 0) TL0 is an 8-bit timer/counter controlled by the standard Timer-0 control bits. TH0 is an 8-bit timer only controlled by Timer-1 control bits. (Timer 1) Timer/Counter 1 is stopped.

#### Ti

1

| Timer 0 LSB                             |          |            |            |                |            |            |            |            |

|-----------------------------------------|----------|------------|------------|----------------|------------|------------|------------|------------|

| Bit:                                    | 7        | 6          | 5          | 4              | 3          | 2          | 1          | 0          |

|                                         | TL0.7    | TL0.6      | TL0.5      | TL0.4          | TL0.3      | TL0.2      | TL0.1      | TL0.0      |

| l                                       | Mnemonic | TL0        | Add        | ress: 8Ah      |            |            |            |            |

| TL0.7-0: Timer 0                        | Low byte |            |            |                |            |            |            |            |

| Timer 1 LSB                             |          |            |            |                |            |            |            |            |

| Bit:                                    | 7        | 6          | 5          | 4              | 3          | 2          | 1          | 0          |

|                                         | TL1.7    | TL1.6      | TL1.5      | TL1.4          | TL1.3      | TL1.2      | TL1.1      | TL1.0      |

| Mnemonic: TL1 Address: 8Bh              |          |            |            |                |            |            |            |            |

| No.                                     | Mnemonic | TL1        | Add        | ress: 8Bh      |            |            |            |            |

| TL1.7-0: Timer 1                        |          | TL1        | Add        | ress: 8Bh      |            |            |            |            |

|                                         |          | TL1        | Add        | ress: 8Bh      |            |            |            |            |

| TL1.7-0: Timer 1                        |          | TL1<br>6   | Add<br>5   | ress: 8Bh<br>4 | 3          | 2          | 1          | 0          |

| TL1.7-0: Timer 1<br>Timer 0 MSB         | Low byte |            |            |                |            | 2<br>TH0.2 | 1<br>TH0.1 | 0<br>TH0.0 |

| TL1.7-0: Timer 1<br>Timer 0 MSB<br>Bit: | Low byte | 6<br>TH0.6 | 5<br>TH0.5 | 4              | 3<br>TH0.3 |            | -          | -          |

## nuvoTon

| Timer <sup>·</sup> |                                         |           |                |             |           |         |       |        |        |

|--------------------|-----------------------------------------|-----------|----------------|-------------|-----------|---------|-------|--------|--------|

| Timer              | Bit:                                    | 7         | 6              | 5           | 4         | 3       | 2     | 1      | 0      |

|                    |                                         | TH1.7     | TH1.6          | TH1.5       | TH1.4     | TH1.3   | TH1.2 | TH1.1  | TH1.0  |

|                    | M                                       | nemonic   | : TH1          | Add         | ress: 8Dh | 12      | Sec.  |        |        |

| H1.7-0             | : Timer 1                               | High byte | •              |             |           |         |       |        |        |

| uxilia             | ry Regis                                | ster      |                |             |           |         |       |        |        |

|                    | Bit:                                    | 7         | 6              | 5           | 4         | 3       | 2     | 50     | 0      |

|                    |                                         | -         | -              | -           | -         | -       | - 0   | EXTRAM | ALEOFF |

|                    | М                                       | nemonic   | : AUXR         | Add         | ress: 8Eh |         |       |        |        |

| BIT                | NAME                                    |           |                |             |           | FUNCTIO | N     | 0      | 220    |

| 7~2                | -                                       | Reser     | ve             |             |           |         |       |        | YO.    |

| 1                  | EXTRA                                   | 0 = Er    | Enable AUX-RAM |             |           |         |       |        |        |

| 1                  |                                         | 1 = Di    | sable AU       | X-RAM       |           |         |       |        |        |

| 0                  | ALEOF                                   | 0: ALE    | E express      | ion is ena  | bled.     |         |       |        |        |

| Ū                  | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 1: ALE    | E express      | ion is disa | bled.     |         |       |        |        |

| Port 1             |                                         |           |                |             |           |         |       |        |        |

|                    | Bit:                                    | 7         | 6              | 5           | 4         | 3       | 2     | 1      | 0      |

|                    |                                         |           |                |             |           |         |       |        |        |

P1.7

P1.6

P1.5

P1.4

P1.3

P1.2

P1.1

P1.0

Mnemonic: P1

Address: 90h

P1.7-0: General-purpose input/output port. Port-read instructions read the port pins, while read-modify-write instructions read the port latch.

#### Port 4.1 Low Address Comparator

Publication Release Date: March 2, 2009 Revision A12

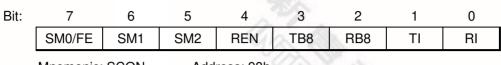

### **Serial Port Control**

Mnemonic: SCON

Address: 98h

|       | BIT  | NAME   |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                          |                    | FUN      | ICTION                                                                                                                             |  |  |  |

|-------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|       | 7    | SM0/FE | SFR deter<br>below. Wh                                                                                                                         | Serial port, Mode 0 (SM0) bit or Framing-Error (FE) Flag: The SMOD0 bit in PCON<br>FR determines whether this bit acts as SM0 or as FE. SM0 is described with SMI1<br>elow. When used as FE, this bit indicates whether the stop bit is invalid (FE=1) or<br>alid (FE=0). This bit must be manually cleared by software. |                    |          |                                                                                                                                    |  |  |  |

|       |      |        | Serial port                                                                                                                                    | Mode                                                                                                                                                                                                                                                                                                                     | e 1 (SM1) bit:     |          | Sa G                                                                                                                               |  |  |  |

|       |      |        | Mode: SM0                                                                                                                                      | SM1                                                                                                                                                                                                                                                                                                                      | Description        | Length   | Baud rate                                                                                                                          |  |  |  |

|       | 6    | SM1    | 0 0                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                        | Synchronous        | 8        | 6(6T mode)/12(12T mode) T <sub>clk</sub>                                                                                           |  |  |  |

|       | 0    | SIVIT  | 1 0                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                        | Asynchronous       | 10       | Variable                                                                                                                           |  |  |  |

|       |      |        | 2 1                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                        | Asynchronous       | 11       | 32/16(6T mode) or 64/32(12T mode) T <sub>clk</sub>                                                                                 |  |  |  |

|       |      |        | 3 1                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                        | Asynchronous       | 11       | Variable                                                                                                                           |  |  |  |

|       |      |        | Multi-proce                                                                                                                                    | essor                                                                                                                                                                                                                                                                                                                    | communication.     |          | <u>്</u>                                                                                                                           |  |  |  |

|       | 5    | SM2    |                                                                                                                                                | (Modes 2 and 3) Set this bit to enable the multi-processor communication feature. With this feature, RI is not activated if the ninth data bit received (RB8) is 0.                                                                                                                                                      |                    |          |                                                                                                                                    |  |  |  |

|       | 5    |        | (Mode 1) 5                                                                                                                                     | Set this                                                                                                                                                                                                                                                                                                                 | s bit to 1 to keep | RI de-a  | ctivated if a valid stop bit is not received.                                                                                      |  |  |  |

|       |      |        | (Mode 0) SM2 controls the serial port clock. If clear, the serial port runs at 1/12 the oscillator. This is compatible with the standard 8052. |                                                                                                                                                                                                                                                                                                                          |                    |          |                                                                                                                                    |  |  |  |

|       |      |        | Receive enable:                                                                                                                                |                                                                                                                                                                                                                                                                                                                          |                    |          |                                                                                                                                    |  |  |  |

|       | 4    | REN    | 1 = Serial reception is enabled                                                                                                                |                                                                                                                                                                                                                                                                                                                          |                    |          |                                                                                                                                    |  |  |  |

| 100   |      |        | 0 = Serial reception is disabled                                                                                                               |                                                                                                                                                                                                                                                                                                                          |                    |          |                                                                                                                                    |  |  |  |

| an I  | 3    | TB8    | (Modes 2 and 3) This is the ninth bit to be transmitted. This bit is set and cleared by software as desired.                                   |                                                                                                                                                                                                                                                                                                                          |                    |          |                                                                                                                                    |  |  |  |

| 1 CON | SP . |        | (Modes 2 and 3) This is the ninth data bit that was received.                                                                                  |                                                                                                                                                                                                                                                                                                                          |                    |          |                                                                                                                                    |  |  |  |

| - (S) | 2    | RB8    | (Mode 1) I                                                                                                                                     | SM2                                                                                                                                                                                                                                                                                                                      | is 0, RB8 is the   | stop bit | that was received.                                                                                                                 |  |  |  |

| X     | 6    | X      | (Mode 0) N                                                                                                                                     | lo fun                                                                                                                                                                                                                                                                                                                   | ction.             |          |                                                                                                                                    |  |  |  |

|       | 1    | τ      | mode 0 or                                                                                                                                      | at the                                                                                                                                                                                                                                                                                                                   |                    | e stop b | y the hardware at the end of the eighth bit in<br>it in modes 1 – 3 during serial transmission.                                    |  |  |  |

|       | 0    | RI     | mode 0 o                                                                                                                                       | r half                                                                                                                                                                                                                                                                                                                   | way through the    | e stop k | $\gamma$ the hardware at the end of the eighth bit in bit in modes 1 – 3 during serial reception. can be cleared only by software. |  |  |  |

## nuvoTon

1 = switch to DPTR1

## nuvoTon

|   | BIT | NAME | FUNCTION                                                                                                                     |

|---|-----|------|------------------------------------------------------------------------------------------------------------------------------|

| 2 | 7~0 |      | The SADDR should be programmed to the given or broadcast address for serial port to which the slave processor is designated. |

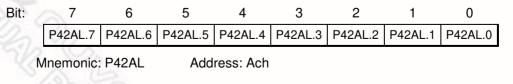

### Port 4.2 Low Address Comparator

## nuvoTon

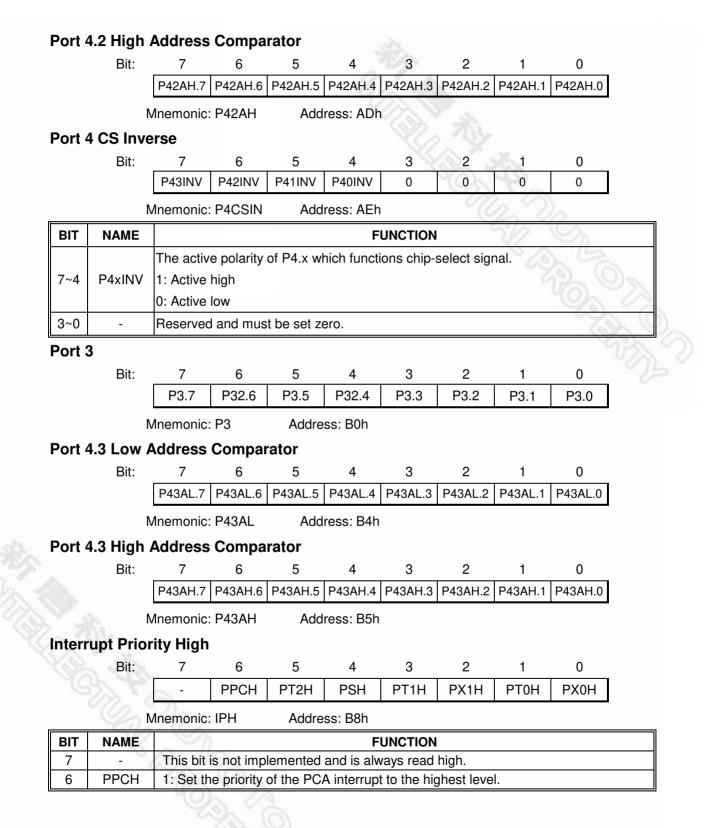

| 5 | PT2H | 1: Set the priority of the Timer 2 interrupt to the highest level.                |

|---|------|-----------------------------------------------------------------------------------|

| 4 | PSH  | 1: Set the priority of the Serial Port interrupt to the highest level.            |

| 3 | PT1H | 1: Set the priority of the Timer 1 interrupt to the highest level.                |

| 2 | PX1H | 1: Set the priority of external interrupt INT1 to the highest level.              |

| 1 | PT0H | 1: Set the priority of the Timer 0 interrupt to the highest level.                |

| 0 | PX0H | 1: Set the priority of external interrupt $\overline{INT0}$ to the highest level. |

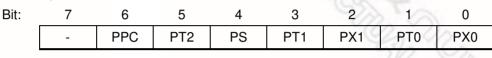

### **Interrupt Priority**

Mnemonic: IP

Address: B8h

| BIT | NAME | FUNCTION                                                           |

|-----|------|--------------------------------------------------------------------|

| 7   | -    | This bit is not implemented and is always read high.               |

| 6   | PPC  | 1: Set the priority of the PCA interrupt one level higher.         |

| 5   | PT2  | 1: Set the priority of the Timer 2 interrupt one level higher.     |

| 4   | PS   | 1: Set the priority of the Serial Port interrupt one level higher. |

| 3   | PT1  | 1: Set the priority of the Timer 1 interrupt one level higher.     |

| 2   | PX1  | 1: Set the priority of external interrupt INT1 one level higher.   |

| 1   | PT0  | 1: Set the priority of the Timer 0 interrupt one level higher.     |

| 0   | PX0  | 1: Set the priority of external interrupt INTO one level higher.   |

### **Slave Address Mask Enable**

Mnemonic: SADEN

Address: B9h

| BIT | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7~0 | SADEN | This register enables the Automatic Address Recognition feature of the serial port.<br>When a bit in SADEN is set to 1, the same bit in SADDR is compared to the<br>incoming serial data. When a bit in SADEN is set to 0, the same bit in SADDR is a<br>"don't care" value in the comparison. The serial port interrupt occurs only if all the<br>SADDR bits where SADEN is set to 1 match the incoming serial data. |

### **On-Chip Programming Control**

| Bit: | 2 700            | 6 | 5 | 4 | 3 | 2 | 1       | 0       |

|------|------------------|---|---|---|---|---|---------|---------|

|      | SWRST/<br>REBOOT | 2 | - | - | - | 0 | FBOOTSL | FPROGEN |

Mnemonic: CHPCON Address: BFh

Publication Release Date: March 2, 2009 Revision A12

| BIT   | NAME                    | FUNCTION                                                                                                                                                                                                                                                                                                                                                  |

|-------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | W: SWRESET<br>R: REBOOT | When FBOOTSL and FPROGEN are set to 1, set this bit to 1 to force the microcontroller to reset to the initial condition, just like power-on reset. This action re-boots the microcontroller and starts normal operation.<br>Read this bit to determine whether or not a hardware reboot is in progress.                                                   |

| 6 – 2 | -                       | Reserved                                                                                                                                                                                                                                                                                                                                                  |

| 1     | FBOOTSL                 | <ul> <li>Program Location Selection. This bit should be set before entering ISP mode.</li> <li>0: The Loader Program is in the 64-KB AP Flash EPROM. The 4-KB LD Flash EPROM is the destination for re-programming.</li> <li>1: The Loader Program is in the 4-KB memory bank. The 64-KB AP Flash EPROM is the destination for re-programming.</li> </ul> |

| 0     | FPROGEN                 | <ul> <li>FLASH EPROM Programming Enable.</li> <li>1: Enable in-system programming mode. In this mode, erase, program and read operations are achieved during device enters idle state.</li> <li>0: Disable in-system programming mode. The on-chip flash memory is read-only.</li> </ul>                                                                  |

CHPCON has an unrestricted read access, however, the write access is protected by timed-access protection. See the section of timed-access protection for more information.

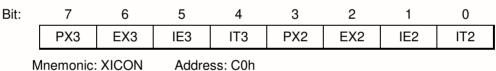

### **External Interrupt Control**

**Mnemonic: XICON**

| BIT | NAME | FUNCTION                                                                                                                     |

|-----|------|------------------------------------------------------------------------------------------------------------------------------|

| 7   | PX3  | 1: Set the priority of external interrupt $\overline{INT3}$ one level higher.                                                |

| 6   | EX3  | 1: Enable external interrupt INT3.                                                                                           |

| 5   | IE3  | Interrupt INT3 flag. This bit is set and cleared automatically by the hardware when the interrupt is detected and processed. |

| 4   | IT3  | 1: INT3 is falling-edge triggered                                                                                            |

|     | 115  | 0: INT3 is low-level triggered                                                                                               |

| 3   | PX2  | 1: Set the priority of external interrupt $\overline{INT2}$ one level higher.                                                |

| 2   | EX2  | 1: Enable external interrupt INT2.                                                                                           |

| 1   | IE2  | Interrupt INT2 flag. This bit is set and cleared automatically by the hardware when the interrupt is detected and processed. |

| 0   | IT2  | 1: INT2 is falling-edge triggered                                                                                            |

| 0   | 5    | 0: INT2 is low-level triggered                                                                                               |

## nuvoTon

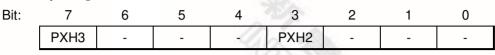

### **External Interrupt High Control**

Mnemonic: XICONH Address: C1h

| BIT   | NAME | FUNCTION                                                                          |

|-------|------|-----------------------------------------------------------------------------------|

| 7     | PXH3 | 1: Set the priority of external interrupt $\overline{INT3}$ to the highest level. |

| 6 - 4 | -    | Reserved                                                                          |

| 3     | PXH2 | 1: Set the priority of external interrupt INT2 to the highest level.              |

| 2 - 0 | -    | Reserved                                                                          |

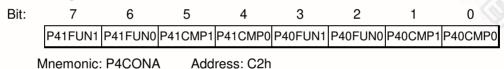

### Port 4 Control Register A

| BIT  | NAME    | FUNCTION                                                            |

|------|---------|---------------------------------------------------------------------|

| 76   | P41FUN1 | P4.1 function control bits, similar to P43FUN1 and P43FUN0 below.   |

| 7, 6 | P41FUN0 | F4.1 function control bits, similar to F43FONT and F43FOND below.   |

| 5, 4 | P41CMP1 | P4.1 address-comparator length control bits, similar to P43CMP1 and |

| 5,4  | P41CMP0 | P43CMP0 below.                                                      |

| 2.0  | P40FUN1 | D4.0 function control bits, similar to D42ELIN1 and D42ELIN0 below  |

| 3, 2 | P40FUN0 | P4.0 function control bits, similar to P43FUN1 and P43FUN0 below.   |

| 1.0  | P40CMP1 | P4.0 address-comparator length control bits, similar to P43CMP1 and |

| 1,0  | P40CMP0 | P43CMP0 below.                                                      |

### Port 4 Control Register B

| Bit: | 7       | 6        | 5       | 4          | 3       | 2       | 1       | 0       |

|------|---------|----------|---------|------------|---------|---------|---------|---------|

|      | P43FUN1 | P43FUN0  | P43CMP1 | P43CMP0    | P42FUN1 | P42FUN0 | P42CMP1 | P42CMP0 |

|      | Mnemoni | c: P4CON | B Add   | lress: C3h |         |         |         |         |

| BIT  | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                          |

|------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 6 | P43FUN1<br>P43FUN0 | <ul> <li>00: Mode 0. P4.3 is a general purpose I/O port, like Port 1.</li> <li>01: Mode 1. P4.3 is a read-strobe signal for chip-select purposes. The address range depends on SFR P43AH, P43AL, P43CMP1 and P43CMP0.</li> <li>10: Mode 2. P4.3 is a write-strobe signal for chip-select purposes. The address range depends on SFR P43AH, P43AL, P43CMP1 and P43CMP0.</li> </ul> |

|      |                    | P43CMP0.<br>11: Mode 3. P4.3 is a read/write-strobe signal for chip-select purposes. The<br>address range depends on SFR P43AH, P43AL, P43CMP1, and<br>P43CMP0.                                                                                                                                                                                                                   |

| 5, 4 | P43CMP1<br>P43CMP0 | <ul> <li>Chip-select signal address comparison:</li> <li>00: Compare the full 16-bit address with P43AH and P43AL.</li> <li>01: Compare the 15 MSB of the 16-bit address with P43AH and P43AL.</li> <li>10: Compare the 14 MSB of the 16-bit address with P43AH and P43AL.</li> <li>11: Compare the 8 MSB of the 16-bit address with P43AH.</li> </ul>                            |

| 3, 2 | P42FUN1<br>P42FUN0 | P4.2 function control bits, similar to P43FUN1 and P43FUN0 above.                                                                                                                                                                                                                                                                                                                 |

| 1, 0 | P42CMP1<br>P42CMP0 | P4.2 address-comparator length control bits, similar to P43CMP1 and P43CMP0 above.                                                                                                                                                                                                                                                                                                |

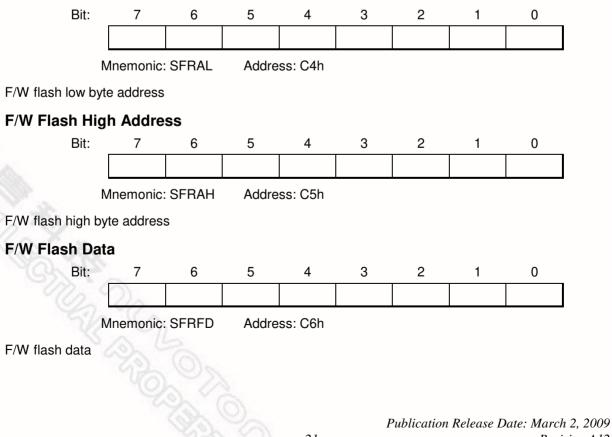

### F/W Flash Low Address

## nuvoTon

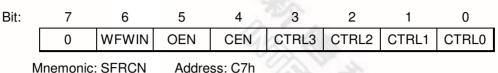

### F/W Flash Control

Mnemonic: SFRCN

| BIT   | NAME      | FUNCTION                                                                                                                 |

|-------|-----------|--------------------------------------------------------------------------------------------------------------------------|

| 7     | -         | Reserved                                                                                                                 |

|       |           | On-chip Flash EPROM bank select for in-system programming. This bit should be defined by the loader program in ISP mode. |

| 6     | WFWIN     | 0: 64-KB Flash EPROM is the destination for re-programming.                                                              |

|       |           | 1: 4-KB Flash EPROM is the destination for re-programming.                                                               |

| 5     | OEN       | Flash EPROM output enable.                                                                                               |

| 4     | CEN       | Flash EPROM chip enable.                                                                                                 |

| 3 - 0 | CTRL[3:0] | Flash control signals                                                                                                    |

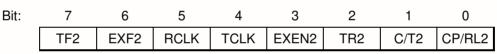

### **Timer 2 Control**

Mnemonic: T2CON Address: C8h

|       | BIT        | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                |

|-------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 7          | TF2  | Timer 2 overflow flag: If RCLK and TCLK are 0, this bit is set when Timer 2 overflows or when the count is equal to the value in the capture register in down-count mode. This bit can also be set by software, and it can only be cleared by software.                                                                 |

| and a | 6          | EXF2 | Timer 2 External Flag: When Timer 2 is in either capture or auto-reload mode<br>and DCEN is 0, a negative transition on the T2EX pin (P1.1) and EXEN2=1 sets<br>this flag. This flag can also be set by software. Once set, this flag generates a<br>Timer-2 interrupt, if enabled, and it must be cleared by software. |

| - R   | 1          | DOLK | Receive Clock Flag: Set this bit to force Timer 2 into baud-rate generator mode when receiving data on the serial port in modes 1 or 3.                                                                                                                                                                                 |

| 1     | 5          | RCLK | 1 = Timer 2 overflow is the time base.                                                                                                                                                                                                                                                                                  |

|       | $\sim Q^2$ | 4    | 0 = Timer 1 overflow is the time base.                                                                                                                                                                                                                                                                                  |

|       | 0          | Ch'  | Transmit clock Flag: Set this bit to force Timer 2 into baud-rate generator mode when transmitting data on the serial port in modes 1 or 3.                                                                                                                                                                             |

|       | 4          | TCLK | 1 = Timer 2 overflow is the time base.                                                                                                                                                                                                                                                                                  |

|       |            | ~6   | 0 = Timer 1 overflow is the time base.                                                                                                                                                                                                                                                                                  |

Continued

| BIT | NAME   | FUNCTION                                                                                                                                                                                         |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | EXEN2  | Timer 2 External Enable: If Timer 2 is not in baud-rate generator mode (see RCLK and TCLK above), set this bit to allow a negative transition on the T2EX pin to capture/reload Timer 2 counter. |

|     |        | Timer 2 Run Control:                                                                                                                                                                             |

| 2   | TR2    | 1 = Enable Timer 2.                                                                                                                                                                              |

|     |        | 0 = Disable Timer 2, which preserves the current value in TH2 and TL2.                                                                                                                           |

|     |        | Counter/Timer select:                                                                                                                                                                            |

| 1   | C/T2   | 0 = Timer 2 operates as a timer at a speed controlled by T2M (CKCON.5)                                                                                                                           |

|     |        | 1 = Timer 2 counts negative edges on the T2EX pin.                                                                                                                                               |

|     |        | Capture/Reload Select: If EXEN2 is set to 1, this bit determines whether the capture or auto-reload function is activated.                                                                       |

| 0   | CP/RL2 | 0 = auto-reload when timer 2 overflows or a falling edge is detected on T2EX                                                                                                                     |

| 0   | GP/RL2 | 1 = capture each falling edge is detected on T2EX                                                                                                                                                |

|     |        | If either RCLK or TCLK is set, this bit has no function, as Timer 2 runs in auto-<br>reload mode.                                                                                                |

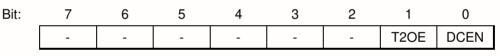

### **Timer 2 Mode**

Mnemonic: T2MOD Address: C9h

| BIT | NAME | FUNCTION                                                                                                                      |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------|

| 7~2 | -    | Reserved                                                                                                                      |

| 1   | T2OE | Timer 2 Output Enable. This bit enables/disables the Timer 2 clock-out function.                                              |

| 0   |      | Down Count Enable: Setting DCEN to 1 allows T2EX pin to control the direction that Timer 2 counts in 16-bit auto-reload mode. |

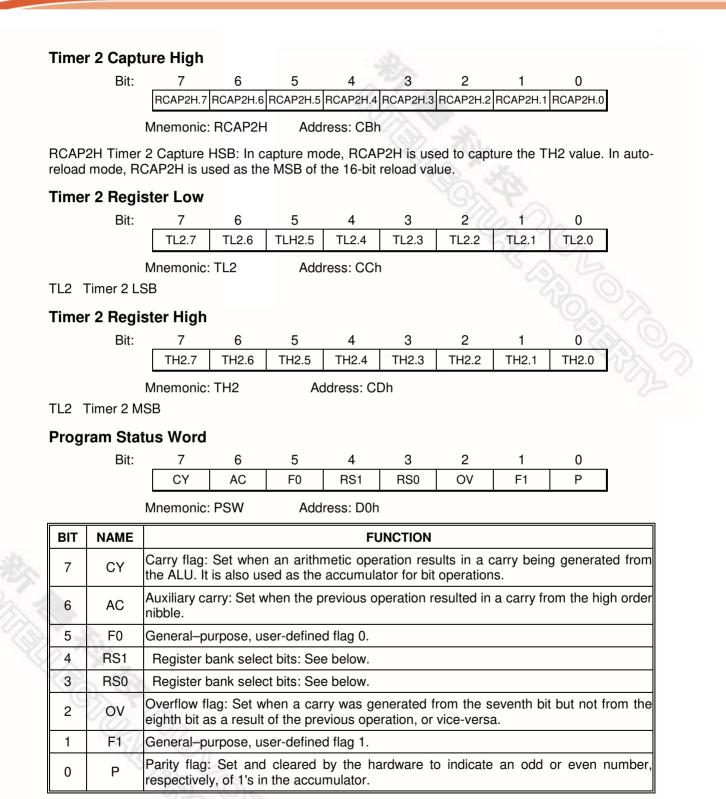

### Timer 2 Capture Low Bit: 7

| : | 7        | 6        | 5        | 4         | 3        | 2        | 1        | 0        |

|---|----------|----------|----------|-----------|----------|----------|----------|----------|

|   | RCAP2L.7 | RCAP2L.6 | RCAP2L.5 | RCAP2L.4  | RCAP2L.3 | RCAP2L.2 | RCAP2L.1 | RCAP2L.0 |

| N | Inemonic | RCAP2L   | Add      | ress: CAh | ı        |          |          |          |

RCAP2L Timer 2 Capture LSB: In capture mode, RCAP2L is used to capture the TL2 value. In autoreload mode, RCAP2L is used as the LSB of the 16-bit reload value.

## nuvoTon