# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **CompactFlash<sup>TM</sup> Disk INDUSTRIAL GRADE** *W7CFxxxA-H Series*

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO WINTEC INDUSTRIES PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED.

ALL INFORMATION IN THIS DOCUMENT IS PROVIDED ON AN "AS-IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

• Please contact your nearest Wintec representative for the latest updates or additional product information.

## **Revision History**

| Revision | Month    | Year    | History                                                     |

|----------|----------|---------|-------------------------------------------------------------|

| 2.0      | February | 2006    | -ROHS Spec Release                                          |

|          |          |         | -Add Title Page & Revision History                          |

| 2.1      | June     | 2006    | -Update Table 28: Identify Drive Information                |

| 2.1      | June     | 2000    | -Update Table 37: Attribute Memory Read AC Characteristics  |

|          |          |         | -Update Table 38: Attribute Memory Write AC Characteristics |

|          |          |         | -Update Table 28: Identify Drive Information                |

|          |          |         | -Update Tables 37~42                                        |

|          |          |         | -Update Table 43: True IDE Mode I/O Read/Write Timing       |

| 2.2      | June     | 2006    | -Update Table 44: True IDE DMA Mode I/O Read/Write Timing   |

|          |          |         | -Update Figures 14~19                                       |

|          |          |         | -Update Figure 20: True IDE Mode I/O Timing Diagram         |

|          |          |         | -Update Figure 21: True IDE DMA Mode I/O Timing Diagram     |

|          | December | er 2006 | -Update Table 37 Attribute Memory Read Timing               |

| 2.3      |          |         | -Update Table 38 Attribute Memory Write Timing              |

| 2.5      |          |         | -Update Table 39 I/O Access Read Timing                     |

|          |          |         | -Update Table 41 Common Memory Access Read Timing           |

| 2.4      | Mari     | 2007    | -Update DMA pins' description, Pin 43 DMARQ and 44 DMACK    |

| 2.4      | May      | 2007    | -Update Table 7 Layout                                      |

| 2.5      | March    | 2008    | -Update new naming scheme for the CF card                   |

| 2.6      | May      | 2008    | -Update Table 48 Ordering Information and naming guide      |

| 2.7      | October  | 2008    | -Add section 4.1 Labeling and Marking                       |

| 2.8      | November | 2008    | -Add 16GB capacity to the specification                     |

| 2.0      | Lanuami  | 2000    | -Update table 48 with 8GB Real Capacity                     |

| 2.9      | January  | 2009    | -Update table 48 key with firmware options                  |

| 2.10     | January  | 2010    | -Update the ordering information with firmware options      |

## CompactFlash<sup>™</sup> Card INDUSTRIAL GRADE

WxCFxxxA-H Series ROHS 6/6 Compliant

#### Features

#### GENERAL

- Type I Density up to 16-GB

- 32-bit RISC/DSP Controller

- Solid State Data Storage

- Dual 3.3V / 5V Interface

- Industry Standard Compatibility

- Specialized for High-Reliability

- ROHS 6/6 Compliant

#### PERFORMANCE

- True IDE Mode Capable

- PIO Mode 0-4

- DMA Mode 0-2 (Optional)

- High Performance 16.7 MB/s Burst

- Low Power Consumption

- ATA-2 Compliant (w/DMA Enable)

#### RELIABILITY

- > 2,000,000 Program/Erase Cycles

- Industrial Wear Leveling

- Includes Static Block Management

- Spares & Bad Block Management

- On-Board ECC

- Corrects up to 6-bytes/Sector

- High Environmental Tolerance

- 10-Year Data Retention

- Unlimited Reads

#### COMPATIBILITY

- CFA Spec, Revision 4.1, Feb 2007

- PCMCIA PC Card Standard, 7.0, February 1999

- PCMCIA PC Card ATA Spec, 7.0, Feb 1999

#### DESCRIPTION

The Wintec Industries W7CFxxxA-H series of ROHS Compliant Industrial Grade CompactFlash<sup>TM</sup> Memory Cards are constructed with Samsung NAND-type single-level-cell (SLC) flash memory devices paired to a powerful 32-bit RISC/DSP-based system controller for virtual-to-physical address mapping and other flash management functions.

Wintee Industrial CompactFlash<sup>TM</sup> Cards employ a variety of sophisticated error checking and flash management utilities allowing for maximum levels of data reliability and card endurance. Patented wear-leveling methods ensure even wear of flash blocks across the entire card capacity. Background operations track erase counts, prioritize new writes to blocks with lower wear, and relocate static data to blocks with higher wear. Bad-block Management routines replace worn blocks with spare blocks reserved by the controller on card initialization. Reed-Solomon based ECC algorithms capable of detecting and correcting up to 6 bytes per 512 byte sector are implemented on the fly without performance degradation to ensure data reliability through user data transfers and background wear-leveling operations. Additional information regarding the specifics of wear leveling, ECC methods, and application-specific card life calculations are available upon request and under NDA.

Industrial grade reliability, industry standard compatibility, and the ability to emulate IDE hard disk drives make Wintec CompactFlash<sup>TM</sup> Cards ideal for industrial, military, and other high endurance applications.

Wintec Type I CompactFlash<sup>TM</sup> Card

#### **Configuration Options**

- Industrial Temperature

- Fixed / Removable Disk

- DMA Mode Enable

- Data Programming Service

- Custom Labeling

- NOTE:

1. See Section 5.0 for Configuration & Ordering Guide

## **Table of Contents**

| 1.0 | Genera  | al Product Specifications                          | 3        |

|-----|---------|----------------------------------------------------|----------|

| 2.0 | Card H  | Function Explanation                               | 12       |

|     | 2.1     | Attribute Access                                   | 13       |

|     | 2.2     | Task File Register Access                          | 13       |

|     |         | 2.2.1 I/O Address Map                              | 14       |

|     |         | 2.2.2 Memory Access Map                            | 15       |

|     | • •     | 2.2.3 True IDE Mode                                | 16       |

|     | 2.3     | Configuration Register                             | 16       |

|     |         | 2.3.1 Configuration Option Register                | 17       |

|     |         | 2.3.2 Configuration and Status Register            | 17       |

|     |         | 2.3.3 Pin Replacement Register                     | 18       |

|     | 2.4     | 2.3.4 Socket and Copy Register                     | 18       |

|     | 2.4     | Task File Register Specification2.4.1Data Register | 20       |

|     |         | 2.4.1Data Register2.4.2Error Register              | 20       |

|     |         | 2.4.2 Entri Register<br>2.4.3 Feature Register     | 20<br>20 |

|     |         | 2.4.4 Sector Count Register                        | 20<br>20 |

|     |         | 2.4.5 Sector Number Register                       | 20<br>20 |

|     |         | 2.4.6 Cylinder Low Register                        | 20<br>20 |

|     |         | 2.4.7 Cylinder High Register                       | 20 21    |

|     |         | 2.4.8 Drive Head Register                          | 21       |

|     |         | 2.4.9 Status Register                              | 21       |

|     |         | 2.4.10 Alternate Status Register                   | 22       |

|     |         | 2.4.11 Command Register                            | 22       |

|     |         | 2.4.12 Device Control Register                     | 23       |

|     |         | 2.4.13 Drive Address Register                      | 23       |

|     | 2.5     | ATA Command Specification                          | 24       |

|     |         | 2.5.1 ATA Command Set Description                  | 25       |

|     |         | 2.5.2 Sector Transfer Protocol                     | 26       |

| 3.0 | Electri | ical Specification                                 | 29       |

|     | 3.1     | General                                            | 29       |

|     | 3.2     | DC Characteristics                                 | 32       |

|     |         | 3.2.1 Current Waveform                             | 32       |

|     | 3.3     | AC Characteristics                                 | 34       |

|     |         | 3.3.1 General                                      | 34       |

|     | 3.4     | Reset Characteristics                              | 45       |

|     | 3.5     | User Notes                                         | 46       |

| 4.0 | Physic  | al Specifications                                  | 47       |

| 5.0 | Produc  | ct Guide & Ordering Information                    | 48       |

## **1.0 General Product Specification**

For all the following specifications, values are defined at ambient temperature and nominal supply voltage unless otherwise stated.

#### **Table 1: Performance Specifications**

| Parameter                                | Spec                     |           |

|------------------------------------------|--------------------------|-----------|

| Burst Transfer Rate To/From Host         |                          | 16.6 MB/s |

| <b>Burst Transfer Rate To/From Flash</b> |                          | 20.0 MB/s |

| Sustained Read (Typical)                 |                          | 8.0 MB/s  |

| Sustained Write (Typical)                |                          | 6.0 MB/s  |

| Active-to-Sleep Delay                    | Programmable             |           |

| Command-to-DRQ (Max.)                    |                          | 50.0 ms   |

|                                          | Sleep-to-Write (Max.)    | 2.5 ms    |

| Startun Timos                            | Sleep-to-Read (Max.)     | 20 ms     |

| Startup Times                            | Reset-to-Ready (Typical) | 50.0 ms   |

|                                          | Reset-to-Ready (Max.)    | 400.0 ms  |

NOTE:

1. All performance figures are based on testing done in True IDE PIO Mode 4.

#### Table 2: Card Endurance

| Parameter            | Spec               |

|----------------------|--------------------|

| Program/Erase Cycles | > 2,000,000 Cycles |

| Read Cycles          | Unlimited          |

| Data Retention       | 10 Years (Min.)    |

| MTBF                 | > 4,000,000 Hours  |

#### **Table 3: Card Data Reliability**

| Parameter              | Spec                               |

|------------------------|------------------------------------|

| Non-Recoverable Errors | < 1 in 10 <sup>14</sup> Bytes Read |

| Erroneous Correction   | < 1 in 10 <sup>20</sup> Bytes Read |

| ECC Correctability     | 6 Bytes/Sector                     |

| ECC Detectability      | 6 Bytes/Sector                     |

#### **Table 4: Environmental Specifications**

| Parameters  |                  | Operating         | Non-Operating    |  |

|-------------|------------------|-------------------|------------------|--|

| Tomporatura | Standard Temp.   | 0°C to 70°C       | -55°C to 95°C    |  |

| Temperature | Industrial Temp. | -40°C to 85°C     | -55°C to 95°C    |  |

| II!         |                  | 8% to 95%         | 8% to 95%        |  |

| Humidity    |                  | (Non-Condensing)  | (Non-Condensing) |  |

| Vibration   |                  | 16.3 G rms        |                  |  |

| Altitude    |                  | 80,000 ft. (Max.) | N/A              |  |

| Shock       |                  | 2,000 G (Max.)    | IN/A             |  |

| Acoustic    |                  | 0 db              |                  |  |

#### **Table 5: Power Consumption**

| Capacity | Sleep (Max) | Read/Write<br>(Typical) | Read/Write<br>(Max) |

|----------|-------------|-------------------------|---------------------|

| 32MB     | 300 µ       | 40 mA                   | 50 mA               |

| 64MB     | 300 µ       | 40 mA                   | 50 mA               |

| 128MB    | 300 µ       | 40 mA                   | 50 mA               |

| 256MB    | 300 µ       | 40 mA                   | 50 mA               |

| 512MB    | 450 μ       | 45.02mA                 | 60.10mA             |

| 1-GB     | 450 μ       | 45.02mA                 | 60.10mA             |

| 2-GB     | 600 µ       | 45.06mA                 | 60.30mA             |

| 4-GB     | 600 µ       | 45.06mA                 | 60.30mA             |

| 8-GB     | 600 µ       | 45.06mA                 | 60.30mA             |

NOTE:

1. Input voltage 3.3V ( $\pm 5\%)$  or 5V ( $\pm 10\%)$  with a maximum ripple of 100mV peak-to-peak.

2. All values listed are at 25°C and nominal supply voltage.

3. Stated figures are based on primary configurations and may vary as larger density component NAND flashes are released.

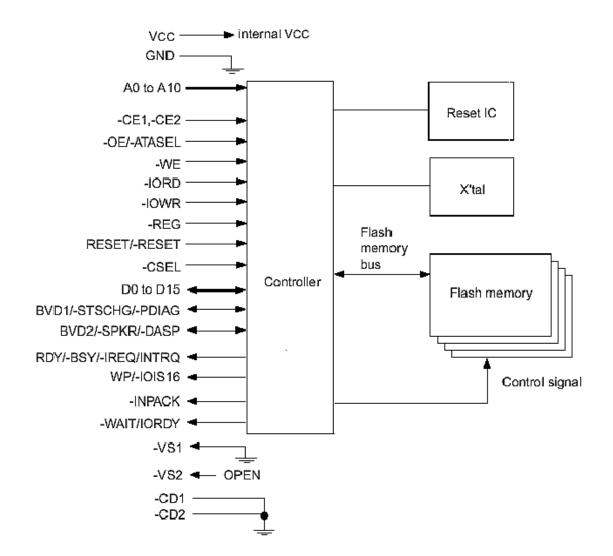

**Figure 1: Card Block Diagram**

NOTE: -CE1, -CE2, -OE, -WE -IORD, -IOWR, -REG, -RESET, -CSEL, -PDIAG, -DASP pins are pulled up in card. -CE1, -CE2, -OE, -WE, -IORD, -IOWR, -REG pins are Schmitt trigger type input buffer.

#### **Table 6: Card Pin Assignment**

| PC Ca | rd Memory M       |            | PC Card I/O Mode |                   |            |     | True IDE Mod      | le     |

|-------|-------------------|------------|------------------|-------------------|------------|-----|-------------------|--------|

| Pin   | Signal            | Туре       | Pin              | Signal            | Туре       | Pin | Signal            | Туре   |

| 1     | GND               | Ground     | 1                | GND               | Ground     | 1   | GND               | Ground |

| 2     | D03               | I/O        | 2                | D03               | I/O        | 2   | D03               | I/O    |

| 3     | D03               | I/O<br>I/O | 3                | D03               | I/O<br>I/O | 3   | D04               | I/O    |

| 4     | D01               | I/O<br>I/O | 4                | D01               | I/O<br>I/O | 4   | D05               | I/O    |

| 5     | D05               | I/O<br>I/O | 5                | D05               | I/O        | 5   | D05               | I/O    |

| 6     | D07               | I/O        | 6                | D07               | I/O        | 6   | D07               | I/O    |

| 7     | -CE1              | I          | 7                | -CE1              | I          | 7   | -CS0              | I      |

| 8     | A10               | I          | 8                | A10               | I          | 8   | A10 <sup>2</sup>  | I      |

| 9     | -OE               | I          | 9                | -OE               | I          | 9   | -ATA SEL          | I      |

| 10    | A09               | I          | 10               | A09               | Ī          | 10  | A09 <sup>2</sup>  | Ī      |

| 11    | A08               | I          | 11               | A08               | I          | 11  | A08 <sup>2</sup>  | I      |

| 12    | A07               | I          | 12               | A07               | I          | 12  | A07 <sup>2</sup>  | I      |

| 13    | VCC               | Power      | 13               | VCC               | Power      | 13  | VCC               | Power  |

| 14    | A06               | I          | 14               | A06               | I          | 14  | A06 <sup>2</sup>  | I      |

| 15    | A05               | I          | 15               | A05               | I          | 15  | A05 <sup>2</sup>  | I      |

| 16    | A04               | I          | 16               | A04               | I          | 16  | A04 <sup>2</sup>  | I      |

| 17    | A03               | I          | 17               | A03               | I          | 17  | A03 <sup>2</sup>  | I      |

| 18    | A02               | Ι          | 18               | A02               | Ι          | 18  | A02               | Ι      |

| 19    | A01               | I          | 19               | A01               | I          | 19  | A01               | Ī      |

| 20    | A00               | I          | 20               | A00               | I          | 20  | A00               | I      |

| 21    | D00               | I/O        | 21               | D00               | I/O        | 21  | D00               | I/O    |

| 22    | D01               | I/O        | 22               | D01               | I/O        | 22  | D01               | I/O    |

| 23    | D02               | I/O        | 23               | D02               | I/O        | 23  | D02               | I/O    |

| 24    | WP                | 0          | 24               | -IOIS16           | 0          | 24  | -IOCS16           | 0      |

| 25    | -CD2              | 0          | 25               | -CD2              | 0          | 25  | -CD2              | 0      |

| 26    | -CD1              | 0          | 26               | -CD1              | 0          | 26  | -CD1              | 0      |

| 27    | D11 <sup>1</sup>  | I/O        | 27               | D11 <sup>1</sup>  | I/O        | 27  | D11 <sup>1</sup>  | I/O    |

| 28    | D12 <sup>1</sup>  | I/O        | 28               | D12 <sup>1</sup>  | I/O        | 28  | D12 <sup>1</sup>  | I/O    |

| 29    | D13 <sup>1</sup>  | I/O        | 29               | D13 <sup>1</sup>  | I/O        | 29  | D13 <sup>1</sup>  | I/O    |

| 30    | D14 <sup>1</sup>  | I/O        | 30               | D14 <sup>1</sup>  | I/O        | 30  | D14 <sup>1</sup>  | I/O    |

| 31    | D15 <sup>1</sup>  | I/O        | 31               | D15 <sup>1</sup>  | I/O        | 31  | D15 <sup>1</sup>  | I/O    |

| 32    | -CE2 <sup>1</sup> | Ι          | 32               | -CE2 <sup>1</sup> | Ι          | 32  | -CS1 <sup>1</sup> | Ι      |

| 33    | -VS1              | 0          | 33               | -VS1              | 0          | 33  | -VS1              | 0      |

| 34    | -IORD             | Ι          | 34               | -IORD             | Ι          | 34  | -IORD             | Ι      |

| 35    | -IOWR             | Ι          | 35               | -IOWR             | Ι          | 35  | -IOWR             | Ι      |

| 36    | -WE               | Ι          | 36               | -WE               | Ι          | 36  | -WE <sup>3</sup>  | Ι      |

| 37    | RDY/BSY           | 0          | 37               | IREQ              | 0          | 37  | INTRQ             | 0      |

| 38    | VCC               | Power      | 38               | VCC               | Power      | 38  | VCC               | Power  |

| 39    | -CSEL             | Ι          | 39               | -CSEL             | Ι          | 39  | -CSEL             | I      |

| 40    | -VS2              | 0          | 40               | -VS2              | 0          | 40  | -VS2              | 0      |

| 41    | RESET             | Ι          | 41               | RESET             | Ι          | 41  | RESET             | Ι      |

| 42    | -WAIT             | 0          | 42               | -WAIT             | 0          | 42  | IORDY             | 0      |

| 43    | -INPACK           | 0          | 43               | -INPACK           | 0          | 43  | DMARQ             | 0      |

| 44    | -REG              | Ι          | 44               | -REG              | Ι          | 44  | -DMACK            | I      |

| 45    | BVD2              | I/O        | 45               | -SPKR             | I/O        | 45  | -DASP             | I/O    |

| 46    | BVD1              | I/O        | 46               | -STSCHG           | I/O        | 46  | -PDIAG            | I/O    |

| 47    | D08 <sup>1</sup>  | I/O        | 47               | D08 <sup>1</sup>  | I/O        | 47  | D08 <sup>1</sup>  | I/O    |

| 48    | D09 <sup>1</sup>  | I/O        | 48               | D09 <sup>1</sup>  | I/O        | 48  | D09 <sup>1</sup>  | I/O    |

| 49    | D10 <sup>1</sup>  | I/O        | 49               | D10 <sup>1</sup>  | I/O        | 49  | D10 <sup>1</sup>  | I/O    |

| 50    | GND               | Ground     | 50               | GND               | Ground     | 50  | GND               | Ground |

NOTE:

These signals are required only for 16-bit access and not required when installed in 8-bit systems. For lowest power dissipation, leave these signals open. Should be grounded by the host. Should be tied to VCC by the host.

1. 2. 3.

| Signal Name                                     | Туре | Pin #                 | Description                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A10 - A0<br>(PC Card Memory Mode)               |      | 8, 10, 11, 12, 14 -20 | These address lines along with the –REG signal are used to select the following: The I/O port address registers within the Compact Flash Card, the memory mapped port address registers within the card, a byte in the card's information structure and its configuration control and status registers. |

| A10 - A0<br>(PC Card I/O Mode)                  | Ι    |                       | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                              |

| A2 - A0<br>(True IDE Mode)                      |      | 18, 19, 20            | In True IDE Mode only A[2:0] is used to select the one of eight registers in the Task File.                                                                                                                                                                                                             |

| A10 - A3<br>(True IDE Mode)                     |      | 10, 19, 20            | In True IDE Mode these remaining address lines should be grounded by the host.                                                                                                                                                                                                                          |

| BVD1<br>(PC Card Memory Mode)                   |      |                       | This signal is asserted high as the BVD1 signal since a battery is not used with this product.                                                                                                                                                                                                          |

| -STSCHG<br>(PC Card I/O Mode)<br>Status Changed | I/O  | 46                    | This signal is asserted low to alert the host to changes in the RDY/ -BSY and Write Protect states, while the I/O interface is configured. Its use is controlled by the Card Config and Status Register.                                                                                                |

| -PDIAG<br>(True IDE Mode)                       |      |                       | In the True IDE Mode, this input/output is the Pass Diagnostic signal in the Master/Slave handshake protocol.                                                                                                                                                                                           |

| BVD2<br>(PC Card Memory Mode)                   |      |                       | This output line is always driven to a high state in Memory<br>Mode since a battery is not required for this product.                                                                                                                                                                                   |

| -SPKR<br>(PC Card I/O Mode)                     | I/O  | 45                    | This output line is always driven to a high state in I/O Mode since this product does not support the audio function.                                                                                                                                                                                   |

| -DASP<br>(True IDE Mode)                        |      |                       | In the True IDE Mode, this input/output is the Disk Active/Slave Present signal in the Master/Slave handshake protocol.                                                                                                                                                                                 |

| -CD1, -CD2<br>(PC Card Memory Mode)             |      |                       | These Card Detect pins are connected to ground on the<br>Compact Flash Card. They are used by the host to determine<br>if the card is fully inserted into its socket.                                                                                                                                   |

| -CD1, -CD2<br>(PC Card I/O Mode)                | 0    | 25, 26                | This signal is the same for all modes.                                                                                                                                                                                                                                                                  |

| -CD1, -CD2<br>(True IDE Mode)                   |      |                       | This signal is the same for all modes.                                                                                                                                                                                                                                                                  |

| Signal Name                                        | Туре | Pin #                              | Description                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------|------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -CE1, -CE2<br>(PC Card Memory Mode)<br>Card Enable |      |                                    | These input signals are used both to select the card and to indicate to the card whether a byte or a word operation is being performed. –CE2 always accesses the odd byte of the word. –CE1 accesses the even byte or the Odd byte of the word depending on A0 and –CE2. A multiplexing scheme based on A0, -CE1, -CE2 allows 8 bit hosts to access all data on D0 -D7. |

| -CE1, -CE2<br>(PC Card I/O Mode)<br>Card Enable    | Ι    | 7, 32                              | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                                                                                              |

| -CS0, -CS1<br>(True IDE Mode)                      |      |                                    | In the True IDE Mode –CS0 is the chip select for the task file registers while –CS1 is used to select the Alternate Status Register and the Device Control Register.                                                                                                                                                                                                    |

| -CSEL<br>(PC Card Memory Mode)                     |      |                                    | This signal is not used for this mode.                                                                                                                                                                                                                                                                                                                                  |

| -CSEL<br>(PC Card I/O Mode)                        | Ι    | 39                                 | This signal is not used for this mode.                                                                                                                                                                                                                                                                                                                                  |

| -CSEL<br>(True IDE Mode)                           |      |                                    | This internally pulled up signal is used to configure this<br>device as a Master or a Slave when configured in the True<br>IDE Mode. When this pin is grounded, this device is<br>configured as a Master. When this pin is open, this device is<br>configured as a Slave.                                                                                               |

| D15 - D00<br>(PC Card Memory Mode)                 |      |                                    | These lines carry the Data, Commands and Status information between the host and the controller. D00 is the LSB of the Even Byte of the Word. D08 is the LSB of the Odd Byte of the Word.                                                                                                                                                                               |

| D15 - D00<br>(PC Card I/O Mode)                    | I/O  | 2-6, 21, 22, 23, 27-31, 47, 48, 49 | These signals are the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                                                                                           |

| D15 - D00<br>(True IDE Mode)                       |      |                                    | In True IDE Mode all Task File operations occur in byte mode on the low order bus D00 -D07 while all data transfers are 16 bits using D00 -D15.                                                                                                                                                                                                                         |

| GND<br>(PC Card Memory Mode)                       |      |                                    | Ground.                                                                                                                                                                                                                                                                                                                                                                 |

| GND<br>(PC Card I/O Mode)                          | -    | 1, 50                              | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                  |

| GND<br>(True IDE Mode)                             |      |                                    | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                  |

| -INPACK<br>(PC Card Memory Mode)                   |   |    | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------|---|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -INPACK<br>(PC Card I/O Mode)<br>Input Acknowledge | 0 | 43 | The Input Acknowledge signal is asserted by the Compact<br>Flash Card when the card is selected and responding to an I/O<br>read cycle at the address that is on the address bus. This<br>signal is used by the host to control the enable of any input<br>data buffers between the card and the CPU.                                                                                                                                       |

|                                                    |   |    | This signal is a DMA Request that is used for DMA data<br>transfers between host and device. It shall be asserted by the<br>device when it is ready to transfer data to or from the host.<br>For Multiword DMA transfers, the direction of data transfer<br>is controlled by DIOR- and DIOWThis signal is used in a<br>handshake manner with DMACK- before negating<br>DMAREQ, and reasserting DMAREQ if there is more data to<br>transfer. |

|                                                    |   |    | DMAREQ shall not be driven when the device is not selected.                                                                                                                                                                                                                                                                                                                                                                                 |

| DMARQ<br>(True IDE Mode)                           |   |    | While a DMA operation is in progress, -CS0 and -CS1 shall<br>be held negated and the width of the transfers shall be 16 bits.                                                                                                                                                                                                                                                                                                               |

|                                                    |   |    | If there is no hardware support for DMA mode in the host,<br>this output signal is not used and should not be connected at<br>the host .In this case, the BIOS must report that DMA mode<br>is not supported by the host so that the device driver will not<br>attempt DMA mode.                                                                                                                                                            |

|                                                    |   |    | A host that does not support DMA mode and implements<br>both PCMCIA and true-IDE modes of operation need not<br>alter the PCMICIA mode connections while in True-IED<br>mode as long as this does not prevent proper operation in any<br>mode.                                                                                                                                                                                              |

| -IORD<br>(PC Card Memory Mode)                     |   |    | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                                                       |

| -IORD<br>(PC Card I/O Mode)                        | Ι | 34 | This is an I/O Read strobe generated by the host. This signal gates I/O data onto the bus from the Compact Flash Card when the card is configured to use the I/O interface.                                                                                                                                                                                                                                                                 |

| -IORD<br>(True IDE Mode)                           |   |    | In True IDE Mode, this signal has the same function as in PC Card I/O Mode.                                                                                                                                                                                                                                                                                                                                                                 |

| Signal Name                       | Туре | Pin # | Description                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -IOWR<br>(PC Card Memory Mode)    |      |       | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                          |

| - IOWR<br>(PC Card I/O Mode)      | I    | 35    | The I/O Write strobe pulse is used to clock I/O data on the Card Data bus into the Compact Flash controller registers when the card is configured to use the I/O interface.<br>The clocking will occur on the negative to positive edge of the signal (trailing edge).                                                                                         |

| - IOWR<br>(True IDE Mode)         |      |       | In True IDE Mode, this signal has the same function as in PC Card I/O Mode.                                                                                                                                                                                                                                                                                    |

| -OE<br>(PC Card Memory Mode)      |      |       | This is an Output Enable strobe generated by the host<br>interface. It is used to read data from the Compact Flash Card<br>in Memory Mode and to read the CIS and configuration<br>registers.                                                                                                                                                                  |

| -OE<br>(PC Card I/O Mode)         | I    | 9     | In PC Card I/O Mode, this signal is used to read the CIS and configuration registers.                                                                                                                                                                                                                                                                          |

| -ATA SEL<br>(True IDE Mode)       |      |       | To enable True IDE Mode this input should be grounded by the host.                                                                                                                                                                                                                                                                                             |

|                                   |      |       | In Memory Mode this signal is set high when the Compact<br>Flash Card is ready to accept a new data transfer operation<br>and held low when the card is busy. The host memory card<br>socket must provide a pull-up resistor.                                                                                                                                  |

| RDY/-BSY<br>(PC Card Memory Mode) | 0    | 37    | At power up and at Reset, the RDY/-BSY signal is held low<br>(busy) until the Compact Flash Card has completed its power<br>up or reset function. The RDY/-BSY signal is held high<br>(disabled from being busy) whenever the following condition<br>is true: The Compact Flash Card has been powered up with<br>+RESET continuously disconnected or asserted. |

| - IREQ<br>(PC Card I/O Mode)      |      |       | I/O Operation – After the Compact Flash Card has been<br>configured for I/O operation, this signal is used as – Interrupt<br>Request. This line is strobed low to generate a pulse mode<br>interrupt or held low for a level mode interrupt.                                                                                                                   |

| -INTRQ<br>(True IDE Mode)         |      |       | In True IDE Mode, this signal is the active high Interrupt Request to the host.                                                                                                                                                                                                                                                                                |

| Signal Name                                              | Туре | Pin #  | Description                                                                                                                                                                                                                                                      |

|----------------------------------------------------------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -REG<br>(PC Card Memory Mode)<br>Attribute Memory Select |      |        | This signal is used during Memory Cycles to distinguish<br>between Common Memory and Register (Attribute) Memory<br>accesses. High for Common Memory, Low for Attribute<br>Memory.                                                                               |

| -REG<br>(PC Card I/O Mode)                               |      |        | The signal must also be active (low) during I/O Cycles when the I/O address is on the Bus.                                                                                                                                                                       |

|                                                          |      |        | This is a DMA Acknowledge signal that is asserted by the host in response to DMAREQ to initiate DMA transfers.                                                                                                                                                   |

|                                                          | Ι    | 44     | While DMA operations are not active, the card shall ignore the –DMACK signal, including a floating condition.                                                                                                                                                    |

| -DMACK<br>(True IDE Mode)                                |      |        | If DAM operation is not supported by a True-IDE Mode only<br>host, this signal should be driven high or connected to VCC<br>by the host.                                                                                                                         |

|                                                          |      |        | A host that does not support DMA mode and implements<br>both PCMCIA and True-IDE modes of operation need not<br>alter the PCMCIA mode connections while in True-IDE<br>mode as long as this does not prevent proper operation all<br>modes.                      |

| -RESET<br>(PC Card Memory Mode)                          | Ţ    | 41     | When the pin is high, this signal resets the Compact Flash<br>Card. The card is Reset only at power up if this pin is left<br>high or open from power-up. The card is also reset when the<br>Soft Reset bit in the Card Configuration Option Register is<br>set. |

| -RESET<br>(PC Card I/O Mode)                             | 1    | 41     | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                       |

| -RESET<br>(True IDE Mode)                                |      |        | In the True IDE Mode this input pin is the active low hardware reset from the host.                                                                                                                                                                              |

| VCC<br>(PC Card Memory Mode)                             |      |        | +5, +3.3V power.                                                                                                                                                                                                                                                 |

| VCC<br>(PC Card I/O Mode)                                | -    | 13, 38 | This signal is the same for all modes.                                                                                                                                                                                                                           |

| VCC<br>(True IDE Mode)                                   |      |        | This signal is the same for all modes.                                                                                                                                                                                                                           |

| -VS1, -VS2<br>(PC Card Memory Mode)                      |      |        | Voltage Sense Signals. –VS1 is grounded so that the Compact Flash Card CIS can be read at 3.3 volts and –VS2 is open and reserved by PCMCIA for a secondary voltage.                                                                                             |

| -VS1, -VS2<br>(PC Card I/O Mode)                         | 0    | 33, 40 | This signal is the same for all modes.                                                                                                                                                                                                                           |

| -VS1, -VS2<br>(True IDE Mode)                            |      |        | This signal is the same for all modes.                                                                                                                                                                                                                           |

| Signal Name                    | Туре | Pin # | Description                                                                                                                                                                                                                                                              |

|--------------------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -WAIT<br>(PC Card Memory Mode) |      |       | This signal is not asserted for all modes.                                                                                                                                                                                                                               |

| -WAIT<br>(PC Card I/O Mode)    | О    | 42    | This signal is not asserted for all modes.                                                                                                                                                                                                                               |

| -IORDY<br>(True IDE Mode)      |      |       | This signal is not asserted for all modes.                                                                                                                                                                                                                               |

| -WE<br>(PC Card Memory Mode)   |      |       | This is a signal driven by the host and used for strobing<br>memory write data to the registers of the Compact Flash Card<br>when the card is configured in the memory interface mode. It<br>is also used for writing the configuration registers.                       |

| -WE<br>(PC Card I/O Mode)      | Ι    | 36    | In PC Card I/O Mode, this signal is used for writing the configuration registers.                                                                                                                                                                                        |

| -WE<br>(True IDE Mode)         |      |       | In True IDE Mode this input signal is not used and should be connected to VCC by the host.                                                                                                                                                                               |

| -WP<br>(PC Card Memory Mode)   |      |       | Memory Mode – The Compact Flash Card does not have a write protect switch. This signal is held low after the completion of the reset initialization sequence.                                                                                                            |

| -IOIS16<br>(PC Card I/O Mode)  | О    | 24    | I/O Operation – When the Compact Flash Card is configured<br>for I/O Operation, Pin 24 is used for the –I/O Selected is 16<br>Bit Port (-IOIS16) function. A Low signal indicates that a 16<br>bit or odd byte only operation can be performed at the<br>addressed port. |

| -IOCS16<br>(True IDE Mode)     |      |       | In True IDE Mode this output signal is asserted low when<br>this device is expecting a word data transfer cycle.                                                                                                                                                         |

## 2.0 Card Function Explanation

### 2.1 Attribute Access Specifications

When CIS-ROM region or Configuration register region is accessed, read and write operations are executed under the condition of -REG = "L" as follows. That region can be accessed by Byte/Word/Odd-byte modes, which are defined by PC card standard specifications.

| Table 8:  | Attribute     | Read          | Access   | Mode |

|-----------|---------------|---------------|----------|------|

| I unit of | 1 Ittl Induce | <b>I</b> teuu | 1 ACCC00 | moue |

| Mode                    | -REG | -CE2 | -CE1 | A0 | -OE | -WE | D8 -D15 | D0 -D7    |

|-------------------------|------|------|------|----|-----|-----|---------|-----------|

| Standby mode            |      | Н    |      |    |     |     | High-Z  | High-Z    |

| Dute access (9 hit)     | L    | Н    | L    | L  | L   | Н   | High-Z  | Even byte |

| Byte access (8-bit)     | L    | Н    | L    | Н  | L   | Н   | High-Z  | Invalid   |

| Word access (16-bit)    | L    | L    | L    |    | L   | Н   | Invalid | Even byte |

| Odd byte access (8-bit) | L    | L    | Н    |    | L   | Н   | Invalid | High-Z    |

#### Table 9: Attribute Write Access Mode

| Mode                    | -REG | -CE2 | -CE1 | A0 | -OE | -WE | D8 -D15    | D0 -D7     |

|-------------------------|------|------|------|----|-----|-----|------------|------------|

| Standby mode            |      | Н    |      |    |     |     | Don't care | Don't care |

| Byte access (8-bit)     | L    | Н    | L    | L  | Н   | L   | Don't care | Even byte  |

|                         | L    | Н    | L    | Н  | Н   | L   | Don't care | Don't care |

| Word access (16-bit)    | L    | L    | L    |    | Н   | L   | Don't care | Even byte  |

| Odd byte access (8-bit) | L    | L    | Н    |    | Н   | L   | Don't care | Don't care |

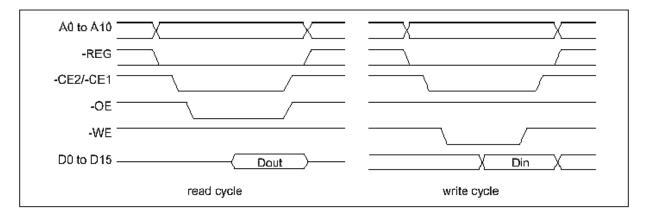

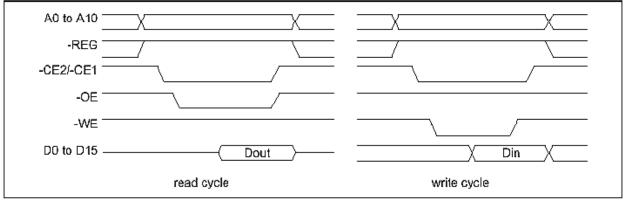

#### Figure 2: Attribute Access Timing Example

### 2.2 Task File Register Access Specifications

There are two cases of Task File register mapping, one is mapped I/O address area, and the other is mapped Memory address area. Each case of Task File register read and write operations are executed under the condition as follows. That area can be accessed by Byte/Word/Odd Byte modes, which are defined by PC card standard specifications.

#### 2.2.1 I/O Address Map

| -                       |      |      |      |    |       |       |     |     |          |           |

|-------------------------|------|------|------|----|-------|-------|-----|-----|----------|-----------|

| Mode                    | -REG | -CE2 | -CE1 | A0 | -IORD | -IOWR | -OE | -WE | D8 -D15  | D0 -D7    |

| Standby mode            |      | Н    |      |    |       |       |     |     | High-Z   | High-Z    |

| Dute access (8 bit)     | L    | Н    | L    | L  | L     | Н     | Н   | Н   | High-Z   | Even byte |

| Byte access (8-bit)     | L    | Н    | L    | Н  | L     | Н     | Н   | Н   | High-Z   | Odd byte  |

| Word access (16-bit)    | L    | L    | L    |    | L     | Н     | Н   | Н   | Odd byte | Even byte |

| Odd byte access (8-bit) | L    | L    | Н    |    | L     | Н     | Н   | Н   | Odd byte | High-Z    |

#### Table 10: Task File Register Read Access Mode (i)

#### Table 11: Task File Register Write Access Mode (i)

| Mode                    | -REG | -CE2 | -CE1 | AO | -IORD | -IOWR | -OE | -WE | D8 -D15    | D0 -D7     |

|-------------------------|------|------|------|----|-------|-------|-----|-----|------------|------------|

| Standby mode            |      | Н    |      |    |       |       |     |     | Don't care | Don't care |

| Brita agagas (8 hit)    | L    | Н    | L    | L  | Н     | L     | Н   | Н   | Don't care | Even byte  |

| Byte access (8-bit)     | L    | Н    | L    | Н  | Н     | L     | Н   | Н   | Don't care | Odd byte   |

| Word access (16-bit)    | L    | L    | L    |    | Н     | L     | Н   | Н   | Odd byte   | Even byte  |

| Odd byte access (8-bit) | L    | L    | Н    |    | Н     | L     | Η   | Н   | Odd byte   | Don't care |

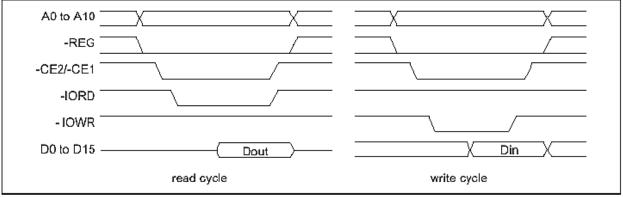

Figure 3: Task File Register Access Timing Example (i)

#### 2.2.2 Memory Address Map

Task File Register Read Access Mode (ii)

| Mode                    | -REG | -CE2 | -CE1 | A0 | -IORD | -IOWR | -OE | -WE | D8 -D15  | D0 -D7    |

|-------------------------|------|------|------|----|-------|-------|-----|-----|----------|-----------|

| Standby mode            |      | Н    |      |    |       |       |     |     | High-Z   | High-Z    |

| Brita appage (8 hit)    | Н    | Н    | L    | L  | L     | Н     | Н   | Н   | High-Z   | Even byte |

| Byte access (8-bit)     | Н    | Н    | L    | Н  | L     | Н     | Н   | Н   | High-Z   | Odd byte  |

| Word access (16-bit)    | Н    | L    | L    |    | L     | Н     | Н   | Н   | Odd byte | Even byte |

| Odd byte access (8-bit) | Н    | L    | Н    |    | L     | Н     | Н   | Н   | Odd byte | High-Z    |

#### Table 13: Task File Register Write Access Mode (ii)

| Mode                    | -REG | -CE2 | -CE1 | AO | -IORD | -IOWR | -OE | -WE | D8 -D15    | D0 -D7     |

|-------------------------|------|------|------|----|-------|-------|-----|-----|------------|------------|

| Standby mode            |      | Н    |      |    |       |       |     |     | Don't care | Don't care |

| Byte access (8-bit)     | Н    | Н    | L    | L  | Н     | L     | Н   | Н   | Don't care | Even byte  |

| Byte access (8-bit)     | Н    | Н    | L    | Н  | Н     | L     | Н   | Н   | Don't care | Odd byte   |

| Word access (16-bit)    | Н    | L    | L    |    | Н     | L     | Н   | Н   | Odd byte   | Even byte  |

| Odd byte access (8-bit) | Н    | L    | Н    |    | Н     | L     | Н   | Н   | Odd byte   | Don't care |

Figure 4: Task File Register Access Timing Example (ii)

#### 2.2.3 True IDE Mode

The card can be configured in a True IDE Mode of operation. This card is configured in this mode only when the –OE input signal is asserted GND by the host. In this True IDE Mode Attribute Registers are not accessible from the host. Only I/O operation to the task files and data registers are allowed. If this card is configured during power on sequence, data registers are accessed in word (16-bit). The card permits 8-bit accesses if the user issues a Set Feature Command to put the device in 8-bit mode.

#### Table 14: True IDE Mode Read I/O Function

| Mode                    | -CE2 | -CE1 | A0 -A2 | -IORD | -IOWR | D8 -D15  | D0 -D7     |

|-------------------------|------|------|--------|-------|-------|----------|------------|

| Invalid mode            | L    | L    |        |       |       | High-Z   | High-Z     |

| Standby mode            | Н    | Н    |        |       |       | High-Z   | High-Z     |

| Data register access    | Н    | L    | 0      | L     | Н     | Odd byte | Even byte  |

| Alternate status access | L    | Н    | 6H     | L     | Н     | High-Z   | Status out |

| Other task file access  | Н    | L    | 1-7H   | L     | Н     | High-Z   | Data       |

#### Table 15: True IDE Mode Write I/O Function

| Mode                    | -CE2 | -CE1 | A0 -A2 | -IORD | -IOWR | D8 -D15    | D0 -D7     |

|-------------------------|------|------|--------|-------|-------|------------|------------|

| Invalid mode            | L    | L    |        |       |       | Don't care | Don't care |

| Standby mode            | Н    | Н    |        |       |       | Don't care | Don't care |

| Data register access    | Н    | L    | 0      | L     | Н     | Odd byte   | Even byte  |

| Alternate status access | L    | Н    | 6H     | L     | Н     | Don't care | Control in |

| Other task file access  | Н    | L    | 1-7H   | L     | Н     | Don't care | Data       |

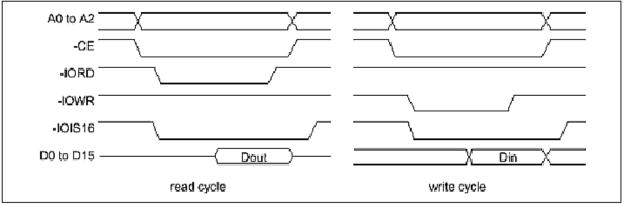

Figure 5: True IDE Mode I/O Access Timing Example

### 2.3 Configuration Register Specification

This card supports four configuration registers for the purpose of the configuration and observation of this card. These registers can be used in memory card mode and I/O card mode. In True IDE mode, these registers cannot be used.

#### 2.3.1 Configuration Option register (Address 200H)

This register is used for setting the card configuration status and for issuing soft reset to the card.

| bit 7  | bit 6   | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|--------|---------|-------|-------|-------|-------|-------|-------|

| SRESET | LevlREQ | INDEX |       |       |       |       |       |

| NOTE:  |         |       |       |       |       |       |       |

Initial value: 00H

#### **Table 17: Option Register Function**

| Name             | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRESET (HOST->)  | R/W | Setting this bit to "1", places the card in the reset state (Card Hard Reset). This operation is equal to Hard Reset, except this bit is not cleared. Then this bit set to "0", places the card in the reset state of Hard Reset (This bit is set to "0" by Hard Reset). Card configuration status is reset and the card internal initialized operation starts when Card hard Reset is executed, so next access to the card should be the same sequence as the power on sequence. |

| LevIREQ (HOST->) | R/W | This bit sets to "0" when pulse mode interrupt is selected, and "1" when level mode interrupt is selected.                                                                                                                                                                                                                                                                                                                                                                        |

| INDEX (HOST->)   | R/W | This bit is used for select operation mode of the card as follows. When Power on, Card Hard Reset and Soft Reset, this data is "000000" for the purpose of Memory card interface recognition.                                                                                                                                                                                                                                                                                     |

#### Table 18: INDEX bit assignment

|   | ] | INDE | X Bi | t |   | Tool: File register address | Monning mode          |

|---|---|------|------|---|---|-----------------------------|-----------------------|

| 5 | 4 | 3    | 2    | 1 | 0 | Task File register address  | Mapping mode          |

| 0 | 0 | 0    | 0    | 0 | 0 | 0H to FH, 400H to 7FFH      | Memory Mapped         |

| 0 | 0 | 0    | 0    | 0 | 1 | xx0H to xxFH                | Contiguous I/O Mapped |

| 0 | 0 | 0    | 0    | 1 | 0 | 1F0H to 1F7H, 3F6H to 3F7H  | Primary I/O Mapped    |

| 0 | 0 | 0    | 0    | 1 | 1 | 170H to 177H, 376H to 377H  | Secondary I/O Mapped  |

#### 2.3.2 Configuration and Status Register (Address 202H)

This register is used for observing the card state.

| bit 7 | bit 6  | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| CHGED | SIGCHG | IOIS8 | 0     | 0     | PWD   | INTR  | 0     |

NOTE: 1. 1nitial value: 00H

#### Table 19: Configuration and Status Register Function

| Name            | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHGED (HOST->)  | R   | This bit indicates that CRDY/-BSY bit on Pin Replacement register is set to "1".<br>When CHGED bit is set to "1", -STSCHG pin is held "L" at the condition of<br>SIGCHG bit set to "1" and the card configured for the I/O interface.                                                                                                                                                                                            |

| SIGCHG (HOST->) | R/W | This bit is set or reset by the host for enabling and disabling the status-change signal (-STSCHG pin). When the card is configured I/O card interface and this bit is set to "1", -STSCHG pin is controlled by CHGED bit. If this bit is set to "0", -STSCHG pin is kept "H".                                                                                                                                                   |

| IOIS8 (HOST->)  | R/W | The host sets this field to "1" when it can provide I/O cycles only with one 8-bit data bus (D7 to D0).                                                                                                                                                                                                                                                                                                                          |

| PWD (HOST->)    | R/W | When this bit is set to "1", the card enters sleep stat (Power Down mode). When this bit is reset to "0", the card transfers to idle state (active mode). RRDY/-BSY bit on Pin Replacement Register becomes BUSY when this bit is changed. RRDY/-BSY will not become Ready until the power state requested has been entered. This card automatically powers down when it is idle, and powers back up when it receives a command. |

| INTR (HOST->)   | R   | This bit indicates the internal state of the interrupt request. This bit state is available whether I/O card interface has been configured or not. This signal remains true until the condition which caused the interrupt request has been serviced. If interrupts are disabled by the –IEN bit in the Device Control Register, this bit is a zero.                                                                             |

#### 2.3.3 Pin Replacement Register (Address 204H)

This register is used for providing the signal state of -IREQ signal when the card configured I/O card interface.

| bit 7 | bit 6 | bit 5     | bit 4 | bit 3 | bit 2 | bit 1     | bit 0 |

|-------|-------|-----------|-------|-------|-------|-----------|-------|

| 0     | 0     | CRDY/-BSY | 0     | 1     | 1     | RRDY/-BSY | 0     |

| NOTE  |       |           |       |       |       |           |       |

**NOTE: 1.** Initial value 0CH

#### **Table 20: Pin Replacement Register Function**

| Name               | R/W | Function                                                                                                  |

|--------------------|-----|-----------------------------------------------------------------------------------------------------------|

| CRDY/-BSY (HOST->) | R/W | This bit is set to "1" when the RRDY/-BSY bit changes state. This bit may also be written by the host     |

| RRDY/-BSY (HOST->) | R/W | When read, this bit indicates +READY pin states. When written, this bit is used for CRDY/-BSY bit masking |

#### 2.3.4 Socket and Copy Register (Address 206H)

This register is used for identification of the card from the other cards. Host can read and write this register. This register should be set by host before Configuration Option register is set.

| bit 7 b | oit 6 bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|---------|-------------|-------|-------|-------|-------|-------|

| 0       | 0 0         | DRV#  | 0     | 0     | 0     | 0     |

NOTE: 1. Initial value: 00H

#### **Table 21: Socket and Copy Register Function**

| Name          | R/W | Function                                                                                                                                                                                                                |

|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRV# (HOST->) | R/W | This field are used for the configuration of the plural cards. When host configures the plural cards, written the card's copy number in this field. In this way, host can perform the card's master/slave organization. |

### 2.4 Task File Register Specification

These registers are used for reading and writing the storage data in the card. These registers are mapped five types by the configuration of INDEX in Configuration Option register. The decoded addresses are shown as follows.

#### Table 22: Memory map (INDEX=0)

| -REG | A10 | A9 -A4 | A3 | A2 | A1 | A0 | Offset | -OE=L                   | -WE=L                   |

|------|-----|--------|----|----|----|----|--------|-------------------------|-------------------------|

| 1    | 0   |        | 0  | 0  | 0  | 0  | 0H     | Data register           | Data register           |

| 1    | 0   |        | 0  | 0  | 0  | 1  | 1H     | Error register          | Feature register        |

| 1    | 0   |        | 0  | 0  | 0  | 0  | 2H     | Sector count register   | Sector count register   |

| 1    | 0   |        | 0  | 0  | 0  | 1  | 3H     | Sector number register  | Sector number register  |

| 1    | 0   |        | 0  | 1  | 1  | 0  | 4H     | Cylinder low register   | Cylinder low register   |

| 1    | 0   |        | 0  | 1  | 1  | 1  | 5H     | Cylinder high register  | Cylinder high register  |

| 1    | 0   |        | 0  | 1  | 1  | 0  | 6H     | Drive head register     | Drive head register     |

| 1    | 0   |        | 1  | 1  | 1  | 1  | 7H     | Status register         | Command register        |

| 1    | 0   |        | 1  | 0  | 0  | 0  | 8H     | Dup. even data register | Dup. even data register |

| 1    | 0   |        | 1  | 0  | 0  | 1  | 9H     | Dup. odd data register  | Dup. odd data register  |

| 1    | 0   |        | 1  | 1  | 1  | 1  | DH     | Dup. error register     | Dup. feature register   |

| 1    | 0   |        | 1  | 1  | 1  | 0  | EH     | Alt. status register    | Device control register |

| 1    | 0   |        | 1  | 1  | 1  | 1  | FH     | Drive address register  | Reserved                |

| 1    | 1   |        |    |    |    | 0  | 8H     | Even data register      | Even data register      |

| 1    | 1   |        |    |    |    | 1  | 9H     | Odd data register       | Odd data register       |

#### Table 23: Contiguous I/O map (INDEX=1)

| -REG | A10 -A4 | A3 | A2 | A1 | A0 | Offset | -IORD=L                 | -IOWR=L                 |

|------|---------|----|----|----|----|--------|-------------------------|-------------------------|

| 0    |         | 0  | 0  | 0  | 0  | 0H     | Data register           | Data register           |

| 0    |         | 0  | 0  | 0  | 1  | 1H     | Error register          | Feature register        |

| 0    |         | 0  | 0  | 1  | 0  | 2H     | Sector count register   | Sector count register   |

| 0    |         | 0  | 0  | 1  | 1  | 3H     | Sector number register  | Sector number register  |

| 0    |         | 0  | 1  | 0  | 0  | 4H     | Cylinder low register   | Cylinder low register   |

| 0    |         | 0  | 1  | 0  | 1  | 5H     | Cylinder high register  | Cylinder high register  |

| 0    |         | 0  | 1  | 1  | 0  | 6H     | Drive head register     | Drive head register     |

| 0    |         | 0  | 1  | 1  | 1  | 7H     | Status register         | Command register        |

| 0    |         | 1  | 0  | 0  | 0  | 8H     | Dup. even data register | Dup. even data register |

| 0    |         | 1  | 0  | 0  | 1  | 9H     | Dup. odd data register  | Dup. odd data register  |

| 0    |         | 1  | 1  | 0  | 1  | DH     | Dup. error register     | Dup. feature register   |

| 0    |         | 1  | 1  | 1  | 0  | EH     | Alt. status register    | Device control register |

| 0    |         | 1  | 1  | 1  | 1  | FH     | Drive address register  | Reserved                |

| -REG | A10 | A9 -A4 | A3 | A2 | A1 | A0 | -IORD=L                | -IOWR=L                 |

|------|-----|--------|----|----|----|----|------------------------|-------------------------|

| 0    |     | 1FH    | 0  | 0  | 0  | 0  | Data register          | Data register           |

| 0    |     | 1FH    | 0  | 0  | 0  | 1  | Error register         | Feature register        |

| 0    |     | 1FH    | 0  | 0  | 1  | 0  | Sector count register  | Sector count register   |

| 0    |     | 1FH    | 0  | 0  | 1  | 1  | Sector number register | Sector number register  |

| 0    |     | 1FH    | 0  | 1  | 0  | 0  | Cylinder low register  | Cylinder low register   |

| 0    |     | 1FH    | 0  | 1  | 0  | 1  | Cylinder high register | Cylinder high register  |

| 0    |     | 1FH    | 0  | 1  | 1  | 0  | Drive head register    | Drive head register     |

| 0    |     | 1FH    | 0  | 1  | 1  | 1  | Status register        | Command register        |

| 0    |     | 3FH    | 0  | 1  | 1  | 0  | Alt. status register   | Device control register |

| 0    |     | 3FH    | 0  | 1  | 1  | 1  | Drive address register | Reserved                |

#### Table 25: Secondary I/O Map (INDEX=3)

| -REG | A10 | A9 -A4 | A3 | A2 | A1 | A0 | -IORD=L                | -IOWR=L                 |

|------|-----|--------|----|----|----|----|------------------------|-------------------------|

| 0    |     | 17H    | 0  | 0  | 0  | 0  | Data register          | Data register           |

| 0    |     | 17H    | 0  | 0  | 0  | 1  | Error register         | Feature register        |

| 0    |     | 17H    | 0  | 0  | 1  | 0  | Sector count register  | Sector count register   |

| 0    |     | 17H    | 0  | 0  | 1  | 1  | Sector number register | Sector number register  |

| 0    |     | 17H    | 0  | 1  | 0  | 0  | Cylinder low register  | Cylinder low register   |

| 0    |     | 17H    | 0  | 1  | 0  | 1  | Cylinder high register | Cylinder high register  |

| 0    |     | 17H    | 0  | 1  | 1  | 0  | Drive head register    | Drive head register     |

| 0    |     | 17H    | 0  | 1  | 1  | 1  | Status register        | Command register        |

| 0    |     | 37H    | 0  | 1  | 1  | 0  | Alt. status register   | Device control register |

| 0    |     | 37H    | 0  | 1  | 1  | 1  | Drive address register | Reserved                |

#### Table 26: True IDE Mode I/O Map

| -CE2 | -CE1 | A2 | A1 | A0 | -IORD=L                | -IOWR=L                 |

|------|------|----|----|----|------------------------|-------------------------|