# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Nuvoton PCI TO ISA BRIDGE

W83628AG W83629AG

Revision: 1.2 Date: January, 2008

|   | PAGES  | DATES      | VERSION | MAIN CONTENTS                                                                                                                                                |

|---|--------|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | N.A.   | 07/30/2007 | 0.5     | 1. First published version.                                                                                                                                  |

| 2 | 34, 38 | 08/02/2007 | 0.51    | <ol> <li>Update the information of Chapter 10 Absolute<br/>Maximum Ratings.</li> <li>Modify the description of Chapter 12 AC<br/>Characteristics.</li> </ol> |

| 3 | N.A.   | 11/01/2007 | 1.0     | 1. All versions before 1.0 are preliminary versions.                                                                                                         |

| 4 | 1      | 11/28/2007 | 1.1     | 1. Add the ordering information                                                                                                                              |

| 5 | 11     | 31/1/2008  | 1.2     | 1. Modify DC characteristics                                                                                                                                 |

#### W83628AG & W83629AG Datasheet Revision History

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this data sheet belong to their respective owners.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Nuvoton customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nuvoton for any damages resulting from such improper use or sales.

## nuvoTon

#### Table of Contents -

| 1.  | GENE   | RAL DES   | CRIPTION                              | 1    |

|-----|--------|-----------|---------------------------------------|------|

| 2.  | FEATU  | JRES      |                                       | 1    |

| 3.  | PACK   | AGE       |                                       | 1    |

| 4.  | ORDE   | RING INF  | ORMATION                              | 1    |

| 5.  | BLOC   | K DIAGRA  | M OF W83628AG                         | 2    |

| 6.  | BLOC   | K DIAGRA  | M OF W83629AG                         | 3    |

| 7.  | FUNC   | TION DES  | CRIPTION                              | 4    |

|     | 7.1    | PCI Inter | face                                  | 4    |

|     | 7.2    |           | face                                  |      |

|     | 7.3    |           | Q Interface                           |      |

|     | 7.4    |           | DMA Interface                         |      |

|     | 7.5    |           | SYSCLK Clock Generation               |      |

|     | 7.6    | ISA Bus   | I/O Recovery Time                     | 8    |

|     | 7.7    |           | ·                                     |      |

| 8.  | PIN C  | ONFIGUR   | ATION                                 | 9    |

|     | 8.1    | PIN CON   | IFIGURATION FOR W83628AG              | 9    |

|     | 8.2    | PIN CON   | IFIGURATION FOR W83629AG              | 10   |

| 9.  | PIN DI | ESCRIPTI  | ON                                    | . 11 |

|     | 9.1    | W83628    | AG PIN DESCRIPTION                    | 11   |

|     |        | 9.1.1     | PCI Interface                         | 11   |

|     |        | 9.1.2     | Control Logic and Handshaking Signals | .13  |

|     |        | 9.1.3     | ISA Interface Signals                 | .13  |

|     |        | 9.1.4     | Power Signals                         | .16  |

|     |        | 9.1.5     | NC Pins                               | .16  |

|     | 9.2    | W83629/   | AG PIN DESCRIPTION                    | 17   |

|     |        | 9.2.1     | Control Logic and Handshaking Signals | .17  |

|     |        | 9.2.2     | PC/PCI Interface                      | .17  |

|     |        | 9.2.3     | IRQ Serializer Interface              | .18  |

|     |        | 9.2.4     | Power Signals                         | .18  |

|     |        | 9.2.5     | NC Pins                               | .18  |

| 10. | PCI C  | ONFIGUR   | ATION REGISTERS                       | 19   |

|     | 10.1   | VID-VEN   | IDOR IDENTIFICATION REGISTER          | 19   |

|     | 10.2   | DID-DEV   | ICE IDENTIFICATION REGISTER           | 19   |

|     | 10.3   | PCICMD    | -PCI COMMAND REGISTER                 | 19   |

Publication Release Date: January, 2008 Revision 1.2

| 10.4  | PCISTS-PCI STATUS REGISTER                                      | 20 |

|-------|-----------------------------------------------------------------|----|

| 10.5  | REVID-REVISION IDENTIFICATION REGISTER                          | 21 |

| 10.6  | CCODE-CALSS CODE REGISTER                                       | 21 |

| 10.7  | HEADT-HEAD TYPE REGISTER                                        | 22 |

| 10.8  | IO_RCVR-IO RECOVERY REGISTER                                    | 22 |

| 10.9  | WISA_STS-ISA BRIDGE ERROR STATUS REGISTER                       | 23 |

| 10.10 | BRIDGE FAST MEMORY DECODER #0 CONTROL REGISTERS                 | 24 |

| 10.11 | BRIDGE FAST MEMORY DECODER #1 CONTROL REGISTERS                 | 25 |

| 10.12 | BRIDGE FAST MEMEORY DECODER #2 CONTROL REGISTERS                | 26 |

| 10.13 | WISA_FADC-ISA BRIDGE FAST IO DECODERS CONTROL REGISTERS         | 27 |

| 10.14 | ISA_FAD0MC-ISA BRIDGE FAST DECODERS # 0 MASK CONTROL REGISTER   | 29 |

| 10.15 | WISA_FAD0MC-ISA BRIDGE FAST DECODERS # 1 MASK CONTROL REGIST 29 | ER |

| 10.16 | WISA_FAD0MC-ISA BRIDGE FAST DECODERS # 2 MASK CONTROL REGIST 29 | ER |

| 10.17 | WISA_FAD0MC-ISA BRIDGE FAST DECODERS # 3 MASK CONTROL REGIST 29 | ER |

| 10.18 | WISA_FAD0MC-ISA BRIDGE FAST DECODERS # 4 MASK CONTROL REGIST 30 | ER |

| 10.19 | WISA_FAD0MC-ISA BRIDGE FAST DECODERS # 5 MASK CONTROL REGIST 30 | ER |

| 10.20 | WISA_FAD0MC-ISA BRIDGE FAST DECODERS # 6 MASK CONTROL REGIST 30 | ER |

| 10.21 | WISA_FAD0MC-ISA BRIDGE FAST DECODERS # 7 MASK CONTROL REGIST 30 | ER |

| 10.22 | WISA_FADCB0-ISA BRIDGE FAST DECODERS # 0 BASE ADDRESS REGISTER  | 31 |

| 10.23 | WISA_FADCB1-ISA BRIDGE FAST DECODERS # 1 BASE ADDRESS REGISTER  | 31 |

| 10.24 | WISA_FADCB2-ISA BRIDGE FAST DECODERS # 2 BASE ADDRESS REGISTER  | 31 |

| 10.25 | WISA_FADCB3-ISA BRIDGE FAST DECODERS # 3 BASE ADDRESS REGISTER  | 31 |

| 10.26 | WISA_FADCB4-ISA BRIDGE FAST DECODERS # 4 BASE ADDRESS REGISTER  | 31 |

| 10.27 | WISA_FADCB5-ISA BRIDGE FAST DECODERS # 5 BASE ADDRESS REGISTER  | 32 |

| 10.28 | WISA_FADCB6-ISA BRIDGE FAST DECODERS # 6 BASE ADDRESS REGISTER  | 32 |

| 10.29 | WISA_FADCB7-ISA BRIDGE FAST DECODERS # 7 BASE ADDRESS REGISTER  | 32 |

| 10.30 | WISA_CTRLREG1-ISA BRIDGE CONTROL REGISTER 1                     | 33 |

| 10.31 | WISA_CTRLREG2-ISA BRIDGE CONTROL REGISTER 2                     | 34 |

| 10.32 | WISA_CTRLREG3-ISA BRIDGE CONTROL REGISTER 3                     | 34 |

| 10.33 | WISA_CTRLREG4-ISA BRIDGE CONTROL REGISTER 4                     | 35 |

Publication Release Date: January, 2008 Revision 1.2

## nuvoTon

|     | 10.34 BRIDGE FAST MEMORY DECODER #3 CONTROL REGISTERS | 35 |

|-----|-------------------------------------------------------|----|

|     | 10.35 WISA_TSTREG-ISA BRIDGE TEST REGISTER            | 36 |

| 11. | ABSOLUTE MAXIMUM RATINGS                              | 37 |

| 12. | DC CHARACTERISTICS                                    | 37 |

| 13. | AC CHARACTERISTICS                                    | 40 |

| 14. | WAVEFORMS                                             | 43 |

| 15. | TOP MARKING SPECIFICATION                             | 58 |

| 16. | PACKAGE DIMENSIONS 1 FOR W83628AG (128-PIN PQFP)      | 59 |

| 17. | PACKAGE DIMENSIONS 2 FOR W83629AG (48-PIN LQFP)       | 59 |

#### 1. GENERAL DESCRIPTION

The W83628AG is a PCI-to-ISA bus conversion IC. The W83629AG is a condensed centralizer IC for IRQ and DMA control. W83628AG and W83629AG together form a complete set for the PCI-to-ISA bridge.

For the new generation Intel chipsets featuring LPC bus but not supporting ISA bus and slots, the W83628AG plus the W83629AG are the best companion solution for the non-ISA chipset. Also the packages of the W83628AG (128-QFP) and the W83629AG (48-LQFP) are the most cost-effective solution that minimizes the M/B board layout size and cost.

For the new generation chipsets featuring LPC interface but not supporting ISA bus, the best and the most complete solution will be the combination of the W83627 (Nuvoton LPC I/O) family and the set of the W83628AG and the W83629AG.

#### 2. FEATURES

#### PCI to ISA Bridge

- Full ISA Bus Support, including ISA Masters

- 5V ISA and 3.3V PCI interfaces

- PC/PCI DMA protocol for Software Transparent

- IRQ Serializer for ISA Parallel IRQ transfer to Serial IRQ

- Supports 3 fully ISA Compatible Slots without Buffering

- PCI Bus at 25MHz, 33MHz and up to 40MHz

- Supports Programmable ISA Bus Divide the PCI Bus Clock into 3 or 4

- All ISA Signals can be Isolated

- Supports Configuration registers for performance programming

#### 3. PACKAGE

- 128-pin QFP for the W83628AG

- 48-pin LQFP for the W83629AG

#### 4. ORDERING INFORMATION

| PART NUMBER | DESCRIPTION                   | PRODUCTION FLOW          |

|-------------|-------------------------------|--------------------------|

| W83628AG    | 128-PIN QFP, Pb-free          | Commercial, 0°C to +70°C |

| W83629AG    | 48-PIN LQFP, Pb-free          | Commercial, 0°C to +70°C |

| W83628AGEVB | W83628/629AG Evaluation board |                          |

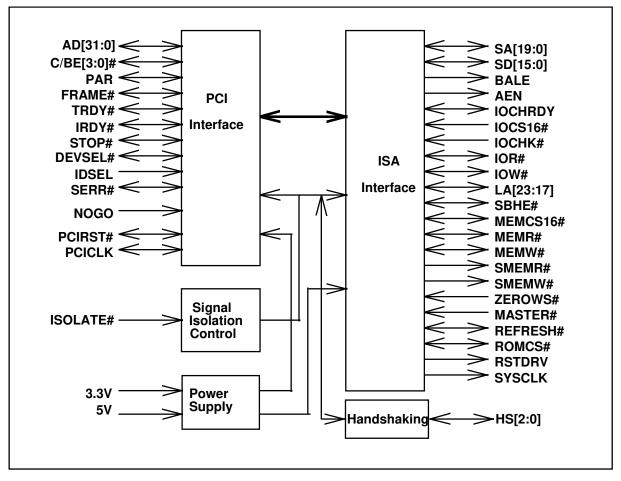

#### 5. BLOCK DIAGRAM OF W83628AG

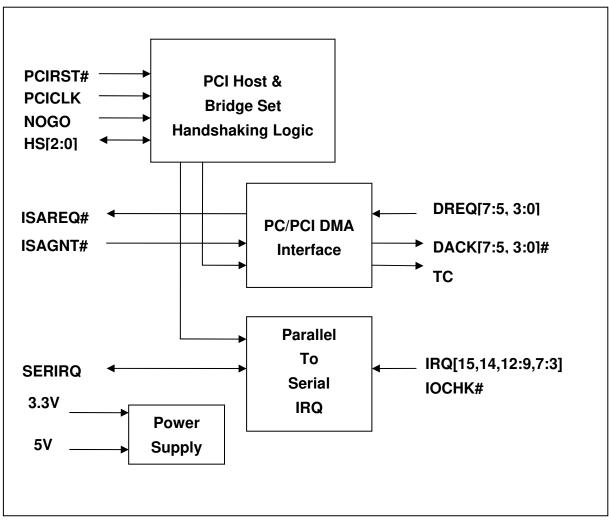

#### 6. BLOCK DIAGRAM OF W83629AG

#### 7. FUNCTION DESCRIPTION

The W83628AG and W83629AG support the functional sub-block interfaces described below:

#### 7.1 PCI Interface

The W83628AG provides a PCI slave/master interface. The slave mode means the PCI cycles are initiated by the PCI Host Bridge or South Bridge chipset. Default is PCI bus cycle information from PCI Host Bridge being received in PCI slave mode. When ISA bus's MASTER# signal is asserted, the W83628A's PCI interface as slave mode will be switched to PCI master mode to drive/initiate PCI bus cycles to PCI bus. The W83628AG supports some positive decodes and implements subtractive decodes for unclaimed PCI accesses.

The PCI slave interface supports the positive decodes as below:

- PCI configuration register spaces which are positively decode with medium DEVSEL# timing speed on the Type0 PCI configuration cycle.

- Eight IO positively decode space which can be programmed to claim PCI I/O cycle with Fast/Medium/Slow/Subtractive DEVSEL# timing speed.

- Four Memory positively decode spaces which can be programmed to claim PCI Memory cycle with Fast/Medium/Slow/Substractive DEVSEL# timing speed.

- PC/PCI DMA (PPDMA) cycle space: The I/O portion of the DMA cycle generates a PCI I/O cycle to one of the four I/O addresses of 0000h/0004h/00C0h/00C4h

- ISA BIOS ROM boot up scheme: upload boot ROM on ISA bus during system boot up. Enable/disbale optionally the function through the external pull-up resistor on signal ROMCS# of the W83628AG. When PCIRST# is asserted, the signal ROMCS# will be detected and latched. After PCIRST# is released, the latched signal High(1)/Low(0) means to enable(1)/disable(0) the ISA BIOS ROM boot up function, respectively. The latched bit can also be disabled/enabled through Type0 PCI configuration cycle.

The PCI master interface will issue PCI cycle for ISA bus master cycle.

The W83628AG and the W83629AG together support PC/PCI DMA. The W83629AG uses dedicated ISAREQ# and ISAGNT# signals to permit ISA devices' transfer requests associated with specific DMA channels. Upon receiving a request and getting control of the PCI bus, South Bridge chipset performs a two-cycle transfer. For example, if data is to be moved from the peripheral to the main memory, the chipset will first read data from the peripheral and then write it to the main memory.

When in PC/PCI DMA cycle, the W83629AG DACKn# is decoded from ISAGNT#. As long as the ISAGNT# and MASTER# signals are asserted and are with an ISA command issued by ISA master, then the W83628AG PCI master interface will issues a PCI cycle for ISA master.

#### 7.2 ISA Interface

The W83628AG provides an ISA bus interface for the subtractive decoded memory and I/O cycles on PCI. Default is driving/issuing relative legacy ISA bus cycle to ISA bus in ISA master mode. Generally if a valid PCI memory or I/O cycle is received by the W83628AG PCI slave interface, it will be passed to the internal ISA interface and the ISA interface will convert it to correspond to the ISA bus cycle. When ISA bus's MASTER# signal is asserted, the W83628AG ISA interface as master mode will be switched to ISA slave mode to receive legacy ISA bus cycles from the ISA bus. That means there is an ISA command issued by ISA master. The related ISA bus cycle will be passed to PCI master interface to drive/issue corresponding PCI bus cycle.

#### 7.3 Serial IRQ Interface

The W83629AG supports a serialized IRQ slave which conforms to the specification of "Serialized IRQ Support for PCI system, rev. 6.0, September 1, 1995". Two modes, continuous and quiet, are supported.

The serial IRQ interface provides signal filtering and encoding logic for all legacy parallel ISA IRQ channels (IRQ15-14, 12-9, 7-3 and IOCHK#) to convert them to serial IRQ on the SERIRQ line. The IRQ/Data serializer is a Wired-OR structure that simply passes the state of one or more device's IRQ(s) and/or Data to the host controller. The transfer can be initiated by either a device or the host controller. A transfer, called an IRQSER Cycle, consists of three frame types: one Start Frame, several IRQ/Data Frames, and one Stop Frame.

This protocol uses the PCI Clock as its clock source and conforms to the PCI bus electrical specification.

|           |          | SL<br>or<br>H | START FRAME        | IRQ0 FRAMI | E   IRQ1 FRAME<br>  S   R   T | IRQ2 FRAME<br>S   R   T |

|-----------|----------|---------------|--------------------|------------|-------------------------------|-------------------------|

| PCICLK    |          |               |                    |            |                               |                         |

| IRQSER    |          |               | START <sup>1</sup> |            |                               |                         |

| Drive Sou | urce     | IRQ1          | Host Controller    | None       | IRQ1                          | None                    |

| Н         | l=Host C | ontrol        | SL=Slave Control   | R=Recovery | T=Turn-around                 | S=Sample                |

• Start Frame timing with source sampled a low pulse on IRQ1

Start Frame pulse can be 4-8 clocks wide

### nuvoTon

|       | <ul> <li>Stop F</li> </ul>      | -rame Timing with       | Host using 17 IRQSER                     | sampling period        |                    |

|-------|---------------------------------|-------------------------|------------------------------------------|------------------------|--------------------|

|       | IRQ14<br>  FRAME<br>  S   R   T | IRQ15<br>FRAME<br>S R T | IOCHCK# ST<br>FRAME S R T I <sup>2</sup> | TOP FRAME<br>H   R   T | NEXT CYCLE         |

| PCICL |                                 |                         |                                          |                        |                    |

| IRQSE | R                               |                         |                                          | STOP <sup>1</sup>      | START <sup>3</sup> |

| Drive | er None                         | IRQ15                   | None H                                   | lost Controller        |                    |

|       | H=Host Control                  | R=Recovery              | T=Turn-around                            | S=Sample               | I= Idle.           |

|       |                                 |                         |                                          |                        |                    |

- 1. Stop pulse is 2 clocks wide for Quiet mode, 3 clocks wide for Continuous mode.

- 2. There may be none, one or more Idle states during the Stop Frame.

- 3. The next IRQSER cycle's Start Frame pulse <u>may</u> or may not start immediately after the turn-around clock of the Stop Frame.

The main difference between the quite mode and the continuous mode for the IRQSER Frame is:

- Quiet (Active) Mode: Any device may initiate a Start Frame by driving the IRQSER low for one clock, while the IRQSER is Idle.

- Continuous (Idle) Mode: Only the Host controller can initiate a Start Frame to update IRQ/Data line information.

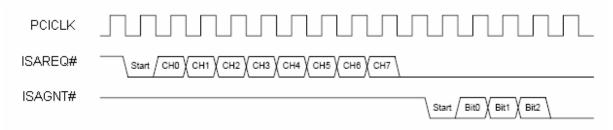

#### 7.4 PC/PCI DMA Interface

The W83629AG supports PC/PCI DMA Serial Channel Passing Protocol interface as shown in Figure 6-1.

Figure 6-1: PC/PCI DMA Serial Channel Passing Protocol

When the W83629AG receives the legacy ISA DMA requesting DRQn, the DMA interface must encode the channel request information, where CH0-CH7 will be active high, depending on which is requested as the DMA channel.

The South Bridge chipset encodes the granted channel on the ISAGNT# line, where the bits have the same meaning. For example, the sequence [start, bit0, bit1, bit2] = [0, 1, 0, 0] grants DMA channel 1 to the requesting device, and the sequence [start, bit0, bit1, bit2] = [0, 0, 1, 1] grants DMA channel 6 to the requesting device.

After receiving a valid grant and detecting ISAGN# start bit, the W83629AG will decode and convert the ISAGNT# signal information to corresponding legacy ISA DMA acknowledge DACKn# signal.

Table 6-1 below shows the I/O portion of the DMA cycle generates a PCI I/O cycle to one of the four I/O addresses. The W83628AG will recognize the PCI I/O cycle with the DMA I/O address. These cycles must be qualified by an active ISAGNT# signal to the requesting device. A2 of DMA I/O address bit 2 is used to indicate DMA Terminal Count cycle.

| DMA CYCLE TYPE | DMA I/O ADDRESS | TC(A2) | PCI CYCLE TYPE |

|----------------|-----------------|--------|----------------|

| Normal         | 00h             | 0      | I/O Read/Write |

| Normal TC      | 04h             | 1      | I/O Read/Write |

| Verify         | 0C0h            | 0      | I/O Read       |

| Verify TC      | 0C4h            | 1      | I/O Read       |

Table 6-1: DMA Cycle Type and I/O Address

#### 7.5 ISA Bus SYSCLK Clock Generation

The W83628AG generates the ISA SYSCLK clock using PCI clock signal. A PCICLK divisor (3, 4) is programmable through PCI configuration register to generate the ISA SYSCLK clock signal. This provides ISA SYSCLK frequencies 8.33MHz and 11MHz of a typical 33MHz PCICLK.

#### 7.6 ISA Bus I/O Recovery Time

The W83628AG supports 8-bit/16-bit I/O recovery time for back-to-back ISA I/O cycles. The register can be programmed through Type0 PCI configuration cycle.

#### 7.7 NOGO

The W83628AG and W83629AG also support NOGO function. The NOGO signal generally connected to South Bridge chipset's NOGO signal is used to disable the subtractive decode function when NOGO signal is asserted high during system boot-up, since there is only one subtractive decode device presented on the PCI bus.

#### 8. PIN CONFIGURATION

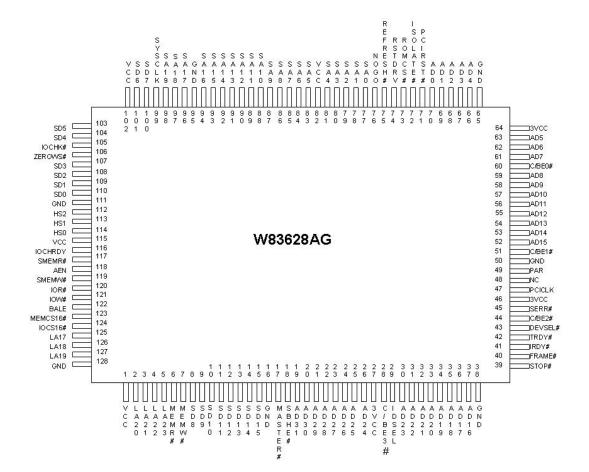

#### 8.1 PIN CONFIGURATION FOR W83628AG

Publication Release Date: January, 2008 Revision 1.2

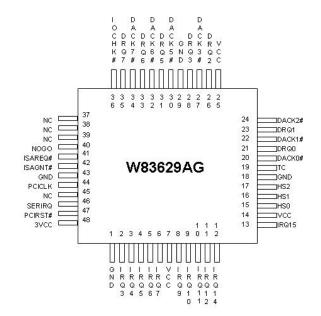

8.2 PIN CONFIGURATION FOR W83629AG

#### 9. PIN DESCRIPTION

Note: Please refer to Section 10 DC CHARACTERISTICS for details.

| I/O10t             | - TTL level bi-directional pin with 10 mA source-sink capability            |

|--------------------|-----------------------------------------------------------------------------|

| I/O18t             | - TTL level bi-directional pin with 18 mA source-sink capability            |

| I/O10tp3           | - 3.3V TTL level bi-directional pin with 10 mA source-sink capability       |

| I/O18tp3           | - 3.3V TTL level bi-directional pin with 18 mA source-sink capability       |

| I/OD10t            | - TTL level bi-directional pin open drain output with 10 mA sink capability |

| I/OD18t            | - TTL level bi-directional pin open drain output with 18 mA sink capability |

| OUT <sub>10t</sub> | - TTL level output pin with 10 mA source-sink capability                    |

| OUT <sub>18t</sub> | - TTL level output pin with 18 mA source-sink capability                    |

| OD10               | - Open-drain output pin with 10 mA sink capability                          |

| INt                | - TTL level input pin                                                       |

| INts               | - TTL level Schmitt-trigger input pin                                       |

|                    |                                                                             |

#### 9.1 W83628AG PIN DESCRIPTION

#### 9.1.1 PCI Interface

| SYMBOL     | PIN   | I/O      | FUNCTION                                                                                                                                                                                                                                   | LEVEL |

|------------|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|            | 19-26 |          |                                                                                                                                                                                                                                            |       |

|            | 30-37 |          | PCI Bus Address and Data Signals. The standard                                                                                                                                                                                             |       |

| AD[31:0]   | 52-59 | I/O18tp3 | PCI address and data lines. The address is driven<br>with FRAME# assertion; the data is driven or                                                                                                                                          | 3.3V  |

|            | 61-63 |          | received in following clocks.                                                                                                                                                                                                              |       |

|            | 66-70 |          |                                                                                                                                                                                                                                            |       |

|            | 28,44 |          | PCI Bus Command and Byte Enables. During the                                                                                                                                                                                               |       |

| C/BE[3:0]# |       | I/O18tp3 | address phase of a transaction, C/BE[3:0]# define the bus command. During the data phase,                                                                                                                                                  | 3.3V  |

|            | 51,60 |          | C/BE[3:0]# are used as Byte Enables.                                                                                                                                                                                                       |       |

| PCICLK     | 47    | INts     | <b>PCI Bus System Clock</b> . PCICLK provides timing<br>for all transactions on the PCI bus. All the other PCI<br>signals are sampled on the rising edge of PCICLK,<br>and all timing parameters are defined with respect<br>to this edge. | 3.3V  |

## nuvoTon

#### 8.1.1 PCI Interface, contiuned

| SYMBOL  | PIN | I/O                  | FUNCTION                                                                                                                                                                                                        | LEVEL |

|---------|-----|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| FRAME#  | 40  | I/O <sub>18tp3</sub> | <b>Frame Signal</b> . FRAME# is driven by the current PCI bus master to indicate the beginning and duration of an access.                                                                                       | 3.3V  |

| IDSEL   | 29  | IN <sub>ts</sub>     | <b>Initialization Device Select.</b> IDSEL is used as a chip select during configuration read and write transactions. This signal should be externally tied to one of the upper 21 address signals.             | 3.3V  |

| STOP#   | 39  | I/O <sub>10tp3</sub> | <b>Bus Stop#.</b> STOP# indicates the current target is requesting the master to stop the current PCI bus transaction.                                                                                          | 3.3V  |

| IRDY#   | 41  | I/O10tp3             | <b>Initiator Ready.</b> IRDY# indicates the initiating agent's ability to complete the current data phase of the PCI bus transaction.                                                                           | 3.3V  |

| TRDY#   | 42  | I/O10tp3             | <b>Target Ready.</b> TRDY# indicates the target agent's ability to complete the current data phase of the PCI bus transaction.                                                                                  | 3.3V  |

| DEVSEL# | 43  | I/O10tp3             | <b>Device Select.</b> The W83628AG drives DEVSEL# to indicate that it is the target of the current PCI bus transaction. The W83628AG uses subtractive decoding and the NOGO protocol to claim PCI transactions. | 3.3V  |

| SERR#   | 45  | OD10                 | <b>System Error.</b> SERR# can be pulsed active by any PCI agent that detects a system error condition.                                                                                                         | 3.3V  |

| PAR     | 49  | I/O10tp3             | <b>Parity Signal.</b> The W83628AG generates even parity across AD[31:0] and C/BE[3:0]#.                                                                                                                        | 3.3V  |

| PCIRST# | 71  | IN <sub>ts</sub>     | <b>PCI Reset.</b> The W83628AG receives PCIRST# as a reset from the PCI Bus.                                                                                                                                    | 3.3V  |

| SYMBOL   | PIN     | I/O              | FUNCTION                                                                                                                                                                                                                                                  | LEVEL |

|----------|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|          |         |                  | <b>Handshaking Signals.</b> HS[2:0] are connected to the W83629AG for PCI to ISA SET handshaking signals.                                                                                                                                                 |       |

| HS[2:0]  | 112-114 | I/O10t           | HS1 is handshaking Signal 1; this pin is weak<br>pulled-down while PCIRST# is asserted.<br>Applying a pull-up resistor (4.7Kohm) to this pin<br>disables ISA bridge subtraction decoder.                                                                  | 5V    |

| ISOLATE# | 72      | IN <sub>ts</sub> | <b>Isolation Control Input. Isolate#</b> is an active low signal by user programming to control all of the output signals of the W83628AG to Isolation and Tri-state.                                                                                     | 3.3V  |

| NOGO     | 76      | INt              | <b>NOGO</b> , This signal indicates which master initiates<br>the current transaction and whether or not the<br>current bus cycle is targeted for the ISA bus. This<br>signal is a point-to-point connection between PCI<br>HOST Bridge and the W83628AG. | 5V    |

#### 9.1.2 Control Logic and Handshaking Signals

#### 9.1.3 ISA Interface Signals

| SYMBOL    | PIN                                      | I/O                | FUNCTION                                                                                                                                                                                      | LEVEL |

|-----------|------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| SA[19:17] | 98-96                                    | I/O18t             | System Address Bus. These are the upper<br>address lines that define the ISA's byte granular<br>address space (up to 1 Mbyte). SA[19:17] are at an<br>unknown state upon PCIRST#.             | 5V    |

| SA[16:0]  | 94-83<br>81-77                           | I/O18t             | <b>System Address Bus.</b> These are the bi-directional lower address lines that define the ISA's byte granular address space (up to 1 Mbyte). SA[16:0] are at an unknown state upon PCIRST#. | 5V    |

| SD[15:0]  | 110-107,<br>104,103,<br>101,100,<br>8-15 | I/O18t             | <b>System Data.</b> SD[15:0] provide the 16-bit data path for devices residing on the ISA Bus. The W83628AG tri-states SD[15:0] during PCIRST#.                                               | 5V    |

| AEN       | 118                                      | OUT <sub>18t</sub> | Address Enable. AEN is asserted during DMA cycles. This signal is also driven high when the W83628AG initiates refresh cycles. AEN is driven low upon PCIRST#.                                | 5V    |

| IOR#      | 120                                      | I/O18t             | I/O Read. IOR# is the command to an ISA I/O slave device that the slave may drive data on to the ISA data bus (SD[15:0]).                                                                     | 5V    |

## nuvoTon

| SYMBOL    | PIN            | I/O                | FUNCTION                                                                                                                                                                                                                              | LEVEL |

|-----------|----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| IOW#      | 121            | I/O18t             | <b>I/O Write.</b> IOW# is the command to an ISA I/O slave device that the slave may latch data from the ISA data bus (SD[15:0]).                                                                                                      | 5V    |

| IOCHRDY   | 116            | I/O18t             | <b>I/O Channel Ready.</b> Resources on the ISA Bus negate IOCHRDY to indicate that additional time (wait states) is required to complete the cycle.                                                                                   | 5V    |

| SYSCLK    | 99             | OUT18t             | <b>ISA System Clock.</b> SYSCLK is the reference clock for the ISA bus. The SYSCLK is generated by dividing PCICLK by 3 or 4.                                                                                                         | 5V    |

| RSTDRV    | 74             | OUT <sub>18t</sub> | <b>Reset Drive.</b> The W83628AG asserts RSTDRV to reset devices that reside on the ISA Bus. The W83628AG asserts this signal while the PCIRST# is asserted.                                                                          | 5V    |

| IOCS16#   | 124            | INt                | <b>16-bit I/O Chip Select.</b> This signal is driven by I/O devices on the ISA Bus to indicate that they support 16-bit I/O bus cycles.                                                                                               | 5V    |

| SBHE#     | 18             | I/O18t             | <b>System Byte High Enable.</b> SBHE# asserted indicates that a byte is being transferred on the upper byte (SD[15:8]) of the data bus. SBHE# is at an unknown state upon PCIRST#.                                                    | 5V    |

| IOCHK#    | 105            | INt                | I/O Channel Check. IOCHK# can be driven by any resource on the ISA bus during the detection of an error.                                                                                                                              | 5V    |

| MEMR#     | 6              | I/O18t             | <b>Memory Read.</b> MEMR# asserted indicates the current ISA bus cycle is a memory read.                                                                                                                                              | 5V    |

| MEMW#     | 7              | I/O18t             | <b>Memory Write.</b> MEMW# asserted indicates the current ISA bus cycle is a memory write.                                                                                                                                            | 5V    |

| MASTER#   | 17             | INt                | <b>MASTER#.</b> This signal is used with a DREQ line by an ISA master to gain control over the ISA Bus.                                                                                                                               | 5V    |

| LA[23:17] | 5-2<br>127-125 | I/O18t             | <b>Unlatched Address.</b> The LA[23:17] address lines<br>are bi-directional. These address lines allow<br>accesses to physical memory on the ISA Bus up to<br>16 Mbytes. LA[23:17] are outputs when the<br>W83628AG owns the ISA Bus. | 5V    |

## nuvoTon

| SYMBOL   | PIN | I/O                | FUNCTION                                                                                                                                                                                                                                                                                                                                                             | LEVEL |

|----------|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| ROMCS#   | 73  | I/O10t             | ROMCS#. This pin is weak pulled-down while<br>PCIRST is asserted. Applying a pull-up resistor<br>(4.7K ohm) to this pin enables positive decoder<br>of BIOS address range (depending on Configure<br>register 70, bit 3,2). When the BIOS access<br>range is enabled, the pin is BIOS ROMCS#<br>output.                                                              | 5V    |

| REFRESH# | 75  | I/O18t             | <b>Refresh.</b> REFRESH# asserted indicates that a refresh cycle is in progress, or that an ISA master is requesting the W83628AG to generate a refresh cycle. Upon PCIRST#, this signal is tri-stated.                                                                                                                                                              | 5V    |

| ZEROWS#  | 106 | INt                | <b>Zero Wait States.</b> An ISA slave asserts ZEROWS# after its address and command signals are decoded to indicate that the current cycle can be executed as an ISA zero wait state cycle. ZEROWS# has no effect during 16-bit I/O cycles.                                                                                                                          | 5V    |

| SMEMR#   | 117 | OUT <sub>18t</sub> | <b>Standard Memory Read.</b> SMEMR# asserted indicates the current ISA bus cycle is a memory read cycle to an address below 1 Mbyte.                                                                                                                                                                                                                                 | 5V    |

| SMEMW#   | 119 | OUT <sub>18t</sub> | <b>Standard Memory Write.</b> SMEMW# asserted indicates the current ISA bus cycle is a memory write cycle to an address below 1 Mbyte.                                                                                                                                                                                                                               | 5V    |

| BALE     | 122 | OUT <sub>18t</sub> | <b>Bus Address Latch Enable.</b> BALE is an active<br>high signal asserted by the W83628AG to indicate<br>that the address (SA[19:0], LA[23:17]) and SBHE#<br>signal lines are valid.<br>The LA[23:17] address lines are latched on the<br>trailing edge of BALE. BALE remains asserted<br>throughout DMA and ISA master cycles. BALE is<br>driven low upon PCIRST#. | 5V    |

| MEMCS16# | 123 | I/OD18t            | <b>Memory Chip Select 16.</b> MEMCS16# asserted indicates that the memory slave supports 16-bit accesses.                                                                                                                                                                                                                                                            | 5V    |

#### 9.1.4 Power Signals

| SYMBOL | PIN                             | I/O | FUNCTION     | LEVEL |

|--------|---------------------------------|-----|--------------|-------|

| VCC    | 1, 82, 102, 115                 | PWR | 5V Supply.   | 5V    |

| 3VCC   | 27, 46, 64                      | PWR | 3.3V Supply. | 3.3V  |

| GND    | 16, 38, 50, 65, 95,<br>111, 128 | PWR | Ground.      | 0V    |

#### 9.1.5 NC Pins

| SYMBOL | PIN | I/O | FUNCTION       | LEVEL |

|--------|-----|-----|----------------|-------|

| NC     | 48  |     | No Connection. |       |

#### 9.2 W83629AG PIN DESCRIPTION

| SYMBOL  | PIN   | I/O              | FUNCTION                                                                                                                                                                                                                                      | LEVEL |

|---------|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| HS[2:0] | 17-15 | I/O10t           | <b>Handshaking Signals.</b> HS[2:0] are connected to the W83628AG for PCI to ISA SET handshaking signals.                                                                                                                                     | 5V    |

| NOGO    | 40    | INts             | <b>NO GO.</b> This signal indicates which master initiates the current transaction and whether or not the current bus cycle is targeted for the ISA bus. This signal is a point-to-point connection between PCI HOST Bridge and the W83628AG. | 5V    |

| PCICLK  | 44    | INts             | <b>PCI Bus System Clock</b> . PCICLK provides timing<br>for all transactions on the PCI bus. All the other<br>PCI signals are sampled on the rising edge of<br>PCICLK, and all timing parameters are defined<br>with respect to this edge.    | 3.3V  |

| PCIRST# | 47    | IN <sub>ts</sub> | <b>PCI Reset.</b> The W83628AG receives PCIRST# as a reset from the PCI Bus.                                                                                                                                                                  | 3.3V  |

#### 9.2.1 Control Logic and Handshaking Signals

#### 9.2.2 PC/PCI Interface

| SYMBOL           | PIN                          | I/O                | FUNCTION                                                                                                                                                                                                     | LEVEL |

|------------------|------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| ISAREQ#          | 41                           | OUT <sub>18t</sub> | <b>ISA Bus Request.</b> This signal is a point-to-point signal between the W83629AG and a PCI HOST arbiter. The W83629AG asserts this signal according to the PC/PCI protocol.                               | 3.3V  |

| ISAGNT#          | 42                           | INts               | <b>ISA Bus Grant.</b> This signal is a point-to-point signal between the W83629AG and a PCI HOST Bridge's secondary bus PCPCIGNT# signal. The W83629AG asserts this signal according to the PC/PCI protocol. | 3.3V  |

| DRQ<br>[7:5,3:0] | 35,33,31,<br>28,26,23,<br>21 | INt                | <b>DMA Request.</b> The DREQ signal indicates that either a slave DMA device is requesting DMA services, or an ISA bus master is requesting to use the ISA bus.                                              | 5V    |

## nuvoTon

| SYMBOL             | PIN                          | I/O                | FUNCTION                                                                                                                     | LEVEL |

|--------------------|------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------|-------|

| DACK<br>[7:5,3:0]# | 34,32,30,<br>27,24,22,<br>20 | OUT <sub>18t</sub> | <b>DMA Acknowledge.</b> The DACK# signal indicates that either a DMA channel or an ISA bus master is granted to the ISA bus. | 5V    |

| тс                 | 19                           | OUT <sub>18t</sub> | <b>Terminal Count.</b> The W83628AG asserts TC to DMA slaves as a terminal count indicator.                                  | 5V    |

#### 9.2.3 IRQ Serializer Interface

| SYMBOL              | PIN         | I/O     | FUNCTION                                                                                                              | LEVEL |

|---------------------|-------------|---------|-----------------------------------------------------------------------------------------------------------------------|-------|

| SERIRQ              | 46          | I/OD10t | Serial Interrupt Requested Signals. This signal is to transfer IRQ from the parallel IRQ mode to the serial IRQ mode. | 3.3V  |

| IRQ[3:7,9:12,14,15] | 2-6<br>8-13 | INt     | Parallel Interrupt Requested Input.                                                                                   | 5V    |

| ЮСНК#               | 36          | INt     | <b>I/O Channel Check.</b> IOCHK# can be driven<br>by any resource on the ISA bus with the<br>detection of an error.   | 5V    |

#### 9.2.4 Power Signals

| SYMBOL | PIN           | I/O | FUNCTION     | LEVEL |

|--------|---------------|-----|--------------|-------|

| VCC    | 7, 14, 25     | PWR | 5V Supply.   | 5V    |

| 3VCC   | 48            | PWR | 3.3V Supply. | 3.3V  |

| GND    | 1, 18, 29, 43 | PWR | Ground.      | 0V    |

#### 9.2.5 NC Pins

| SYMBOL | PIN            | I/O | FUNCTION      | LEVEL |

|--------|----------------|-----|---------------|-------|

| NC     | 37, 38, 39, 45 |     | No Connection |       |

#### **10. PCI CONFIGURATION REGISTERS**

#### 10.1 VID-VENDOR IDENTIFICATION REGISTER

| Address Offset: | 01h_00h   |

|-----------------|-----------|

| Default Value:  | 10h_50h   |

| Attribute:      | Read only |

This register is read-only and contains Nuvoton vendor identification number (1050h).

#### 10.2 DID-DEVICE IDENTIFICATION REGISTER

Default Value: 06h\_28h

Attribute: Read only

This register is read-only and contains the device identification number (0628h).

#### 10.3 PCICMD-PCI COMMAND REGISTER

| Address Offset: | 05h_04h    |

|-----------------|------------|

| Default Value:  | 00h_07h    |

| Attribute:      | Read/Write |

This register provides control over the ISA bridge to generate and respond to PCI cycles properly. When a 0 is written to this register, the ISA bridge is to be disconnected from the PCI bus for all accesses except configuration accesses.

#### Bit 15:10 Reserved.

Bit 9 Fast Back to Back. This bit always returns a zero.

- =1 Enable.

- =0 Disable.

- Bit 7 Wait Cycle Control (Not supported).

Hardwired to zero.

Bit 6 Parity Error Response (Not supported).

Hardwired to zero.

Bit 5 VGA Palette Snoop Enable (Not supported).

Hardwired to zero.

## nuvoTon

| Bit 4                                                              | Memory Write and Invalidate Enable (Not supported).                                                                                       |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                    | Hardwired to zero.                                                                                                                        |

| Bit 3                                                              | Parity Error Response (Not supported).                                                                                                    |

|                                                                    | Hardwired to zero.                                                                                                                        |

| Bit 2                                                              | Bus Master Enable                                                                                                                         |

|                                                                    | Hardwired to one. The ISA bridge Bus Masters are always supported to generate a PCI Bus master cycle.                                     |

| Bit 1                                                              | Memory Space Enable                                                                                                                       |

|                                                                    | Hardwired to one. The ISA bridge Memory space is always enabled.                                                                          |

| Bit 0                                                              | I/O Space Enable                                                                                                                          |

|                                                                    | Hardwired to one. The ISA bridge I/O space is always enabled.                                                                             |

| 10.4                                                               | PCISTS-PCI STATUS REGISTER                                                                                                                |

| Address Offset:                                                    | 07h_06h                                                                                                                                   |

| Default Value:                                                     | 02h_00h                                                                                                                                   |

| Attribute:                                                         | Read/Write                                                                                                                                |

| This register shows status information for PCI bus related events. |                                                                                                                                           |

| Bit 15                                                             | Detected Parity Error                                                                                                                     |

|                                                                    | Hardwired to zero. The ISA bridge does not check bus parity.                                                                              |

| Bit 14                                                             | Signaled System Error                                                                                                                     |

|                                                                    | This bit is set when ISA bridge asserts SERR# on PCI bus.                                                                                 |

| Bit 13                                                             | Received Master Abort Status                                                                                                              |

|                                                                    | This bit is set when the ISA bridge is target aborted as a master on the PCI bus.<br>Software sets this bit to 0 by writing a 1 to it.    |

| Bit 12                                                             | Received Target Abort Status                                                                                                              |

|                                                                    | This bit is set when the ISA bridge target aborts a PCI transaction as a target.<br>Software sets this bit to 0 by writing a 1 to it.     |

| Bit 11                                                             | Signaled Target Abort Status                                                                                                              |

|                                                                    | This bit is set when the ISA bridge signals a target abortion for a PCI transaction.<br>Software sets this bit to 0 by writing a 1 to it. |

| Bit 10:9                                                           | DEVSEL# Timing. This 2 bits always return a 01b (medium decode).                                                                          |

| Bit 8                                                              | Data Parity Detected (Not supported)                                                                                                      |

|                                                                    | Hardwired to zero.                                                                                                                        |

|                                                                    |                                                                                                                                           |