# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Winbond LPC I/O W83637HF W83637HG

Revision: 1.6 Date: 2006/03/22

|    | PAGES        | DATES      | VERSION | MAIN CONTENTS                                                   |

|----|--------------|------------|---------|-----------------------------------------------------------------|

| 1  | N. A.        | 03/25/2001 | 0.50    | No Released.<br>For Winbond Internal use only.                  |

| 2  |              | 08/09/2001 | 0.60    | First published.                                                |

| 3  |              | 02/18/2002 | 0.70    | Update Chapter 10. (Hardware Monitor Device)                    |

| 4  |              | 08/28/2002 | 1.0     | New update                                                      |

| 5  |              | 09/27/2002 | 1.1     | ADD Secure Digital Function Description                         |

| 6  | 7<br>100~101 | 04/15/2003 | 1.2     | ADD Block Digram<br>ADD Chapter 4.1 Plug and Play Configuration |

| 7  | 130~137      | 06/25/2003 | 1.3     | Add Chapter 9 DC Specification                                  |

| 8  | N.A.         | 11/23/2005 | 1.4     | Add Pb-free package                                             |

| 9  | N.A.         | 02/10/2006 | 1.5     | Remove 5VSB H/W monitor sensor function.                        |

| 10 | Page.5       | 03/23/2006 | 1.6     | Correct GPIO pins to 21-pin, not 40-pin                         |

### **Revision History**

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this data sheet belong to their respective owners.

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

### Tables of Contents-

| 1. | GENERAL DESCRIPTION 1 |          |                                                  |    |  |  |  |  |  |

|----|-----------------------|----------|--------------------------------------------------|----|--|--|--|--|--|

| 2. | FEATL                 | JRES     |                                                  | 3  |  |  |  |  |  |

| 3. | BLOCK DIAGRAM         |          |                                                  |    |  |  |  |  |  |

| 4. | PIN CONFIGURATION     |          |                                                  |    |  |  |  |  |  |

| 5. | PIN DE                | ESCRIPTI | ON                                               |    |  |  |  |  |  |

|    | 5.1                   |          | LPC Interface                                    | 10 |  |  |  |  |  |

|    | 5.2                   |          | FDC Interface                                    | 11 |  |  |  |  |  |

|    | 5.3                   |          | Multi-Mode Parallel Port                         | 12 |  |  |  |  |  |

|    | 5.4                   |          | Serial Port Interface                            | 17 |  |  |  |  |  |

|    | 5.5                   |          | KBC Interface                                    | 18 |  |  |  |  |  |

|    | 5.6                   |          | ACPI Interface                                   | 19 |  |  |  |  |  |

|    | 5.7                   |          | Hardware Monitor Interface                       | 19 |  |  |  |  |  |

|    | 5.8                   |          | Game Port & MIDI Port                            | 20 |  |  |  |  |  |

|    | 5.9                   |          | Card Reader Interface                            | 21 |  |  |  |  |  |

|    |                       | 5.9.1    | Smart Card Interface                             | 21 |  |  |  |  |  |

|    |                       | 5.9.2    | MS/SD Card Interface                             | 21 |  |  |  |  |  |

|    | 5.10                  |          | General Purpose I/O Port                         | 22 |  |  |  |  |  |

|    |                       | 5.10.1   | General Purpose I/O Port 1 (Power source is Vcc) | 22 |  |  |  |  |  |

|    |                       | 5.10.2   | General Purpose I/O Port 2 (Power source is Vcc) | 22 |  |  |  |  |  |

|    |                       | 5.10.3   | General Purpose I/O Port 3 (Power source is VSB) |    |  |  |  |  |  |

|    | 5.11                  |          | Power Pins                                       | 23 |  |  |  |  |  |

| 6. | HARD                  | WARE MO  | DNITOR                                           | 24 |  |  |  |  |  |

|    | 6.1                   |          | General Description                              | 24 |  |  |  |  |  |

|    | 6.2                   |          | Access Interface                                 | 24 |  |  |  |  |  |

|    |                       | 6.2.1    | LPC interface                                    | 24 |  |  |  |  |  |

|    | 6.3                   |          | Analog Inputs                                    | 26 |  |  |  |  |  |

|    |                       | 6.3.1    | Monitor over 4.096V voltage                      | 27 |  |  |  |  |  |

|    |                       | 6.3.2    | CPUVCORE voltage detection method                |    |  |  |  |  |  |

|    |                       | 6.3.3    | Temperature Measurement Machine                  |    |  |  |  |  |  |

|    | 6.4                   |          | FAN Speed Count and FAN Speed Control            | 29 |  |  |  |  |  |

|    |                       | 6.4.1    | Fan speed count                                  |    |  |  |  |  |  |

|    |                       | 6.4.2    | Fan speed control                                |    |  |  |  |  |  |

|    | 6.5                   |          | Smart Fan Control                                |    |  |  |  |  |  |

|    |                       | 6.5.1    | Thermal Cruise mode                              | -  |  |  |  |  |  |

|    |                       | 6.5.2    | Fan Speed Cruise mode                            |    |  |  |  |  |  |

|    |                       | 6.5.3    | Manual Control Mode                              | 34 |  |  |  |  |  |

|    | 6.6    |          | SMI# Interrupt Mode                                                                                                                 | 34   |

|----|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------|------|

|    |        | 6.6.1    | Voltage SMI# mode                                                                                                                   |      |

|    |        | 6.6.2    | Fan SMI# mode                                                                                                                       | 34   |

|    |        | 6.6.3    | The W83637HF temperature sensor 1(SYSTIN) SMI# interrupt has two modes                                                              | 35   |

|    |        | 6.6.4    | The W83637HF temperature sensor 2(CPUTIN) and sensor 3(VTIN) SMI# international has two modes and it is programmed at CR[4Ch] bit 6 |      |

|    | 6.7    |          | OVT# Interrupt Mode                                                                                                                 | 37   |

|    | 6.8    |          | Registers and RAM                                                                                                                   | 38   |

| 7. | SMAR   | T CARD F | READER INTERFACE (SCR)                                                                                                              | 81   |

|    | 7.1    |          | Features                                                                                                                            | 81   |

|    | 7.2    |          | Register File                                                                                                                       | 82   |

|    | 7.3    |          | Smart Card ID Number (base address + 2 when BDLAB = 1, fixed at 70h)                                                                | 94   |

|    | 7.4    |          | Functional Description                                                                                                              | 94   |

|    | 7.5    |          | Initialization                                                                                                                      | 94   |

|    | 7.6    |          | Activation                                                                                                                          | 94   |

|    | 7.7    |          | Answer-to-Reset                                                                                                                     | 95   |

|    | 7.8    |          | Data Transfer                                                                                                                       | 95   |

|    | 7.9    |          | Cold Reset and Warm Reset                                                                                                           | 95   |

|    | 7.10   |          | Power States                                                                                                                        | 96   |

|    | 7.11   |          | Disabled State                                                                                                                      | 96   |

|    | 7.12   |          | Active State                                                                                                                        | 96   |

|    | 7.13   |          | Idle State                                                                                                                          | 96   |

|    | 7.14   |          | Power Down State                                                                                                                    | 97   |

| 8. | CONF   | IGURATIO | ON REGISTER                                                                                                                         | 98   |

| 0. | 8.1    |          | Plug and Play Configuration                                                                                                         |      |

|    | 0.1    | 8.1.1    | Compatible PnP                                                                                                                      |      |

|    |        | 8.1.2    | Configuration Sequence                                                                                                              |      |

|    | 8.2    |          | The PNP ID of the W83637HF/HG Card Reader Device (For E                                                                             |      |

|    | Progra | mming us | ;e)                                                                                                                                 |      |

|    | 8.3    |          | Chip (Global) Control Register                                                                                                      | .101 |

|    |        | 8.3.1    | Logical Device 0 (FDC)                                                                                                              | 106  |

|    |        | 8.3.2    | Logical Device 1 (Parallel Port)                                                                                                    | 110  |

|    |        | 8.3.3    | Logical Device 2 (UART A)                                                                                                           |      |

|    |        | 8.3.4    | Logical Device 3 (UART B)                                                                                                           |      |

|    |        | 8.3.5    | Logical Device 5 (KBC)                                                                                                              |      |

|    |        | 8.3.6    | Logical Device 6 (CIR)                                                                                                              |      |

|    |        | 8.3.7    | Logical Device 7 (Game Port and MIDI Port and GPIO Port 1)                                                                          |      |

|    |        | 8.3.8    | Logical Device 8 (GPIO Port 2 This power of the Port is VCC source)                                                                 |      |

|    |        | 8.3.9    | Logical Device 9 (GPIO Port 3 This power of the Port is standby source (VSB) )                                                      | 117  |

|     | 8.4                              | Logical Device A (ACPI)                 | .118 |  |  |  |  |  |

|-----|----------------------------------|-----------------------------------------|------|--|--|--|--|--|

|     | 8.5                              | Logical Device B (Hardware Monitor)     | .126 |  |  |  |  |  |

|     | 8.6                              | Logical Device C (Smart Card interface) | .126 |  |  |  |  |  |

|     | 8.7                              | Logical Device D (MS/SD Card Interface) | .127 |  |  |  |  |  |

| 9.  | ELECTRICAL C                     | HARACTERISTICS                          | .129 |  |  |  |  |  |

|     | 9.1                              | Absolute Maximum Ratings                | .129 |  |  |  |  |  |

|     | 9.2                              | DC Characteristics                      | .129 |  |  |  |  |  |

| 10. | ORDERING INS                     | TRUCTION                                | .137 |  |  |  |  |  |

| 11. | HOW TO READ THE TOP MARKING      |                                         |      |  |  |  |  |  |

| 12. | PACKAGE DIMENSIONS               |                                         |      |  |  |  |  |  |

| 13. | APPENDIX A: APPLICATION CIRCUITS |                                         |      |  |  |  |  |  |

### 1. GENERAL DESCRIPTION

W83637HF/HG is the new generation of Winbond's LPC I/O products. It is an evolving product from Winbond's most popular LPC I/O chip W83627HF/HG – which integrates the disk driver adapter, serial port (UART), keyboard controller (KBC), SIR, CIR, game port, MIDI port, hardware monitor, ACPI, On Now Wake-Up – plus additional new features: the Smart Card reader interface and Memory Stick <sup>TM</sup> reader interface.

The Smart Card application is gaining more and more attention; it provides a very high-grade security and convenience in Internet transaction, banking, telephony, electronic payments, etc. W83637HF/HG supports a smart card reader interface featuring Smart wake-up function. This smart card reader interface fully meets the ISO7816 and PC/SC (Personal Computer/Smart Card Workgroup) standards. W83637HF/HG provides a minimum external components and lowest cost solution for smart card applications.

W83637HF/HG implements a standard Memory Stick<sup>™</sup> reader interface. The Memory Stick<sup>™</sup> has been a new mainstream media for storing and transferring data. It's ultra-small size and high storage capacity make it can be used in very wide variety products, including the Audio, Video and PC.

The disk drive adapter functions of W83637HF/HG include a floppy disk drive controller compatible with the industry standard 82077/765, data separator, write pre-compensation circuit, decode logic, data rate selection, clock generator, drive interface control logic, and interrupt and DMA logic. The wide range of functions integrated onto the W83637HF/HG greatly reduces the number of components required for interfacing with floppy disk drives. W83637HF/HG supports four 360K, 720K, 1.2M, 1.44M, or 2.88M disk drives and data transfer rates of 250 Kb/s, 300 Kb/s, 500 Kb/s, 1 Mb/s, and 2 Mb/s.

W83637HF/HG provides two high-speed serial communication ports (UARTs), one of which supports serial Infrared communication. Each UART includes a 16-byte send/receive FIFO, a programmable baud rate generator, complete modem control capability, and a processor interrupts system. Both UARTs provide legacy speed with baud rate up to 115.2k bps and also advanced speed with baud rates of 230k, 460k, or 921k bps, which support higher speed modems. In addition, W83637HF/HG provides IR functions: IrDA 1.0 (SIR for 1.152K bps) and TV remote IR (Consumer IR, supporting NEC, RC-5, extended RC-5, and RECS-80 protocols).

W83637HF/HG supports one PC-compatible printer port (SPP), Bi-directional Printer port (BPP) and also Enhanced Parallel Port (EPP) and Extended Capabilities Port (ECP). Through the printer port interface pins, also available are: Extension FDD Mode and Extension 2FDD Mode allowing one or two external floppy disk drives to be connected.

The configuration registers support mode selection, function enable/disable, and power down function selection. Furthermore, the configurable PnP features are compatible with the plug-and-play feature demand of Windows 95/98<sup>TM</sup>, which makes system resource allocation more efficient than ever.

W83637HF/HG provides functions that comply with ACPI (*Advanced Configuration and Power Interface*), which includes support of legacy and ACPI power management through PME# or PSOUT# function pins. For OnNow keyboard Wake-Up, OnNow mouse Wake-Up, and OnNow CIR Wake-Up. W83637HF/HG also has auto power management to reduce the power consumption.

The keyboard controller is based on 8042 compatible instruction set with a 2K Byte programmable ROM and a 256-Byte RAM bank. Keyboard BIOS firmware are available with optional AMIKEY<sup>TM</sup> -2, Phoenix MultiKey/42<sup>TM</sup>, or customer code.

W83637HF/HG provides a set of flexible I/O control functions to the system designer through a set of General Purpose I/O port. These GPIO ports may serve as simple I/O or may be individually configured to provide a predefined alternate function.

W83637HF/HG is made to fully comply with Microsoft PC98 and PC99 Hardware Design Guide. Moreover, W83637HF/HG is made to meet the specification of PC2001's requirement in the power management: ACPI 1.0/1.0b/2.0 and DPM (Device Power Management).

W83637HF/HG contains a game port and a MIDI port. The game port is designed to support 2 joysticks and can be applied to all standard PC game control devices. They are very important for an entertainment or consumer computer.

W83637HF/HG supports hardware status monitoring for personal computers. It can be used to monitor several critical hardware parameters of the system, including power supply voltages, fan speeds, and temperatures, which are very important for a high-end computer system to work stably and properly. Moreover, W83637HF/HG support the Smart Fan control system, including the "Thermal Cruise<sup>TM</sup>" and "Speed Cruise<sup>TM</sup>" functions. Smart Fan can make system more stable and user friendly.

### 2. FEATURES

#### General

- Meet LPC Spec. 1.01

- Support LDRQ#(LPC DMA), SERIRQ (serial IRQ)

- Compliant with Microsoft PC2000/PC2001 Hardware Design Guide

- Support DPM (Device Power Management), ACPI

- Programmable configuration settings

- Single 24 or 48 MHz clock input

### FDC

- Compatible with IBM PC AT disk drive systems

- Variable write pre-compensation with track selectable capability

- Support vertical recording format

- DMA enable logic

- 16-byte data FIFOs

- Support floppy disk drives and tape drives

- Detects all overrun and underrun conditions

- Built-in address mark detection circuit to simplify the read electronics

- FDD anti-virus functions with software write protect and FDD write enable signal (write data signal was forced to be inactive)

- Support up to four 3.5-inch or 5.25-inch floppy disk drives

- Completely compatible with industry standard 82077

- 360K/720K/1.2M/1.44M/2.88M format; 250K, 300K, 500K, 1M, 2M bps data transfer rate

- Support 3-mode FDD, and its Win95/98 driver

### UART

- Two high-speed 16550 compatible UARTs with 16-byte send/receive FIFOs

- MIDI compatible

- Fully programmable serial-interface characteristics:

- --- 5, 6, 7 or 8-bit characters

- --- Even, odd or no parity bit generation/detection

- --- 1, 1.5 or 2 stop bits generation

- Internal diagnostic capabilities:

- --- Loop-back controls for communications link fault isolation

- --- Break, parity, overrun, framing error simulation

- Programmable baud generator allows division of 1.8461 MHz and 24 MHz by 1 to (2<sup>16</sup>-1)

- Maximum baud rate up to 921k bps for 14.769 MHz and 1.5M bps for 24 MHz

#### Infrared

- Support IrDA version 1.0 SIR protocol with maximum baud rate up to 115.2K bps

- Support SHARP ASK-IR protocol with maximum baud rate up to 57,600 bps

- Support Consumer IR

#### **Parallel Port**

- Compatible with IBM parallel port

- Support PS/2 compatible bi-directional parallel port

- Support Enhanced Parallel Port (EPP) Compatible with IEEE 1284 specification

- Support Extended Capabilities Port (ECP) Compatible with IEEE 1284 specification

- Extension FDD mode supports disk drive B; and Extension 2FDD mode supports disk drives A and B through parallel port

- Enhanced printer port back-drive current protection

### **Keyboard Controller**

- 8042 based with optional F/W from AMIKKEY<sup>TM</sup>-2, Phoenix MultiKey/42<sup>TM</sup> or customer code with 2K bytes of programmable ROM, and 256 bytes of RAM

- Asynchronous Access to Two Data Registers and One status Register

- Software compatibility with the 8042

- Support PS/2 mouse

- Support port 92

- Support both interrupt and polling modes

- Fast Gate A20 and Hardware Keyboard Reset

- 8 Bit Timer/ Counter

- Support binary and BCD arithmetic

- 6 MHz, 8 MHz, 12 MHz, or 16 MHz operating frequency

#### **Game Port**

- Support two separate Joysticks

- Support every Joystick two axis (X, Y) and two button (A, B) controllers

#### **MIDI Port**

- The baud rate is 31.25 K baud

- 16-byte input FIFO

- 16-byte output FIFO

#### Winbond Electronics Corp.

#### General Purpose I/O Ports

- 21 programmable general purpose I/O ports

- General purpose I/O ports can serve as simple I/O ports, interrupt steering inputs, watching dog timer output, power LED output, infrared I/O pins, KBC control I/O pins, suspend LED output, RSMRST# signal, PWROK signal, STR (suspend to DRAM) function, VID control function,

#### **OnNow Functions**

- Keyboard Wake-Up by programmable keys

- Mouse Wake-Up by programmable buttons

- CIR Wake-Up by programmable keys

- SMART Card Wake-up by SCPSNT

- On Now Wake-Up from all of the ACPI sleeping states (S1-S5)

#### **Smart Card Reader Interface**

- PC/SC T=0, T=1 compliant

- ISO7816 protocol compliant

- With 16-byte send/receive FIFOs

- Programmable baud generator

- Standard drivers for Windows 98 ME<sup>™</sup>, Windows 2000<sup>™</sup>

### Memory Stick<sup>™</sup> Reader Interface

• Meet SONY Memory Stick<sup>™</sup> Specification Version 1.03

#### **Hardware Monitor Functions**

- Smart fan control system, support "Thermal Cruise<sup>™</sup>" and "Speed Cruise<sup>™</sup>"

- 3 thermal inputs from optionally remote thermistors or 2N3904 transistors or Pentium<sup>™</sup> II/III/4 thermal diode output

- 3 positive voltage inputs (typical for +5V, +3.3V, Vcore)

- 1 intrinsic voltage monitoring (typical for Vbat)

- 3 fan speed monitoring inputs

- 3 fan speed control

- Build in Case open detection circuit

- WATCHDOG comparison of all monitored values

- Programmable hysteresis and setting points for all monitored items

- Over temperature indicate output

- Automatic Power On voltage detection Beep

- Issue SMI#, IRQ, OVT# to activate system protection

- Winbond Hardware Doctor<sup>™</sup> Support

- Intel LDCM<sup>TM</sup> / Acer ADM<sup>TM</sup> compatible

### Package

• 128-pin PQFP

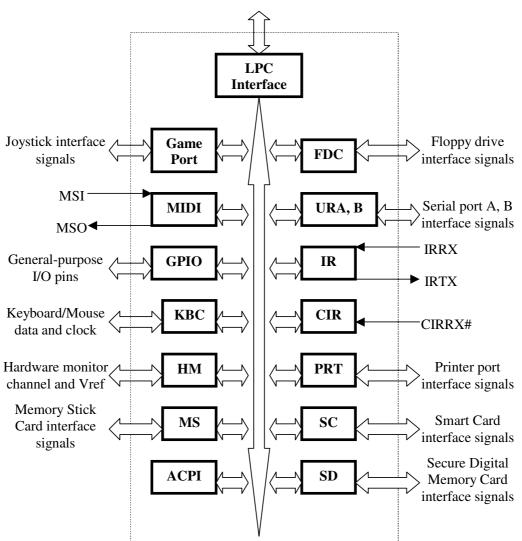

### 3. BLOCK DIAGRAM

LRESET#, LCLK, LFRAME#, LAD[3:0], LDRQ#, SERIRQ

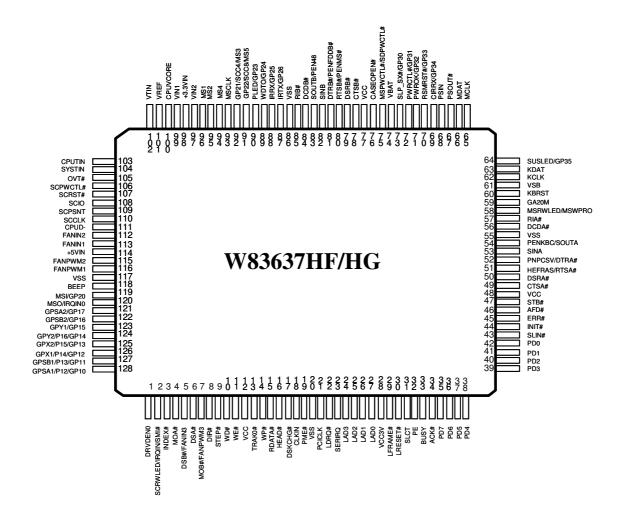

### 4. PIN CONFIGURATION

#### **Unbond** Electronics Corp.

### 5. PIN DESCRIPTION

|           | PIN DESCRIPTION                                                                                                                  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------|

| I/O12t    | TTL level bi-directional pin with 12 mA source-sink capability.                                                                  |

| I/O24t    | TTL level bi-directional pin with 24 mA source-sink capability.                                                                  |

| I/O12ts   | TTL level Schmitt-trigger bi-directional pin with 12 mA source-sink capability.                                                  |

| I/O24ts   | TTL level Schmitt-trigger bi-directional pin with 24 mA source-sink capability.                                                  |

| I/OD12t   | TTL level bi-directional pin and open drain output with 12 mA sink capability.                                                   |

| I/OD24t   | TTL level bi-directional pin and open drain output with 24 mA sink capability.                                                   |

| I/OD12ts  | TTL level Schmitt-trigger bi-directional pin and open drain output with 12 mA sink capability.                                   |

| I/OD24ts  | TTL level Schmitt-trigger bi-directional pin and open drain output with 24 mA sink capability.                                   |

| I/OD12cs  | CMOS level Schmitt-trigger bi-directional pin and open drain output with 12 mA sink capability.                                  |

| I/OD16cs  | CMOS level Schmitt-trigger bi-directional pin and open drain output with 16 mA sink capability.                                  |

| I/OD12csd | CMOS level Schmitt-trigger bi-directional pin with internal pull down resistor and open drain output with 12 mA sink capability. |

| I/OD12csu | CMOS level Schmitt-trigger bi-directional pin with internal pull up resistor and open drain output with 12 mA sink capability.   |

|           |                                                                                                                                  |

| O4t       | TTL level output pin with 4 mA source-sink capability.                                                                           |

| O12t      | TTL level output pin with 12 mA source-sink capability.                                                                          |

| O16t      | TTL level output pin with 16 mA source-sink capability.                                                                          |

| O24t      | TTL level output pin with 24 mA source-sink capability.                                                                          |

| O24ts     | TTL level Schmitt-trigger output pin with 24 mA source-sink capability.                                                          |

| OD12t     | TTL level open drain output pin with 12 mA sink capability.                                                                      |

| OD24t     | TTL level open drain output pin with 24 mA sink capability.                                                                      |

| O8c       | CMOS level output pin with 8 mA source-sink capability.                                                                          |

|           |                                                                                                                                  |

| INt       | TTL level input pin.                                                                                                             |

| INts      | TTL level Schmitt-trigger input pin.                                                                                             |

| INtu      | TTL level input pin with internal pull up resistor.                                                                              |

| INc       | CMOS level input pin.                                                                                                            |

| INcd      | CMOS level input pin with internal pull down resistor.                                                                           |

| INcsu     | CMOS level Schmitt-trigger input pin with internal pull up resistor.                                                             |

### 5.1 LPC Interface

| SYMBOL   | PIN   | I/O                | FUNCTION                                                                                                                        |

|----------|-------|--------------------|---------------------------------------------------------------------------------------------------------------------------------|

| CLKIN    | 18    | INt                | System clock input. According to the input frequency 24MHz or 48MHz, it is selectable through register. Default is 24MHz input. |

| PME#     | 19    | OD <sub>12t</sub>  | Generated PME event.                                                                                                            |

| PCICLK   | 21    | IN <sub>ts</sub>   | PCI clock input.                                                                                                                |

| LDRQ#    | 22    | O <sub>12t</sub>   | Encoded DMA Request signal.                                                                                                     |

| SERIRQ   | 23    | I/O12t             | Serial IRQ input/Output.                                                                                                        |

| LAD[3:0] | 24-27 | I/O <sub>12t</sub> | These signal lines communicate address, control, and data information over the LPC bus between a host and a peripheral.         |

| LFRAME#  | 29    | IN <sub>ts</sub>   | Indicates start of a new cycle or termination of a broken cycle.                                                                |

| LRESET#  | 30    | IN <sub>ts</sub>   | Reset signal. It can connect to PCIRST# signal on the host.                                                                     |

### 5.2 FDC Interface

| SYMBOL  | PIN | I/O               | FUNCTION                                                                                                                                                                                                                                                                          |

|---------|-----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRVDEN0 | 1   | OD <sub>24t</sub> | Drive Density Select bit 0.                                                                                                                                                                                                                                                       |

| INDEX#  | 3   | IN <sub>csu</sub> | This Schmitt-triggered input from the disk drive is active low when the head is positioned over the beginning of a track marked by an index hole. This input pin is pulled up internally by a 1 K $\Omega$ resistor. The resistor can be disabled by bit 7 of L0-CRF0 (FIPURDWN). |

| MOA#    | 4   | OD <sub>24t</sub> | Motor A On. When set to 0, this pin enables disk drive 0. This is an open drain output.                                                                                                                                                                                           |

| DSB#    | 5   | OD <sub>24t</sub> | Drive Select B. When set to 0, this pin enables disk drive B. This is an open drain output.                                                                                                                                                                                       |

| FANIN3  |     | I/O24ts           | 0V to +5V amplitude fan tachometer input                                                                                                                                                                                                                                          |

| DSA#    | 6   | OD <sub>24t</sub> | Drive Select A. When set to 0, this pin enables disk drive A. This is an open drain output.                                                                                                                                                                                       |

| MOB#    | 7   | OD <sub>24t</sub> | Motor B On. When set to 0, this pin enables disk drive 1. This is an open drain output.                                                                                                                                                                                           |

| FANPWM3 |     | OD <sub>24t</sub> | Fan speed control. Use the Pulse Width Modulation ( <b>PWM</b> ) technical knowledge to control the Fan's RPM.                                                                                                                                                                    |

| DIR#    | 8   | OD <sub>24t</sub> | Direction of the head step motor. An open drain output.<br>Logic 1 = outward motion<br>Logic 0 = inward motion                                                                                                                                                                    |

| STEP#   | 9   | OD <sub>24t</sub> | Step output pulses. This active low open drain output produces a pulse to move the head to another track.                                                                                                                                                                         |

| WD#     | 10  | OD <sub>24t</sub> | Write data. This logic low open drain writes pre-compensation serial data to the selected FDD. An open drain output.                                                                                                                                                              |

| WE#     | 11  | OD <sub>24t</sub> | Write enable. An open drain output.                                                                                                                                                                                                                                               |

| TRACK0# | 13  | INcsu             | Track 0. This Schmitt-triggered input from the disk drive is active<br>low when the head is positioned over the outermost track. This<br>input pin is pulled up internally by a 1 K $\Omega$ resistor. The resistor<br>can be disabled by bit 7 of L0-CRF0 (FIPURDWN).            |

| WP#     | 14  | IN <sub>csu</sub> | Write protected. This active low Schmitt input from the disk drive indicates that the diskette is write-protected. This input pin is pulled up internally by a 1 K $\Omega$ resistor. The resistor can be disabled by bit 7 of L0-CRF0 (FIPURDWN).                                |

| RDATA#  | 15  | IN <sub>csu</sub> | The read data input signal from the FDD. This input pin is pulled up internally by a 1 K $\Omega$ resistor. The resistor can be disabled by bit 7 of L0-CRF0 (FIPURDWN).                                                                                                          |

| HEAD#   | 16  | OD24t             | Head select. This open drain output determines which disk drive<br>head is active.<br>Logic 1 = side 0<br>Logic 0 = side 1                                                                                                                                                        |

FDC Interface, continued

| SYMBOL  | PIN | I/O   | FUNCTION                                                                                                                                                                                                                     |

|---------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSKCHG# | 17  | INcsu | Diskette change. This signal is active low at power on and whenever the diskette is removed. This input pin is pulled up internally by a 1 K $\Omega$ resistor. The resistor can be disabled by bit 7 of L0-CRF0 (FIPURDWN). |

### 5.3 Multi-Mode Parallel Port

The following pins have alternate functions, which are controlled by CR28 and L3-CRF0.

| SYMBOL  | PIN | I/O               | FUNCTION                                                                                                                                                                                                                  |

|---------|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLCT    | 31  | INts              | PRINTER MODE:                                                                                                                                                                                                             |

| WE2#    |     | OD <sub>12t</sub> | An active high input on this pin indicates that the printer is selected. Refer to the description of the parallel port for definition of this pin in ECP and EPP mode.                                                    |

| VV L Z# |     | 0D <sub>12t</sub> | EXTENSION FDD MODE: WE2#                                                                                                                                                                                                  |

|         |     |                   | This pin is for Extension FDD B; its function is the same as the WE# pin of FDC.                                                                                                                                          |

|         |     |                   | EXTENSION 2FDD MODE: WE2#                                                                                                                                                                                                 |

|         |     |                   | This pin is for Extension FDD A and B; its function is the same as the WE# pin of FDC.                                                                                                                                    |

| PE      | 32  | INts              | PRINTER MODE:                                                                                                                                                                                                             |

| WD2#    |     | OD <sub>12t</sub> | An active high input on this pin indicates that the printer has detected the end of the paper. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode. EXTENSION FDD MODE: WD2# |

|         |     |                   | This pin is for Extension FDD B; its function is the same as the WD# pin of FDC.                                                                                                                                          |

|         |     |                   | EXTENSION 2FDD MODE: WD2#                                                                                                                                                                                                 |

|         |     |                   | This pin is for Extension FDD A and B; its function is the same as the WD# pin of FDC.                                                                                                                                    |

| BUSY    | 33  | IN <sub>ts</sub>  | PRINTER MODE:                                                                                                                                                                                                             |

| MOB2#   |     | OD <sub>12t</sub> | An active high input indicates that the printer is not ready to receive data. Refer to the description of the parallel port for definition of this pin in ECP and EPP mode.                                               |

| WIGDE#  |     | 0D <sub>12t</sub> | EXTENSION FDD MODE: MOB2#                                                                                                                                                                                                 |

|         |     |                   | This pin is for Extension FDD B; its function is the same as the MOB# pin of FDC.                                                                                                                                         |

|         |     |                   | EXTENSION 2FDD MODE: MOB2#                                                                                                                                                                                                |

|         |     |                   | This pin is for Extension FDD A and B; its function is the same as the MOB# pin of FDC.                                                                                                                                   |

| Iulti-Mode Parallel Port, continued |     |                     |                                                                                                                                                                                                                           |  |  |

|-------------------------------------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SYMBOL                              | PIN | I/O                 | FUNCTION                                                                                                                                                                                                                  |  |  |

| ACK#                                | 34  | IN <sub>ts</sub>    | PRINTER MODE: ACK#                                                                                                                                                                                                        |  |  |

|                                     |     |                     | An active low input on this pin indicates that the printer has<br>received data and is ready to accept more data. Refer to the<br>description of the parallel port for the definition of this pin in ECP<br>and EPP mode. |  |  |

| DSB2#                               |     | OD <sub>12t</sub>   | EXTENSION FDD MODE: DSB2#                                                                                                                                                                                                 |  |  |

|                                     |     |                     | This pin is for the Extension FDD B; its functions is the same as the DSB# pin of FDC.                                                                                                                                    |  |  |

|                                     |     |                     | EXTENSION 2FDD MODE: DSB2#                                                                                                                                                                                                |  |  |

|                                     |     |                     | This pin is for Extension FDD A and B; its function is the same as the DSB# pin of FDC.                                                                                                                                   |  |  |

| PD7                                 | 35  | I/O <sub>12ts</sub> | PRINTER MODE: PD7                                                                                                                                                                                                         |  |  |

|                                     |     |                     | Parallel port data bus bit 7. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.                                                                                           |  |  |

| DSA2#                               |     | OD <sub>12t</sub>   | EXTENSION FDD MODE: This pin is a tri-state output.                                                                                                                                                                       |  |  |

| 2 01 1211                           |     | 0012                | EXTENSION 2FDD MODE: DSA2#                                                                                                                                                                                                |  |  |

|                                     |     |                     | This pin is for Extension FDD A; its function is the same as the DSA# pin of FDC.                                                                                                                                         |  |  |

| PD6                                 | 36  | I/O <sub>12ts</sub> | PRINTER MODE: PD6                                                                                                                                                                                                         |  |  |

|                                     |     |                     | Parallel port data bus bit 6. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.                                                                                           |  |  |

| MOA2#                               |     | OD <sub>12t</sub>   | EXTENSION FDD MODE: This pin is a tri-state output.                                                                                                                                                                       |  |  |

|                                     |     | 00121               | EXTENSION. 2FDD MODE: MOA2#                                                                                                                                                                                               |  |  |

|                                     |     |                     | This pin is for Extension FDD A; its function is the same as the MOA# pin of FDC.                                                                                                                                         |  |  |

| PD5                                 | 37  | I/O <sub>12ts</sub> | PRINTER MODE: PD5                                                                                                                                                                                                         |  |  |

|                                     |     |                     | Parallel port data bus bit 5. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.                                                                                           |  |  |

|                                     |     |                     | EXTENSION FDD MODE: This pin is a tri-state output.                                                                                                                                                                       |  |  |

|                                     |     |                     | EXTENSION 2FDD MODE: This pin is a tri-state output.                                                                                                                                                                      |  |  |

| Iulti-Mode Parallel Port, continued |     |                     |                                                                                                                                       |  |  |

|-------------------------------------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SYMBOL                              | PIN | I/O                 | FUNCTION                                                                                                                              |  |  |

| PD4                                 | 38  | I/O <sub>12ts</sub> | PRINTER MODE: PD4                                                                                                                     |  |  |

|                                     |     |                     | Parallel port data bus bit 4. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.       |  |  |

| DSKCHG2#                            |     | IN <sub>ts</sub>    | EXTENSION FDD MODE: DSKCHG2#                                                                                                          |  |  |

|                                     |     | " IS                | This pin is for Extension FDD B; the function of this pin is the same as the DSKCHG# pin of FDC. It is pulled high internally.        |  |  |

|                                     |     |                     | EXTENSION 2FDD MODE: DSKCHG2#                                                                                                         |  |  |

|                                     |     |                     | This pin is for Extension FDD A and B; this function of this pin is the same as the DSKCHG# pin of FDC. It is pulled high internally. |  |  |

| PD3                                 | 39  | I/O <sub>12ts</sub> | PRINTER MODE: PD3                                                                                                                     |  |  |

|                                     |     |                     | Parallel port data bus bit 3. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.       |  |  |

| RDATA2#                             |     | IN <sub>ts</sub>    | EXTENSION FDD MODE: RDATA2#                                                                                                           |  |  |

|                                     |     | livis               | This pin is for Extension FDD B; its function is the same as the RDATA# pin of FDC. It is pulled high internally.                     |  |  |

|                                     |     |                     | EXTENSION 2FDD MODE: RDATA2#                                                                                                          |  |  |

|                                     |     |                     | This pin is for Extension FDD A and B; its function is the same as the RDATA# pin of FDC. It is pulled high internally.               |  |  |

| PD2                                 | 40  | I/O <sub>12ts</sub> | PRINTER MODE: PD2                                                                                                                     |  |  |

|                                     |     |                     | Parallel port data bus bit 2. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.       |  |  |

| WP2#                                |     | IN <sub>ts</sub>    | EXTENSION FDD MODE: WP2#                                                                                                              |  |  |

|                                     |     |                     | This pin is for Extension FDD B; its function is the same as the WP# pin of FDC. It is pulled high internally.                        |  |  |

|                                     |     |                     | EXTENSION. 2FDD MODE: WP2#                                                                                                            |  |  |

|                                     |     |                     | This pin is for Extension FDD A and B; its function is the same as the WP# pin of FDC. It is pulled high internally.                  |  |  |

| PD1                                 | 41  | I/O <sub>12ts</sub> | PRINTER MODE: PD1                                                                                                                     |  |  |

|                                     |     |                     | Parallel port data bus bit 1. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.       |  |  |

| TRAK02#                             |     | IN <sub>ts</sub>    | EXTENSION FDD MODE: TRAK02#                                                                                                           |  |  |

|                                     |     | ""ts                | This pin is for Extension FDD B; its function is the same as the TRAK0# pin of FDC. It is pulled high internally.                     |  |  |

|                                     |     |                     | EXTENSION. 2FDD MODE: TRAK02#                                                                                                         |  |  |

|                                     |     |                     | This pin is for Extension FDD A and B; its function is the same as the TRAK0# pin of FDC. It is pulled high internally.               |  |  |

Multi-Mode Parallel Port, continued

| SYMBOL  | PIN | I/O                 | FUNCTION                                                                                                                                          |

|---------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| PD0     | 42  | I/O <sub>12ts</sub> | PRINTER MODE: PD0                                                                                                                                 |

|         |     |                     | Parallel port data bus bit 0. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.                   |

| INDEX2# |     | IN <sub>ts</sub>    | EXTENSION FDD MODE: INDEX2#                                                                                                                       |

|         |     |                     | This pin is for Extension FDD B; its function is the same as the INDEX# pin of FDC. It is pulled high internally.                                 |

|         |     |                     | EXTENSION 2FDD MODE: INDEX2#                                                                                                                      |

|         |     |                     | This pin is for Extension FDD A and B; its function is the same as the INDEX# pin of FDC. It is pulled high internally.                           |

| SLIN#   | 43  | OD <sub>12t</sub>   | PRINTER MODE: SLIN#                                                                                                                               |

|         |     |                     | Output line for detection of printer selection. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode. |

| STEP2#  |     | OD <sub>12t</sub>   | EXTENSION FDD MODE: STEP2#                                                                                                                        |

|         |     |                     | This pin is for Extension FDD B; its function is the same as the STEP# pin of FDC.                                                                |

|         |     |                     | EXTENSION 2FDD MODE: STEP2#                                                                                                                       |

|         |     |                     | This pin is for Extension FDD A and B; its function is the same as the STEP# pin of FDC.                                                          |

| INIT#   | 44  | OD <sub>12t</sub>   | PRINTER MODE: INIT#                                                                                                                               |

|         |     |                     | Output line for the printer initialization. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.     |

| DIR2#   |     | OD <sub>12t</sub>   | EXTENSION FDD MODE: DIR2#                                                                                                                         |

|         |     |                     | This pin is for Extension FDD B; its function is the same as the DIR# pin of FDC.                                                                 |

|         |     |                     | EXTENSION 2FDD MODE: DIR2#                                                                                                                        |

|         |     |                     | This pin is for Extension FDD A and B; its function is the same as the DIR# pin of FDC.                                                           |

| Multi-Mode Parallel Port, continued |     |                   |                                                                                                                                                                                                        |  |

|-------------------------------------|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SYMBOL                              | PIN | I/O               | FUNCTION                                                                                                                                                                                               |  |

| ERR#                                | 45  | IN <sub>ts</sub>  | PRINTER MODE: ERR#                                                                                                                                                                                     |  |

|                                     |     |                   | An active low input on this pin indicates that the printer has<br>encountered an error condition. Refer to the description of the<br>parallel port for the definition of this pin in ECP and EPP mode. |  |

| HEAD2#                              |     | OD <sub>12t</sub> | EXTENSION FDD MODE: HEAD2#                                                                                                                                                                             |  |

|                                     |     |                   | This pin is for Extension FDD B; its function is the same as the HEAD# pin of FDC.                                                                                                                     |  |

|                                     |     |                   | EXTENSION 2FDD MODE: HEAD2#                                                                                                                                                                            |  |

|                                     |     |                   | This pin is for Extension FDD A and B; its function is the same as the HEAD# pin of FDC.                                                                                                               |  |

| AFD#                                | 46  | OD <sub>12t</sub> | PRINTER MODE: AFD#                                                                                                                                                                                     |  |

|                                     |     |                   | An active low output from this pin causes the printer to auto feed a line after a line is printed. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.   |  |

| DRVDEN0                             |     | OD <sub>12t</sub> | EXTENSION FDD MODE: DRVDEN0                                                                                                                                                                            |  |

|                                     |     |                   | This pin is for Extension FDD B; its function is the same as the DRVDEN0 pin of FDC.                                                                                                                   |  |

|                                     |     |                   | EXTENSION 2FDD MODE: DRVDEN0                                                                                                                                                                           |  |

|                                     |     |                   | This pin is for Extension FDD A and B; its function is the same as the DRVDEN0 pin of FDC.                                                                                                             |  |

| STB#                                | 47  | OD <sub>12t</sub> | PRINTER MODE: STB#                                                                                                                                                                                     |  |

|                                     |     |                   | An active low output is used to latch the parallel data into the printer. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.                            |  |

|                                     |     |                   | EXTENSION FDD MODE: This pin is a tri-state output                                                                                                                                                     |  |

|                                     |     |                   | EXTENSION 2FDD MODE: This pin is a tri-state output.                                                                                                                                                   |  |

Multi-Mode Parallel Port, continued

#### **Winbond** Electronics Corp.

| SYMBOL | PIN | I/O                                               | FUNCTION                                                                                                                                                                                                                                                                    |  |

|--------|-----|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CTSA#  | 49  | INt Clear To Send. It is the modem control input. |                                                                                                                                                                                                                                                                             |  |

| CTSB#  | 78  |                                                   | The function of these pins can be tested by reading bit 4 of the handshake status register.                                                                                                                                                                                 |  |

| DSRA#  | 50  | IN <sub>t</sub>                                   | Data Set Ready. An active low signal indicates the modem or                                                                                                                                                                                                                 |  |

| DSRB#  | 79  |                                                   | data set is ready to establish a communication link and transfer data to the UART.                                                                                                                                                                                          |  |

| RTSA#  | 51  | O <sub>8c</sub>                                   | UART A Request To Send. An active low signal informs the modem or data set that the controller is ready to send data.                                                                                                                                                       |  |

| HEFRAS |     | INcd                                              | During power-on reset, this pin is pulled down internally and is defined as HEFRAS, which provides the power-on value for CR26 bit 6 (HEFRAS). A 4.7 k $\Omega$ is recommended if intends to pull up. (select 4EH as configuration I/O port's address)                      |  |

| RTSB#  | 80  | O <sub>8c</sub>                                   | UART B Request To Send. An active low signal informs the modem or data set that the controller is ready to send data.                                                                                                                                                       |  |

| ENGMTO |     | INcd                                              | Watch Dog Time-Out enable.                                                                                                                                                                                                                                                  |  |

| DTRA   | 52  | O <sub>8c</sub>                                   | UART A Data Terminal Ready. An active low signal informs the modem or data set that the controller is ready to communicate.                                                                                                                                                 |  |

| PNPCVS |     | INcd                                              | During power-on reset, this pin is pulled down internally and is defined as PNPCVS, which provides the power-on value for CR24 bit 0 (PNPCVS). A 4.7 k $\Omega$ is recommended if intends to pull up. (clear the default value of FDC, UARTs, PRT, Game port and MIDI port) |  |

### 5.4 Serial Port Interface

| SYMBOL         | PIN      | I/O                     | FUNCTION                                                                                                                                                                                                                          |  |

|----------------|----------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DTRB#          | 81       | O <sub>8c</sub>         | UART B Data Terminal Ready. An active low signal informs the modem or data set that controller is ready to communicate.                                                                                                           |  |

| SINA<br>SINB   | 53<br>82 | INt                     | Serial Input. It is used to receive serial data through the communication link.                                                                                                                                                   |  |

| SOUTA          | 54       | O <sub>8c</sub>         | UART A Serial Output. It is used to transmit serial data out to the communication link.                                                                                                                                           |  |

| PENKBC         |          | INcd                    | During power-on reset, this pin is pulled down internally and is defined as PENKBC, which provides the power-on value for CR24 bit 2 (PENKBC). A 4.7 k $\Omega$ resistor is recommended if intends to pull up. (enable KBC)       |  |

| SOUTB<br>PEN48 | 83       | O <sub>8c</sub><br>INcd | UART B Serial Output. During power-on reset, this pin is pulled down internally and is defined as PEN48, which provides the power-on value for CR24 bit 6 (EN48). A 4.7 k $\Omega$ resistor is recommended if intends to pull up. |  |

| DCDA#          | 56       | INt                     | Data Carrier Detect. An active low signal indicates the modem or                                                                                                                                                                  |  |

| DCDB#          | 84       |                         | data set has detected a data carrier.                                                                                                                                                                                             |  |

| RIA#           | 57       | INt                     | Ring Indicator. An active low signal indicates that a ring signal is                                                                                                                                                              |  |

| RIB#           | 85       |                         | being received from the modem or data set.                                                                                                                                                                                        |  |

#### Serial Port Interface, continued

### 5.5 KBC Interface

| SYMBOL | PIN | I/O                  | FUNCTION                                                        |

|--------|-----|----------------------|-----------------------------------------------------------------|

| GA20M  | 59  | O16t                 | Gate A20 output. This pin is high after system reset. (KBC P21) |

| KBRST  | 60  | O16t                 | Keyboard reset. This pin is high after system reset. (KBC P20)  |

| KCLK   | 62  | I/OD <sub>16cs</sub> | Keyboard Clock.                                                 |

| KDAT   | 63  | I/OD <sub>16cs</sub> | Keyboard Data.                                                  |

| MCLK   | 65  | I/OD <sub>16cs</sub> | PS2 Mouse Clock.                                                |

| MDAT   | 66  | I/OD <sub>16cs</sub> | PS2 Mouse Data.                                                 |

### 5.6 ACPI Interface

| SYMBOL | PIN | I/O               | FUNCTION                                                                                                                         |

|--------|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------|

| PSOUT# | 67  | OD <sub>12t</sub> | Panel Switch Output. This signal is used for Wake-Up system from S5 <sub>cold</sub> state. This pin is pulse output, active low. |

| PSIN   | 68  | IN <sub>cd</sub>  | Panel Switch Input. This pin is high active with an internal pull down resistor.                                                 |

| VBAT   | 74  | pvdf_rc1000_vbat  | Battery voltage input.                                                                                                           |

### 5.7 Hardware Monitor Interface

| SYMBOL    | PIN | I/O                 | FUNCTION                                                                                                                                                              |  |

|-----------|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CASEOPEN# | 76  | IN <sub>t</sub>     | CASE OPEN. An active low input from an external device when case is opened. This signal can be latched if pin VBAT is connect to battery, even W83637HF is power off. |  |

| VIN2      | 97  | AIN                 | 0V to 4.096V FSR Analog Inputs.                                                                                                                                       |  |

| VIN1      | 99  | AIN                 | 0V to 4.096V FSR Analog Inputs.                                                                                                                                       |  |

| CPUVCORE  | 100 | AIN                 | 0V to 4.096V FSR Analog Inputs.                                                                                                                                       |  |

| VREF      | 101 | AOUT                | Reference Voltage for temperature maturation.                                                                                                                         |  |

| VTIN      | 102 | AIN                 | Temperature sensor 3 inputs. It is used for temperature maturation.                                                                                                   |  |

| CPUTIN    | 103 | AIN                 | Temperature sensor 2 inputs. It is used for CPU1 temperature maturation.                                                                                              |  |

| SYSTIN    | 104 | AIN                 | Temperature sensor 1 input. It is used for system temperature maturation.                                                                                             |  |

| OVT#      | 105 | OD <sub>24t</sub>   | Over temperature Shutdown Output. It indicated the temperature is over temperature limit.                                                                             |  |

| SMI#      |     |                     | System Management Interrupt channel input.                                                                                                                            |  |

| FANIN2    | 112 | I/O <sub>12ts</sub> | 0V to +5V amplitude fan tachometer input.                                                                                                                             |  |

| FANIN1    | 113 |                     |                                                                                                                                                                       |  |

| FANPWM1   | 116 | O <sub>12t</sub>    | Fan speed control. Use the Pulse Width Modulation (PWM)                                                                                                               |  |

| FANPWM2   | 115 | (OD12t)             | technical knowledge to control the Fan's RPM.                                                                                                                         |  |

| BEEP      | 118 | OD12t               | Beep function for hardware monitor. This pin is low after system reset.                                                                                               |  |

|              | 5.8 Game Port & MIDI Port |                                               |                                                                                                          |  |  |

|--------------|---------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|