# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **8-BIT CID MICROCONTROLLER**

# Table of Contents-

| 1.  | GENE   | RAL DESCRIPTION                                        | 2    |

|-----|--------|--------------------------------------------------------|------|

| 2.  | FEATU  | JRES                                                   | 2    |

| 3.  | PIN CO | ONFIGURATION                                           | 4    |

| 4.  | PIN DE | ESCRIPTION                                             | 5    |

| 5.  | BLOC   | K DIAGRAM                                              | 7    |

| 6.  | FUNC   | TIONAL DESCRIPTION                                     | 8    |

|     | 6.1    | Memory Organization                                    | 9    |

|     | 6.2    | Special Function Registers                             | . 12 |

|     | 6.3    | Initial State of Registers                             | . 32 |

|     | 6.4    | Instruction                                            | . 33 |

|     | 6.5    | Power Management                                       | . 37 |

|     | 6.6    | Reset                                                  | . 38 |

|     | 6.7    | Interrupt                                              | . 38 |

|     | 6.8    | Programmable Timers/Counters                           | . 41 |

|     | 6.9    | Serial Port 1                                          | . 45 |

|     | 6.10   | Comparator                                             | . 47 |

|     | 6.11   | DTMF Generator                                         | . 47 |

|     | 6.12   | FSK Generator                                          | . 48 |

|     | 6.13   | I/O Ports                                              | . 50 |

|     | 6.14   | Divider                                                | . 50 |

|     | 6.15   | Calling Identity Delivery (CID)                        | . 51 |

| 7.  | APPLI  | CATION CIRCUIT                                         | . 60 |

| 8.  | ELECT  | RICAL CHARACTERISTICS                                  | . 66 |

|     | 8.1    | Absolute Maximum Ratings*                              | . 66 |

|     | 8.2    | Recommended Operating Conditions                       | . 66 |

|     | 8.3    | DC Characteristics                                     | . 67 |

|     | 8.4    | Electrical Characteristics - Gain Control OP-Amplifier | . 68 |

|     | 8.5    | AC Characteristics                                     | . 69 |

| 9.  | PACKA  | AGE DIMENSION                                          | . 72 |

| 10. | REVIS  | ION HISTORY                                            | . 73 |

# **1. GENERAL DESCRIPTION**

The W925E/C240 is an all in one single 8-bit micro-controller with widely used Calling Identity Delivery (CID) function. The 8-bit CPU core is based on the 8051 family; therefore, all the instructions are compatible to the Turbo 8051 series. The CID part consisted of FSK decoder, DTMF receiver, CPE\* Alert Signal (CAS) detector and Ring detector. Also built-in DTMF generator and FSK generator with baud rate 1200 bps (bits/sec). Using W925E/C240 can easily implement the CID adjunct box and the feature phone or Short Message Service (SMS) phone with CID function. The main features are listed in the next section.

# 2. FEATURES

- **APPLICATION**: The **SMS** phone with CID function and CID adjunct box.

- CPU: 8-bit micro-controller is similar to the 8051 family.

- EEPROM type(E version) operating voltage:

- $\mu$ C: Depend on the operating vol. option. Either 2.4 to 3.6V or 3.0 to 5.5V for operating. If 2.4 to 3.6V be selected, the  $\mu$ C operating range is from 2.4 to 3.6V, else if 3.0 to 5.5V be selected, the  $\mu$ C operating range is from 3.0 to 5.5V.

CID: 3.0 to 5.5V.

- MASK type(C version) operating voltage:

$\mu C$ : 2.2 to 5.5V.

CID: 3.0 to 5.5V.

- Dual-clock operation:

- Main oscillator: 3.58MHz crystal for CID and DTMF function. And built-in RC oscillator.

- Sub oscillator: 32768Hz crystal.

- Main and sub oscillators are enable/disable by bit control individually.

- **ROM**: 256K bytes internal flash EEPROM/MASK ROM type.

- Up 128K bytes for program ROM.

- Total 256K bytes for look-up table ROM.

- Separate 256K into 4 pages, each page is 64K addressable.

- RAM:

- 256 bytes on chip scratch-pad RAM.

- 8K bytes on chip RAM for MOVX instruction.

- CID

- Compatible with Bellcore TR-NWT-000030 & SR-TSV-002476, British Telecom(BT) SIN227, U.K. Cable Communication Association(CCA) specification.

- FSK modulator/demodulator: for Bell 202 and ITU-T V.23 FSK with 1200-baud rate.

- CAS detector: for dual tones of Bellcore CAS and BT Idle State and Loop State Dual Tone Alert Signal (DTAS).

- DTMF generator/receiver;

- Ring detector: for line reversal for BT, ring burst for CCA or ring signal for Bellcore.

- Two independent OP amps with adjustable gain for Tip/Ring and Telephone Hybrid connections.

- I/O: 40 I/O pins.

- P0: Bit and byte addressable. I/O mode can be bit controlled. Open drain type.

- P1~P3: Bit and byte addressable. Pull high and I/O mode can be bit controlled.

- P4: Byte addressable. Pull high and I/O mode can be bit controlled.

- Note: "CPE\*" Customer Premises Equipment

- Power mode:

- Dual-clock slow operation mode: System is operated by the sub-oscillator (Fosc=Fs and Fm is stopped)

- Idle mode: CPU hold. The clock to the CPU is halted, but the interrupt, timer and watchdog timer block work normally but CID function is disabled.

- Power down mode: All activity is completely stopped and power consumption is less than 1 μA.

- Timer: 2 13/16-bit timers, or 8-bit auto-reload timers, that are Timer0 and Timer1.

- Watchdog timer: WDT can be programmed by the user to serve as a system monitor.

- Interrupt: 11 interrupt sources with two levels of priority.

- 4 interrupts from INT0, INT1, INT2 and INT3.

- 2 interrupts from Timer0, Timer1.

- 1 interrupt from Serial port.

- 1 interrupt from CID.

- 1 interrupt from 13/14-bit Divider.

- 1 interrupt from Comparator.

- 1 interrupt from Watch Dog Timer.

- **Divider:** 13/14 bit divider, clock source from sub-oscillator, therefore, DIVF set every 0.25/0.5 second.

- Comparator:

- Comparator: 1 analog inputs from VNEG pin, 2 reference input pins, one is from VPOS pin and another is from internal regulator output.

- Serial port:

- An 8-bit serial transceiver with SCLK and SDATA.

- Package:

- 100pin LQFP: The part numbers are W925E240 & W925C240

- Lead free 100pin LQFP: The part numbers are W925E240FG & W925G240

# **3. PIN CONFIGURATION**

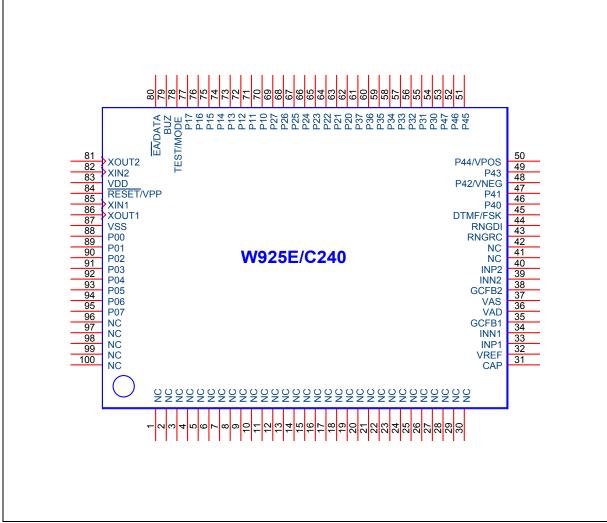

Figure 3-1 shows the pin assignment. The package type is 100pin QFP.

Figure 3-1 W925E/C240 Pin Configuration

# 4. PIN DESCRIPTION

| NAME            | I/O    | DESCRIPTION                                                                                                                                                                                                                                                                              |

|-----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST/MODE       | I/O    | TEST pin. In E version (EEPROM type), it works as a Mode pin to select programming mode. In C version (Mask type), this pin with internal pull-low resistor.                                                                                                                             |

| EA /DATA        | I, I/O | Set high for normal function. In E version, it works as a Data pin. In C version, this pin with internal pull-high resistor.                                                                                                                                                             |

| RESET /VPP      | I      | RESET pin. A low pulse causes the whole chip reset. In E version, this pin works as a VPP pin, which is a supply programming voltage. In C version, this pin with internal pull-high resistor.                                                                                           |

| RNGDI           | Ι      | Ring Detect Input (Schmitt trigger input). Used for ring detection and line reversal detection. Must maintain a voltage between VAD and VAS.                                                                                                                                             |

| RNGRC           | 0      | Ring RC (Open drain output and Schmitt trigger input). Used to set the time interval from the end of RNGDI pin to the inactive condition of the RNGON pin. An external resistor must connected to VAD and a capacitor connected to $V_{SS}$ , the time interval is the RC time constant. |

| CAP             | 0      | Must be connected $0.1\mu F$ capacitor to $V_{SS}$ .                                                                                                                                                                                                                                     |

| VREF            | 0      | Reference Voltage. Nominally, VDD/2 is used to bias the input of the gain control op-amp.                                                                                                                                                                                                |

| GCFB1           | 0      | Op-amp1 Feed-back Gain Control signal. Select the input gain by connecting this pin and the INN1 pin with feedback resistor. It is recommended that the op-amp1 be set to unity gain.                                                                                                    |

| INN1            | I      | Inverting Input of the gain control op-amp1.                                                                                                                                                                                                                                             |

| INP1            | I      | Non-inverting Input of the gain control op-amp1.                                                                                                                                                                                                                                         |

| GCFB2           | 0      | Op-amp2 Feed-back Gain Control signal. Select the input gain by connecting this pin and the INN2 pin with feedback resistor. It is recommended that the op-amp2 be set to unity gain.                                                                                                    |

| INN2            | I      | Inverting Input of the gain control op-amp2.                                                                                                                                                                                                                                             |

| INP2            | I      | Non-inverting Input of the gain control op-amp2.                                                                                                                                                                                                                                         |

| VAD             | I      | Analog voltage supply.                                                                                                                                                                                                                                                                   |

| VAS             | I      | Analog ground.                                                                                                                                                                                                                                                                           |

| V <sub>DD</sub> | I      | Digital voltage supply.                                                                                                                                                                                                                                                                  |

| V <sub>SS</sub> | I      | Digital ground.                                                                                                                                                                                                                                                                          |

| XOUT1           | 0      | Output pin for main-oscillator. Connected to 3.58MHz crystal for CID function.                                                                                                                                                                                                           |

| XIN1            | I      | Input pin for main-oscillator. Connected to 3.58MHz crystal for CID function.                                                                                                                                                                                                            |

Pin Description, continued

| NAME       | I/O | DESCRIPTION                                                                                                                                                                                                   |

|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XOUT2      | 0   | Output pin for sub-oscillator. Connected to 32.768KHz crystal only. Suggest to add an external capacitor about 10~30pF to ground(VSS) for the accuracy of the oscillator.                                     |

| XIN2       | I   | Input pin for sub-oscillator. Connected to 32.768KHz crystal only. Suggest to add an external capacitor about 10~30pF to ground(VSS) for the accuracy of the oscillator.                                      |

| DTMF/FSK   | 0   | FTE=0, Dual-Tone Multi-Frequency(DTMF) signal output                                                                                                                                                          |

| DTMITSK    | 0   | FTE=1, FSK signal output                                                                                                                                                                                      |

| BUZ        | 0   | Buzzer output pin. If buzzer function is disabled, BUZ pin is in floating state.                                                                                                                              |

| P00-P07    | I/O | Input/output port0. Port0 data can be bit controlled. The I/O mode is controlled by P0IO register. Port0 is open drain type when it is configured as output mode.                                             |

| P10-P17    | I/O | Input/output port1 with pull high resistors. Port1 data can be bit controlled.<br>The I/O mode is controlled by P1IO register. The P10-P13 and P14-P17<br>indicate the external interrupt pins(INT2 and INT3) |

| P20-P27    | I/O | Input/output port2 with pull high resistors. Port2 data can be bit controlled. The I/O mode is controlled by P2IO register.                                                                                   |

| P30-P37    | I/O | Input/output port3 with pull high resistors. Port3 data can be bit controlled. The I/O mode is controlled by P3IO register. The special function of port3 is referred to the description of P3 register.      |

| P40-P47    | 1/0 | Contents are byte controlled. Pull high and I/O mode can be bit controlled.                                                                                                                                   |

| F40-F47    | 1/0 | The special function of P4 is referred to the description of P4 register.                                                                                                                                     |

| VPOS, VNEG | I   | The comparator V+, V- analog input pins. Share pin with P4.2 and P4.4                                                                                                                                         |

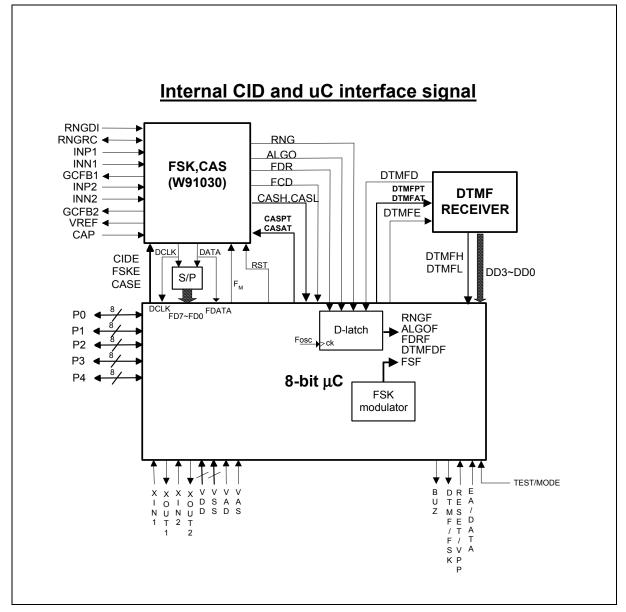

# 5. BLOCK DIAGRAM

# 6. FUNCTIONAL DESCRIPTION

The W925E/C240 is an 8-bit micro-controller with CID function. The 8-bit micro-control has the same instruction set as the 8051 family, with one addition: DEC DPTR (op-code A5H, the DPTR is decreased by 1). In addition, the W925E/C240 contains on-chip 8K bytes MOVX RAM.

### ROM

There are 256K bytes EEPROM/MASK ROM. Only 128K bytes EEPROM/MASK ROM is used for program code. The completely 256K bytes EEPROM/MASK ROM can be used for the look-up table memory.

### On-chip Data RAM

The W925E/C240 has 8K normal RAM which address is from 0000H to 1FFFH. It only can be accessed by MOVX instruction; this on-chip RAM is optional under software control. The on-chip data RAM is not used for executable program memory. There is no conflict or overlap among the 256 bytes scratchpad RAM and the 8K Bytes MOVX RAM as they use different addressing modes and separate instructions.

### CID

The CID functions include the FSK decoder, CAS detector, and DTMF decoder and ring detector.

### FSK Modulator

Support ITU-T V.23 and Bellcore 202 FSK transmit modulated signal.

### **DTMF Modulator**

The W925E/C240 built-in dual tone multi-frequency generator.

### I/O Ports:

The W925E/C240 has five 8-bit I/O ports giving 40 lines. Port0 to Port3 can be used as an 8-bit general I/O port with bit-addressable. The I/O mode of each port is controlled by PxIO registers. Port1 to Port4 have internal pull high resistors enabled/disabled by PxH registers. Port0 is open-drain type in output mode.

### Serial I/O Port

The serial port, through P4.0 (SCLK) and P4.1 (SDATA), is an 8-bit synchronous serial I/O interface.

### Timers

The W925E/C240 has two 13/16-bit timers or an 8 bits auto-reload timers. An independent watchdog timer is used as a system monitor or as a very long time period timer. A divider can produce the divider interrupt in every period of 0.5S or 0.25S.

### Comparator

The W925E/C240 has an internal comparator with one external analog signal input path VNEG and an external path VPOS or a regulator voltage for the reference input REF1.

### Interrupts

The W925E/C240 provides 11 interrupt resources with two priority level, including 4 external interrupt sources, 2 timer interrupts, 1 CID interrupt, 1 divider interrupt, 1 serial port interrupt, 1 comparator interrupt and 1 watchdog timer interrupt.

### **Power Management**

The W925E/C240 has IDLE and POWER DOWN modes of operation. In the IDLE mode, the clock to the CPU core is stopped however the functions of the timers, divider, CID and interrupts are active continuously. In the POWER DOWN mode, both of the system clock stop oscillating and the chip operation is completely stopped. POWER DOWN mode is the state of the lowest power consumption.

# 6.1 Memory Organization

The W925E/C240 separates the memory into two separate sections, the Program Memory and the Data Memory. The Program Memory is used to store the instruction op-codes and look-up table data, while the Data Memory is used to store data or for memory mapped devices.

### **Program Memory**

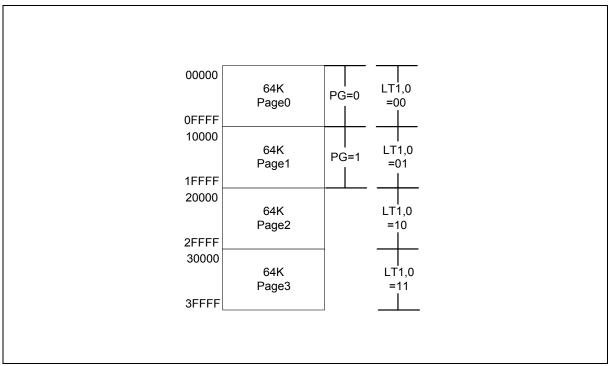

The Program Memory on the W925E/C240 can be up to 256K bytes that are divided into 4 pages, each page has the size of 64K bytes. The upper 128K bytes are used to store the op-codes and the whole 256K can be used to store look-up table data. Because the op-code is 64K addressable, a PG bit in PAGE register decides which ROM page between page0, page1 is enabled, and the ALU fetches the op-code from the selected ROM page. If PG=0, ALU fetches the op-code from page0. If PG=1, ALU fetches the op-code from page1. When MOVC instruction is executed, ALU fetches the look-up table data according the indication of LT1 and LT0 bits. The value of LT1 and LT0 indicates which ROM page is active for look-up table instruction.

Figure 6-1 Program Memory Map

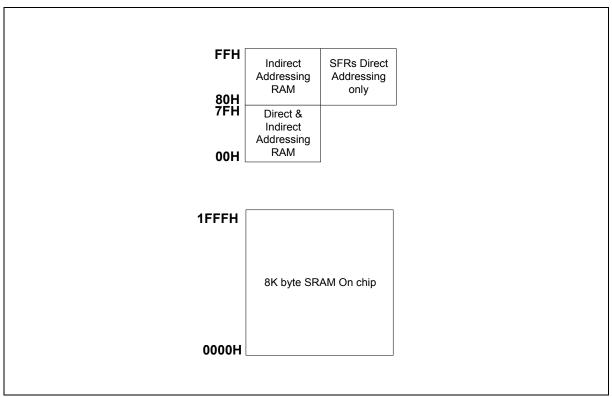

## **Data Memory**

The W925E/C240 contains on-chip 8K MOVX RAM of Data Memory, which can only be accessed by MOVX instructions from the address 0000H to 1FFFH. In addition, the W925E/C240 has 256 bytes of on-chip scratchpad RAM. This can be accessed either by direct addressing or by indirect addressing. There are also Special Function Registers (SFRs), which can only be accessed by direct addressing. Since the scratchpad RAM is only 256 bytes, it can be used only when data contents are small. In the event that larger data contents are present, the only one selection is on-chip MOVX RAM. The on-chip MOVX RAM can only be accessed by a MOVX instruction. However, the on-chip RAM has the fastest access times. The memory map is shown Figure 6-2 and Figure 6-3 shows the scratched-pad RAM/register addressing.

Figure 6-2 memory map

|                |        |    |    | RAM        | Indirect |    |    |    | FFh        |

|----------------|--------|----|----|------------|----------|----|----|----|------------|

|                |        |    |    |            |          |    |    |    | 80h        |

|                |        |    |    | RAM        | Direct   |    |    |    | 7Fh<br>30h |

| ◀-┐            | 78 🗲   | 79 | 7A | 7B         | 7C       | 7D | 7E | 7F | 2Fh        |

|                | 70     | 71 | 72 | 73         | 74       | 75 | 76 | 77 | 2Eh        |

|                | 68     | 69 | 6A | 6B         | 6C       | 6D | 6E | 6F | 2Dh        |

|                | 60     | 61 | 62 | 63         | 64       | 65 | 66 | 67 | 2Ch        |

| 1              | 58     | 59 | 5A | 5B         | 5C       | 5D | 5E | 5F | 2Bh        |

|                | 50     | 51 | 52 | 53         | 54       | 55 | 56 | 57 | 2Ah        |

| I              | 48     | 49 | 4A | 4B         | 4C       | 4D | 4E | 4F | 29h [      |

| Bit Addressabl | 40 Bit | 41 | 42 | 43         | 44       | 45 | 46 | 47 | 28h        |

|                | 38     | 39 | 3A | 3B         | 3C       | 3D | 3E | 3F | 27h 📘      |

| 20H-2FH        | 00     | 31 | 32 | 33         | 34       | 35 | 36 | 37 | 26h 📘      |

|                | 28     | 29 | 2A | 2B         | 2C       | 2D | 2E | 2F | 25h        |

|                | 20     | 21 | 22 | 23         | 24       | 25 | 26 | 27 | 24h        |

|                | 18     | 19 | 1A | 1B         | 1C       | 1D | 1E | 1F | 23h        |

|                | 10     | 11 | 12 | 13         | 14       | 15 | 16 | 17 | 22h        |

|                | 08     | 09 | 0A | 0B         | 0C       | 0D | 0E | 0F | 21h        |

| ◀-┘            | 00 🗲   | 01 | 02 | 03         | 04       | 05 | 06 | 07 | 20h        |

|                |        |    |    | <b>x</b> 3 | Bank     |    |    |    | 1Fh<br>18h |

|                |        |    |    |            |          |    |    |    | 17h        |

|                |        |    |    | κ2         | Bank     |    |    |    | 10h        |

|                |        |    |    |            |          |    |    |    | 0Fh        |

|                |        |    |    | <b>(1</b>  | Bank     |    |    |    | 08h        |

|                |        |    |    |            |          |    |    |    | 07h        |

|                |        |    |    | <b>(</b> 0 | Bank     |    |    |    | 00h        |

Figure 6-3 Scratchpad RAM/Register Addressing

# 6.2 Special Function Registers

The W925E/C240 uses Special Function Registers (SFRs) to control and monitor peripherals and their Modes.

The SFRs reside in the register locations 80-FFh and accessed by direct addressing only. Some of the SFRs are bit addressable. This is very useful in cases where one wishes to modify a particular bit without changing the others. The SFRs that are bit addressable are those whose addresses end in 0 or 8. The list of SFRs is as follows. The table is condensed with eight locations per row. Empty locations indicate that there are no registers at these addresses. The content of reserved bits or registers is not guaranteed.

| F8 | EIP   | CIDGD | CIDGA |        |       |        |        |        |

|----|-------|-------|-------|--------|-------|--------|--------|--------|

| F0 | В     |       |       |        |       |        |        |        |

| E8 | EIE   |       |       |        |       |        |        |        |

| E0 | ACC   |       |       |        |       |        |        |        |

| D8 | WDCON |       |       |        |       |        |        |        |

| D0 | PSW   |       |       |        |       |        |        |        |

| C8 | DIVC  |       |       |        |       |        |        |        |

| C0 | SCON1 | SBUF1 | REGVC |        | PMR   | STATUS | FSKTC  | FSKTB  |

| B8 | IP    |       | DTMFG | COMPR  | IRC1  | IRC2   | CASPT  | CASAT  |

| B0 | P3    | CIDR  | CIDFG | CIDPCR | FSKDR | DTMFDR | DTMFPT | DTMFAT |

| A8 | IE    |       |       |        |       |        | P4IO   |        |

| A0 | P2    | HB    | P4H   |        |       |        | P4     |        |

| 98 |       |       |       | P1EF   |       | P1H    | P2H    | P3H    |

| 90 | P1    | EXIF  | RPAGE | P1SR   | P0IO  | P1I0   | P2IO   | P3IO   |

| 88 | TCON  | TMOD  | TL0   | TL1    | TH0   | TH1    | CKCON1 | CKCON2 |

| 80 | P0    | SP    | DPL   | DPH    | DPL1  | DPH1   | DPS    | PCON   |

Note: The SFRs in the column with dark borders are bit-addressable.

A brief description of the SFRs now follows.

### PORT 0

| Bit:    | 7     | 6    | 5    | 4    | 3    | 2          | 1    | 0    |

|---------|-------|------|------|------|------|------------|------|------|

|         | P0.7  | P0.6 | P0.5 | P0.4 | P0.3 | P0.2       | P0.1 | P0.0 |

| Mnemoni | c: P0 |      |      |      |      | Address: 8 | 30h  |      |

(initial=FFh, input mode)

P0: P0 can be selected as input or output mode by the P0IO register. At initial reset, P0IO is set to FFH, P0 is used as input mode. When P0IO is set to 0, the P0 is used as CMOS open drain mode.

| STACK POINTI                   | ER                                                                                                                                        |                                                               |                          |                         |                      |                      | (initial=07          | H)                   |                       |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------|-------------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|

|                                | Bit:                                                                                                                                      | 7                                                             | 6                        | 5                       | 4                    | 3                    | 2                    | 1                    | 0                     |

|                                |                                                                                                                                           | SP.7                                                          | SP.6                     | SP.5                    | SP.4                 | SP.3                 | SP.2                 | SP.1                 | SP.0                  |

|                                | Mnemon                                                                                                                                    | ic: SP                                                        |                          |                         |                      |                      | Address: 8           | 31h                  |                       |

|                                | SP: The Stack Pointer stores the scratchpad RAM address where the stack begins. In other words, it always points to the top of the stack. |                                                               |                          |                         |                      |                      |                      |                      |                       |

| DATA POINTER LOW (initial=00H) |                                                                                                                                           |                                                               |                          |                         |                      |                      |                      |                      |                       |

|                                | Bit:                                                                                                                                      | 7                                                             | 6                        | 5                       | 4                    | 3                    | 2                    | 1                    | 0                     |

|                                |                                                                                                                                           | DPL.7                                                         | DPL.6                    | DPL.5                   | DPL.4                | DPL.3                | DPL.2                | DPL.1                | DPL.0                 |

|                                | Mnemon                                                                                                                                    | ic: DPL                                                       |                          |                         |                      |                      | Address: 8           | 32h                  |                       |

| DPL: This is the               | e low byte                                                                                                                                | e of the sta                                                  | andard 80                | 52 16-bit (             | data point           | er.                  |                      |                      |                       |

| DATA POINTEI                   | R HIGH                                                                                                                                    |                                                               |                          |                         |                      |                      | (initial=00          | H)                   |                       |

|                                | Bit:                                                                                                                                      | 7                                                             | 6                        | 5                       | 4                    | 3                    | 2                    | 1                    | 0                     |

|                                |                                                                                                                                           | DPH.7                                                         | DPH.6                    | DPH.5                   | DPH.4                | DPH.3                | DPH.2                | DPH.1                | DPH.0                 |

|                                | Mnemon                                                                                                                                    | ic: DPH                                                       |                          |                         |                      |                      | Address: 8           | 33h                  |                       |

| DPH: This is the               | e high byt                                                                                                                                | te of the st                                                  | andard 80                | )52 16-bit              | data poin            | iter.                |                      |                      |                       |

| DATA POINTEI                   | R LOW1                                                                                                                                    |                                                               |                          |                         |                      |                      | (initial=00          | H)                   |                       |

|                                | Bit:                                                                                                                                      | 7                                                             | 6                        | 5                       | 4                    | 3                    | 2                    | 1                    | 0                     |

|                                |                                                                                                                                           | DPL1.7                                                        | DPL1.6                   | DPL1.5                  | DPL1.4               | DPL1.3               | DPL1.2               | DPL1.1               | DPL1.0                |

|                                | Mnemoni                                                                                                                                   | ic: DPL1                                                      |                          |                         |                      |                      | Address: 8           | 34h                  |                       |

| W925<br>registe<br>place       | E/C240. 1<br>er DPS.0                                                                                                                     | byte of th<br>The user of<br>= 1. The<br>nd DPH. I<br>e user. | can switch<br>instructio | n betweer<br>ons that u | i DPL, DF<br>se DPTR | PH and D<br>will now | PL1, DPH<br>access [ | 1 simply<br>OPL1 and | by setting<br>DPH1 in |

| DATA POINTEI                   | R HIGH1                                                                                                                                   |                                                               |                          |                         |                      |                      | (initial=00          | H)                   |                       |

|                                | Bit:                                                                                                                                      | 7                                                             | 6                        | 5                       | 4                    | 3                    | 2                    | 1                    | 0                     |

|                                |                                                                                                                                           | DPH1.7                                                        | DPH1.6                   | DPH1.5                  | DPH1.4               | DPH1.3               | DPH1.2               | DPH1.1               | DPH1.0                |

|                                | Mnemon                                                                                                                                    | ic: DPH1                                                      |                          |                         |                      |                      | Address: 8           | 35h                  |                       |

|                                |                                                                                                                                           |                                                               |                          |                         |                      |                      |                      |                      |                       |

DPH1: This is the high byte of the new additional 16-bit data pointer. That has been added to the W925E/C240. The user can switch between DPL, DPH and DPL1, DPH1 simply by setting register DPS = 1. The instructions that use DPTR will now access DPL1 and DPH1 in place of DPL and DPH. If they are not required, they can be used as conventional register locations by the user.

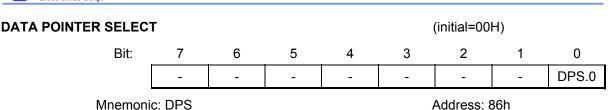

DPS.0: This bit is used to select either the DPL,DPH pair or the DPL1,DPH1 pair as the active Data Pointer. When set to 1, DPL1,DPH1 will be selected, otherwise DPL,DPH will be selected.

DPS.1-7: These bits are reserved, but will read 0.

### **POWER CONTROL**

|         |         |   |   |      |     | ,          | ,   |     |

|---------|---------|---|---|------|-----|------------|-----|-----|

| Bit:    | 7       | 6 | 5 | 4    | 3   | 2          | 1   | 0   |

|         | -       | - | - | IDLT | GF1 | GF0        | PD  | IDL |

| Mnemoni | c: PCON |   |   |      |     | Address: 8 | 37h |     |

- IDLT: This bit controls the idle mode type. In idle mode when idle mode is released by any interrupt, if IDLT=1 it will not jump to the corresponding interrupt; if IDLT=0 it will jump to the corresponding interrupt.

- GF1-0: These two bits are general-purpose user flags.

- PD: Setting this bit causes the W925E/C240 to go into the POWER DOWN mode. In this mode, all the clocks are stopped and program execution is frozen. Power down mode can be released by INT0~INT3 and ring detection of CID interrupt.

- IDL: Setting this bit causes the W925E/C240 to go into the IDLE mode. The type of idle mode is selected by IDLT. In this mode the clocks to the CPU are stopped, so program execution is frozen. However, the clock path to the timers blocks and interrupt blocks is not stopped, and these blocks continue operating.

### TIMER CONTROL

| Bit: | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

|      | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

### Mnemonic: TCON

Address: 88h

(initial=00H)

(initial=00H)

- TF1: Timer 1 overflows flag. This bit is set when Timer 1 overflows. It is cleared automatically when the program does a timer 1 interrupt service routine. Software can also set or clear this bit.

- TR1: Timer 1 runs control. This bit is set or cleared by software to turn timer on or off.

- TF0: Timer 0 overflows flag. This bit is set when Timer 0 overflows. It is cleared automatically when the program does a timer 0 interrupt service routine. Software can also set or clear this bit.

- TR0: Timer 0 runs control. This bit is set or cleared by software to turn timer on or off.

- IE1: Interrupt 1 edge detects: Set by hardware when an edge/level is detected on INT1. This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise, it follows the pin.

- IT1: Interrupt 1 type control: Set/cleared by software to specify falling edge/ low level triggered external inputs.

(initial=00H)

- IE0: Interrupt 0 edge detects: Set by hardware when an edge/level is detected on INT0. This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise, it follows the pin.

- IT0: Interrupt 0 type control. Set/cleared by software to specify falling edge/ low level triggered external inputs.

### TIMER MODE CONTROL

|         |         |     |    |    |      | •          | ,   |    |

|---------|---------|-----|----|----|------|------------|-----|----|

| Bit:    | 7       | 6   | 5  | 4  | 3    | 2          | 1   | 0  |

|         | GATE    | C/T | M1 | M0 | GATE | C/T        | M1  | M0 |

| Mnemoni | c: TMOD |     |    |    |      | Address: 8 | 39h |    |

Bit7~4 control timer 1, bit3~0 control timer0

- GATE: Gating control. When this bit is set, Timer x is enabled only while INTx pin is high and TRx control bit is set. When cleared, Timer x is enabled whenever TRx control bit is set.

- $C/\overline{T}$ : Timer or Counter Select. When cleared, the timer is incremented by internal clocks. When set, the timer counts high-to-low edges of the Tx pin.

Note: X is either 0 or 1.

M1, M0: Mode Select bits:

- M1 M0 Mode

- 0 0 Mode 0: 13-bits timer

- 0 1 Mode 1: 16-bits timer

- 1 0 Mode 2: 8-bits with auto-reload from Thx

- 1 1 Reserved

| TIMER 0 LOW BYTE                    |            | (initial=00H) |            |            |            |                   |            |            |

|-------------------------------------|------------|---------------|------------|------------|------------|-------------------|------------|------------|

| Bit:                                | 6          | 5             | 4          | 3          | 2          | 1                 | 0          |            |

|                                     | TL0.7      | TL0.6         | TL0.5      | TL0.4      | TL0.3      | TL0.2             | TL0.1      | TL0.0      |

| Mnemonic: TL0 Address: 8Ah          |            |               |            |            |            |                   |            |            |

| TL0.7-0: Timer 0 low byte register. |            |               |            |            |            |                   |            |            |

|                                     |            |               |            |            |            |                   |            |            |

| TIMER 1 LOW BYTE                    | -          |               |            |            |            | (initial=00       | H)         |            |

| TIMER 1 LOW BYTE<br>Bit:            | 7          | 6             | 5          | 4          | 3          | (initial=00)<br>2 | H)<br>1    | 0          |

| _                                   | 7<br>TL1.7 | 6<br>TL1.6    | 5<br>TL1.5 | 4<br>TL1.4 |            | •                 | ,          | 0<br>TL1.0 |

| _                                   | TL1.7      | 1             | 1          | -          | 3<br>TL1.3 | 2                 | 1<br>TL1.1 |            |

| TIMER 0 HIGH BYTE                                                                                                                                                                                               |                               |       |       |       |       | (initial=00 | H)    |       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------|-------|-------|-------|-------------|-------|-------|

| Bit:                                                                                                                                                                                                            | 7                             | 6     | 5     | 4     | 3     | 2           | 1     | 0     |

|                                                                                                                                                                                                                 | TH0.7                         | TH0.6 | TH0.5 | TH0.4 | TH0.3 | TH0.2       | TH0.1 | TH0.0 |

| Mnemoni                                                                                                                                                                                                         | c: TH0                        |       |       |       | ŀ     | Address: 8  | BCh   | -     |

| TH0.7-0: Timer 0 high by                                                                                                                                                                                        | te register                   |       |       |       |       |             |       |       |

| TIMER 1 HIGH BYTE (initial=00H)                                                                                                                                                                                 |                               |       |       |       |       |             |       |       |

| Bit:                                                                                                                                                                                                            | 7                             | 6     | 5     | 4     | 3     | 2           | 1     | 0     |

|                                                                                                                                                                                                                 | TH1.7                         | TH1.6 | TH1.5 | TH1.4 | TH1.3 | TH1.2       | TH1.1 | TH1.0 |

| Mnemonic: TH1                                                                                                                                                                                                   |                               |       |       |       | ŀ     | Address: 8  | BDh   |       |

| TH1.7-0: Timer 1 high by                                                                                                                                                                                        | te register                   |       |       |       |       |             |       |       |

| CLOCK CONTROL1                                                                                                                                                                                                  |                               |       |       |       |       | (initial=00 | H)    |       |

| Bit:                                                                                                                                                                                                            | 7                             | 6     | 5     | 4     | 3     | 2           | 1     | 0     |

|                                                                                                                                                                                                                 | WD1                           | WD0   | T1S1  | T1S0  | T0S1  | T0S0        | DIVS  | M/S   |

| Mnemoni                                                                                                                                                                                                         | Mnemonic: CKCON1 Address: 8Eh |       |       |       |       |             |       |       |

| WD1-0: Watchdog timer mode select bits: These bits determine the time-out period for the watchdog timer. In all four time-out options the reset time-out is 512 clocks more than the interrupt time-out period. |                               |       |       |       |       |             |       |       |

| WD1 | WD0 | Interrupt time-out   | Reset time-out             |

|-----|-----|----------------------|----------------------------|

| 0   | 0   | Fosc/2 <sup>12</sup> | Fosc/2 <sup>12</sup> + 512 |

| 0   | 1   | Fosc/2 <sup>15</sup> | Fosc/2 <sup>15</sup> + 512 |

| 1   | 0   | Fosc/2 <sup>18</sup> | Fosc/2 <sup>18</sup> + 512 |

| 1   | 1   | Fosc/2 <sup>21</sup> | Fosc/2 <sup>21</sup> + 512 |

T0S0-1&T1S0-1: Timer0 & Timer1 clock source mode select bits. These bits determine the timer0 & timer1 clock source.

| T0S1<br>(T1S1) | T0S0<br>(T1S0) | Prescale Clock<br>Source |

|----------------|----------------|--------------------------|

| 0              | 0              | Fosc/2 <sup>2</sup>      |

| 0              | 1              | Fosc/2 <sup>6</sup>      |

| 1              | 0              | Fosc/2 <sup>10</sup>     |

| 1              | 1              | Fs                       |

|                |                |                          |

DIVS: Divider clock source control bit 1:

DIVS = 0 : Fs/2<sup>13</sup> DIVS= 1 : Fs/2<sup>14</sup>

# $\overline{M}$ /S: System clock source control bit: $\overline{M}$ /S = 0 : Fosc = XIN1 (F<sub>M</sub>) $\overline{M}$ /S = 1 : Fosc = XIN2 (Fs)

### CLOCK CONTROL2

|       |       |     |     |   | (initial = 0 | 0H) |   |

|-------|-------|-----|-----|---|--------------|-----|---|

| 7     | 6     | 5   | 4   | 3 | 2            | 1   | 0 |

| ENBUZ | BUZSL | KT1 | KT0 | - | -            | -   | - |

Mnemonic: CKCON2

Bit:

Address: 8Fh

- ENBUZ: When ENBUZ=1 the BUZ pin works as buzzer output, otherwise BUZ pin is in floating state.

- BUZSL: Buzzer output selection. When BUZSL=0 BUZ is the output of octave tone. When BUZZL=1, BUZ is the output of key tone.

- KT1-0: Key tone frequency sources from divider. When divider is enable, KT1 and KT0 determines the key tone frequency.

| KT1 | KT0 | Key tone<br>frequency |

|-----|-----|-----------------------|

| 0   | 0   | Low                   |

| 0   | 1   | 512Hz                 |

| 1   | 0   | 1024Hz                |

| 1   | 1   | 2048Hz                |

PORT 1

(initial=FFH,input mode)

| Bit: | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|

|      | P1.7 | P1.6 | P1.5 | P1.4 | P1.3 | P1.2 | P1.1 | P1.0 |

Mnemonic: P1

Address: 90h

P1.7-0: P1 can be selected as input or output mode by the P1IO register, at initial reset, P1IO is set to 1, so P1 is used as input mode. When P1IO is set to 0, the P1 is used as CMOS output mode. When P1EF are set and P1IO are set as input mode P1 can be used as external interrupt source. The functions are listed below.

| P1.0 : INT2.0 | External Interrupt 2 |

|---------------|----------------------|

| P1.1 : INT2.1 | External Interrupt 2 |

| P1.2 : INT2.2 | External Interrupt 2 |

| P1.3 : INT2.3 | External Interrupt 2 |

| P1.4 : INT3.0 | External Interrupt 3 |

| P1.5 : INT3.1 | External Interrupt 3 |

| P1.6 : INT3.2 | External Interrupt 3 |

| P1.7 : INT3.3 | External Interrupt 3 |

| Electronics Corp.                       |               |            |              |              |             |              |           |        |

|-----------------------------------------|---------------|------------|--------------|--------------|-------------|--------------|-----------|--------|

| EXTERNAL INTERRUPT FLAG (initial = 00H) |               |            |              |              |             |              |           |        |

| Bit:                                    | 7             | 6          | 5            | 4            | 3           | 2            | 1         | 0      |

|                                         | -             | -          | -            | COMPF        | DIVF        | CIDF         | IE3       | IE2    |

| Mnemor                                  | nic: EXIF     |            |              |              |             | Address: 9   | 91h       |        |

| COMPF: Comparator flag                  | g. Set by h   | ardware v  | when RES     | SC bit is fr | om low to   | high.        |           |        |

| DIVF: Divider overflow                  | flag.         |            |              |              |             |              |           |        |

| CIDF: CID interrupt flag                | g. Set by h   | ardware w  | hen at lea   | ast one of   | CID flags   | is set.      |           |        |

| IE3: External Interrup                  | t 3 flag. Se  | et by hard | ware whe     | n a falling  | edge is d   | etected o    | n INT3.   |        |

| IE2: External Interrup                  | ot 2 flag. Se | et by hard | ware whe     | n a falling  | edge is d   | etected o    | n INT2.   |        |

| ROM PAGE POINTER                        |               |            |              |              |             | (initial = 0 | 0H)       |        |

| Bit:                                    | 7             | 6          | 5            | 4            | 3           | 2            | 1         | 0      |

|                                         | -             | -          | LT1          | LT0          | -           | -            | -         | PG     |

| Mnemon                                  | nic: RPAGE    | Ξ          |              |              | ,           | Address: 9   | 92h       |        |

|                                         |               |            |              |              |             |              |           |        |

| LT1 and LT0 determine t                 | the ROM p     | age of the | e instructio | on MOVC      | reading th  | ne content   | t from RO | M.     |

| F                                       | ROM PAGE      | Rom        | address      |              |             |              |           |        |

| (LT1, LT0) = (0, 0) F                   | Page 0        | 00000      | 0H-0FFFF     | 4            |             |              |           |        |

|                                         | Page 1        |            | 0H-1FFFF     |              |             |              |           |        |

|                                         | Page 2        |            | 0H-2FFFF     |              |             |              |           |        |

|                                         | age 3         |            | 0H-3FFFF     |              |             |              |           |        |

| PG = 0 indicates the exe                | • •           | -          |              |              |             |              |           |        |

| PG = 1 indicates the exe                | cuting pro    | gram is in | page 1, f    | rom 1000     | 0H-1FFFF    | Ή            |           |        |

| P1 PINS STATUS                          |               |            |              |              |             | (initial = 0 | 0H)       |        |

| Bit:                                    | 7             | 6          | 5            | 4            | 3           | 2            | 1         | 0      |

|                                         | P1.7SR        | P1.6SR     | P1.5SR       | P1.4SR       | P1.3SR      | P1.2SR       | P1.1SR    | P1.0SR |

| Mnemor                                  | nic: P1SR     |            |              |              | /           | Address: 9   | 93h       |        |

| P1SR: Set when a fallin                 | g edge is o   | detected c | on the cori  | respondin    | g P1 pin, o | clear by s   | oftware.  |        |

| P0 I/O PORT CONTROL                     | -             |            |              |              |             | (initial = F | FH)       |        |

| Bit:                                    | 7             | 6          | 5            | 4            | 3           | 2            | 1         | 0      |

|                                         | P0.7IO        | P0.6IO     | P0.5IO       | P0.4IO       | P0.3IO      | P0.2IO       | P0.1IO    | P0.0IO |

| Mnemonic: P0IO Address: 94h             |               |            |              |              |             |              |           |        |

| P0IO: P0 pins I/O conti                 |               |            |              |              | ,           |              |           |        |

| 1: input mode                           |               |            |              |              |             |              |           |        |

| 0: output mode                          |               |            |              |              |             |              |           |        |

|                                         |               |            |              |              |             |              |           |        |

|                                         |               |            |              |              |             |              |           |        |

| P1 I/O | PORT CONTROL                                          |            |            |            |        |        | (initial = F | FH)    |        |

|--------|-------------------------------------------------------|------------|------------|------------|--------|--------|--------------|--------|--------|

|        | Bit:                                                  | 7          | 6          | 5          | 4      | 3      | 2            | 1      | 0      |

|        |                                                       | P1.7IO     | P1.6IO     | P1.5IO     | P1.4IO | P1.3IO | P1.2IO       | P1.1IO | P1.0IO |

|        | Mnemoni                                               | c: P1IO    |            |            |        |        | Address: 9   | 95h    |        |

| P1IO:  | P1 pins I/O contro                                    | ol.        |            |            |        |        |              |        |        |

|        | 1: input mode                                         |            |            |            |        |        |              |        |        |

|        | 0: output mode                                        |            |            |            |        |        |              |        |        |

| P2 I/O | PORT CONTROL                                          |            |            |            |        |        | (initial = F | FH)    |        |

|        | Bit:                                                  | 7          | 6          | 5          | 4      | 3      | 2            | 1      | 0      |

|        |                                                       | P2.7IO     | P2.6IO     | P2.5IO     | P2.4IO | P2.3IO | P2.2IO       | P2.1IO | P2.0IO |

|        | Mnemoni                                               | c: P2IO    |            |            |        |        | Address: 9   | 96h    |        |

| P2IO:  | P2 pins I/O contro<br>1: input mode<br>0: output mode | ol.        |            |            |        |        |              |        |        |

| P3 I/O | PORT CONTROL                                          |            |            |            |        |        | (initial = F | FH)    |        |

|        | Bit:                                                  | 7          | 6          | 5          | 4      | 3      | 2            | 1      | 0      |

|        |                                                       | P3.7IO     | P3.6IO     | P3.5IO     | P3.4IO | P3.3IO | P3.2IO       | P3.1IO | P3.0IO |

|        | Mnemoni                                               | c: P3IO    |            |            |        |        | Address: 9   | 97h    |        |

| P3IO:  | P3 pins I/O contro<br>1: input mode<br>0: output mode | ol.        |            |            |        |        |              |        |        |

| P1 PIN | IS INTERRUPT EA                                       | BLE        |            |            |        |        | (initial = 0 | 0H)    |        |

|        | Bit:                                                  | 7          | 6          | 5          | 4      | 3      | 2            | 1      | 0      |

|        |                                                       | P1.7EF     | P1.6EF     | P1.5EF     | P1.4EF | P1.3EF | P1.2EF       | P1.1EF | P1.0EF |

|        | Mnemoni                                               | c: P1EF    |            |            |        |        | Address: §   | 9Bh    |        |

| P1EF:  | P1 pins interrupt                                     | function e | nabled/dis | sabled reg | gister |        |              |        |        |

|        | 0: disable                                            |            |            |            |        |        |              |        |        |

|        | 1: enable                                             |            |            |            |        |        |              |        |        |

| P1 PU  | LL-HIGH CONTRO                                        | DL         |            |            |        |        | (initial = 0 | 0H)    |        |

|        | Bit:                                                  | 7          | 6          | 5          | 4      | 3      | 2            | 1      | 0      |

|        |                                                       | P1.7H      | P1.6H      | P1.5H      | P1.4H  | P1.3H  | P1.2H        | P1.1H  | P1.0H  |

|        | Mnemoni                                               | c: P1H     |            |            |        | /      | Address: 9   | 9Dh    |        |

|        |                                                       |            |            |            |        |        |              |        |        |

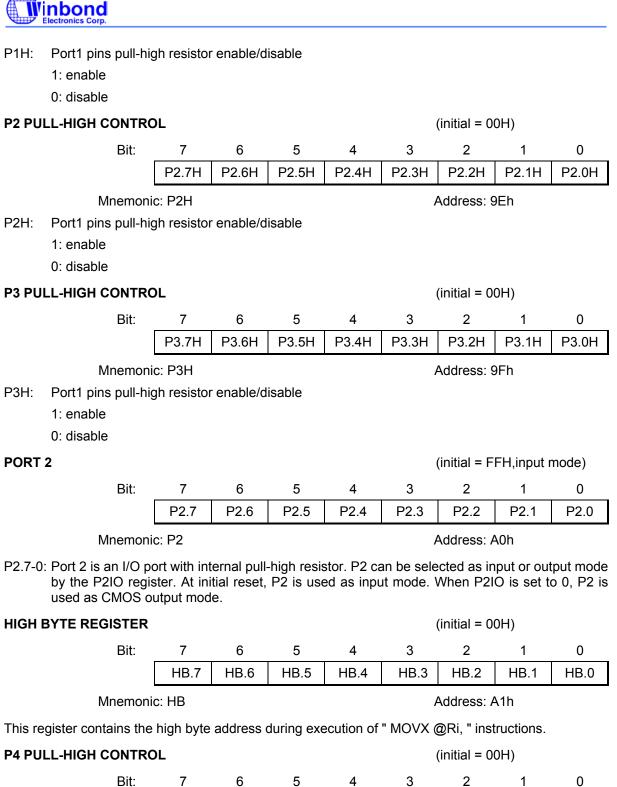

#### P4H: Port4 pins pull-high resistor enable/disable

- 1: enable

- 0: disable

### PORT 4

(initial = FFH,input mode)

| Bit:         | 7    | 6    | 5    | 4    | 3    | 2          | 1    | 0    |

|--------------|------|------|------|------|------|------------|------|------|

|              | P4.7 | P4.6 | P4.5 | P4.4 | P4.3 | P4.2       | P4.1 | P4.0 |

| Mnemonic: P4 |      |      |      |      | A    | Address: A | \6h  |      |

P4.7-0: Port 4 is an I/O port with internal pull-high resistor. P4 can be selected as input or output mode by the P4IO register. At initial reset, P4IO is set to 0FFh, P4 is used as input mode. When P4IO is set to 00h, P4 is used as CMOS output mode. Special function of P4 is described below.

| P4.4 | VPOS  | Positive input of the comparator                       |

|------|-------|--------------------------------------------------------|

| P4.2 | VNEG  | Negative input of the comparator                       |

| P4.1 | SDATA | Serial port data I/O                                   |

| P4.0 | SCLK  | Serial port clock I/O with Smith trigger in input path |

| A III | inbond            |

|-------|-------------------|

|       | Electronics Corp. |

| PORT 3 |              |            |      |           |          |             | (initial = F | FH,input r | mode) |

|--------|--------------|------------|------|-----------|----------|-------------|--------------|------------|-------|

|        | Bit:         | 7          | 6    | 5         | 4        | 3           | 2            | 1          | 0     |

|        |              | P3.7       | P3.6 | P3.5      | P3.4     | P3.3        | P3.2         | P3.1       | P3.0  |

|        | Address: B0h |            |      |           |          |             |              |            |       |

|        | n ha aalaati | ad an immu |      | t made by | the DOIC | \ realister |              |            |       |

P3.7-0: P3 can be selected as input or output mode by the P3IO register, at initial reset, P3IO is set to 0FFH, P3 is used as input mode. When P3IO is set to 00h, the P3 is used as CMOS output mode. Special function of P3 is described below.

| P3.5 | T1          | Timer/Counter 1 external count input |

|------|-------------|--------------------------------------|

| P3.4 | Т0          | Timer/Counter 0 external count input |

| P3.3 | INT1        | External interrupt 1                 |

| P3.2 | <b>INTO</b> | External interrupt 0                 |

### CID REGISTER

(initial = 00H,**read only**)

| Bit: | 7 | 6    | 5     | 4   | 3     | 2   | 1    | 0   |

|------|---|------|-------|-----|-------|-----|------|-----|

|      | - | FCLK | FDATA | FCD | DTMFD | FDR | ALGO | RNG |

|      |   |      |       |     |       |     |      |     |

Mnemonic: CIDR

Address: B1h

This SFR indicates the CID signal immediately. Register data is set or cleared by hardware only.

FCLK: FSK serial clock with the baud rate of 1200Hz.

FDATA: FSK serial bit data.

FCD: Set when FSK carrier is detected. Cleared when FSK carrier is disappeared.

DTMFD: Set when DTMF decoded data is ready. Cleared when DTMF signal ends.

FDR: Set when FSK 8 bits data is ready. Cleared before next FSK start bit comes

ALGO: Dual tone Alert signal Guard time detect signal. Set when a guard time qualified dual tone alert signal has been detected. Cleared when the guard time qualified dual tone alert signal is absent.

RNG: Ring detection bit. High to indicate the detection of line reversal and/or ringing.

| CID FLAG GENERATOR | (initial = 00H) |   |   |     |              |      |       |      |  |

|--------------------|-----------------|---|---|-----|--------------|------|-------|------|--|

| Bit:               | 7               | 6 | 5 | 4   | 3            | 2    | 1     | 0    |  |

|                    | -               | - | - | FSF | DTMFDF       | FDRF | ALGOF | RNGF |  |

| Mnemonic: CIDFG    |                 |   |   |     | Address: B2h |      |       |      |  |

FSF: Set when FSK Latch clock low to high. Cleared by software

DTMFDF: Set when DTMFD low to high. Cleared by software

FDRF: Set when FDR low to high. Cleared by software.

ALGOF: Set when ALGO low to high. Cleared by software.

RNGF: Set when RNG low to high. Cleared by software.

| CID POWER CONTROL                   | REGISTE                                  | R           |             |           | (         | (initial = 0 | 0H)  |       |  |  |

|-------------------------------------|------------------------------------------|-------------|-------------|-----------|-----------|--------------|------|-------|--|--|

| Bit:                                | 7                                        | 6           | 5           | 4         | 3         | 2            | 1    | 0     |  |  |

|                                     | -                                        | -           | -           | CIDE      | -         | FSKE         | CASE | DTMFE |  |  |

| Mnemoni                             | c: CIDPCI                                | २           |             |           | ŀ         | Address: E   | 33h  |       |  |  |

| CIDE: Global enable CI              | D function                               | . Low to c  | disable all | functions | of CID pa | rts.         |      |       |  |  |

| FSKE: Enable FSK dem                | odulation                                | circuit.    |             |           |           |              |      |       |  |  |

| CASE: Enable Dual Tone              | e Alert Sig                              | nal detec   | tion circui | t.        |           |              |      |       |  |  |

| DTMFE: Enable DTMF de               | DTMFE: Enable DTMF demodulation circuit. |             |             |           |           |              |      |       |  |  |

| FSK DATA REGISTER (initial = XXH)   |                                          |             |             |           |           |              |      |       |  |  |

| Bit:                                | 7                                        | 6           | 5           | 4         | 3         | 2            | 1    | 0     |  |  |

|                                     | FD7                                      | FD6         | FD5         | FD4       | FD3       | FD2          | FD1  | FD0   |  |  |

| Mnemonic: FSKDR Address: B4h        |                                          |             |             |           |           |              |      |       |  |  |

| FD7-0: 8 bits FSK demodulated data. |                                          |             |             |           |           |              |      |       |  |  |

| DTMF DATA REGISTER                  |                                          |             |             |           |           | (initial = X | XH)  |       |  |  |

| Bit:                                | 7                                        | 6           | 5           | 4         | 3         | 2            | 1    | 0     |  |  |

|                                     | CASH                                     | CASL        | DTMFH       | DTMFL     | DD3       | DD2          | DD1  | DD0   |  |  |

| Mnemoni                             | c: DTMFD                                 | R           |             |           | ŀ         | Address: E   | 35h  |       |  |  |

| CASH: Set when Dual                 | Tone Alert                               | Signal hi   | igh tone is | detected  |           |              |      |       |  |  |

| CASL: Set when Dual                 | Tone Alert                               | Signal Io   | w tone is   | detected. |           |              |      |       |  |  |

| DTMFH: Set when DTMF                | <sup>-</sup> high tone                   | e is detec  | ted.        |           |           |              |      |       |  |  |

| DTMFL: Set when DTMF                | low tone                                 | is detected | ed.         |           |           |              |      |       |  |  |

| DD3-0: 4 bits DTMF de               | modulated                                | l data.     |             |           |           |              |      |       |  |  |

| DTMF PRESENT TIME F                 | REGISTER                                 | R           |             |           |           | (initial = 1 | 9H)  |       |  |  |

| Bit:                                | 7                                        | 6           | 5           | 4         | 3         | 2            | 1    | 0     |  |  |

|                                     | DPT7                                     | DPT6        | DPT5        | DPT4      | DPT3      | DPT2         | DPT1 | DPT0  |  |  |

| Mnemonic: DTMFPT Address: B6h       |                                          |             |             |           |           |              |      |       |  |  |

The clock period of guard-time timer is 0.8582mS. The default DTMF present time is 21.45mS.

DPT7-0: The pre-set data register for counting DTMF present time. When DTMF is detected(Est, low to high), the guard timer starts to up-count from 00H. As the guard timer is equal to the value of DTMFPT, the exist of the DTMF is accepted. Est changes to low state to stop and reset the counter.

| DTMF ABSENT TIME RE | GISTER |      | (initial = 19H) |      |              |      |      |      |  |  |

|---------------------|--------|------|-----------------|------|--------------|------|------|------|--|--|

| Bit:                | 7      | 6    | 5               | 4    | 3            | 2    | 1    | 0    |  |  |

|                     | DAT7   | DAT6 | DAT5            | DAT4 | DAT3         | DAT2 | DAT1 | DAT0 |  |  |

| Mnemonic: DTMFAT    |        |      |                 |      | Address: B7h |      |      |      |  |  |

The clock period of guard-time timer is 0.8582mS. The default DTMF absent time is 21.45mS.

DAT7-0: The pre-set data register for counting DTMF absent time. When DTMF is absent(Est, high to low), the guard timer starts to up-count from 00H. As the guard timer is equal to the value of DTMFAT, the finish of DTMF is recognized. Est changes to low state to stop and reset the counter.

### INTERRUPT PRIORITY

| ORITY |   |     | (initial = 00H) |   |     |     |     |     |  |  |  |

|-------|---|-----|-----------------|---|-----|-----|-----|-----|--|--|--|

| Bit:  | 7 | 6   | 5               | 4 | 3   | 2   | 1   | 0   |  |  |  |

|       | - | PS1 | -               | - | PT1 | PX1 | PT0 | PX0 |  |  |  |

|       |   |     |                 |   |     |     |     |     |  |  |  |

Mnemonic: IP

Address: B8h

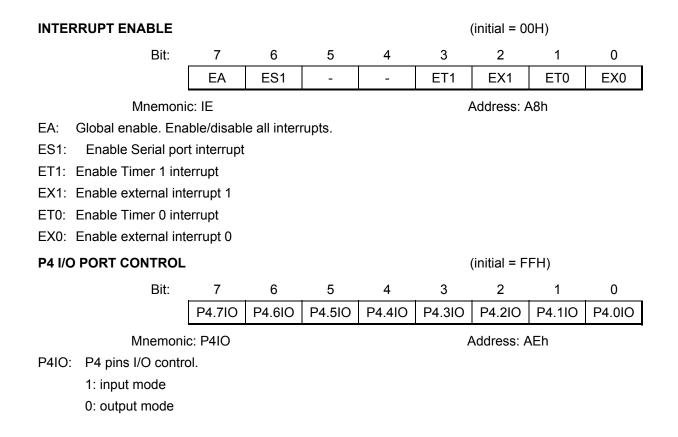

IP.7: This bit is un-implemented and will read high.

PS1: This bit defines the Serial port interrupt priority. PS1 = 1 sets it to higher priority level

PT1: This bit defines the Timer 1 interrupt priority. PT1 = 1 sets it to higher priority level.

PX1: This bit defines the External interrupt 1 priority. PX1 = 1 sets it to higher priority level.

PT0: This bit defines the Timer 0 interrupt priority. PT0 = 1 sets it to higher priority level.

PX0: This bit defines the External interrupt 0 priority. PX0 = 1 sets it to higher priority level.

### DTMF GENERATOR REGISTER

| Bit: | 7 | 6    | 5  | 4  | 3  | 2  | 1  | 0  |

|------|---|------|----|----|----|----|----|----|

|      | - | DTGE | HE | LE | L1 | L0 | H1 | H0 |

Mnemonic: DTMFG

| L1 | L0 | H1 | H0 | Selected tone |

|----|----|----|----|---------------|

| х  | х  | 0  | 0  | 1209Hz        |

| х  | х  | 0  | 1  | 1336Hz        |

| х  | х  | 1  | 0  | 1477Hz        |

| х  | х  | 1  | 1  | 1633Hz        |

| 0  | 0  | х  | х  | 697Hz         |

| 0  | 1  | Х  | х  | 770Hz         |

| 1  | 0  | х  | х  | 852Hz         |

| 1  | 1  | х  | х  | 941Hz         |

LE: Enable low group frequency output.

HE: Enable high group frequency output.

DTGE: Enable dual tone output to DTMF pin.

Address: BAh

(initial = 00H)

| Electroni   | cs Corp.                                                                                                                                                                           |                                                             |              |             |    |                 |         |          |        |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------|-------------|----|-----------------|---------|----------|--------|--|--|--|

| COMPARA     | TOR REGIST                                                                                                                                                                         | ER                                                          |              |             |    | (initial = 00H) |         |          |        |  |  |  |

| Bit:        | 7                                                                                                                                                                                  | 6                                                           | 5            | 4           | 3  | 5               | 2       | 1        | 0      |  |  |  |

|             | -                                                                                                                                                                                  | -                                                           | -            | -           | RE | SC              | REF     | -        | COMPEN |  |  |  |

|             | Mnemoni                                                                                                                                                                            | c: COMPF                                                    | ર            |             |    |                 | Addres  | s: BBh   |        |  |  |  |

| RESC:       | Result of the comparator. Set when positive analog input voltage is(VPOS or 1.0v internal regular output) higher than negative analog input voltage(VNEG) RESC is a read only bit. |                                                             |              |             |    |                 |         |          |        |  |  |  |