Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 4 M × 4 BANKS × 16 BITS DDR SDRAM

# Table of Contents-

| 1. | GEN  | IERAL DESCRIPTION                                             | 4  |

|----|------|---------------------------------------------------------------|----|

| 2. | FEAT | TURES                                                         | 4  |

| 3. | ORD  | PER INFORMATION                                               | 4  |

| 4. | KEY  | PARAMETERS                                                    | 5  |

| 5. | BALL | L CONFIGURATION                                               | 6  |

| 6. | BALL | L DESCRIPTION                                                 | 7  |

| 7. | BLO  | CK DIAGRAM                                                    | 8  |

| 8. |      | CTIONAL DESCRIPTION                                           |    |

| 0. | 8.1  | Power Up Sequence                                             | -  |

|    | 8.2  | Command Function                                              |    |

|    | 0.2  | 8.2.1 Bank Activate Command                                   |    |

|    |      | 8.2.2 Bank Precharge Command                                  |    |

|    |      | 8.2.3 Precharge All Command                                   |    |

|    |      | 8.2.4 Write Command                                           |    |

|    |      | 8.2.5 Write with Auto-precharge Command                       | 10 |

|    |      | 8.2.6 Read Command                                            | 10 |

|    |      | 8.2.7 Read with Auto-precharge Command                        | 10 |

|    |      | 8.2.8 Mode Register Set Command                               | 11 |

|    |      | 8.2.9 Extended Mode Register Set Command                      |    |

|    |      | 8.2.10 No-Operation Command                                   | 11 |

|    |      | 8.2.11 Burst Read Stop Command                                | 11 |

|    |      | 8.2.12 Device Deselect Command                                | 11 |

|    |      | 8.2.13 Auto Refresh Command                                   |    |

|    |      | 8.2.14 Self Refresh Entry Command                             |    |

|    |      | 8.2.15 Self Refresh Exit Command                              |    |

|    |      | 8.2.16 Data Write Enable /Disable Command                     |    |

|    | 8.3  | Read Operation                                                |    |

|    | 8.4  | Write Operation                                               |    |

|    | 8.5  | Precharge                                                     |    |

|    | 8.6  | Burst Termination                                             |    |

|    | 8.7  | Refresh Operation                                             |    |

|    | 8.8  | Power Down Mode                                               |    |

|    | 8.9  | Input Clock Frequency Change during Precharge Power Down Mode | 14 |

# massas winbond sassas

|     | 8.10  | Mode Register Operation                                                   | 14 |

|-----|-------|---------------------------------------------------------------------------|----|

|     |       | 8.10.1 Burst Length field (A2 to A0)                                      | 14 |

|     |       | 8.10.2 Addressing Mode Select (A3)                                        | 15 |

|     |       | 8.10.3 CAS Latency field (A6 to A4)                                       | 16 |

|     |       | 8.10.4 DLL Reset bit (A8)                                                 | 16 |

|     |       | 8.10.5 Mode Register /Extended Mode register change bits (BA0, BA1)       | 16 |

|     |       | 8.10.6 Extended Mode Register field                                       | 16 |

|     |       | 8.10.7 Reserved field                                                     | 16 |

| 9.  | OPE   | RATION MODE                                                               | 17 |

|     | 9.1   | Simplified Truth Table                                                    | 17 |

|     | 9.2   | Function Truth Table                                                      | 18 |

|     | 9.3   | Function Truth Table for CKE                                              | 21 |

|     | 9.4   | Simplified Stated Diagram                                                 | 22 |

| 10. | ELEC  | TRICAL CHARACTERISTICS                                                    | 23 |

|     | 10.1  | Absolute Maximum Ratings                                                  | 23 |

|     | 10.2  | Recommended DC Operating Conditions                                       | 23 |

|     | 10.3  | Capacitance                                                               | 24 |

|     | 10.4  | Leakage and Output Buffer Characteristics                                 | 24 |

|     | 10.5  | DC Characteristics                                                        | 25 |

|     | 10.6  | AC Characteristics and Operating Condition                                | 26 |

|     | 10.7  | AC Test Conditions                                                        | 27 |

| 11. | SYST  | EM CHARACTERISTICS FOR DDR SDRAM                                          | 29 |

|     | 11.1  | Table 1: Input Slew Rate for DQ, DQS, and DM                              | 29 |

|     | 11.2  | Table 2: Input Setup & Hold Time Derating for Slew Rate                   | 29 |

|     | 11.3  | Table 3: Input/Output Setup & Hold Time Derating for Slew Rate            | 29 |

|     | 11.4  | Table 4: Input/Output Setup & Hold Derating for Rise/Fall Delta Slew Rate | 29 |

|     | 11.5  | Table 5: Output Slew Rate Characteristics (X16 Devices only)              | 29 |

|     | 11.6  | System Notes:                                                             | 30 |

| 12. | TIMIN | NG WAVEFORMS                                                              | 32 |

|     | 12.1  | Command Input Timing                                                      | 32 |

|     | 12.2  | Timing of the CLK Signals                                                 | 32 |

|     | 12.3  | Read Timing (Burst Length = 4)                                            | 33 |

|     | 12.4  | Write Timing (Burst Length = 4)                                           | 34 |

|     | 12.5  | DM, DATA MASK (W9425G6JB)                                                 |    |

|     | 12.6  | Mode Register Set (MRS) Timing                                            |    |

|     | 12.7  | Extend Mode Register Set (EMRS) Timing                                    |    |

|     | 12.8  | Auto-precharge Timing (Read Cycle, CL = 2)                                | 38 |

# W9425G6JB

# **Esses winbond**

|     | 12.9  | Auto-precharge Timing (Read cycle, CL = 2), continued                | . 39 |

|-----|-------|----------------------------------------------------------------------|------|

|     | 12.10 | Auto-precharge Timing (Write Cycle)                                  | . 40 |

|     | 12.11 | Read Interrupted by Read (CL = 2, BL = 2, 4, 8)                      | . 41 |

|     | 12.12 | Burst Read Stop (BL = 8)                                             | . 41 |

|     | 12.13 | Read Interrupted by Write & BST (BL = 8)                             | . 42 |

|     | 12.14 | Read Interrupted by Precharge (BL = 8)                               | . 42 |

|     | 12.15 | Write Interrupted by Write (BL = 2, 4, 8)                            | . 43 |

|     | 12.16 | Write Interrupted by Read (CL = 2, BL = 8)                           | . 43 |

|     | 12.17 | Write Interrupted by Read (CL = 3, BL = 4)                           | . 44 |

|     | 12.18 | Write Interrupted by Precharge (BL = 8)                              | . 44 |

|     | 12.19 | 2 Bank Interleave Read Operation (CL = 2, BL = 2)                    | . 45 |

|     | 12.20 | 2 Bank Interleave Read Operation (CL = 2, BL = 4)                    | . 45 |

|     | 12.21 | 4 Bank Interleave Read Operation (CL = 2, BL = 2)                    | . 46 |

|     | 12.22 | 4 Bank Interleave Read Operation (CL = 2, BL = 4)                    | . 46 |

|     | 12.23 | Auto Refresh Cycle                                                   | . 47 |

|     | 12.24 | Precharged/Active Power Down Mode Entry and Exit Timing              | . 47 |

|     | 12.25 | Input Clock Frequency Change during Precharge Power Down Mode Timing | . 47 |

|     | 12.26 | Self Refresh Entry and Exit Timing                                   | . 48 |

| 13. | PACK  | AGE SPECIFICATION                                                    | . 49 |

| 14. | REVIS | SION HISTORY                                                         | . 50 |

|     |       |                                                                      |      |

# 1. GENERAL DESCRIPTION

W9425G6JB is a CMOS Double Data Rate synchronous dynamic random access memory (DDR SDRAM), organized as 4,194,304 words  $\times$  4 banks  $\times$  16 bits. W9425G6JB delivers a data bandwidth of up to 400M words per second (-5). To fully comply with the personal computer industrial standard, W9425G6JB is sorted into two speed grades: 5 and -5I. The -5/-5I is compliant to the DDR400/CL3 specification (the -5I grade which is guaranteed to support -40°C  $\sim$  85°C).

All Input reference to the positive edge of CLK (except for DQ, DM and CKE). The timing reference point for the differential clock is when the CLK and  $\overline{\text{CLK}}$  signals cross during a transition. Write and Read data are synchronized with the both edges of DQS (Data Strobe).

By having a programmable Mode Register, the system can change burst length, latency cycle, interleave or sequential burst to maximize its performance. W9425G6JB is ideal for main memory in high performance applications.

### 2. FEATURES

- 2.5V ± 0.2V Power Supply

- Up to 200 MHz Clock Frequency

- Double Data Rate architecture; two data transfers per clock cycle

- Differential clock inputs (CLK and CLK)

- DQS is edge-aligned with data for Read; center-aligned with data for Write

- CAS Latency: 2, 2.5 and 3

- Burst Length: 2, 4 and 8

- Auto Refresh and Self Refresh

- Precharged Power Down and Active Power Down

- Write Data Mask

- Write Latency = 1

- 7.8µS refresh interval (8K/ 64 mS refresh)

- Maximum burst refresh cycle: 8

- Interface: SSTL 2

- Packaged in 60 Ball TFBGA (8X13 mm²), using Lead free materials with RoHS compliant

# 3. ORDER INFORMATION

| PART NUMBER  | SPEED      | SELF REFRESH<br>CURRENT (MAX.) | OPERATING<br>TEMPERATURE |

|--------------|------------|--------------------------------|--------------------------|

| W9425G6JB-5  | DDR400/CL3 | 2 mA                           | 0°C ~ 70°C               |

| W9425G6JB-5I | DDR400/CL3 | 2 mA                           | -40°C ~ 85°C             |

# 4. KEY PARAMETERS

| SYMBOL | DESCRIPTION                             |             | MIN./MAX. | -5/-5 <b>l</b> |

|--------|-----------------------------------------|-------------|-----------|----------------|

|        |                                         | 01 0        | Min.      | 7.5 nS         |

|        |                                         | CL = 2      | Max.      | 12 nS          |

| tore   | Cleak Cyala Tima                        | CI OF       | Min.      | 6 nS           |

| tck    | Clock Cycle Time                        | CL = 2.5    | Max.      | 12 nS          |

|        |                                         | CL = 3      | Min.      | 5 nS           |

|        |                                         |             | Max.      | 12 nS          |

| tras   | Active to Precharge Command Period      |             | Min.      | 40 nS          |

| tRC    | Active to Ref/Active Command Period     | Min.        | 55 nS     |                |

| IDD0   | Operating Current: One Bank Active-Pred | harge       | Max.      | 65 mA          |

| IDD1   | Operating Current: One Bank Active-Read | d-Precharge | Max.      | 80 mA          |

| IDD4R  | Burst Operation Read Current            |             | Max.      | 120 mA         |

| IDD4W  | Burst Operation Write Current           |             | Max.      | 115 mA         |

| IDD5   | Auto Refresh Current                    |             | Max.      | 65 mA          |

| IDD6   | Self Refresh Current                    |             | Max.      | 2 mA           |

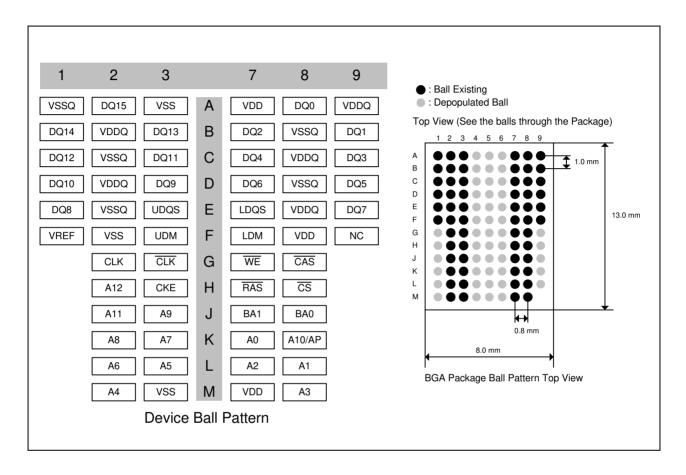

# 5. BALL CONFIGURATION

# 6. BALL DESCRIPTION

| BALL NUMBER                                                             | SYMBOL                                                                     | FUNCTION                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                         |                                                                            | -                            | Multiplexed pins for row and column address. Row address: A0–A12. Column address: A0–A8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| K7, L8, L7, M8,<br>M2, L3, L2, K3,<br>K2, J3, K8, J2, H2                | A0 – A12                                                                   | Address                      | Provide the row address for Bank Activate commands, and the column address and Auto-precharge bit (A10) for Read/Write commands, to select one location out of the memory array in the respective bank. A10 is sampled during a precharge command to determine whether the precharge applies to one bank (A10 Low) or all banks (A10 High). If only one bank is to be precharged, the bank is selected by BA0, BA1. The address inputs also provide the op-code during a Mode Register Set command. BA0 and BA1 define which mode register is loaded during the Mode Register Set command (MRS or EMRS). |

| J8, J7                                                                  | BA0, BA1                                                                   | Bank Select                  | Select bank to activate during row address latch time, or bank to read/write during column address latch time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A8, B9, B7, C9,<br>C7, D9, D7, E9,<br>E1, D3, D1, C3,<br>C1, B3, B1, A2 | DQ0 –<br>DQ15                                                              | Data Input/ Output           | The DQ0 – DQ15 input and output data are synchronized with both edges of DQS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| E7, E3                                                                  | LDQS,<br>UDQS                                                              | Data Strobe                  | DQS is Bi-directional signal. DQS is input signal during write operation and output signal during read operation. It is Edgealigned with read data, Center-aligned with write data.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| H8                                                                      | CS                                                                         | Chip Select                  | Disable or enable the command decoder. When command decoder is disabled, new command is ignored and previous operation continues.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| H7, G8, G7                                                              | $\overline{\text{RAS}}$ , $\overline{\text{CAS}}$ , $\overline{\text{WE}}$ | Command Inputs               | Command inputs (along with $\overline{\mbox{CS}}$ ) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| F7, F3                                                                  | LDM, UDM                                                                   | Write Mask                   | When DM is asserted "high" in burst write, the input data is masked. DM is synchronized with both edges of DQS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| G2, G3                                                                  | CLK,                                                                       | Differential Clock<br>Inputs | All address and control input signals are sampled on the crossing of the positive edge of CLK and negative edge of $\overline{\text{CLK}}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| НЗ                                                                      | CKE                                                                        | Clock Enable                 | CKE controls the clock activation and deactivation. When CKE is low, Power Down mode, Suspend mode, or Self Refresh mode is entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| F1                                                                      | VREF                                                                       | Reference Voltage            | VREF is reference voltage for inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| F8, M7, A7                                                              | VDD                                                                        | Power (+2.5V)                | Power for logic circuit inside DDR SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A3, F2, M3                                                              | Vss                                                                        | Ground                       | Ground for logic circuit inside DDR SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| B2, D2, C8, E8,<br>A9                                                   | VDDQ                                                                       | Power (+2.5V) for I/O Buffer | Separated power from VDD, used for output buffer, to improve noise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A1, C2, E2, B8,<br>D8                                                   | Vssq                                                                       | Ground for I/O<br>Buffer     | Separated ground from Vss, used for output buffer, to improve noise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| F9                                                                      | NC                                                                         | No Connection                | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

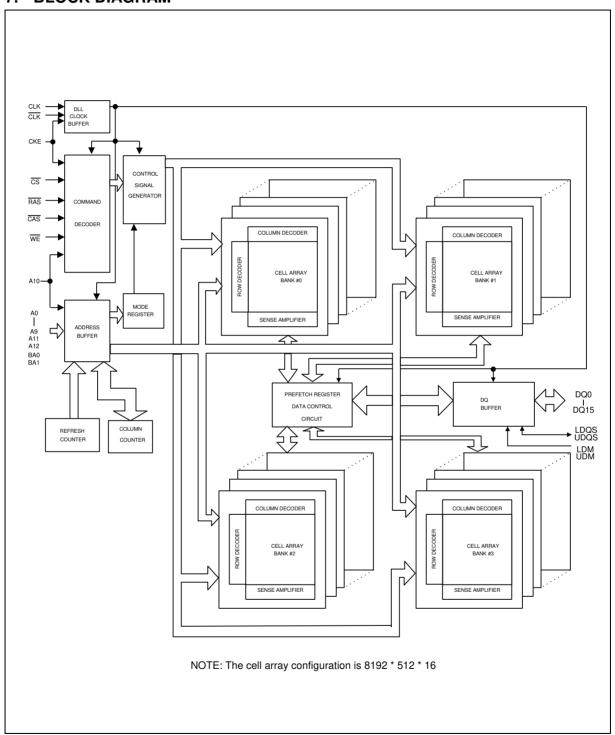

# 7. BLOCK DIAGRAM

- 8 -

# 8. FUNCTIONAL DESCRIPTION

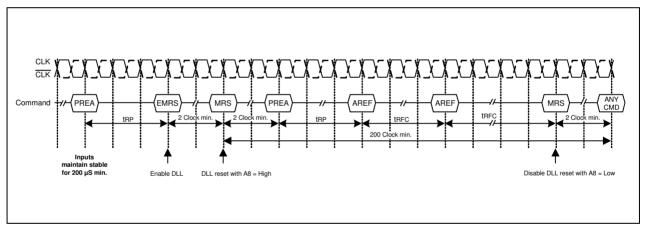

# 8.1 Power Up Sequence

- (1) Apply power and attempt to CKE at a low state ( $\leq 0.2V$ ), all other inputs may be undefined

- 1) Apply VDD before or at the same time as VDDQ.

- 2) Apply VDDQ before or at the same time as VTT and VREF.

- (2) Start Clock and maintain stable condition for 200 μS (min.).

- (3) After stable power and clock, apply NOP and take CKE high.

- (4) Issue precharge command for all banks of the device.

- (5) Issue EMRS (Extended Mode Register Set) to enable DLL and establish Output Driver Type.

- (6) Issue MRS (Mode Register Set) to reset DLL and set device to idle with bit A8. (An additional 200 cycles(min) of clock are required for DLL Lock before any executable command applied.)

- (7) Issue precharge command for all banks of the device.

- (8) Issue two or more Auto Refresh commands.

- (9) Issue MRS-Initialize device operation with the reset DLL bit deactivated A8 to low.

Initialization sequence after power-up

#### 8.2 Command Function

#### 8.2.1 Bank Activate Command

The Bank Activate command activates the bank designated by the BA (Bank address) signal. Row addresses are latched on A0 to A12 when this command is issued and the cell data is read out of the sense amplifiers. The maximum time that each bank can be held in the active state is specified as tRAS (max). After this command is issued, Read or Write operation can be executed.

# 8.2.2 Bank Precharge Command

$$(\overline{RAS} = "L", \overline{CAS} = "H", \overline{WE} = "L", BA0, BA1 = Bank, A10 = "L", A0 to A9, A11, A12 = Don't Care)$$

The Bank Precharge command percharges the bank designated by BA. The precharged bank is switched from the active state to the idle state.

# 8.2.3 Precharge All Command

$$(\overline{RAS} = "L", \overline{CAS} = "H", \overline{WE} = "L", BA0, BA1 = Don't Care, A10 = "H", A0 to A9, A11, A12 = Don't Care)$$

The Precharge All command precharges all banks simultaneously. Then all banks are switched to the idle state.

#### 8.2.4 Write Command

The write command performs a Write operation to the bank designated by BA. The write data are latched at both edges of DQS. The length of the write data (Burst Length) and column access sequence (Addressing Mode) must be in the Mode Register at power-up prior to the Write operation.

### 8.2.5 Write with Auto-precharge Command

$$(\overline{RAS} = "H", \overline{CAS} = "L", \overline{WE} = "L", BA0, BA1 = Bank, A10 = "H", A0 to A8 = Column Address)$$

The Write with Auto-precharge command performs the Precharge operation automatically after the Write operation. This command must not be interrupted by any other commands.

#### 8.2.6 Read Command

$$(\overline{RAS} = "H", \overline{CAS} = "L", \overline{WE} = "H", BA0, BA1 = Bank, A10 = "L", A0 to A8 = Column Address)$$

The Read command performs a Read operation to the bank designated by BA. The read data are synchronized with both edges of DQS. The length of read data (Burst Length), Addressing Mode and CAS Latency (access time from  $\overline{\text{CAS}}$  command in a clock cycle) must be programmed in the Mode Register at power-up prior to the Read operation.

#### 8.2.7 Read with Auto-precharge Command

The Read with Auto-precharge command automatically performs the Precharge operation after the Read operation.

1) READA≥tRAS (min) - (BL/2) x tCK

Internal precharge operation begins after BL/2 cycle from Read with Auto-precharge command.

2)  $tRCD(min) \le READA < tRAS(min) - (BL/2) x tCK$

Data can be read with shortest latency, but the internal Precharge operation does not begin until after tRAS (min) has completed.

This command must not be interrupted by any other command.

#### 8.2.8 Mode Register Set Command

The Mode Register Set command programs the values of CAS Latency, Addressing Mode, Burst Length and DLL reset in the Mode Register. The default values in the Mode Register after power-up are undefined, therefore this command must be issued during the power-up sequence. Also, this command can be issued while all banks are in the idle state. Refer to the table for specific codes.

#### 8.2.9 Extended Mode Register Set Command

$$(\overline{RAS} = "L", \overline{CAS} = "L", \overline{WE} = "L", BA0 = "H", BA1 = "L", A0 to A12 = Register data)$$

The Extended Mode Register Set command can be implemented as needed for function extensions to the standard (SDR-SDRAM). These additional functions include DLL enable/disable, output drive strength selection. The default value of the extended mode register is not defined; therefore this command must be issued during the power-up sequence for enabling DLL. Refer to the table for specific codes.

### 8.2.10 No-Operation Command

$$(\overline{RAS} = "H", \overline{CAS} = "H", \overline{WE} = "H")$$

The No-Operation command simply performs no operation (same command as Device Deselect).

### 8.2.11 Burst Read Stop Command

$$(\overline{RAS} = "H", \overline{CAS} = "H", \overline{WE} = "L")$$

The Burst stop command is used to stop the burst operation. This command is only valid during a Burst Read operation.

#### 8.2.12 Device Deselect Command

$$(CS = "H")$$

The Device Deselect command disables the command decoder so that the  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and Address inputs are ignored. This command is similar to the No-Operation command.

#### 8.2.13 Auto Refresh Command

AUTO REFRESH is used during normal operation of the DDR SDRAM and is analogous to CAS–BEFORE–RAS (CBR) refresh in previous DRAM types. This command is non persistent, so it must be issued each time a refresh is required.

The refresh addressing is generated by the internal refresh controller. This makes the address bits "Don't Care" during an AUTO REFRESH command. The DDR SDRAM requires AUTO REFRESH

cycles at an average periodic interval of

tREFI (maximum). To allow for improved efficiency in scheduling and switching between tasks, some flexibility in the absolute refresh interval is provided. A maximum of eight AUTO REFRESH commands can be posted to any given DDR SDRAM, and the maximum absolute interval between any AUTO REFRESH command and the next AUTO REFRESH command is 8 \* trefi.

# 8.2.14 Self Refresh Entry Command

$$(\overline{RAS} = "L", \overline{CAS} = "L", \overline{WE} = "H", CKE = "L", BA0, BA1, A0 to A12 = Don't Care)$$

The SELF REFRESH command can be used to retain data in the DDR SDRAM, even if the rest of the system is powered down. When in the self refresh mode, the DDR SDRAM retains data without external clocking. The SELF REFRESH command is initiated like an AUTO REFRESH command except CKE is disabled (LOW). The DLL is automatically disabled upon entering SELF REFRESH, and is automatically enabled upon exiting SELF REFRESH. Any time the DLL is enabled a DLL Reset must follow and 200 clock cycles should occur before a READ command can be issued. Input signals except CKE are "Don't Care" during SELF REFRESH. Since CKE is a SSTL 2 input, VREF must be maintained during SELF REFRESH.

#### 8.2.15 Self Refresh Exit Command

$$(CKE = "H", \overline{CS} = "H" \text{ or } CKE = "H", \overline{RAS} = "H", \overline{CAS} = "H")$$

The procedure for exiting self refresh requires a sequence of commands. First, CLK must be stable prior to CKE going back HIGH. Once CKE is HIGH, the DDR SDRAM must have NOP commands issued for txsnr because time is required for the completion of any internal refresh in progress. A simple algorithm for meeting both refresh and DLL requirements is to apply NOPs for 200 clock cycles before applying any other command.

The use of SELF REFREH mode introduces the possibility that an internally timed event can be missed when CKE is raised for exit from self refresh mode. Upon exit from SELF REFRESH an extra auto refresh command is recommended.

#### 8.2.16 Data Write Enable / Disable Command

(DM = "L/H" or LDM, UDM = "L/H")

During a Write cycle, the DM or LDM, UDM signal functions as Data Mask and can control every word of the input data. The LDM signal controls DQ0 to DQ7 and UDM signal controls DQ8 to DQ15.

# 8.3 Read Operation

Issuing the Bank Activate command to the idle bank puts it into the active state. When the Read command is issued after tRCD from the Bank Activate command, the data is read out sequentially, synchronized with both edges of DQS (Burst Read operation). The initial read data becomes available after CAS Latency from the issuing of the Read command. The CAS Latency must be set in the Mode Register at power-up.

When the Precharge Operation is performed on a bank during a Burst Read and operation, the Burst operation is terminated.

When the Read with Auto-precharge command is issued, the Precharge operation is performed automatically after the Read cycle then the bank is switched to the idle state. This command cannot be interrupted by any other commands. Refer to the diagrams for Read operation.

# 8.4 Write Operation

Issuing the Write command after tRCD from the bank activate command. The input data is latched sequentially, synchronizing with both edges(rising & falling) of DQS after the Write command (Burst write operation). The burst length of the Write data (Burst Length) and Addressing Mode must be set in the Mode Register at power-up.

When the Precharge operation is performed in a bank during a Burst Write operation, the Burst operation is terminated.

When the Write with Auto-precharge command is issued, the Precharge operation is performed automatically after the Write cycle, then the bank is switched to the idle state, The Write with Auto-precharge command cannot be interrupted by any other command for the entire burst data duration.

Refer to the diagrams for Write operation.

# 8.5 Precharge

There are two Commands, which perform the precharge operation (Bank Precharge and Precharge All). When the Bank Precharge command is issued to the active bank, the bank is precharged and then switched to the idle state. The Bank Precharge command can precharge one bank independently of the other bank and hold the unprecharged bank in the active state. The maximum time each bank can be held in the active state is specified as tRAS (max). Therefore, each bank must be precharged within tRAS(max) from the bank activate command.

The Precharge All command can be used to precharge all banks simultaneously. Even if banks are not in the active state, the Precharge All command can still be issued. In this case, the Precharge operation is performed only for the active bank and the precharge bank is then switched to the idle state.

#### 8.6 Burst Termination

When the Precharge command is used for a bank in a Burst cycle, the Burst operation is terminated. When Burst Read cycle is interrupted by the Precharge command, read operation is disabled after clock cycle of (CAS Latency) from the Precharge command. When the Burst Write cycle is interrupted by the Precharge command, the input circuit is reset at the same clock cycle at which the precharge command is issued. In this case, the DM signal must be asserted "high" during twn to prevent writing the invalided data to the cell array.

When the Burst Read Stop command is issued for the bank in a Burst Read cycle, the Burst Read operation is terminated. The Burst read Stop command is not supported during a write burst operation. Refer to the diagrams for Burst termination.

#### 8.7 Refresh Operation

Two types of Refresh operation can be performed on the device: Auto Refresh and Self Refresh. By repeating the Auto Refresh cycle, each bank in turn refreshed automatically. The Refresh operation must be performed 8192 times (rows) within 64mS. The period between the Auto Refresh command and the next command is specified by tRFC.

Self Refresh mode enters issuing the Self Refresh command (CKE asserted "low") while all banks are in the idle state. The device is in Self Refresh mode for as long as CKE held "low". In the case of distributed Auto Refresh commands, distributed auto refresh commands must be issued every 7.8  $\mu$ S and the last distributed Auto Refresh commands must be performed within 7.8  $\mu$ S before entering the self refresh mode. After exiting from the Self Refresh mode, the refresh operation must be performed within 7.8  $\mu$ S. In Self Refresh mode, all input/output buffers are disabled,

resulting in lower power dissipation (except CKE buffer). Refer to the diagrams for Refresh operation.

### 8.8 Power Down Mode

Two types of Power Down Mode can be performed on the device: Active Standby Power Down Mode and Precharge Standby Power Down Mode.

When the device enters the Power Down Mode, all input/output buffers and DLL are disabled resulting in low power dissipation (except CKE buffer).

Power Down Mode enter asserting CKE "low" while the device is not running a burst cycle. Taking CKE "high" can exit this mode. When CKE goes high, a No operation command must be input at next CLK rising edge. Refer to the diagrams for Power Down Mode.

# 8.9 Input Clock Frequency Change during Precharge Power Down Mode

DDR SDRAM input clock frequency can be changed under following condition:

DDR SDRAM must be in precharged power down mode with CKE at logic LOW level. After a minimum of 2 clocks after CKE goes LOW, the clock frequency may change to any frequency between minimum and maximum operating frequency specified for the particular speed grade. During an input clock frequency change, CKE must be held LOW. Once the input clock frequency is changed, a stable clock must be provided to DRAM before precharge power down mode may be exited. The DLL must be RESET via EMRS after precharge power down exit. An additional MRS command may need to be issued to appropriately set CL etc. After the DLL relock time, the DRAM is ready to operate with new clock frequency.

# 8.10 Mode Register Operation

The mode register is programmed by the Mode Register Set command (MRS/EMRS) when all banks are in the idle state. The data to be set in the Mode Register is transferred using the A0 to A12 and BA0, BA1 address inputs.

The Mode Register designates the operation mode for the read or write cycle. The register is divided into five filed: (1) Burst Length field to set the length of burst data (2) Addressing Mode selected bit to designate the column access sequence in a Burst cycle (3) CAS Latency field to set the assess time in clock cycle (4) DLL reset field to reset the DLL (5) Regular/Extended Mode Register filed to select a type of MRS (Regular/Extended MRS). EMRS cycle can be implemented the extended function (DLL enable/Disable mode).

The initial value of the Mode Register (including EMRS) after power up is undefined; therefore the Mode Register Set command must be issued before power operation.

#### 8.10.1 Burst Length field (A2 to A0)

This field specifies the data length for column access using the A2 to A0 pins and sets the Burst Length to be 2, 4, and 8 words.

| A2 | A1 | Α0 | BURST LENGTH |

|----|----|----|--------------|

| 0  | 0  | 0  | Reserved     |

| 0  | 0  | 1  | 2 words      |

| 0  | 1  | 0  | 4 words      |

| 0  | 1  | 1  | 8 words      |

| 1  | х  | Х  | Reserved     |

# 8.10.2 Addressing Mode Select (A3)

The Addressing Mode can be one of two modes; Interleave mode or Sequential Mode, When the A3 bit is "0", Sequential mode is selected. When the A3 bit is "1", Interleave mode is selected. Both addressing Mode support burst length 2, 4, and 8 words.

| А3 | ADDRESSING MODE |

|----|-----------------|

| 0  | Sequential      |

| 1  | Interleave      |

# 8.10.2.1. Addressing Sequence of Sequential Mode

A column access is performed by incrementing the column address input to the device. The address is varied by the Burst Length as the following.

## **Addressing Sequence of Sequential Mode**

| DATA   | ACCESS ADDRESS | BURST LENGTH                         |

|--------|----------------|--------------------------------------|

| Data 0 | n              | 2 words (address bits is A0)         |

| Data 1 | n + 1          | not carried from A0 to A1            |

| Data 2 | n + 2          | 4 words (address bit A0, A1)         |

| Data 3 | n + 3          | Not carried from A1 to A2            |

| Data 4 | n + 4          |                                      |

| Data 5 | n + 5          | 8 words (address bits A2, A1 and A0) |

| Data 6 | n + 6          | Not carried from A2 to A3            |

| Data 7 | n + 7          | $\mathcal{V}$                        |

# 8.10.2.2. Addressing Sequence for Interleave Mode

A Column access is started from the inputted column address and is performed by interleaving the address bits in the sequence shown as the following.

# **Addressing Sequence of Interleave Mode**

| DATA   | ACCESS ADDRESS                                 | BURST LENGTH |

|--------|------------------------------------------------|--------------|

| Data 0 | A8 A7 A6 A5 A4 A3 A2 A1 A0                     | 2 words      |

| Data 1 | A8 A7 A6 A5 A4 A3 A2 A1 $\overline{\text{A0}}$ |              |

| Data 2 | A8 A7 A6 A5 A4 A3 A2 A1 A0                     | 4 words      |

| Data 3 | A8 A7 A6 A5 A4 A3 A2 A1 A0                     |              |

| Data 4 | A8 A7 A6 A5 A4 A3 A2 A1 A0                     | 8 words      |

| Data 5 | A8 A7 A6 A5 A4 A3 A2 A1 A0                     |              |

| Data 6 | A8 A7 A6 A5 A4 A3 A2 A1 A0                     |              |

| Data 7 | A8 A7 A6 A5 A4 A3 A2 A1 A0                     | J            |

# 8.10.3 CAS Latency field (A6 to A4)

This field specifies the number of clock cycles from the assertion of the Read command to the first data read. The minimum values of CAS Latency depend on the frequency of CLK.

| A6 | <b>A</b> 5 | A4 | CAS LATENCY |

|----|------------|----|-------------|

| 0  | 0          | 0  | Reserved    |

| 0  | 0          | 1  | Reserved    |

| 0  | 1          | 0  | 2           |

| 0  | 1          | 1  | 3           |

| 1  | 0          | 0  | Reserved    |

| 1  | 0          | 1  | Reserved    |

| 1  | 1          | 0  | 2.5         |

| 1  | 1          | 1  | Reserved    |

#### 8.10.4 DLL Reset bit (A8)

This bit is used to reset DLL. When the A8 bit is "1", DLL is reset.

# 8.10.5 Mode Register /Extended Mode register change bits (BA0, BA1)

These bits are used to select MRS/EMRS.

| BA1 | BA0 | A12-A0             |

|-----|-----|--------------------|

| 0   | 0   | Regular MRS Cycle  |

| 0   | 1   | Extended MRS Cycle |

| 1   | Х   | Reserved           |

### 8.10.6 Extended Mode Register field

1) DLL Switch field (A0)

This bit is used to select DLL enable or disable

| A0 | DLL     |

|----|---------|

| 0  | Enable  |

| 1  | Disable |

### 2) Output Driver Size Control field (A6, A1)

The 100%, 60% and 30% or matched impedance driver strength are required Extended Mode Register Set (EMRS) as the following:

| A6 | A1 | BUFFER STRENGTH |  |  |  |

|----|----|-----------------|--|--|--|

| 0  | 0  | 100% Strength   |  |  |  |

| 0  | 1  | 60% Strength    |  |  |  |

| 1  | 0  | Reserved        |  |  |  |

| 1  | 1  | 30% Strength    |  |  |  |

#### 8.10.7 Reserved field

• Test mode entry bit (A7)

This bit is used to enter Test mode and must be set to "0" for normal operation.

Reserved bits (A9, A10, A11, A12)

These bits are reserved for future operations. They must be set to "0" for normal operation.

# 9. OPERATION MODE

The following table shows the operation commands.

# 9.1 Simplified Truth Table

| SYM.  | COMMAND                       | DEVICE<br>STATE       | CKEn-1 | CKEn | DM <sup>(4)</sup> | BA0,<br>BA1 | A10 | A12,<br>A11,<br>A9-A0 | CS | RAS | CAS | WE |

|-------|-------------------------------|-----------------------|--------|------|-------------------|-------------|-----|-----------------------|----|-----|-----|----|

| ACT   | Bank Active                   | Idle <sup>(3)</sup>   | Н      | Χ    | Х                 | ٧           | V   | V                     | ١  | Ш   | Η   | Н  |

| PRE   | Bank Precharge                | Any <sup>(3)</sup>    | Н      | Х    | Х                 | V           | L   | Х                     | L  | L   | Н   | L  |

| PREA  | Precharge All                 | Any                   | Н      | Χ    | Х                 | Х           | Н   | Х                     | L  | L   | Н   | L  |

| WRIT  | Write                         | Active <sup>(3)</sup> | Н      | Χ    | Х                 | V           | L   | V                     | L  | Н   | L   | L  |

| WRITA | Write with Auto-<br>precharge | Active <sup>(3)</sup> | Н      | Х    | Х                 | ٧           | Н   | V                     | L  | Н   | L   | L  |

| READ  | Read                          | Active <sup>(3)</sup> | Н      | Х    | Х                 | V           | L   | V                     | L  | Н   | L   | Н  |

| READA | Read with Auto-<br>precharge  | Active <sup>(3)</sup> | Н      | Х    | Х                 | ٧           | Н   | V                     | L  | Н   | L   | Н  |

| MRS   | Mode Register Set             | Idle                  | Н      | Х    | Х                 | L, L        |     |                       | L  | L   | L   | L  |

| EMRS  | Extended Mode<br>Register Set | Idle                  | Н      | Х    | Х                 | H, L        | Op- | Code <sup>(6)</sup>   | L  | L   | L   | L  |

| NOP   | No Operation                  | Any                   | Н      | Х    | Х                 | Х           | Х   | Х                     | L  | Н   | Н   | Н  |

| BST   | Burst Read Stop               | Active                | Н      | Х    | Х                 | Х           | Х   | Х                     | L  | Н   | Н   | L  |

| DSL   | Device Deselect               | Any                   | Н      | Х    | Х                 | Х           | Х   | Х                     | Н  | Х   | Х   | Х  |

| AREF  | Auto Refresh                  | Idle                  | Н      | Н    | Х                 | Х           | Х   | Х                     | L  | L   | L   | Н  |

| SELF  | Self Refresh Entry            | Idle                  | Η      | L    | Х                 | Х           | Х   | Х                     | L  | L   | Ш   | Н  |

| SELEX | Self Refresh Exit             | Idle (Self            | L      | Н    | Х                 | Х           | Х   | Х                     | Ι  | Χ   | Χ   | Х  |

| SELEX | Sell Reliesh Exit             | Refresh)              | L      | П    | ^                 | ^           | ^   | ^                     | L  | Η   | Η   | Х  |

| PD    | Power Down                    | Idle/                 | Н      | L    | Х                 | Х           | Х   | Х                     | Н  | Х   | Χ   | Х  |

| PD    | Mode Entry                    | Active <sup>(5)</sup> | П      | L    | ^                 | ^           | ^   | ^                     | L  | Н   | Н   | Х  |

| PDEX  | Power Down                    | Any (Power            | L      | Н    | Х                 | Х           | Х   | Х                     | Н  | Х   | Х   | Х  |

| FDEX  | Mode Exit                     | Down)                 |        |      | ^                 | ^           | ^   | ^                     | L  | Н   | Н   | Х  |

| WDE   | Data Write Enable             | Active                | Н      | Χ    | L                 | Х           | Х   | Х                     | Х  | Х   | Χ   | Х  |

| WDD   | Data Write Disable            | Active                | Н      | Х    | Н                 | Х           | Х   | Х                     | Х  | Х   | Χ   | Х  |

#### Notes:

- 1. V = Valid X = Don't Care L = Low level H = High level.

- 2.  $\mathsf{CKE}_n$  signal is input level when commands are issued

- CKE<sub>n-1</sub> signal is input level one clock cycle before the commands are issued

- 3. These are state designated by the BA0, BA1 signals.

- 4. LDM, UDM (W9425G6JB)

- 5. Power Down Mode can not entry in the burst cycle.

- 6. BA0, BA1 select either the Base or the Extended Mode Register (BA0 = 0, BA1 = 0 selects Mode Register; BA0 = 1, BA1 = 0 selects Extended Mode Register; other combinations of BA0, BA1 are reserved; A0~A12 provide the op-code to be written to the selected Mode Register (MRS or EMRS).

# 9.2 Function Truth Table

(Note 1)

| CURRENT<br>STATE | cs         | RAS | CAS | WE          | ADDRESS     | COMMAND    | ACTION                               | NOTES |

|------------------|------------|-----|-----|-------------|-------------|------------|--------------------------------------|-------|

|                  | Н          | Χ   | Χ   | Χ           | Χ           | DSL        | NOP                                  |       |

|                  | L          | Н   | Н   | Х           | Χ           | NOP/BST    | NOP                                  |       |

|                  | L          | Н   | L   | Н           | BA, CA, A10 | READ/READA | ILLEGAL                              | 3     |

| Idlo             | Idle L H L |     | L   | BA, CA, A10 | WRIT/WRITA  | ILLEGAL    | 3                                    |       |

| iule             | L          | L   | Н   | Н           | BA, RA      | ACT        | Row activating                       |       |

|                  | L          | L   | Н   | L           | BA, A10     | PRE/PREA   | NOP                                  |       |

|                  | L          | L   | L   | Н           | Χ           | AREF/SELF  | Refresh or Self refresh              | 2     |

|                  | L          | L   | L   | L           | Op-Code     | MRS/EMRS   | Mode register accessing              | 2     |

|                  | Н          | Χ   | Χ   | Χ           | Χ           | DSL        | NOP                                  |       |

|                  | L          | Н   | Н   | Х           | Χ           | NOP/BST    | NOP                                  |       |

|                  | L          | Н   | L   | Н           | BA, CA, A10 | READ/READA | Begin read: Determine AP             | 4     |

| Row Active       | L          | Н   | L   | L           | BA, CA, A10 | WRIT/WRITA | Begin write: Determine AP            | 4     |

| now Active       | L          | L   | Н   | Н           | BA, RA      | ACT        | ILLEGAL                              | 3     |

|                  | L          | L   | Н   | L           | BA, A10     | PRE/PREA   | Precharge                            | 5     |

|                  | L          | L   | L   | Н           | Χ           | AREF/SELF  | ILLEGAL                              |       |

|                  | L          | L   | L   | L           | Op-Code     | MRS/EMRS   | ILLEGAL                              |       |

|                  | Н          | Х   | Χ   | Х           | Χ           | DSL        | Continue burst to end                |       |

|                  | L          | Н   | Н   | Н           | Χ           | NOP        | Continue burst to end                |       |

|                  | L          | Н   | Н   | L           | Χ           | BST        | Burst stop                           |       |

|                  | L          | Н   | L   | Н           | BA, CA, A10 | READ/READA | Term burst, new read: Determine AP   | 6     |

| Read             | L          | Н   | Г   | L           | BA, CA, A10 | WRIT/WRITA | ILLEGAL                              |       |

|                  | L          | L   | Η   | Н           | BA, RA      | ACT        | ILLEGAL                              | 3     |

|                  | L          | L   | Н   | L           | BA, A10     | PRE/PREA   | Term burst, precharging              |       |

|                  | L          | L   | L   | Н           | Х           | AREF/SELF  | ILLEGAL                              |       |

|                  | L          | L   | L   | L           | Op-Code     | MRS/EMRS   | ILLEGAL                              |       |

|                  | Н          | Х   | Х   | Х           | Х           | DSL        | Continue burst to end                |       |

|                  | L          | Н   | Н   | Н           | Χ           | NOP        | Continue burst to end                |       |

|                  | L          | Н   | Н   | L           | Χ           | BST        | ILLEGAL                              |       |

|                  | L          | Н   | L   | Н           | BA, CA, A10 | READ/READA | Term burst, start read: Determine AP | 6, 7  |

| Write            | L          | Н   | L   | L           | BA, CA, A10 | WRIT/WRITA | Term burst, start read: Determine AP | 6     |

|                  | L          | L   | Н   | Н           | BA, RA      | ACT        | ILLEGAL                              | 3     |

|                  | L          | L   | Н   | L           | BA, A10     | PRE/PREA   | Term burst, precharging              | 8     |

|                  | L          | L   | L   | Н           | Χ           | AREF/SELF  | ILLEGAL                              |       |

|                  | L          | L   | L   | L           | Op-Code     | MRS/EMRS   | ILLEGAL                              |       |

# W9425G6JB

# massa winbond sassa

Function Truth Table, continued

| CURRENT<br>STATE  | cs | RAS | CAS | WE | ADDRESS                  | COMMAND    | ACTION                      | NOTES |

|-------------------|----|-----|-----|----|--------------------------|------------|-----------------------------|-------|

|                   | Н  | Х   | Χ   | Х  | Х                        | DSL        | Continue burst to end       |       |

|                   | L  | Н   | Н   | Н  | Х                        | NOP        | Continue burst to end       |       |

|                   | L  | Н   | Н   | L  | Х                        | BST        | ILLEGAL                     |       |

| Read with         | L  | Н   | L   | Н  | BA, CA, A10              | READ/READA | ILLEGAL                     |       |

| Auto-             | L  | Н   | L   | L  | BA, CA, A10              | WRIT/WRITA | ILLEGAL                     | 3     |

| precharge         | L  | L   | Н   | Н  | BA, RA                   | ACT        | ILLEGAL                     | 3     |

|                   | L  | L   | Н   | L  | BA, A10                  | PRE/PREA   | ILLEGAL                     |       |

|                   | L  | L   | L   | Н  | Χ                        | AREF/SELF  | ILLEGAL                     |       |

|                   | L  | L   | L   | L  | Op-Code                  | MRS/EMRS   | ILLEGAL                     |       |

|                   | Н  | Х   | Х   | Х  | Χ                        | DSL        | Continue burst to end       |       |

|                   | L  | Н   | Н   | Н  | Χ                        | NOP        | Continue burst to end       |       |

|                   | L  | Н   | Н   | L  | Χ                        | BST        | ILLEGAL                     |       |

| Write with        | L  | Н   | L   | Н  | BA, CA, A10              | READ/READA | ILLEGAL                     |       |

| Auto-             | L  | Н   | L   | L  | BA, CA, A10              | WRIT/WRITA | ILLEGAL                     |       |

| precharge         | L  | L   | Н   | Н  | BA, RA                   | ACT        | ILLEGAL                     | 3     |

|                   | L  | L   | Н   | L  | BA, A10 PRE/PREA ILLEGAL |            | ILLEGAL                     | 3     |

|                   | L  | L   | L   | Н  | Χ                        | AREF/SELF  | ILLEGAL                     |       |

|                   | L  | L   | L   | L  | Op-Code                  | MRS/EMRS   | ILLEGAL                     |       |

|                   | Н  | Х   | Χ   | Х  | Χ                        | DSL        | NOP-> Idle after tRP        |       |

|                   | L  | Н   | Н   | Н  | Χ                        | NOP        | NOP-> Idle after tRP        |       |

|                   | L  | Н   | Н   | L  | Χ                        | BST        | ILLEGAL                     |       |

|                   | L  | Н   | L   | Н  | BA, CA, A10              | READ/READA | ILLEGAL                     | 3     |

| Precharging       | L  | Н   | L   | L  | BA, CA, A10              | WRIT/WRITA | ILLEGAL                     | 3     |

|                   | L  | L   | Н   | Н  | BA, RA                   | ACT        | ILLEGAL                     | 3     |

|                   | L  | L   | Н   | L  | BA, A10                  | PRE/PREA   | Idle after tRP              |       |

|                   | L  | L   | L   | Н  | Χ                        | AREF/SELF  | ILLEGAL                     |       |

|                   | L  | L   | L   | L  | Op-Code                  | MRS/EMRS   | ILLEGAL                     |       |

|                   | Н  | Х   | Χ   | Х  | Χ                        | DSL        | NOP-> Row active after tRCD |       |

|                   | L  | Н   | Н   | Н  | Χ                        | NOP        | NOP-> Row active after tRCD |       |

|                   | L  | Н   | Н   | L  | Х                        | BST        | ILLEGAL                     |       |

|                   | L  | Н   | L   | Н  | BA, CA, A10              | READ/READA | ILLEGAL                     | 3     |

| Row<br>Activating | L  | Н   | L   | L  | BA, CA, A10              | WRIT/WRITA | ILLEGAL                     | 3     |

| Activating        | L  | L   | Н   | Н  | BA, RA                   | ACT        | ILLEGAL                     | 3     |

|                   | L  | L   | Н   | L  | BA, A10                  | PRE/PREA   | ILLEGAL                     | 3     |

|                   | L  | L   | L   | Н  | Х                        | AREF/SELF  | ILLEGAL                     |       |

|                   | L  | L   | L   | L  | Op-Code                  | MRS/EMRS   | ILLEGAL                     |       |

# ses winbond sesses

Function Truth Table, continued

| CURRENT<br>STATE      | cs | RAS | CAS | WE | ADDRESS     | COMMAND                             | ACTION                         | NOTES |

|-----------------------|----|-----|-----|----|-------------|-------------------------------------|--------------------------------|-------|

|                       | Н  | Х   | Χ   | Х  | Х           | DSL                                 | NOP->Row active after twn      |       |

|                       | L  | Н   | Н   | Н  | Х           | NOP                                 | NOP->Row active after twn      |       |

|                       | L  | Н   | Н   | L  | Х           | BST                                 | ILLEGAL                        |       |

| Write                 | L  | Н   | Г   | Н  | BA, CA, A10 | READ/READA                          | ILLEGAL                        | 3     |

| Recovering            | L  | Н   | Г   | Г  | BA, CA, A10 | WRIT/WRITA                          | ILLEGAL                        | 3     |

| necovering            | L  | L   | Н   | Н  | BA, RA      | ACT                                 | ILLEGAL                        | 3     |

|                       | L  | L   | Н   | L  | BA, A10     | PRE/PREA                            | ILLEGAL                        | 3     |

|                       | L  | L   | Г   | Н  | X           | AREF/SELF                           | ILLEGAL                        |       |

|                       | L  | L   | Г   | Г  | Op-Code     | MRS/EMRS                            | ILLEGAL                        |       |

|                       | Н  | Х   | Χ   | Χ  | Х           | DSL                                 | NOP->Enter precharge after twn |       |

|                       | L  | Н   | Н   | Н  | Х           | NOP                                 | NOP->Enter precharge after twn |       |

|                       | L  | Н   | Н   | L  | Х           | BST                                 | ILLEGAL                        |       |

| Write                 | L  | Н   | L   | Н  | BA, CA, A10 | READ/READA                          | ILLEGAL                        | 3     |

| Recovering with Auto- | L  | Н   | Г   | Г  | BA, CA, A10 | WRIT/WRITA                          | ILLEGAL                        | 3     |

| precharge             | L  | L   | Н   | Н  | BA, RA      | ACT                                 | ILLEGAL                        | 3     |

|                       | L  | L   | Ι   | Г  | BA, A10     | PRE/PREA                            | ILLEGAL                        | 3     |

|                       | L  | L   | Г   | Н  | X           | AREF/SELF                           | ILLEGAL                        |       |

|                       | L  | L   | Г   | Г  | Op-Code     | MRS/EMRS                            | ILLEGAL                        |       |

|                       | Н  | Χ   | Χ   | Χ  | X           | DSL                                 | NOP->Idle after tRC            |       |

|                       | L  | Н   | Η   | Н  | X           | NOP                                 | NOP->Idle after tRC            |       |

| Refreshing            | L  | Н   | Н   | L  | X           | BST                                 | ILLEGAL                        |       |

| Reflesting            | L  | Н   | L   | Н  | X           | READ/WRIT                           | ILLEGAL                        |       |

|                       | L  | L   | Η   | Χ  | X           | ACT/PRE/PREA                        | ILLEGAL                        |       |

|                       | L  | L   | L   | Χ  | X           | AREF/SELF/MRS/EMRS                  | ILLEGAL                        |       |

|                       | Н  | Χ   | Χ   | Χ  | X           | DSL                                 | NOP->Row after tmRD            |       |

|                       | L  | Н   | Н   | Н  | Χ           | NOP                                 | NOP->Row after tMRD            |       |

| Mode<br>Register      | L  | Н   | Н   | L  | Х           | BST                                 | ILLEGAL                        |       |

| Accessing             | L  | Н   | L   | Χ  | Х           | READ/WRIT                           | ILLEGAL                        |       |

|                       | L  | L   | Х   | Х  | Х           | ACT/PRE/PREA/ARE<br>F/SELF/MRS/EMRS | ILLEGAL                        |       |

### Notes:

- 1. All entries assume that CKE was active (High level) during the preceding clock cycle and the current clock cycle.

- 2. Illegal if any bank is not idle.

- 3. Illegal to bank in specified states; Function may be legal in the bank indicated by Bank Address (BA), depending on the state of that bank.

- 4. Illegal if tRCD is not satisfied.

- 5. Illegal if tras is not satisfied.

- 6. Must satisfy burst interrupt condition.

- 7. Must avoid bus contention, bus turn around, and/or satisfy write recovery requirements.

- 8. Must mask preceding data which don't satisfy twn

Remark: H = High level, L = Low level, X = High or Low level (Don't care), V = Valid data

# 9.3 Function Truth Table for CKE

| CURRENT                                 | СК  | CKE |    |     | CAS | W.E | ADDRESS | ACTION                              | NOTES |

|-----------------------------------------|-----|-----|----|-----|-----|-----|---------|-------------------------------------|-------|

| STATE                                   | n-1 | n   | CS | RAS | CAS | WE  | ADDRESS | ACTION                              | NOTES |

|                                         | Н   | Χ   | Х  | Х   | Х   | Х   | Х       | INVALID                             |       |

|                                         | L   | Н   | Н  | Х   | Х   | Х   | Х       | Exit Self Refresh->Idle after txsnr |       |

| Calf Dafaaah                            | L   | Н   | L  | Н   | Н   | Х   | Х       | Exit Self Refresh->Idle after txsnr |       |

| Self Refresh                            | L   | Н   | L  | Н   | L   | Х   | Х       | ILLEGAL                             |       |

|                                         | L   | Н   | L  | L   | Х   | Х   | Х       | ILLEGAL                             |       |

|                                         | L   | L   | Х  | Х   | Χ   | Х   | Х       | Maintain Self Refresh               |       |

|                                         | Н   | Χ   | Х  | Χ   | Χ   | Х   | Х       | INVALID                             |       |

| Power Down                              | L   | Н   | Х  | Х   | Х   | Х   | Х       | Exit Power down->Idle after tis     |       |

|                                         | L   | L   | Х  | Х   | Х   | Х   | Х       | Maintain power down mode            |       |

|                                         | Н   | Н   | Х  | Х   | Х   | Х   | Х       | Refer to Function Truth Table       |       |

|                                         | Н   | L   | Н  | Х   | Х   | Х   | Х       | Enter Power down                    | 2     |

|                                         | Н   | L   | L  | Н   | Н   | Х   | Х       | Enter Power down                    | 2     |

| All banks Idle                          | Н   | L   | L  | L   | L   | Н   | Х       | Self Refresh                        | 1     |

|                                         | Н   | L   | L  | Н   | L   | Χ   | Х       | ILLEGAL                             |       |

|                                         | Н   | L   | L  | L   | Х   | Х   | Х       | ILLEGAL                             |       |

|                                         | L   | Χ   | Х  | Χ   | Х   | Х   | Х       | Power down                          |       |

|                                         | Н   | Н   | Х  | Х   | Х   | Х   | Х       | Refer to Function Truth Table       |       |

|                                         | Н   | L   | Н  | Х   | Х   | Х   | Х       | Enter Power down                    | 3     |

|                                         | Н   | L   | L  | Н   | Н   | Х   | Х       | Enter Power down                    | 3     |

| Row Active                              | Н   | L   | L  | L   | L   | Н   | Х       | ILLEGAL                             |       |

|                                         | Н   | L   | L  | Н   | L   | Х   | Х       | ILLEGAL                             |       |

|                                         | Н   | L   | L  | L   | Х   | Х   | Х       | ILLEGAL                             |       |

|                                         | L   | Χ   | Х  | Х   | Х   | Х   | Х       | Power down                          |       |

| Any State<br>Other Than<br>Listed Above | Н   | Н   | Х  | Х   | Х   | Х   | Х       | Refer to Function Truth Table       |       |

#### Notes:

- 1. Self refresh can enter only from the all banks idle state.

- 2. Power Down occurs when all banks are idle; this mode is referred to as precharge power down.

- 3. Power Down occurs when there is a row active in any bank; this mode is referred to as active power down.

Remark: H = High level, L = Low level, X = High or Low level (Don't care), V = Valid data

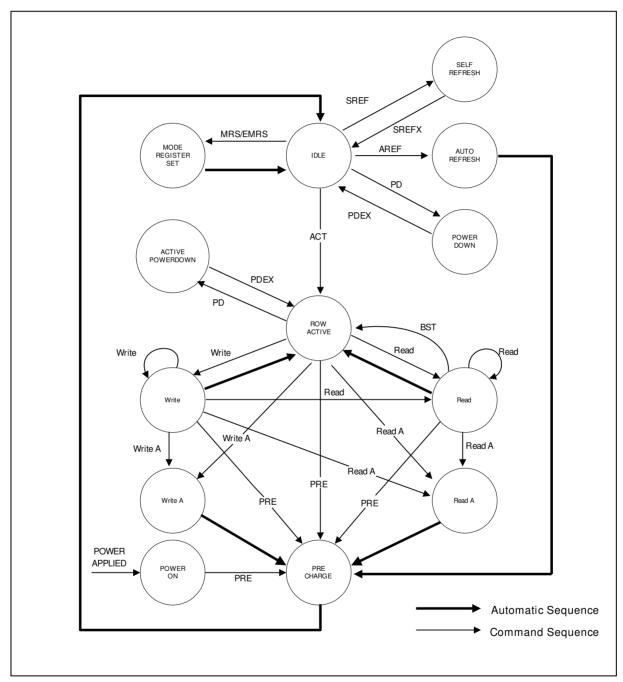

# 9.4 Simplified Stated Diagram

# 10. ELECTRICAL CHARACTERISTICS

# 10.1 Absolute Maximum Ratings

| PARAMETER                              | SYMBOL    | RATING           | UNIT |

|----------------------------------------|-----------|------------------|------|

| Voltage on I/O Pins Relative to Vss    | Vin, Vout | -0.5 ~ VDDQ +0.5 | V    |

| Voltage on Input Pins Relative to VSS  | VIN       | -1 ~ 3.6         | V    |

| Voltage on VDD Supply Relative to VSS  | VDD       | -1 ~ 3.6         | V    |

| Voltage on VDDQ Supply Relative to VSS | VDDQ      | -1 ~ 3.6         | V    |

| Operating Temperature (-5)             | Topr      | 0 ~ 70           | °C   |

| Operating Temperature (-5I)            | Topr      | -40 ~ 85         | °C   |

| Storage Temperature                    | Тsтg      | -55 ~ 150        | °C   |

| Soldering Temperature (10s)            | Tsolder   | 260              | °C   |

| Power Dissipation                      | PD        | 1                | W    |

| Short Circuit Output Current           | lout      | 50               | mA   |

Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# 10.2 Recommended DC Operating Conditions

$(TA = 0 \text{ to } 70^{\circ}\text{C for } -5, TA = -40 \text{ to } 85^{\circ}\text{C for } -5\text{I})$

| SYMBOL    | PARAMETER                                           | MIN.         | TYP.        | MAX.         | UNIT | NOTES  |

|-----------|-----------------------------------------------------|--------------|-------------|--------------|------|--------|

| VDD       | Supply Voltage                                      | 2.3          | 2.5         | 2.7          | V    | 2      |

| VDDQ      | Supply Voltage for I/O Buffer                       | 2.3          | 2.5         | 2.7          | V    | 2      |

| VREF      | Input reference Voltage                             | 0.49 x VDDQ  | 0.50 x VDDQ | 0.51 x VDDQ  | V    | 2, 3   |

| VTT       | Termination Voltage (System)                        | VREF - 0.04  | VREF        | VREF + 0.04  | V    | 2, 8   |

| VIH (DC)  | Input High Voltage (DC)                             | VREF + 0.15  | -           | VDDQ + 0.3   | V    | 2      |

| VIL (DC)  | Input Low Voltage (DC)                              | -0.3         | -           | VREF - 0.15  | V    | 2      |

| VICK (DC) | Differential Clock DC Input Voltage                 | -0.3         | -           | VDDQ + 0.3   | V    | 15     |

| VID (DC)  | Input Differential Voltage. CLK and CLK inputs (DC) | 0.36         | -           | VDDQ + 0.6   | V    | 13, 15 |

| VIH (AC)  | Input High Voltage (AC)                             | VREF + 0.31  | -           | -            | V    | 2      |

| VIL (AC)  | Input Low Voltage (AC)                              | -            | -           | VREF - 0.31  | V    | 2      |

| VID (AC)  | Input Differential Voltage. CLK and CLK inputs (AC) | 0.7          | -           | VDDQ + 0.6   | ٧    | 13, 15 |

| VX (AC)   | Differential AC input Cross Point<br>Voltage        | VDDQ/2 - 0.2 | -           | VDDQ/2 + 0.2 | V    | 12, 15 |

| VISO (AC) | Differential Clock AC Middle Point                  | VDDQ/2 - 0.2 | -           | VDDQ/2 + 0.2 | V    | 14, 15 |

Notes: Undershoot Limit: VIL (min) = -1.5V with a pulse width ≤ 5 nS

Overshoot Limit: VIH (max) = VDDQ +1.5V with a pulse width ≤ 5 nS

VIH (DC) and VIL (DC) are levels to maintain the current logic state.

VIH (AC) and VIL (AC) are levels to change to the new logic state.

# 10.3 Capacitance

$(VDD = VDDQ = 2.5V \pm 0.2V, f = 1~MHz, TA = 25^{\circ}C, VOUT (DC) = VDDQ/2, VOUT (Peak to Peak) = 0.2V)$

| SYMBOL | PARAMETER                               | MIN. | MAX. | DELTA<br>(MAX.) | UNIT |

|--------|-----------------------------------------|------|------|-----------------|------|

| CIN    | Input Capacitance (except for CLK pins) | 1.5  | 2.5  | 0.5             | pF   |

| Cclk   | Input Capacitance (CLK pins)            | 1.5  | 2.5  | 0.25            | pF   |

| CI/O   | DQ, DQS, DM Capacitance                 | 3.5  | 4.5  | 0.5             | pF   |

**Note:** These parameters are periodically sampled and not 100% tested.

# 10.4 Leakage and Output Buffer Characteristics

| SYMBOL               | PARAMETER                                                                                                                      | MIN.      | MAX.      | UNIT | NOTES |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|------|-------|

| lı (L)               | Input Leakage Current Any input $0V \le VIN \le VDD$ , VREF Pin $0V \le VIN \le 1.35V$ (All other pins not under test = $0V$ ) | -2        | 2         | μΑ   |       |

| lo (L)               | Output Leakage Current (Output disabled, 0V ≤ VOUT ≤ VDDQ)                                                                     | -5        | 5         | μΑ   |       |

| Vон                  | Output High Voltage (under AC test load condition)                                                                             | VTT +0.76 | -         | V    |       |

| VoL                  | Output Low Voltage (under AC test load condition)                                                                              | -         | VTT -0.76 | V    |       |

| Іон                  | Output Levels: Full drive option High Current (VOUT = VDDQ - 0.373V, min. VREF, min. VTT                                       | -15       | -         | mA   | 4, 6  |

| loL                  | Low Current (Vout = 0.373V, max. VREF, max. VTT)                                                                               | 15        | -         | mA   | 4, 6  |

| Іонг                 | Output Levels: Reduced drive option - 60% High Current (VOUT = VDDQ - 0.763V, min. VREF, min. VTT                              | -9        | -         | mA   | 5     |