# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# WAU8822 - EVB

## **Evaluation Board User's Guide**

#### nuvoTon

## **Table of Contents**

| System Description:                    |

|----------------------------------------|

| Hardware Description:                  |

| Quick Set-Up:                          |

| Demo Panel:                            |

| Use predefined Saved Configurations: 6 |

| Use predefined Saved Configurations:7  |

| Saved Configurations:7                 |

| Path view Panel:7                      |

| Device Control Panel:                  |

| Input Signal path:                     |

| ADC/Filtering Panel:                   |

| Input Limiter and ALC Panel: 10        |

| Input Limiter and ALC Panel: 11        |

| DAC Filtering/ Digital Audio Panel:12  |

| Output Path Panel:                     |

| Register Map Panel:                    |

| Jumpers and Connectors: 15             |

| Power:                                 |

| Digital Input:                         |

| Note: External clock to J8, TP33: 17   |

| Digital Output:                        |

| ANALOG INPUT                           |

| ANALOG OUTPUT                          |

| USB CONNECTIONS                        |

| Jumpers:                               |

| Test Points:                           |

| Block Diagram:                         |

| Analog-out:                            |

| Level Translator:                      |

| Analog inputs:                         |

| SPDIF Interface:                       |

| Codec Power:                           |

## Kit Contents:

The WAU8822-EVB Board Application Software CD (WAU8822-EVP) User's Guide (included in the supplied CD) USB Cable Data sheet

## **System Description:**

The WAU8822-EVB system consists of an evaluation board with audio inputs and audio outputs and application software that sends command and control via USB. Power is normally provided by USB.

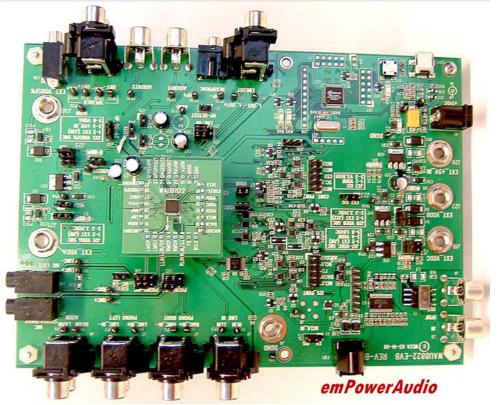

## Hardware Description:

The Evaluation board is controlled via USB cable. The on board Nuvoton W681308 USB Audio controller acts as an SPI /I2C & I2S interface between the PC Software GUI and the WAU8822 audio codec.

## WAU8822 Application Software:

The WAU8822 Application software is powerful and easy to use GUI software which enables the users to control the Nuvoton WAU8822 Stereo Codec and aids system designers to develop software for their system's microcontroller by importing the register map's saved file after they are satisfied with their desired configurations. They are 3 ways to configure and control the W8822/12 Audio Codec family with the WAU8822-Application Software:

- Demo Panel

- Use predefined Saved Configurations

- Click and configure

#### Quick Set-Up:

- 1) Install the software from the CD, follow the on screen directions

- 2) Print out the user's guide from the CD

- 3) Make sure PCB is not connected to PC

- 4) Start the program

- 5) From the Start up screen below select WAU8822 to go to Stereo GUI

- 6) Connect the WAU8822-EVB board to the USB port

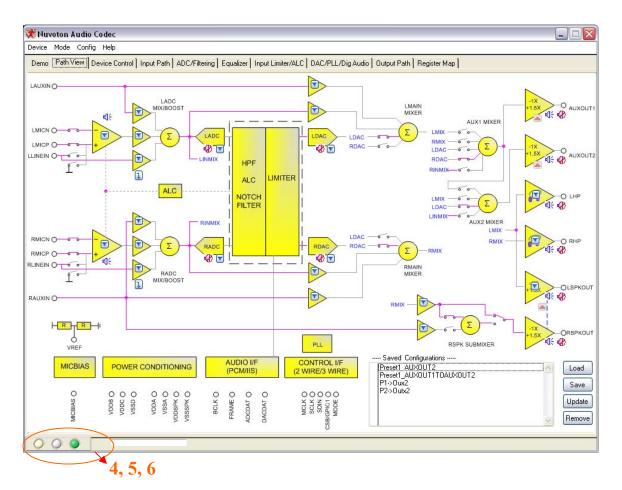

The first screen you will see is a graphical representation of all relevant blocks of the WAU8822 Audio Code called path view. Each block has its own screen panel witch represents associated control registers for that block. When the board is attached to the GUI via the USB cable the Green LED is lit (4)

#### nuvoton

#### Status indicators.

In the left hand corner of the GUI there three indicators.

- 4) This indicator turns green when the WAU8822-EVB is attached to the USB cable.

- 5) This indictors turns solid green when the software loads setting.

6) This indictor blinks and stays green after the software has finished writing to the WAU8822 registers.

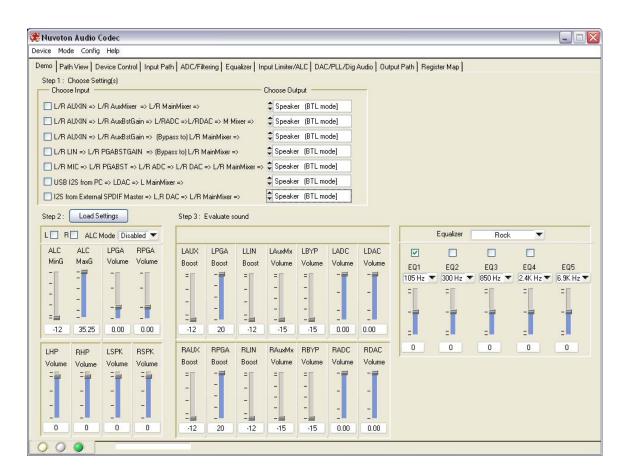

#### Demo Panel:

In the demo panel there are 2 easy steps for setting up and evaluating a full working path

- Step 1. Choose Settings (selecting input such as MIC AUX or Line in Output such as HP, SPKR or Line-out)

- Step 2: Load settings (The GUI writes to each individual control register).

Once the desired path is set, you can evaluate the equalizer or ALC effects here as well.

## Use predefined Saved Configurations:

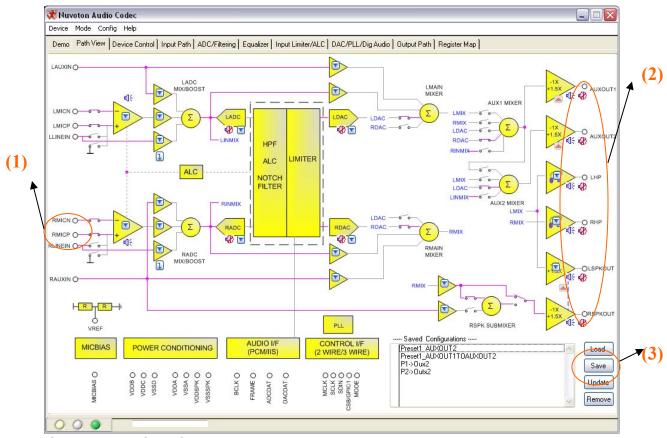

#### Saved Configurations:

In path view panel there are some examples of saved configuration. Double clicking on a saved configuration from the menu will activate that path. Selecting a saved configuration and update also activates that path. The software will automatically write to each control register immediately. This feature can be used to tune different parameters and compare them later

### Click and Configure:

#### Path view Panel:

The WAU8822 is configured through 64 registers. Each individual bit controls a function such as mute or unmute of input/output mixers and amplifiers.

In this panel you can set your desired input output path by clicking on the connecting lines or Icons (1), (2). Notice each time a line is selected the active line is highlighted. The associated registers are written immediately so you can see and hear the immediate effect. Later you can save the path by clicking on add icon (3) for comparison with a different sets of parameters. To quickly get back to your original settings select Load.

The big blocks such as ALC, DAC, and EQ have more than one control bit. Clicking on specific block will take the users to its associated panel where you can set individual control bits for that block. Right click on that panel will take you back to the path view panel.

#### **Device Control Panel:**

#### SELECTION OF CONTROL MODE

In this panel the user's selects device interfaces for WAU8822 from one of the following options:

- 3 Wire write only

- 4 Wire read and write

- I2C read and write

- External Control

The I2S signal connection section boxes configures the W8822-EVB to operate in I2S Master or Slave Mode. In the Master mode the MCLK is generated from:

- On board USB controller ( select this option for playing Mono Audio from USB)

- Audio precision equipment

- Digital Audio (I2S) (Sect this is option for the SPDIF optical audio interface)

| Y Wire SPI Mode Write Only (4 Wire SPI when reading)         4 Wire SPI Mode Read/Write         12C Mode Read/Write         12C Mode Read/Write         12C Signal Connection         Digital Audio Reset         12S Master         Ø On-Board USB (12S) Mode [Feed MCLK to device]         Audio Precision (12S) Master Mode Interface Enable         Digital Audio (12S) Master Mode Interface Enable         12S Slave         Audio Precision (12S) Slave Mode Interface Enable         Digital Audio (12S) Slave Mode Interface Enable | VDDSPK = 5V (Output Boost = 1.5x) VDDSPK = 3.3V (Output Boost = -1.0)  Device Control Power Up Reset Device Power Down Mute All Outputs Load Default Update Bits Enable All Outputs Disable All Outputs |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

Once a device interface is selected, click on the Config Board button to configure the communication to the W8822-EVB board before powering up the WAU8822.

The Reset, Power up, and Power down buttons control the WAU8822. The default for 1.5X boost stage is un-checked. *Please make sure to Change J35 on the WAU8822-EVM boards to 5V or VDDA (3.5) when you change this bit*.

#### nuvoTon

#### Input Signal path:

| Power Management<br>[LPGAEN] Left Channel PGA Enable<br>[RPGAEN] Right Channel PGA Enable | Power Management                                                                                                                                                        | Power Management<br>[LBSTEN] LADC Mix/Boost stage Enable<br>[RBSTEN] R ADC Mix/Boost stage Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Control                                                                             | MicroPhone Bias Voltage Control [MICBIASM] MIC BIAS Mode  MICBIASV] Mic. Bias V  Normal Mode: 0.9 * VDDA ** MIC BIAS output pin is currently disabled: MICBIASEN = 0 ** | Left ADC Boost  [ILPGABST] L PGA Boost (+20dB over 0dB) [LAUXBSTGAIN] LAUXIN Gain  Path Disable [LPGABSTGAIN] LLIN Gain  Path Disable  Right ADC Boost [IIRGABST] R PGA Boost (+20dB over 0dB) [RAUXBSTGAIN] RAUXIN Gain  Path Disable [RPGABSTGAIN] RLIN Gain  Path Disable |

|                                                                                           | ALC Control [ALCEN] ALC Select ALC Off " When ALC is enabled, PGA volumes are controlled automatically, and L,RPGAGAIN bits should not be used. **                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

The ADC control registers and notch filter are selected in this panel. In the digital ADC volume control section a pop up ring select window selects various gains. The selected values are written to its registers automatically.

#### **ADC/Filtering Panel:**

The ADC control registers and notch filter is selected in this panel. In Digital ADC volume control section a pop up ring select window selects various gains. The selected values are written to its registers automatically.

#### Input Limiter and ALC Panel:

In this panel aside from configuring the ALC stage to operate in normal or limiter modes, there is an ALC slider bar that sets the ALC control registers with pre defined parameters for Music, Speech and generic recording. These are suggested optimal values based on experiments and it's only a guide for further optimization for the end portable application.

| 🗱 Nuvoton Audio Codec                                                                                                         |  |

|-------------------------------------------------------------------------------------------------------------------------------|--|

| Device Mode Config Help                                                                                                       |  |

| Demo Path View Device Control Input Path ADC/Filtering Equalizer Input Limiter/ALC DAC/PLL/Dig Audio Output Path Register Map |  |

| [ALCEN] ALC Both Dn                                                                                                           |  |

| [ALCMINGAIN] ALC Minimum Gain Q-12dB [ALCNTH] ALC Noise gate threshold: Q-81dB                                                |  |

| [ALCMXGAIN] ALC Maximum Gain +35.25dB                                                                                         |  |

| ALC Control 2 [ALCSL] ALC target level at ADC output  12dBFS ALC                                                              |  |

| [ALCHT] Hold time before ALC gain 2 0 ms Music-                                                                               |  |

| ALC Control 3                                                                                                                 |  |

| [ALCDCY]ALC Decay   Bms/step [ALCATK]ALC Attack   500us/step                                                                  |  |

| Generic-                                                                                                                      |  |

| ALCM = Limiter Mode                                                                                                           |  |

| [ALCATK] ALC Attack 🗒 124us/step                                                                                              |  |

|                                                                                                                               |  |

|                                                                                                                               |  |

|                                                                                                                               |  |

#### nuvoTon

#### **DAC Filtering/ Digital Audio Panel:**

This Panel is divided into three sections;

- PLL

- DAC

- Digital Audio Control

In each section control bits can be enabled or disabled. The associated registers are written automatically.

In the PLL sections the default is open circuit or disabled. There are two PLL settings (Default 12.2886 MHz) or custom setting, where valid supported frequencies are calculated given the PLL parameters. Other section in this panel enables or disables clock generation from external source, companding control, jack detect. The audio interface box also selects individual bits such as FMT and Word length.

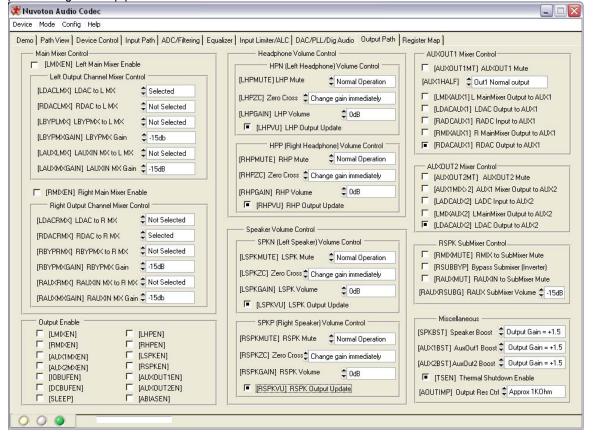

#### **Output Path Panel:**

In this panel all output control bits are written in real time, any selection's effect can be seen in the path view panel or register map panel.

#### **Register Map Panel:**

In the Register map view all control address are in hex. To write to a particular register enter the register address followed by the registers new value and click write.Or you can directly enter binary number for each individual bit. To Read a register , enter a register address and click read, the value will be displayed in the register value box. You can also Read all and Update to see all register.

| emo   Path View   Devi                   | ce Control | Input Path |       | iltering   E |          |       |       |       | 'Dig Audio | ) Output F | Path Reg | ister Map |   |                              |

|------------------------------------------|------------|------------|-------|--------------|----------|-------|-------|-------|------------|------------|----------|-----------|---|------------------------------|

| <u>.</u>                                 | Hou Addr   | Dec Addr   | Bit 8 | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1      | Bit O    | Hex Val   |   | Audio Codec Register Control |

| Software Reset                           | 00         | Dec Addi   | 0     | 0            | 0        | 0     | 0     | 0     | 0          | 0          | 0        | 000       |   | Address x00 Read             |

| Power_Management_1                       | 01         | 1          | 0     | 0            | 0        | 0     | 0     | 0     | 0          | 0          | 0        | 000       |   |                              |

| Power_Management_1                       | 02         | 2          | 0     | 0            | 0        | 0     | 0     | 0     | 0          | 0          | 0        | 000       |   | Value x000 Write             |

| Power_Management_2<br>Power Management_3 | 02         | 3          | 0     | 0            | 0        | 0     | 0     | 0     | 0          | 0          | 0        | 000       |   |                              |

| Audio_Interface                          | 04         | 4          | 0     | 0            | 1        | 0     | 1     | 0     | 0          | 0          | 0        | 050       |   | Read All and Update          |

| Companding                               | 05         | 5          | 0     | 0            | 0        | 0     | 0     | 0     | 0          | 0          | 0        | 000       |   |                              |

| Clock Control 1                          | 06         | 6          | 1     | 0            | 1        | 0     | 0     | 0     | 0          | 0          | 0        | 140       |   |                              |

| Clock Control 2                          | 07         | 7          | 0     | 0            | 0        | 0     | 0     | 0     | 0          | 0          | 0        | 000       |   |                              |

| GPI0                                     | 08         | 8          | 0     | 0            | 0        | 0     | 0     | 0     | 0          | 0          | 0        | 000       |   |                              |

| Jack Detect 1                            | 09         | 9          | 0     | 0            | 0        | 0     | 0     | 0     | 0          | 0          | 0        | 000       |   |                              |

| DAC Control                              | 0A         | 10         | 0     | 0            | 0        | 0     | 0     | 0     | 0          | 0          | 0        | 000       | 1 |                              |

| Left DAC Volume                          | OB         | 11         | 0     | 1            | 1        | 1     | 1     | 1     | 1          | 1          | 1        | OFF       |   |                              |

| Right DAC Volume                         | 0C         | 12         | 0     | 1            | 1        | 1     | 1     | 1     | 1          | 1          | 1        | OFF       |   |                              |

| Jack_Detect_2                            | 0D         | 13         | 0     | 0            | 0        | 0     | 0     | 0     | 0          | 0          | 0        | 000       |   |                              |

| ADC_Control                              | 0E         | 14         | 1     | 0            | 0        | 0     | 0     | 0     | 0          | 0          | 0        | 100       | 1 |                              |

| Left_ADC_Volume                          | OF         | 15         | 0     | 1            | 1        | 1     | 1     | 1     | 1          | 1          | 1        | OFF       |   |                              |

| Right_ADC_Volume                         | 10         | 16         | 0     | 1            | 1        | 1     | 1     | 1     | 1          | 1          | 1        | OFF       |   |                              |

| EQ1-low_self                             | 12         | 18         | 1     | 0            | 0        | 1     | 0     | 1     | 1          | 0          | 0        | 12C       |   |                              |

| EQ2-peak_1                               | 13         | 19         | 0     | 0            | 0        | 1     | 0     | 1     | 1          | 0          | 0        | 02C       |   |                              |

| EQ3-peak_2                               | 14         | 20         | 0     | 0            | 0        | 1     | 0     | 1     | 1          | 0          | 0        | 02C       |   |                              |

| EQ4-peak_3                               | 15         | 21         | 0     | 0            | 0        | 1     | 0     | 1     | 1          | 0          | 0        | 02C       |   |                              |

| EQ5-high-self                            | 16         | 22         | 0     | 0            | 0        | 1     | 0     | 1     | 19         | 0          | 0        | 02C       |   |                              |

| DAC_Limiter_1                            | 18         | 24         | 0     | 0            | 0        | 1     | 1     | 0     | 0          | 1          | 0        | 032       |   |                              |

| DAC Limiter 2                            | 19         | 25         | n     | n            | <u>n</u> | n     | n     | n     | n          | n          | 0        | 000       | ~ |                              |

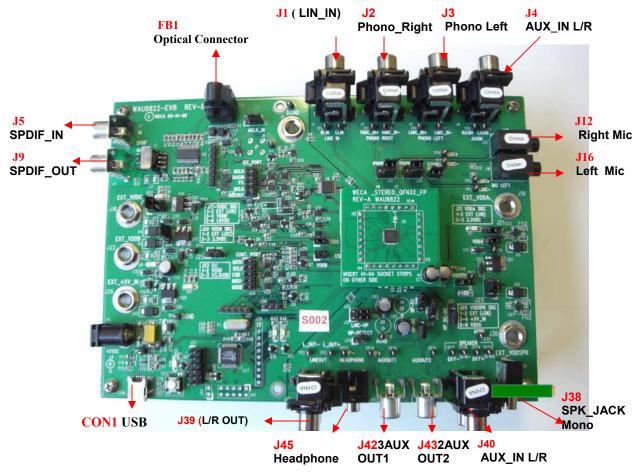

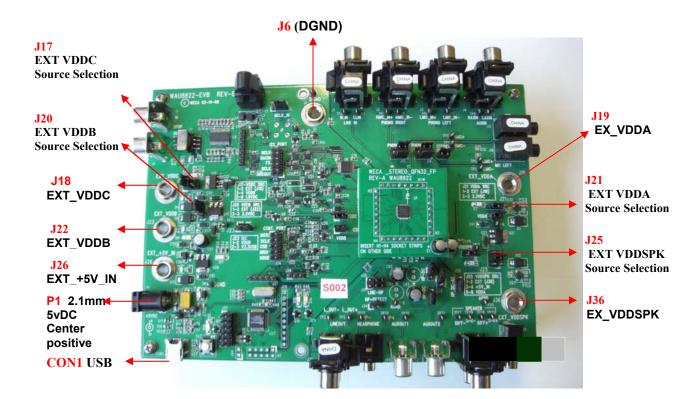

## Jumpers and Connectors:

#### Power:

Power is supplied to the WAU8822-EVB USB interface via the USB connector. If preferred it is also possible to supply +5V power to the level shifters using external supplies connected via Banana jacks.

- Using a USB cable +5V can be provided by the PC at CON1.

- If needed, a stronger 5V supply can be added using the 2.1mm jack at P1.

- Using Banana jacks the various supplies of the CODEC can also be supplied externally; connections are described below: Please make a note to change jumper J17, J20, J21 and J25 source from factory default (powered by USB) to EXT(position 1-2) as needed. See page 21 for detailed descriptions of jumpers.

| REFERENCE<br>DESIGNATOR | SOCKET NAME | SUPPLY       |

|-------------------------|-------------|--------------|

| J6                      | DGND        | 0V           |

| J18                     | EXT_VDDC    | 1.6V to 3.6V |

| J19                     | EX_VDDA     | 2.5V to 3.6V |

| J22                     | EXT_VDDB    | 1.8V to 3.6V |

| J26                     | EXT_+5V_IN  | +5           |

| J36                     | EX_VDDSPK   | 2.5V to 5.0V |

#### Selecting 3.3/5V operation jumper settings:

The default setting for WAU8822-EVB VDDSPK is 5V. To select 3.3V operation set J25 (VDDSPK source) to position (5-6) and J21 to Position (2-3).

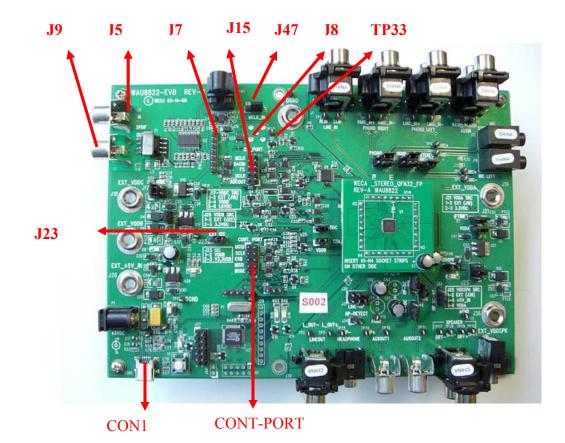

#### **Digital Input:**

There are three methods to input the required digital signal clocks to the WAU8822 audio interface.

- An AES/EBU, UEC958, S/PDIF, EIAJ CP340/1201 signal from coaxial input can be provided via a standard phono jack (J5),

- Direct digital data can be input via a 1x7 pin header (J7)

- Digital Audio Interface is available via one side of a 2x10 pin header (J15). This supports an Audio Precision interface.

Level shifters have been included in the digital input interface path to provide signal buffering to the input signals; this allows an external clock source to be matched to the WAU8822 requirements.

The WAU8822 requires an MCLK input to produce an ADCOUT output, which can be derived either from S/PDIF signal clock recovery or by connecting an external MCLK direct to J8, TP33 or H2. The BCLK and FS clocks can also be derived from the S/PDIF signal clock recovery or by discrete input to header J7. When EVB board is attached to USB the MCLK is generated from on board 12Mhz crystal by the USB controller.

| Reference<br>Designator | Connector Style                             | Signal Name             |

|-------------------------|---------------------------------------------|-------------------------|

| J5                      | Phono Connector                             | SPDIF_IN                |

| J7                      | Header                                      | MCLK_IN                 |

| J7 pin2                 | Header                                      | SPDIF_ADCDAT_IN         |

| J7 pin3                 | Header                                      | SPDIF_FRAME_IN          |

| J7 pin4                 | Header                                      | SPDIF_BCLK_IN           |

| J8                      | SMB Connector ( not populated on the board) | MCLK                    |

| J15 pin 1               | Header                                      | ADCOUT_AP               |

| J15 pin 3               | Header                                      | BCLK_AP                 |

| J15 pin 5               | Header                                      | FS_AP                   |

| J15 pin 7               | Header                                      | DACIN_AP                |

| J15 pin 9               | Header                                      | MCLK_AP                 |

| J47                     | Header                                      | Ext MCLK enable/disable |

#### **Digital Input Connections**

Note: External clock to J8, TP33:

To use the WAU8822 as master you still need to apply an external clock to J8, TP33. Please disable any clock source from the board (Set J47 to position EN and in application software, please select Slave I2S mode in device selection panel see page 15)

#### **Digital Output:**

The ADC output can be obtained in the following ways:

- Converted to an S/PDIF signal via the CS8427CS device (U2) and output from the WAU8822-EVB evaluation board via a standard Phono connector (J9).

- The ADC output data and clocks may be accessed via a 1x7 pin header (J7).

- Digital Audio Interface is available via one side of a 2x10 pin header (J15)

Level shifters have been included in the digital input interface path to provide signal buffering to the output signals; this allows external receiver requirements to be met.

| Reference<br>Designator | Connector Style | Signal Name     |  |  |  |

|-------------------------|-----------------|-----------------|--|--|--|

| J7 pin2                 | Header          | SPDIF_ADCDAT_IN |  |  |  |

| J7 pin3                 | Header          | SPDIF_FRAME_IN  |  |  |  |

| J7 pin4                 | Header          | SPDIF_BCLK_IN   |  |  |  |

| J8                      | SMB Connector   | MCLK            |  |  |  |

| J9                      | Phono Connector | SPDIF_OUT       |  |  |  |

| J15 pin 1               | Header          | ADCOUT_AP       |  |  |  |

| J15 pin 3               | Header          | BCLK_AP         |  |  |  |

| J15 pin 5               | Header          | FS_AP           |  |  |  |

| J15 pin 7               | Header          | DACIN_AP        |  |  |  |

| J15 pin 9               | Header          | MCLK_AP         |  |  |  |

#### **USB and External Control CONNECTIONS**

The 2-wire, 3-wire or 4 wire control signals can be input from the control software via USB connector (CON1); these signals are interpreted by the Nuvoton W861308 USB Controller (U27). Alternatively it is possible to connect control signals directly via J24.

| Reference<br>Designator | Connector<br>Style | Pin Number | Signal Name |

|-------------------------|--------------------|------------|-------------|

| CON1                    | miniUSB<br>Type B  | 1          | VCC         |

|                         |                    | 2          | USBD-       |

|                         |                    | 3          | USBD+       |

|                         |                    | 4          | NC          |

|                         |                    | 5          | GND         |

|                         |                    | 6          | SHIELD      |

|                         |                    | 7          | SHIELD      |

|                         |                    | 8          | SHIELD      |

|                         |                    | 9          | SHIELD      |

| Connector   | Name      | Description                                                                               |

|-------------|-----------|-------------------------------------------------------------------------------------------|

| J15         | JTAG_ICE  | JTAG ICE connector                                                                        |

| J15         | I2S_PORT  | Direct interface Port for IS2 (digital audio)                                             |

| J23         | EXT-I2C   | I2C Voltage source selection. Position (1-2) VDDB<br>and position (3-4) selects V3.3V USB |

| J24         | CONT_PORT | External Signal Interface (SPI)                                                           |

| J29,J37,J41 | J29       | For Nuvoton use to program the W681308 USB controller                                     |

Note that J15 and J24 can be used together to connect the Nuvoton WAU8822 Audio CODEC to any external controller.

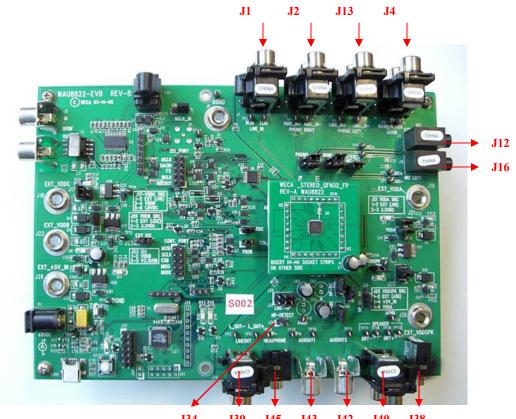

#### **ANALOG INPUT**

The main analog inputs can be configured in one of two ways, either input via 4 phono connectors or via two jack sockets; both of which can be used with a pair of pseudo-differential input signals. Additional auxiliary inputs and line inputs can be input via two pairs of phono connectors. Jumpers J13 and J14 select between the jack socket or phono connector for each input.

J34 J39 J45 J43 J42 J40 J38

| Reference<br>Designator | Connector Style | Signal Name                                                          |  |

|-------------------------|-----------------|----------------------------------------------------------------------|--|

| J1                      | Phono Connector | LIN_IN                                                               |  |

| J2                      | Phono Connector | Phono_Right                                                          |  |

| J3                      | Phono Connector | Phono_Left<br>(Input for WAU8812, and WAU8814)                       |  |

| J4                      | Phono Connector | AUX_IN L/R<br>(Left jack is used for WAU8812, and WAU8814 AUX input) |  |

| J12                     | Jack Socket     | Right Mic Input                                                      |  |

| J16                     | Jack Socket     | Left Mic Input<br>(Input for WAU8812, and WAU8814)                   |  |

#### ANALOG OUTPUT

The analog outputs can be configured in one of two ways, either input via 4 phono connectors or via two jack sockets; both of which can be used with a pair of pseudo-differential input signals.

| Reference<br>Designator | Connector Style | Signal Name                                         |

|-------------------------|-----------------|-----------------------------------------------------|

| J34                     | Header          | HP-Detect                                           |

| J45                     | Jack Socket     | Headphone<br>(Output for WAU8812, and WAU8814)      |

| J39                     | Phono Connector | L/R OUT                                             |

| J42                     | Phono Connector | AUXOUT1                                             |

| J43                     | Phono Connector | AUXOUT2                                             |

| J40                     | Phono Connector | AUX_IN L/R                                          |

| J38                     | Jack            | SPK_JACK (Mono)<br>(Input for WAU8812, and WAU8814) |

All WAU8822 pins are easily accessible via the headers running along each side of the device.

NOTE: It is possible to run a Mono Audio CODEC (e.g. WAU8812) on the WAU8822 platform by using an appropriate daughter card. In this case the left stereo inputs are connected to the Mono device.

#### nuvoTon

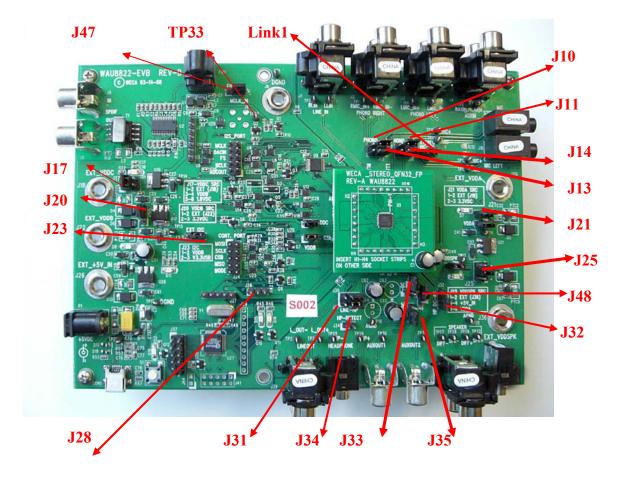

## Jumpers:

| Jumpers | Default Position | Description                                                                                              |

|---------|------------------|----------------------------------------------------------------------------------------------------------|

| J10     | 1-2 (short)      | Position 1-2 selects Right MIC and<br>Position 2-3 selects Right Phono                                   |

| J11     | 1-2 (short)      | Position 1-2 selects Left MIC and<br>Position 2-3 selects Left Phono<br>(Input for WAU8812, and WAU8814) |

| J13     | 1-2 (short)      | Position 1-2 selects Right MIC and<br>Position 2-3 selects Right Phono                                   |

| J14     | 1-2 (short)      | Position 1-2 selects Left MIC and<br>Position 2-3 selects Left Phono<br>(Input for WAU8812, and WAU8814) |

| Jumpers | Default Position | Description                                                                                                                                          |  |

|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| J17     | 3-4(short)       | The 3 position jumper selects the VDDC source. Position 1-2 Sects<br>External VDD via J18, 3-4 Selects VDDB, and position 5-6 sects 1.8VDC           |  |

| J20     | 2-3(short)       | J20 Selects the VDDB source, position 1-2 selects external source via J22 position 2-3 selects 3.3VDC                                                |  |

| J21     | 2-3(short)       | J21 Selects the VDDA source, position 1-2 selects external source via J19 position 2-3 selects 3.3VDC                                                |  |

| J23     | 2-3(short)       | Install for external I2C at VDDB or I2C at 3.3V operation.                                                                                           |  |

| J25     | 3-4 (short)      | Speaker VDD selection jumper. Position 1-2 selects external source via (J36), position 3-4 selects 5VDc and position 5-6 selects analog power (VDDA) |  |

| J28     | 2-3(short)       | For Internal use with the W681308 USB controller                                                                                                     |  |

| J30     | 2-3(short)       | Position 1-2 Left Line_Out select and Position 2-3 selects Left HPOut (<br>Left headphone out)                                                       |  |

| J31     | 2-3(short)       | Position 1-2 Right Line_Out select and Position 2-3 selects right HP+_Out (Right headphone out)                                                      |  |

| J32     | 1-2 (short)      | Position 1-2 selects Headphone cap-less mode and<br>Position 2-3 selects AC coupled headphone output                                                 |  |

| J33     | (Open)           | Open position selects Headphone cap-less mode and<br>Closed Position selects DC coupled headphone output (HP-)<br>(Output for WAU8812, and WAU8814)  |  |

| J34     | 1-2 (short)      | Headphone detect                                                                                                                                     |  |

| J35     | (Open)           | Open position selects Headphone cap-less mode and<br>Closed Position selects DC coupled headphone output (HP+)                                       |  |

| J47     | 2-3(short)       | Install this jumper for external MCLK Position 1-2 enables external MCLK and poison 2-3 disables the external MCLK.                                  |  |

| J48     |                  | Aux1 connection header                                                                                                                               |  |

| Link1   | Closed           | Stereo MIC select                                                                                                                                    |  |

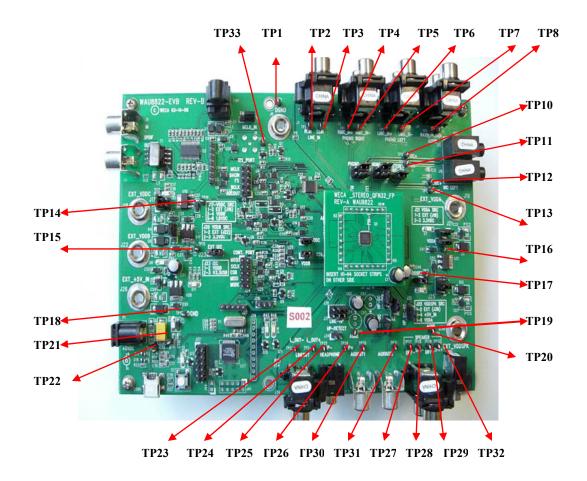

#### **Test Points:**

| Reference<br>Designator | Description                      | Signal Name |

|-------------------------|----------------------------------|-------------|

| TP1                     | Digital Ground                   | DGND        |

| TP2                     | Right Line_In                    | R_LIN       |

| TP3                     | Left Line_In                     | L_LIN       |

| TP4                     | Right Phono-In<br>positive       | RMIC_IN+    |

| TP5                     | Right Phono-In<br>Negative       | RMIC_IN-    |

| TP6                     | Left Phono-In<br>positive        | LMIC_IN+    |

| TP7                     | Left Phono-In<br>Negative        | LMIC_IN-    |

| TP8                     | Right Aux_IN                     | RAUXIN      |

| TP9                     | Left Aux_IN                      | LAUXIN      |

| TP10                    | Right Mic-In Positive            | RMIC+       |

| TP11                    | Right MIC-In<br>Negative         | RMIC-       |

| TP12                    | Left MIC-In positive             | LMIC+       |

| TP13                    | Left MIC-In Negative             | LMIC-       |

| TP14                    | VDDC Source (J17)                | J17-VDD-SRC |

| TP15                    | VDDB Source (J23)                | J23 I2C     |

| TP16                    | Analog Voltage test<br>point     | VDDA        |

| TP17                    | Speaker VDD                      | VDDSPK      |

| TP18                    | Digital Ground                   | DGND        |

| TP19                    | Analog Ground                    | AGND        |

| TP20                    | Analog Ground                    | AGND        |

| TP23                    | LINE OUT                         | L_OUT-      |

| TP24                    | LINE OUT                         | L_OUT+      |

| TP25                    | Headphone                        | HP-         |

| TP26                    | Headphone                        | HP+         |

| TP27                    | Differential Speaker<br>Negative | DIFF-       |

| TP28                    | I Speaker Negative               | SPK-        |

| TP29                    | Differential Speaker<br>Positive | DIFF+       |

| TP332                   | Speaker positive                 | SPK+        |

| TP31                    | AUXOU2                           | AUXOUT1     |

| TP30                    | AUXOUT1                          | AUXOU2      |

| TP33                    | External clock Input             | MCLK_IN     |

#### nuvoTon