Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

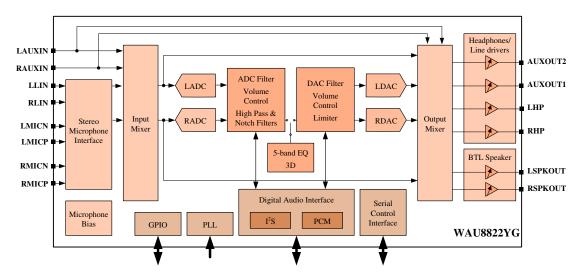

#### **WAU8822**

## 24-bit Stereo Audio Codec with Speaker Driver emPowerAudio™

#### **Description**

The WAU8822 is a low power, high quality CODEC for portable applications. In addition to precision 24-bit stereo ADCs and DACs, this device integrates a broad range of additional functions to simplify implementation of complete audio system solutions. The WAU8822 includes drivers for speaker, headphone, and differential or stereo line outputs, and integrates preamps for stereo differential microphones, significantly reducing external components.

Advanced on-chip digital signal processing includes a 5-band equalizer, a 3-D audio enhancer, a mixed-signal automatic level control for the microphone or line input through the ADC, and a digital limiter function for the playback path. Additional digital filtering options are available in the ADC path, to simplify implementation of specific application requirements such as 'wind noise reduction'. The digital interface can operate as either a master or a slave. Additionally, an internal fractional PLL is available to generate accurate audio sample rate clocks for the CODEC derived from a wide range of commonly available system clock frequencies such as 12MHz and 13MHz.

The WAU8822 operates with analog supply voltages from 2.5V to 3.6V, while the digital core can operate at 1.65V to conserve power. The loudspeaker BTL output pair and two auxiliary line outputs can operate using a 5V supply to increase output power capability, enabling the WAU8822 to drive 1 Watt into an external speaker. Internal register controls enable flexible power saving modes by powering down sub-sections of the chip under software control.

The WAU8822 is specified for operation from -40°C to +85°C, and is available with full automotive AEC-/Q100 & TS16949 qualification. It is packaged in a cost-effective, space-saving 32-lead QFN package.

#### **Key Features**

- DAC: 94dB SNR and -84dB THD ("A" weighted)

- ADC: 90dB SNR and -80dB THD ("A" weighted)

- Integrated BTL speaker driver: 1W into 8Ω

- Integrated head-phone driver: 40mW into 16Ω

- Integrated programmable microphone amplifier

- Integrated line input and line output

- On-chip PLL

- Integrated DSP with specific functions:

- 5-band equalizer

- 3-D audio enhancement

- Automatic level control

- Audio level limiter

- Multiple filtering options

- Standard audio interfaces: PCM and I<sup>2</sup>S

- Serial control interfaces with read/write capability

- Supports audio sample rates from 8kHz to 48kHz

#### **Applications**

- Personal Media Players

- Smartphones

- Personal Navigation Devices

- Portable Game Players

- Camcorders

- Digital Still Cameras

- Portable TVs

- Stereo Bluetooth Headsets

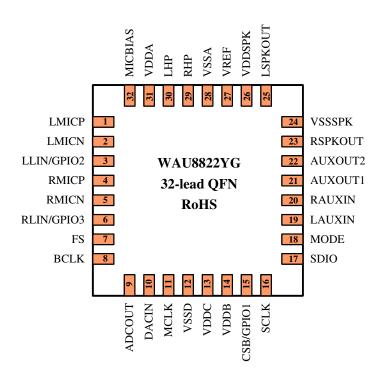

## **Pinout**

| Part Number | Dimension | Package | Package<br>Material |

|-------------|-----------|---------|---------------------|

| WAU8822YG   | 5 x 5 mm  | 32-QFN  | Pb-Free             |

# **Pin Descriptions**

| Pin# | Name       | Туре           | Functionality                                                                               |

|------|------------|----------------|---------------------------------------------------------------------------------------------|

| 1    | LMICP      | Analog Input   | Left MICP Input (common mode)                                                               |

| 2    | LMICN      | Analog Input   | Left MICN Input                                                                             |

| 3    | LLIN/GPIO2 | Analog Input / | Left Line Input / alternate Left MICP Input / GPIO2                                         |

|      |            | Digital I/O    |                                                                                             |

| 4    | RMICP      | Analog Input   | Right MICP Input (common mode)                                                              |

| 5    | RMICN      | Analog Input   | Right MICN Input                                                                            |

| 6    | RLIN/GPIO3 | Analog Input / | Right Line Input/ alternate Right MICP Input / Digital Output                               |

|      |            | Digital I/O    | In 4-wire mode: Must be used for GPIO3                                                      |

| 7    | FS         | Digital I/O    | Digital Audio DAC and ADC Frame Sync                                                        |

| 8    | BCLK       | Digital I/O    | Digital Audio Bit Clock                                                                     |

| 9    | ADCOUT     | Digital Output | Digital Audio ADC Data Output                                                               |

| 10   | DACIN      | Digital Input  | Digital Audio DAC Data Input                                                                |

| 11   | MCLK       | Digital Input  | Master Clock Input                                                                          |

| 12   | VSSD       | Supply         | Digital Ground                                                                              |

| 13   | VDDC       | Supply         | Digital Core Supply                                                                         |

| 14   | VDDB       | Supply         | Digital Buffer (Input/Output) Supply                                                        |

| 15   | CSB/GPIO1  | Digital I/O    | 3-Wire MPU Chip Select or GPIO1 multifunction input/output                                  |

| 16   | SCLK       | Digital Input  | 3-Wire MPU Clock Input / 2-Wire MPU Clock Input                                             |

| 17   | SDIO       | Digital I/O    | 3-Wire MPU Data Input / 2-Wire MPU Data I/O                                                 |

| 18   | MODE       | Digital Input  | Control Interface Mode Selection Pin                                                        |

| 19   | LAUXIN     | Analog Input   | Left Auxiliary Input                                                                        |

| 20   | RAUXIN     | Analog Input   | Right Auxiliary Input                                                                       |

| 21   | AUXOUT1    | Analog Output  | Headphone Ground / Mono Mixed Output / Line Output                                          |

| 22   | AUXOUT2    | Analog Output  | Headphone Ground / Line Output                                                              |

| 23   | RSPKOUT    | Analog Output  | BTL Speaker Positive Output or Right high current output                                    |

| 24   | VSSSPK     | Supply         | Speaker Ground (ground pin for RSPKOUT, LSPKOUT,                                            |

| 25   | LSPKOUT    | Amala a Outmut | AUXOUT2 and AUXTOUT1 output drivers)                                                        |

| 26   | VDDSPK     | Analog Output  | BTL Speaker Negative Output or Left high current output                                     |

| 20   | VDDSPK     | Supply         | Speaker Supply (power supply pin for RSPKOUT, LSPKOUT, AUXOUT2 and AUXTOUT1 output drivers) |

| 27   | VREF       | Reference      | Decoupling for Midrail Reference Voltage                                                    |

| 28   | VSSA       | Supply         | Analog Ground                                                                               |

| 29   | RHP        | Analog Output  | Headphone Positive Output / Line Output Right                                               |

| 30   | LHP        | Analog Output  | Headphone Negative Output / Line Output Left                                                |

| 31   | VDDA       | Supply         | Analog Power Supply                                                                         |

| 32   | MICBIAS    | Analog Output  | Microphone Bias                                                                             |

## **Electrical Characteristics**

Conditions: VDDC = 1.8V, VDDA = VDDB = VCCSPK = 3.3V, MCLK = 12.88MHz,  $T_A$  = +25°C, 1kHz signal, fs = 48kHz, 24-bit audio data, 64X oversampling rate, unless otherwise stated.

| Parameter                              | Symbol            | Comments/Conditions                   | Min | Тур        | Max   | Units            |

|----------------------------------------|-------------------|---------------------------------------|-----|------------|-------|------------------|

| Analog to Digital Converter (AD        | C)                | -                                     |     |            |       |                  |

| Full scale input signal <sup>1</sup>   | V <sub>INFS</sub> | PGABST = 0dB                          |     | 1.0        |       | Vrms             |

|                                        |                   | PGAGAIN = 0dB                         |     | 0          |       | dBV              |

| Signal-to-noise ratio                  | SNR               | Gain = 0dB, A-weighted                | tbd | 90         |       | dB               |

| Total harmonic distortion <sup>2</sup> | THD+N             | Input = -3dB FS input                 |     | -80        | tbd   | dB               |

| Channel separation                     |                   | 1kHz input signal                     |     | 103        |       | dB               |

| Digital to Analog Converter (DA        | C) driving RHI    | P / LHP with 10kΩ / 50pF load         |     |            |       |                  |

| Full-scale output                      |                   | Output boost disabled                 |     | VDDA/3.    | 3     | $V_{rms}$        |

|                                        |                   | PGA gains = 0dB                       |     |            |       |                  |

|                                        |                   | AUX1BST = 1                           |     |            |       |                  |

|                                        |                   | AUX2BST = 1                           |     |            |       | $V_{rms}$        |

|                                        |                   | Output boost enabled                  | 1.5 | * (VDDA /  | (3.3) |                  |

|                                        |                   | PGA gains = 0dB                       |     |            |       |                  |

|                                        |                   | AUX1BST = 0                           |     |            |       |                  |

|                                        |                   | AUX2BST = 0                           |     |            |       |                  |

| Signal-to-noise ratio                  | SNR               | A-weighted                            | 88  | 94         |       | dB               |

| Total harmonic distortion <sup>2</sup> | THD+N             | $R_L = 10k\Omega$ ; full-scale signal |     | -84        | tbd   | dB               |

| Channel separation                     |                   | 1kHz input signal                     |     | 96         |       | dB               |

| Output Mixers                          |                   |                                       |     |            |       |                  |

| Maximum PGA gain into mixer            |                   |                                       |     | +6         |       | dB               |

| Minimum PGA gain into mixer            |                   |                                       |     | -15        |       | dB               |

| PGA gain step into mixer               |                   | Guaranteed monotonic                  |     | 3          |       | dB               |

| Speaker Output (RSPKOUT / LS           | PKOUT with 8      | Ω bridge-tied-load)                   |     | •          |       | *                |

| Full scale output 4                    |                   | SPKBST = 1                            | 7   | VCCSPK / 3 | 3.3   | $V_{rms}$        |

|                                        |                   | SPKBST = 0                            | (VC | CSPK / 3.3 | * 1.5 | V <sub>rms</sub> |

| Total harmonic distortion <sup>2</sup> | THD+N             | $P_0 = 200 \text{mW}$                 |     | *63        |       | dB               |

| Total narmonic distortion              | IIIDIII           | VDDSPK=3.3V                           |     | 03         |       | ub               |

|                                        |                   | $P_0 = 320 \text{mW}$                 |     | -64        |       | dB               |

|                                        |                   | VDDSPK = 3.3V                         |     | -04        |       | ub               |

|                                        |                   | $P_0 = 500 \text{mW},$                |     | -60        |       | dB               |

|                                        |                   | VDDSPK = 5V                           |     |            |       | ub               |

|                                        |                   | $P_0 = 860 \text{mW},$                |     | -61        |       | dB               |

|                                        |                   | VDDSPK = 5V                           |     | 01         |       | 4.2              |

| Signal-to-noise ratio                  | SNR               | VDDSPK = 3.3V                         |     | 91         |       | dB               |

|                                        |                   | LIDD CDLL CLL                         |     | 00         |       | ID.              |

|                                        |                   | VDDSPK=5V                             |     | 90         |       | dB               |

| Power supply rejection ratio           | PSRR              |                                       |     | 81         |       | dB               |

| (50Hz - 22kHz)                         |                   | VDDSPK = 5V (boost)                   |     | 72         |       | dB               |

| Analog Outputs (RHP / LHP; RS          | DKULL / LCD       | , , , ,                               |     | , 2        |       | 3.5              |

| Maximum programmable gain              | FRUUT / LSPI      | NOU1)                                 |     | 16         | T     | ďD               |

|                                        |                   |                                       |     | +6<br>-57  | +     | dB               |

| Minimum programmable gain              |                   | Cumming description                   |     |            | 1     | dB               |

| Programmable gain step size            |                   | Guaranteed monotonic                  |     | 1 05       |       | dB               |

| Mute attenuation                       |                   | 1kHz full scale signal                |     | 85         |       | dB               |

## Electrical Characteristics, cont'd.

Conditions: VDDC = 1.8V, VDDA = VDDB = VCCSPK = 3.3V, MCLK = 12.288MHz,  $T_A = +25$ °C, 1kHz signal, fs = 48kHz, 24-bit audio data, unless otherwise stated.

| Parameter                                                | Symbol              | Comments/Conditions                     | Min           | Тур         | Max          | Units            |

|----------------------------------------------------------|---------------------|-----------------------------------------|---------------|-------------|--------------|------------------|

| Headphone Output (RHP / LHP with                         | th $32\Omega$ load) |                                         |               |             |              |                  |

| 0dB full scale output voltage                            |                     |                                         |               | AVDD / 3.3  | 3            | V <sub>rms</sub> |

| Signal-to-noise ratio                                    | SNR                 | A-weighted                              | 92            |             | dB           |                  |

| Total harmonic distortion <sup>2</sup>                   | THD+N               | $R_L = 16\Omega, \ P_o = 20 \text{mW},$ |               | 80          |              | dB               |

|                                                          |                     | VDDA = 3.3V                             |               |             |              |                  |

|                                                          |                     | $R_L = 32\Omega$ , $P_o = 20$ mW,       |               | 85          |              | dB               |

| AUVOUTA / AUVOUTA - 41 101 O                             | /50-E11             | VDDA = 3.3V                             |               |             |              |                  |

| AUXOUT1 / AUXOUT2 with 10kΩ Full scale output            | / 50pr 10ad         | AUX1BST = 0                             | 7             | /DDSPK / 3  | 2            | V <sub>rms</sub> |

| run scare output                                         |                     | AUX2BST = 0 $AUX2BST = 0$               | ,             | DDSFK/3     | .3           | V rms            |

|                                                          |                     | AUX1BST = 1                             | (VD           | DSPK / 3.3) | * 1.5        | $V_{rms}$        |

|                                                          |                     | AUX2BST = 1                             |               |             |              |                  |

| Signal-to-noise ratio                                    | SNR                 |                                         |               | 87          |              | dB               |

| Total harmonic distortion <sup>2</sup>                   | THD+N               |                                         |               | -83         |              | dB               |

| Channel separation                                       |                     | 1kHz signal                             |               | 99          |              | dB               |

| Power supply rejection ratio                             | PSRR                |                                         |               | 53          |              | dB               |

| (50Hz - 22kHz)                                           |                     | VDDSPK = 5V (boost)                     |               | 56          |              | dB               |

| Microphone Inputs (LMICP, LMIC                           | N, RMICP, I         | RMICN, LLIN, RLIN) and Pr               | <br>ogrammabl | e Gain Amı  | olifier (PGA | (1)              |

| Full scale input signal <sup>1</sup>                     |                     | PGABST = 0dB                            | <u> </u>      | 1.0         |              | Vrms             |

| , ,                                                      |                     | PGAGAIN = 0dB                           |               | 0           |              | dBV              |

| Programmable gain                                        |                     |                                         | -12           |             | 35.25        | dB               |

| Programmable gain step size                              |                     | Guaranteed Monotonic                    |               | 0.75        |              | dB               |

| Mute Attenuation                                         |                     |                                         |               | 120         |              | dB               |

| Input resistance                                         |                     | Inverting Input                         |               | 1.6         |              | 1.0              |

|                                                          |                     | PGA Gain = 35.25dB<br>PGA Gain = 0dB    |               | 1.6<br>47   |              | kΩ<br>kΩ         |

|                                                          |                     | PGA Gain = 0dB<br>PGA Gain = -12dB      |               | 75          |              | kΩ               |

|                                                          |                     | Non-inverting Input                     |               | 94          |              | kΩ               |

| Input capacitance                                        |                     | 1100 myereing input                     |               | 10          |              | pF               |

| PGA equivalent input noise                               |                     | 0 to 20kHz, Gain set to                 |               | 120         |              | μV               |

|                                                          |                     | 35.25dB                                 |               |             |              |                  |

| Input Boost Mixer                                        |                     |                                         |               |             |              |                  |

| Gain boost                                               |                     | Boost disabled                          |               | 0           |              | dB               |

|                                                          |                     | Boost enabled                           |               | 20          |              | dB               |

| Gain range LLIN / RLIN or LAUXIN / RAUXIN to boost/mixer |                     |                                         | -12           |             | 6            | dB               |

| Gain step size to boost/mixer                            |                     |                                         |               | 3           |              | dB               |

| Auxiliary Analog Inputs (LAUXIN,                         | RAUXIN)             |                                         | 1             |             |              | ub.              |

| Full scale input signal <sup>1</sup>                     |                     | Gain = 0dB                              |               | 1.0         |              | Vrms             |

|                                                          |                     |                                         |               | 0           |              | dBV              |

| Input resistance                                         |                     | Aux direct-to-out path, only            |               |             |              |                  |

|                                                          |                     | Input gain = $+6.0$ dB                  |               | 20          |              | kΩ               |

|                                                          |                     | Input gain = 0.0dB                      |               | 40          |              | kΩ               |

| T                                                        |                     | Input gain = -12dB                      |               | 159         | 1            | kΩ               |

| Input capacitance                                        |                     |                                         |               | 10          |              | pF               |

#### Electrical Characteristics, cont'd.

Conditions: VDDC = 1.8V, VDDA = VDDB = VCCSPK = 3.3V, MCLK = 12.88MHz,  $T_A = +25^{\circ}$ C, 1kHz signal, fs = 48kHz, 24-bit audio data, unless otherwise stated.

| Parameter                                              | Symbol               | Comments/Conditions                          | Min           | Тур                             | Max           | Units        |  |  |  |  |  |

|--------------------------------------------------------|----------------------|----------------------------------------------|---------------|---------------------------------|---------------|--------------|--|--|--|--|--|

| Automatic Level Control (ALC) & Limiter: ADC path only |                      |                                              |               |                                 |               |              |  |  |  |  |  |

| Target record level                                    |                      |                                              | -22.5         |                                 | -1.5          | dBFS         |  |  |  |  |  |

| Programmable gain                                      |                      |                                              | -12           |                                 | 35.25         | dB           |  |  |  |  |  |

| Gain hold time <sup>3</sup>                            | t <sub>HOLD</sub>    | Doubles every gain step, with 16 steps total | 0 / 2.6       | 7 / 5.33 /                      | / 43691       | ms           |  |  |  |  |  |

| Gain ramp-up (decay) <sup>3</sup>                      | t <sub>DCY</sub>     | ALC Mode<br>ALC = 0                          |               | 8 / 16 / /                      |               | ms           |  |  |  |  |  |

|                                                        |                      | Limiter Mode<br>ALC = 1                      |               | 2/4//1                          |               | ms           |  |  |  |  |  |

| Gain ramp-down (attack) <sup>3</sup>                   | $t_{ATK}$            | ALC Mode<br>ALC = 0                          |               | 1/2/4//1024 n                   |               | ms           |  |  |  |  |  |

|                                                        |                      | Limiter Mode<br>ALC = 1                      | 0.25          | / 0.5 / 1 /                     | . / 128       | ms           |  |  |  |  |  |

| Mute Attenuation                                       |                      |                                              |               | 120                             |               | dB           |  |  |  |  |  |

| Microphone Bias                                        |                      |                                              |               |                                 |               |              |  |  |  |  |  |

| Bias voltage                                           | V <sub>MICBIAS</sub> | See Figure 3                                 |               | 0, 0.60,0.65,<br>75, 0.85, or 0 | ,             | VDDA<br>VDDA |  |  |  |  |  |

| Bias current source                                    | $I_{MICBIAS}$        |                                              |               | 3                               |               | mA           |  |  |  |  |  |

| Output noise voltage                                   | V <sub>n</sub>       | 1kHz to 20kHz                                |               | 14                              |               | nV/√Hz       |  |  |  |  |  |

| Digital Input/Output                                   |                      |                                              |               |                                 |               |              |  |  |  |  |  |

| Input HIGH level                                       | V <sub>IL</sub>      |                                              | 0.7 *<br>VDDC |                                 |               | V            |  |  |  |  |  |

| Input LOW level                                        | V <sub>IH</sub>      |                                              |               |                                 | 0.3 *<br>VDDC | V            |  |  |  |  |  |

| Output HIGH level                                      | V <sub>OH</sub>      | $I_{Load} = 1 \text{mA}$                     | 0.9 *<br>VDDC |                                 |               | V            |  |  |  |  |  |

| Output LOW level                                       | V <sub>OL</sub>      | $I_{Load} = -1  \text{mA}$                   |               |                                 | 0.1 *<br>VDDC | V            |  |  |  |  |  |

| Input capacitance                                      |                      |                                              |               | 10                              |               | pF           |  |  |  |  |  |

#### Notes

- 1. Full Scale is relative to the magnitude of VDDA and can be calculated as FS = VDDA/3.3.

- 2. Distortion is measured in the standard way as the combined quantity of distortion products plus noise. The signal level for distortion measurements is at 3dB below full scale, unless otherwise noted.

- 3. Time values scale proportionally with MCLK. Complete descriptions and definitions for these values are contained in the detailed descriptions of the ALC functionality.

- 4. With default register settings, SPKVDD should be 1.5xVDDA (but not exceeding maximum recommended operating voltage) to optimize available dynamic range in the AUXOUT1, AUXOU2, RSPKOUT, and LSPKOUT outputs stages.

## **Absolute Maximum Ratings**

| Condition                                                  | Min        | Max         | Units |

|------------------------------------------------------------|------------|-------------|-------|

| VDDB, VDDC, VDDA supply voltages                           | -0.3       | +3.90       | V     |

| VDDSPK supply voltage (default register configuration)     | -0.3       | +5.80       | V     |

| VDDSPK supply voltage (optional low voltage configuration) | -0.3       | +3.90       | V     |

| Core Digital Input Voltage range                           | VSSD – 0.3 | VDDC + 0.30 | V     |

| Buffer Digital Input Voltage range                         | VSSD – 0.3 | VDDB + 0.30 | V     |

| Analog Input Voltage range                                 | VSSA – 0.3 | VDDA + 0.30 | V     |

| Industrial operating temperature                           | -40        | +85         | °C    |

| Storage temperature range                                  | -65        | +150        | °C    |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely influence product reliability and result in failures not covered by warranty.

## **Operating Conditions**

| Condition                     | Symbol                 | Min  | Typical | Max  | Units |

|-------------------------------|------------------------|------|---------|------|-------|

| Digital supply range (Core)   | VDDC                   | 1.65 |         | 3.60 | V     |

| Digital supply range (Buffer) | VDDB                   | 1.65 |         | 3.60 | V     |

| Analog supply range           | VDDA                   | 2.50 |         | 3.60 | V     |

| Speaker supply (SPKBST=0)     | VDDSPK                 | 2.50 |         | 5.50 | V     |

| Speaker supply (SPKBST=1)     | VDDSPK                 | 2.50 |         | 5.50 | V     |

| Ground                        | VSSD<br>VSSA<br>VSSSPK |      | 0       |      | V     |

- 1. VDDA must be  $\geq$  VDDC.

- 2. VDDB must be  $\geq$  VDDC.

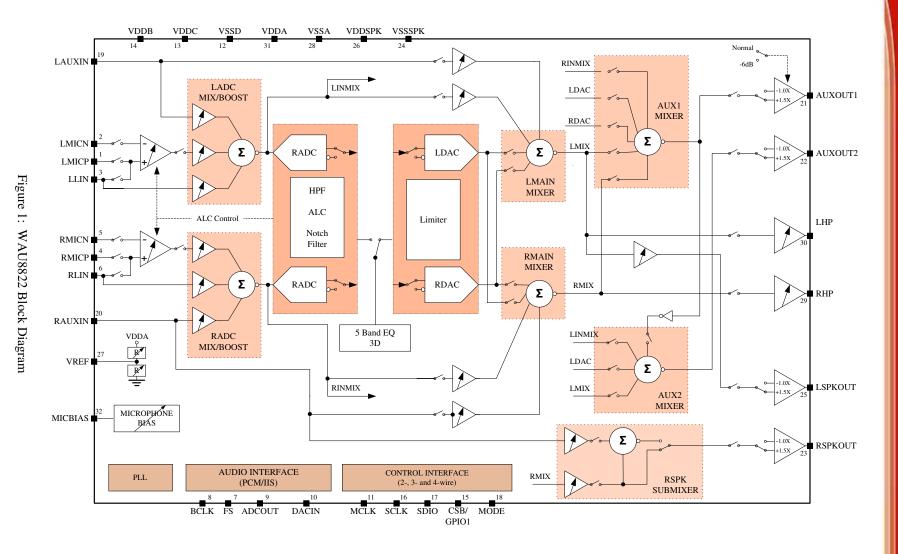

### 1 General Description

The WAU8822 is a stereo device with identical left and right channels that share common support elements. Additionally, the right channel auxiliary output path includes a dedicated submixer that supports mixing the right auxiliary input directly into the right speaker output driver. This enables the right speaker channel to output audio that is not present on any other output.

#### 1.1.1 Analog Inputs

All inputs, except for the wide range programmable amplifier (PGA), have available analog input gain conditioning of -15dB through +6dB in 3dB steps. All inputs also have individual muting functions with excellent channel isolation and off-isolation from all outputs. All inputs are suitable for full quality, high bandwidth signals.

Each of the left-right stereo channels includes a low noise differential PGA amplifier, programmable for high-gain input. This may be used for a microphone level through line level source. Gain may be set from +35.25db through -12dB at the analog difference-amplifier type programmable amplifier input stage. A separate additional 20dB analog gain is available on this input path, between the PGA output and ADC mixer input. The output of the ADC mixer may be routed to the ADC and/or analog bypass to the analog output sections.

Each channel also has a line level input. This input may be routed to the input PGA, and/or directly to the ADC input mixer.

Each channel has a separate additional auxiliary input. This is a line level input which may be routed the ADC input mixer and/or directly to the analog output mixers.

#### 1.1.2 Analog Outputs

There are six high current analog audio outputs. These are very flexible outputs that can be used individually or in stereo pairs for a wide range of end uses. However, these outputs are optimized for specific functions and are described in this section using the functional names that are applicable to those optimized functions.

Each output receives its signal source from built-in analog output mixers. These mixers enable a wide range of signal combinations, including muting of all sources. Additionally, each output has a programmable gain function, output mute function, and output disable function.

The RHP and LHP headphone outputs are optimized for driving a stereo pair of headphones, and are powered from the main analog voltage supply rail, VDDA. These outputs may be coupled using traditional DC blocking series capacitors. Alternatively, these may be configured in a no-capacitor DC coupled design using a virtual ground at ½ VDDA provided by an AUXOUT analog output.

The AUXOUT1 and AUXOUT2 analog outputs are powered from the VDDSPK supply rail and VSSSPK ground return path. The supply rail may be the same as VDDA, or may be a separate voltage up to 5.5Vdc. This higher voltage enables these outputs to have an increased output voltage range and greater output power capability.

The RSPKOUT and LSPKOUT loudspeaker outputs are powered from the VDDSPK power supply rail and VSSGND ground return path. LSPKOUT receives its audio signal via an additional submixer. This submixer supports combining a traditional alert sound (from the RAUXIN input) with the right channel headphone output mixer signal. This submixer also provides the signal invert function that is necessary for the normal BTL (Bridge Tied Load) configuration used to drive a high power external loudspeaker. Alternatively, each loudspeaker output may be used individually as a separate high current analog output driver.

*emPowerAudio*™

#### 1.1.3 ADC, DAC, and Digital Signal Processing

Each left and right channel has an independent high quality ADC and DAC associated with it. These are high performance, 24-bit delta-sigma converters that are suitable for a very wide range of applications.

The ADC and DAC functions are each individually supported by powerful analog mixing and routing. The ADC output may be routed to the digital output path and/or to the input of the DAC in a digital passthrough mode. The ADC and DAC blocks are also supported by advanced digital signal processing subsystems that enable a very wide range of programmable signal conditioning and signal optimizing functions. All digital processing is with 24-bit precision, as to minimize processing artifacts and maximize the audio dynamic range supported by the WAU8822.

The ADCs are supported by a wide range, mixed-mode Automatic Level Control (ALC), a high pass filter, and a notch filter. All of these features are optional and highly programmable. The high pass filter function is intended for DC-blocking or low frequency noise reduction, such as to reduce unwanted ambient noise or "wind noise" on a microphone input. The notch filter may be programmed to greatly reduce a specific frequency band or frequency, such as a 50Hz, 60Hz, or 217Hz unwanted noise.

The DACs are supported by a programmable limiter/DRC (Dynamic Range Compressor). This is useful to optimize the output level for various applications and for use with small loudspeakers. This is an optional feature that may be programmed to limit the maximum output level and/or boost an output level that is too small.

Digital signal processing is also provided for a 3D Audio Enhancement function, and for a 5-Band Equalizer. These features are optional, and are programmable over wide ranges. This pair of digital processing features may be applied jointly to either the ADC audio path or to the DAC audio path, but not to both paths simultaneously.

#### 1.1.4 Voltage Reference and Microphone Bias

Built-in power management includes a high stability voltage reference. This is used as an internal reference, and to generate a high quality, programmable microphone bias supply voltage that is well isolated from the supply rails. This microphone bias supply is suitable for both conventional electret (ECM) type microphone, and to power the newer MEMS all-silicon type microphones.

#### 1.1.5 Digital Interfaces

Command and control of the device is accomplished using a 2-wire/3-wire/4-wire serial control interface. This is a simple, but highly flexible interface that is compatible with many commonly used command and control serial data protocols and host drivers.

Digital audio input/output data streams are transferred to and from the device separately from command and control. The digital audio data interface supports either I2S or PCM audio data protocols, and is compatible with commonly used industry standard devices that follow either of these two serial data formats.

#### 1.1.6 Clock Requirements

The clocking signals required for the audio signal processing, audio data I/O, and control logic may be provided externally, or by optional operation of a built-in PLL (Phase Locked Loop). An external master clock (MCLK) signal must be active for analog audio logic paths to align with control register updates, and is required as the reference clock input for the PLL, if the PLL is used.

The PLL is provided as a low cost, zero external component count optional method to generate required clocks in almost any system. The PLL is a fractional-N divider type design, which enables generating accurate desired audio sample rates derived from a very wide range of commonly available system clocks.

The frequency of the system clock provided as the PLL reference frequency may be any stable frequency in the range between 8MHz and 33MHz. Because the fractional-N multiplication factor is a very high precision 24-bit value, any desired sample rate supported by the WAU8822 can be generated with very high accuracy, typically limited by the accuracy of the external reference frequency. Reference clocks and sample rates outside of these ranges are also possible, but may involve performance tradeoffs and increased design verification.

*emPowerAudio*™

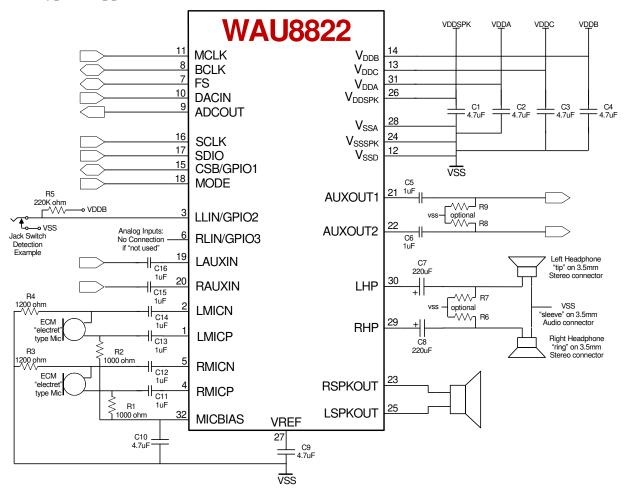

## 2 Application Information

#### 2.1 Typical Application Schematic

Figure 2: Schematic with recommended external components for typical application with AC-coupled headphones and stereo electret (ECM) style microphones.

- Note 1: All non-polar capacitors are assumed to be low ESR type parts, such as with MLC construction or similar. If capacitors are not low ESR, additional 0.1ufd and/or 0.01ufd capacitors may be necessary in parallel with the bulk 4.7ufd capacitors on the supply rails.

- Note 2: Load resistors to ground on outputs may be helpful in some applications to insure a DC path for the output capacitors to charge/discharge to the desired levels. If the output load is always present and the output load provides a suitable DC path to ground, then the additional load resistors may not be necessary. If needed, such load resistors are typically a high value, but a value dependent upon the application requirements.

- Note 3: To minimize pops and clicks, large polarized output capacitors should be a low leakage type.

- Note 4: Depending on the microphone device and PGA gain settings, common mode rejection can be improved by choosing the resistors on each node of the microphone such that the impedance presented to any noise on either microphone wire is equal.

*emPowerAudio*™

### 2.2 Power Consumption

WAU8822 has flexible power management capability which allows sections not being used to be powered down, to draw minimum current in battery-powered applications. Table – shows typical power consumption in different operating conditions.

| Mode     | Conditions                          | VDDA<br>= 3V | VDDC<br>= 1.8V | VDDB<br>= 3V | Total<br>Power |

|----------|-------------------------------------|--------------|----------------|--------------|----------------|

|          |                                     | mA           | mA             | mA           | mW             |

| OFF      |                                     | tbd          | tbd            | tbd          | tbd            |

| Sleep    | VREF off, no clocks,                | 0.1          | 0.001          | 0.0003       | 0.15           |

|          | VREF maintained @ 75kΩ, no clocks,  | 0.0          | 0.001          | 0.0003       | 0.045          |

|          | VREF maintained @ 300kΩ, no clocks, | 0.0          | 0.001          | 0.0003       | 0.025          |

|          | VREF maintained @ 5kΩ, no clocks,   | 0.3          | 0.001          | 0.0003       | 0.78           |

| Stereo   | 8kHz                                | 7.9          | 1.7            | 0.005        | 26.7           |

| Record   | 8kHz, PLL on                        | 10.4         | 2.9            | 0.07         | 36.6           |

| Stereo   | 16Ω HP, 44.1kHz, PLL on, sine wave  | 24.5         | 8.2            | 0.07         | 88.5           |

| Playback | 16Ω HP, 44.1kHz, quiescent          | 4.4          | 6.2            | 0.005        | 24.4           |

|          | 16Ω HP, 44.1kHz, white noise        | 7.2          | 6.5            | 0.005        | 33.3           |

|          | 16Ω HP, 44.1kHz, sine wave          | 22.0         | 6.8            | 0.005        | 78.3           |

|          | 16Ω HP, 44.1kHz, PLL on, sine wave  | 24.5         | 8.2            | 0.07         | 88.5           |

Table 1: Typical Power Consumption in Various Application Modes.

## 2.3 Supply Currents of Specific Blocks

WAU8822 can be programmed to enable/disable various analog blocks individually, and the current to some of the major blocks can be reduced with minimum impact on performance. The table below shows the change in current consumed with different register settings. Sample rate settings will vary current consumption of VDDC supply, which draws consumes approximately 4mA @ 1.8V and fs = 48kHz. Lower sampling rates draw lower current.

| Reg | ister | Function   | Bit          | VDDA current increase/                                                             |           |        |

|-----|-------|------------|--------------|------------------------------------------------------------------------------------|-----------|--------|

| Dec | Hex   | 1 i        |              | Decrease when enabled                                                              |           |        |

|     |       |            | REFIMP[1:0]  | $+100$ μA for $80$ k $\Omega$ and $300$ k $\Omega$<br>$+260$ μA for $3$ k $\Omega$ |           |        |

|     |       |            | IOBUFEN[2]   | +100μA                                                                             |           |        |

|     |       |            | ABIASEN[3]   | +600μΑ                                                                             |           |        |

| 1   | 0.1   | Power      |              | MICBIASEN[4]                                                                       | +540µA    |        |

| 1   | 01    | Management | PLLEN[5]     | +2.5 mA +1/5mA from VDDC with clocks applied                                       |           |        |

|     |       |            | AUX2MXEN[6]  | +200μΑ                                                                             |           |        |

|     |       |            | AUX1MXEN[7]  | +200μΑ                                                                             |           |        |

|     |       |            | DCBUFEN[8]   | +140μΑ                                                                             |           |        |

|     |       |            | LADCEN[0]    | +2.3 mA with 64X OSR<br>+3.3 mA with 128X OSR                                      |           |        |

|     |       |            | RADCEN[1]    | +2.3 mA with 64X OSR<br>+3.3 mA with 128X OSR                                      |           |        |

|     | 02    | Power      | LPGAEN[2]    | +300μΑ                                                                             |           |        |

| 2   |       | 02         | 2 02         | Management                                                                         | RPGAEN[3] | +300μΑ |

|     |       | 2          | LBSTEN[4]    | +650μΑ                                                                             |           |        |

|     |       |            | RBSTEN[5]    | +650μΑ                                                                             |           |        |

|     |       |            | SLEEP[6]     |                                                                                    |           |        |

|     |       |            |              |                                                                                    | LHPEN[7]  | +800μΑ |

|     |       |            | RHPEN[8]     | +800μΑ                                                                             |           |        |

|     |       |            | LDACEN[0]    | +1.6 mA with 64X OSR                                                               |           |        |

|     |       |            | EDITCEI\[0]  | +1.7 mA with 128X OSR                                                              |           |        |

|     |       |            | RDACEN[1]    | +1.6 mA with 64X OSR                                                               |           |        |

|     |       |            |              | +1.7 mA with 128X OSR                                                              |           |        |

|     |       | Power      | LMIXEN[2]    | +250μΑ                                                                             |           |        |

| 3   | 03    | Management | RMIXEN[3]    | +250μΑ                                                                             |           |        |

|     |       | 3          | BIASGEN[4]   |                                                                                    |           |        |

|     |       |            | RSPKEN[5]    | +1.1 mA from VDDSPK                                                                |           |        |

|     |       |            | LSPKEN[6]    | +1.1 mA from VDDSPK                                                                |           |        |

|     |       |            | AUXOUT2EN[7] | +225μΑ                                                                             |           |        |

|     |       |            | AUXOUT1EN[8] | +225μΑ                                                                             |           |        |

|     |       |            | IBIADJ[1:0]  | -1.2mA with IBIADJ at 11                                                           |           |        |

|     |       |            | REGVOLT[2:3] |                                                                                    |           |        |

|     |       | Power      | MICBIASM[4]  |                                                                                    |           |        |

| 58  | 3A    | Management | LPSPKD[5]    | 11 4 11 000 1 000                                                                  |           |        |

|     |       | 4          | LPADC[6]     | -1.1mA with no SNR decrease @ 8kHz                                                 |           |        |

|     |       |            | LPIPBST[7]   | -600μA with no SNR decrease @ 8kHz                                                 |           |        |

|     |       |            | LPDAC[8]     | -1.1mA with 1.4dB SNR decrease<br>@ 44.1kHz                                        |           |        |

Table 2: VDDA 3.3V Supply Current in Various Modes

## 3 Appendix A: Digital Filter Characteristics

| Parameter                            | Conditions   | Min   | Тур   | Max      | Units |

|--------------------------------------|--------------|-------|-------|----------|-------|

| ADC Filter                           |              |       | •     | <u>'</u> |       |

| Passband                             | +/- 0.015dB  | 0     |       | 0.454    | fs    |

| Passoand                             | -6dB         |       | 0.5   |          | fs    |

| Passband Ripple                      |              |       |       | +/-0.015 | dB    |

| Stopband                             |              | 0.546 |       |          | fs    |

| Stopband Attenuation                 | f > 0.546*fs | -60   |       |          | dB    |

| Group Delay                          |              |       | 28.25 |          | 1/fs  |

| ADC High Pass Filter                 |              |       |       |          |       |

|                                      | -3dB         |       | 3.7   |          | Hz    |

| High Pass Filter Corner<br>Frequency | -0.5dB       |       | 10.4  |          | Hz    |

| requesty                             | -0.1dB       |       | 21.6  |          | Hz    |

| DAC Filter                           |              |       |       |          |       |

| Passband                             | +/- 0.035dB  | 0     |       | 0.454    | fs    |

| rassualiu                            | -6dB         |       | 0.5   |          | fs    |

| Passband Ripple                      |              |       |       | +/-0.035 | dB    |

| Stopband                             |              | 0.546 |       |          | fs    |

| Stopband Attenuation                 | f > 0.546*fs | -55   |       |          | dB    |

| Group Delay                          |              |       | 28    |          | 1/fs  |

Table 3: Digital Filter Characteristics

#### **TERMINOLOGY**

- 1. Stop Band Attenuation (dB) the degree to which the frequency spectrum is attenuated (outside audio band)

- 2. Pass-band Ripple any variation of the frequency response in the pass-band region

- 3. Note that this delay applies only to the filters and does not include other latencies, such as from the serial data interface

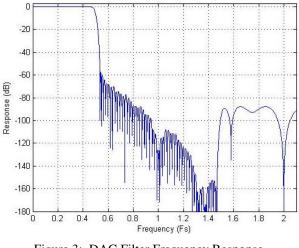

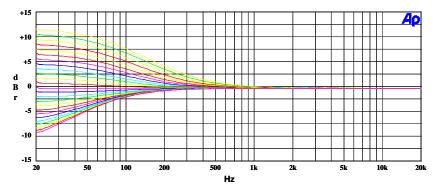

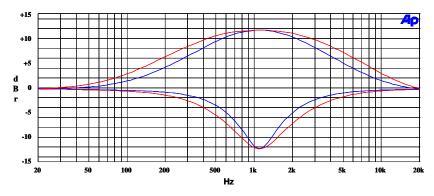

Figure 3: DAC Filter Frequency Response

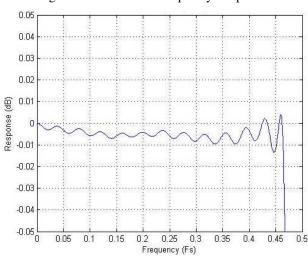

Figure 4: DAC Filter Ripple

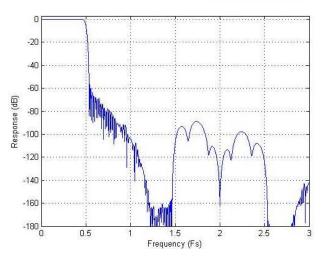

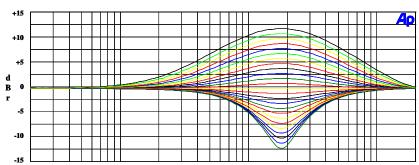

Figure 5: ADC Filter Frequency Response

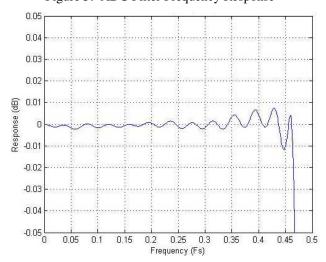

Figure 6: ADC Filter Ripple

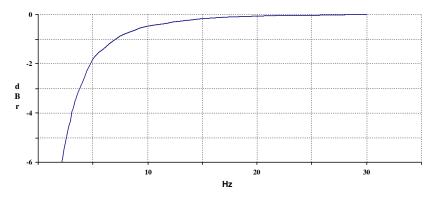

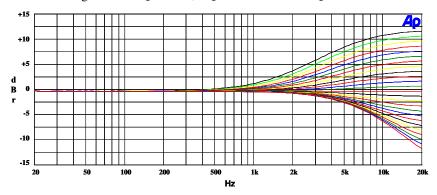

Figure 7: ADC Highpass Filter Response, Audio Mode

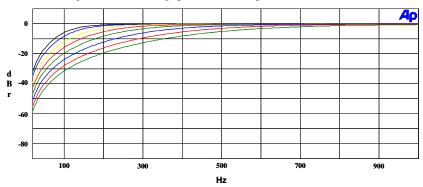

Figure 8: ADC Highpass Filter Response, HPF enabled, FS = 48kHz

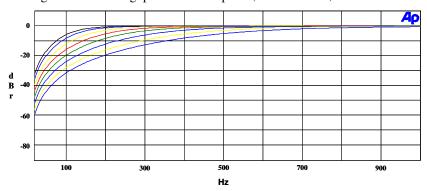

Figure 9: ADC Highpass Filter Response, HPF enabled, FS = 24kHz

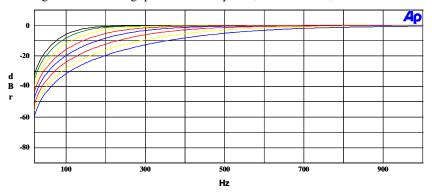

Figure 10: ADC Highpass Filter Response, HPF enabled, FS = 12kHz

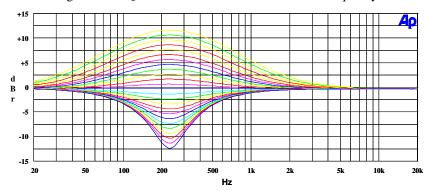

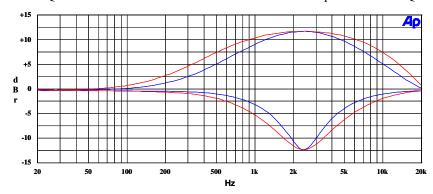

Figure 11: EQ Band 1 Gains for Lowest Cut-Off Frequency

Figure 12: EQ Band 2 Peak Filter Gains for Lowest Cut-Off Frequency with EQ2BW = 0

Figure 13: EQ Band 2, EQ2BW = 0 versus EQ2BW = 1

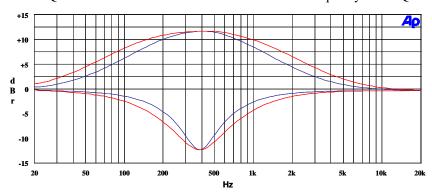

Figure 14: EQ Band 3 Peak Filter Gains for Lowest Cut-Off Frequency with EQ3BW = 0

Figure 15: EQ Band 3, EQ3BW = 0 versus EQ3BW = 1

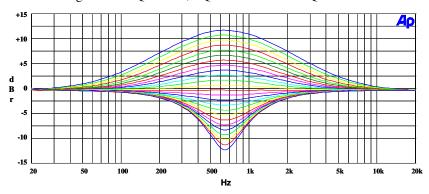

Figure 16: EQ Band 4 Peak Filter Gains for Lowest Cut-Off Frequencies with EQ4BW = 0

Figure 17: EQ Band 4, EQ4BW = 0 versus EQ4BW =1

Figure 18: EQ Band 5 Gains for Lowest Cut-Off Frequency

# 4 Appendix D: Register Overview

| DEC      | HEX      | NAME                              | Bit 8              | Bit 7      | Bit 6     | Bit5           | Bit 4       | Bit 3       | Bit 2     | Bit 1     | Bit 0          | Default    |

|----------|----------|-----------------------------------|--------------------|------------|-----------|----------------|-------------|-------------|-----------|-----------|----------------|------------|

| 0        | 00       | Software Reset                    | Die                | Dit i      | 210       |                | SET (SOFTWA |             | 2002      | 200.2     | Dit 0          | Delaute    |

| 1        | 01       | Power Management 1                | DCBUFEN            | AUX1MXEN   | AUX2MXEN  | PLLEN          | MICBIASEN   | ABIASEN     | IOBUFEN   | RF        | EFIMP          | 000        |

| 2        | 02       | Power Management 2                | RHPEN              | NHPEN      | SLEEP     | RBSTEN         | LBSTEN      | RPGAEN      | LPGAEN    | RADCEN    | LADCEN         | 000        |

| 3        | 03       |                                   |                    | AUXOUT2EN  | LSPKEN    | RSPKEN         | BIASGEN     | RMIXEN      | LMIXEN    | RDACEN    | LDACEN         | 000        |

|          |          | lio Controls                      | MONOCITEN          | HOROGIZEN  | ESI KEN   | ROTRET         | BINDGEN     | KIVIIZKEIV  | LIVIDALIT | REFICEIV  | EDITEER        | 000        |

| 4        | 04       | Audio Interface                   | BCLKP              | LRP        | WL        | FN             | AIF         | MT          | DACPHS    | ADCPHS    | MONO           | 050        |

| 5        | 05       | Companding                        | BCLKI              | Reserved   | ***       | CMB8           | DAC         |             |           | CCM       | PASSTHRU       | 000        |

| 6        | 06       | Clock Control 1                   | CLKM               | Reserved   | MCLKSEL   | CMB6           | DAG         | BCLKSEL     | AD        | Reserved  | CLKIOEN        | 140        |

| 7        | 07       | Clock Control 2                   | 4WSPIEN            |            | Rese      | rvod           | l           | BCLKSLL     | SMPLR     | Reserved  | SCLKEN         | 000        |

| 8        | 08       | GPIO                              | 4WSFIEN            | Reserved   | Kese      | GPIO           | 1DI I       | GPIO1PL     | SWIFLK    | GPIO1SEL  |                | 000        |

| 9        | 09       |                                   | ICKN               | IIDEN      | JCKDEN    | JCK            |             | GFIOTEL     | D.        |           |                | 000        |

| 10       |          | Jack Detect 1<br>DAC Control      |                    |            |           |                |             | DACOS       |           | eserved   | LDACDI         |            |

|          | 0A<br>0B | Left DAC Volume                   |                    | erved      | SOFTMT    | Rese           | LDAC        | DACOS       | AUTOMT    | RDACPL    | LDACPL         | 000        |

| 11       |          |                                   | LDACVU             |            |           |                |             |             |           |           |                | 0FF        |

| 12       | 0C<br>0D | Right DAC Volume<br>Jack Detect 2 | RDACVU<br>Reserved |            | ICKD      | OFNII          | KDAC        | CGAIN       | ICE       | TDOENO    |                | 0FF        |

| 13       |          |                                   |                    | IIDEAM     | JCKD      |                |             | ADCOS       |           | DOEN0     | LADCDI         | 000        |

| 14<br>15 | 0E       | ADC Control                       | HPFEN              | HPFAM      |           | HPF            | LADO        | ADCOS       | Reserved  | RADCPL    | LADCPL         | 100        |

|          | F<br>10  | Left ADC Volume                   | LADCVU             |            |           |                | LADO        |             |           |           |                | 0FF<br>0FF |

| 16       |          | Right ADC Volume                  | RADCVU             |            |           |                | RADO        | GAIN        |           |           |                | UFF        |

| 17       | 11       | Reserved                          |                    |            |           |                |             |             |           |           |                |            |

| Equal    |          | EO11 . ss                         | EOM                | ъ .        | FO        | LOTE           | ı           |             | FOLGO     |           |                | 120        |

| 18       | 12       | EQ1-low cutoff                    | EQM                | Reserved   | EQ1       |                | -           |             | EQ1GC     |           |                | 12C        |

| 19       | 13       | EQ2-peak 1                        | EQ2BW              | Reserved   | EQ2       |                | ļ           |             | EQ2GC     |           |                | 02C        |

| 20       | 14       | EQ3-peak 2                        | EQ3BW              | Reserved   | EQ:       |                |             |             | EQ3GC     |           |                | 02C        |

| 21       | 15       | EQ4-peak3                         | EQ4BW              | Reserved   | EQ4       |                |             |             | EQ4GC     |           |                | 02C        |

| 22       | 16       | EQ5-high cutoff                   | Rese               | erved      | EQ:       | OCF            |             |             | EQ5GC     |           |                | 02C        |

| 23       | 17       | Reserved                          |                    |            |           |                |             |             |           |           |                |            |

|          | Limite   |                                   |                    | 1          |           |                |             |             |           |           |                |            |

| 24       |          | DAC Limiter 1                     | DACLIMEN           | <u> </u>   | DACLI     |                |             |             |           | LIMATK    |                | 032        |

| 25       | 19       | DAC Limiter 2                     | Rese               | erved      |           | DACLIMTHL      |             |             | DAC       | CLIMBST   |                | 000        |

| 26       | 1A       | Reserved                          |                    |            |           |                |             |             |           |           |                |            |

|          | Filter   | l                                 |                    | 1          |           |                |             |             |           |           |                |            |

| 27       | 1B       | Notch Filter 1                    | NFCU1              | NFCEN      |           |                |             | NFCA0[13:7] |           |           |                | 000        |

| 28       | 1C       | Notch Filter 2                    | NFCU2              | Reserved   |           |                |             | NFCA0[6:0]  |           |           |                | 000        |

| 29       | 1D       | Notch Filter 3                    | NFCU3              | Reserved   |           |                |             | NFCA1[13:7] |           |           |                | 000        |

| 30       | 1E       | Notch Filter 4                    | NFCU4              | Reserved   |           |                |             | NFCA1[6:0]  |           |           |                | 000        |

| 31       | 1F       | Reserved                          |                    |            |           |                |             |             |           |           |                |            |

|          | _        | oise Gate Control                 |                    |            |           |                |             |             |           |           |                |            |

| 32       | 20       | ALC Control 1                     |                    | CEN        | Reserved  |                | ALCMXGAIN   |             | l .       | ALCMNGAI  | N              | 038        |

| 33       | 21       | ALC Control 2                     | Reserved           |            | ALC       |                |             |             |           | LCSL      |                | 00B        |

| 34       | 22       | ALC Control 3                     | ALCM               |            | ALCI      | DCY            | I           |             | Al        | CATK      |                | 032        |

| 35       | 23       | Noise Gate                        |                    | Rese       | rved      |                | ALCTBLSEL   | ALCNEN      |           | ALCNTH    |                | 010        |

|          |          | d Loop                            |                    |            |           |                |             |             |           |           |                |            |

| 36       | 24       | PLL N                             |                    | Rese       | rved      | П              | PLLMCLK     |             |           | PLLN      |                | 008        |

| 37       | 25       | PLL K 1                           |                    | Reserved   |           |                | DI I III 03 | PLLI        | K[23:18]  |           |                | 00C        |

| 38       | 26       | PLL K 2                           |                    |            |           |                | PLLK[17:9]  |             |           |           |                | 093        |

| 39       | 27       | PLL K 3                           |                    |            |           |                | PLLK[8:0]   |             |           |           | ) cropy : a) c | 0E9        |

| 40       | 28       | Mic Bias Mode                     |                    |            |           | Reserv         | ved         |             |           |           | MICBIASM       | 000        |

|          | llaneou  |                                   |                    |            | ъ .       |                |             |             |           | DEDELL    |                | 000        |

| 41       | 29       | 3D control                        |                    |            | Reserved  |                |             |             | 3D        | DEPTH     |                | 000        |

| 42       | 2A       | Reserved                          |                    |            |           |                | navr        |             | D         |           | n              | 0.7.7      |

| 43       | 2B       | Right Speaker Submix              |                    | Reserved   | DI DEST   | RMIXMUT        |             |             | RAUXRSUBG |           | RAUXSMUT       | 000        |

| 44       |          | Input Control                     |                    | BIASV      |           | RMICNRPGA      | KMICPRPGA   |             |           | LMICNLPGA | LMICPLPGA      | 033        |

| 45       | 2D       | Left Input PGA Gain               | LPGAU              | LPGAZC     | LPGAMT    |                |             |             | AGAIN     |           |                | 010        |

| 46       | 2E       | Right Input PGA Gain              | RPGAU              | RPGAZC     | RPGAMT    | PG + F cm = :: | , 1         |             | AGAIN     | T 41****  | Di             | 010        |

| 47       | 2F       | Left ADC Boost                    | LPGABST            | Reserved   |           | PGABSTGAIN     |             | Reserved    |           | LAUXBSTGA |                | 100        |

| 48       | 30       | Right ADC Boost                   | RPGABST            | Reserved   |           | RPGABSTGAIN    |             | SPKSTAGE    | anve      | RAUXBSTGA |                | 100        |

| 49       | 31       | Output Control                    |                    | erved      | LDACRMX   | RDACLMX        | AUX1BST     | AUX2BST     | SPKBST    | TSEN      | AOUTIMP        | 002        |

| 50       | 32       | Left Mixer                        |                    | LAUXMXGAIN |           | LAUXLMX        |             | BYPMXGAIN   |           | LBYPLMX   | LDACLMX        | 001        |

| 51       | 33       | Right Mixer                       |                    | RAUXMXGAIN |           | RAUXRMX        | F           | RBYPMXGAIN  |           | RBYPRMX   | RDACRMX        | 001        |

| 52       | 34       | LHP Volume                        | LHPVU              | LHPZC      | LHPMUTE   |                |             |             | PGAIN     |           |                | 039        |

| 53       | 35       | RHP Volume                        | RHPVU              | RHPZC      | RHPMUTE   |                |             |             | PGAIN     |           |                | 039        |

| 54       | 36       | LSPKOUT Volume                    | LSPKVU             | LSPKZC     | LSPKMUTE  |                |             |             | KGAIN     |           |                | 039        |

| 55       | 37       | RSPKOUT Volume                    | RSPKVU             | RSPKZC     | RSPKMUTE  |                |             |             | KGAIN     | 1         | ı              | 039        |

| 56       | 38       | AUX2 Mixer                        |                    | erved      |           |                |             |             | 001       |           |                |            |

| 57       | 39       | AUX1 Mixer                        |                    | erved      | AUXOUT1MT | AUX1HALF       | LMIXAUX1    | LDACAUX1    |           | RMIXAUX1  | RDACAUX1       | 001        |

| 58       | 3A       | Power Management 4                | LPDAC              | LPIPBST    | LPADC     | LPSPKD         | MICBIASM    | REGV        | /OLT      | II.       | BADJ           | 000        |

|          |          | Slot and ADCOUT Imp               | edance Option      | Control    |           |                |             |             |           |           |                |            |

| 59       |          | Left Time Slot                    |                    |            |           | I              | LTSLOT[8:0] |             | _         | T         | I              | 000        |

| 60       | 3C       | Misc                              | PCMTSEN            | TRI        | PCM8BIT   | PUDEN          | PUDPE       | PUDPS       | Reserved  | RTSLOT[9] | LTSLOT[9]      | 020        |

| 61       | 3D       | Right Time Slot                   |                    |            |           |                | RTSLOT[8:0] |             |           |           |                | 000        |

|          | _        | sion and Device ID                |                    |            |           |                |             |             |           |           |                |            |

| 62       | 3E       | Device Revision #                 | Reserved           |            |           |                | RI          | EV          |           |           |                | XXX        |

| 63       | 3F       | Device ID                         |                    |            |           |                | ID          |             |           |           |                | XXX        |

|          | 11000    | Data Sheet Rev 0                  |                    |            | D 1       | 9 of 21        |             |             |           | Sentembe  |                |            |

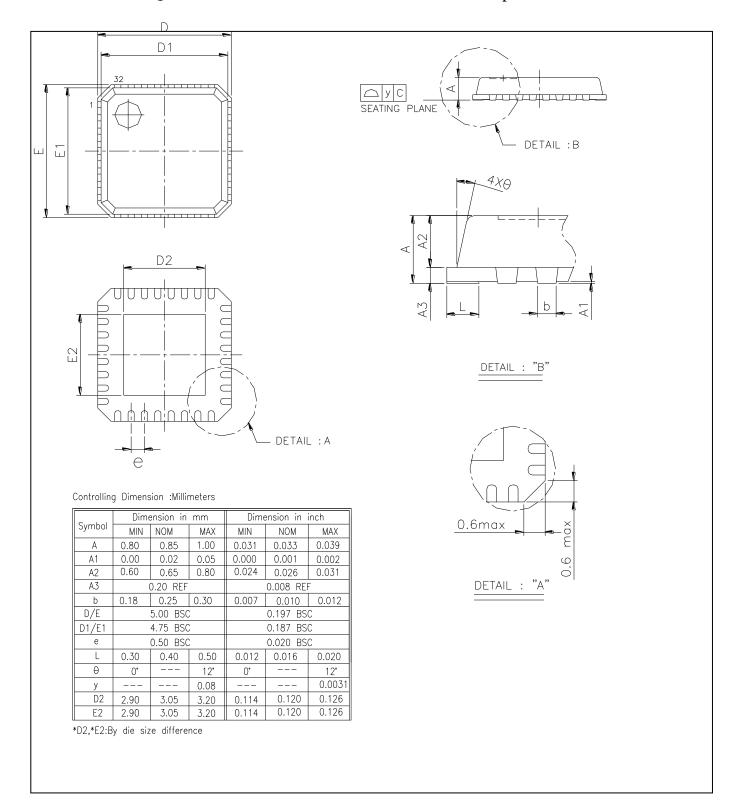

## 5 Package Dimensions

32-lead Plastic QFN; 5X5mm<sup>2</sup>, 1.0mm thickness, 0.5mm lead pitch

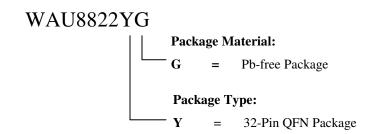

## 6 Ordering Information

Nuvoton Part Number Description

### Version History

| VERSION | DATE           | PAGE | DESCRIPTION          |

|---------|----------------|------|----------------------|

| A0.0    | February, 2008 | NA   | Preliminary Revision |

| A0.6    | May 2008       | NA   | Preliminary Revision |

| A0.86   | September 2008 | NA   | Preliminary Revision |

Table 4: Version History

#### **Important Notice**

Nuvoton products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Furthermore, Nuvoton products are not intended for applications wherein failure of Nuvoton products could result or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.

Nuvoton customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nuvoton for any damages resulting from such improper use or sales.

Please note that all data and specifications are subject to change without notice.

All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.