# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## WM8215

## 60MSPS 10-bit 3-Channel CCD Digitiser

## DESCRIPTION

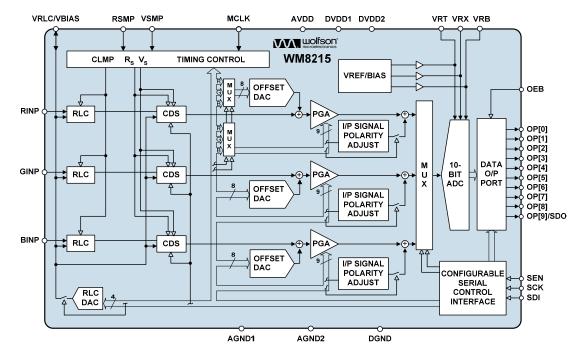

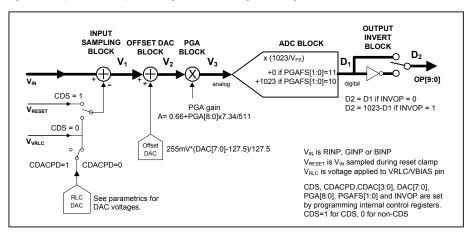

The WM8215 is a 10-bit analogue front end/digitiser IC which processes and digitises the analogue output signals from CCD sensors or Contact Image Sensors (CIS) at pixel sample rates of up to 60MSPS.

The device includes three analogue signal processing channels each of which contains Reset Level Clamping, Correlated Double Sampling and Programmable Gain and Offset adjust functions. The output from each of these channels is time multiplexed into a single high-speed 10-bit Analogue to Digital Converter. The digital output data is available in 10-bit wide parallel format.

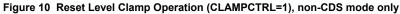

An internal 4-bit DAC is supplied for internal reference level generation. This may be used to reference CIS signals, in non-CDS mode or to clamp CCD signals during Reset Level Clamping. An external reference level may also be supplied. ADC references are generated internally, ensuring optimum performance from the device.

Using an analogue supply voltage of 3.3V and a digital interface supply of 3.3V, the WM8215 typically only consumes 400mW.

## FEATURES

- 10-bit ADC

- 60MSPS conversion rate

- Low power 400mW typical

- 3.3V single supply operation

- 3 channel operation

- Correlated double sampling

- Programmable gain (9-bit resolution)

- Programmable offset adjust (8-bit resolution)

- Flexible clamp timing

- Programmable clamp voltage

- Internally generated voltage references

- 32-lead QFN package

- Serial control interface

## APPLICATIONS

- Digital Copiers

- USB2.0 compatible scanners

- Multi-function peripherals

- High-speed CCD/CIS sensor interface

## **BLOCK DIAGRAM**

## TABLE OF CONTENTS

| FEATURES       1         APPLICATIONS       1         BLOCK DIAGRAM       1         TABLE OF CONTENTS       2         PIN CONFIGURATION       3         ORDERING INFORMATION       3         ORDERING INFORMATION       3         ORDERING INFORMATION       3         PIN DESCRIPTION       4         ABSOLUTE MAXIMUM RATINGS       5         RECOMMENDED OPERATING CONDITIONS       5         THERMAL PERFORMANCE       5         ELECTRICAL CHARACTERISTICS       6         INPUT VIDEO SAMPLING       8         SERIAL INTERFACE       10         INTERNAL POWER ON RESET CIRCUIT       11         DEVICE DESCRIPTION       13         INTRODUCTION       13         INTRODUCTION       13         INTRODUCTION       13         RESET LEVEL CLAMPING (RLC)       14         CD/NON-CDS PROCESSING       16         OFFSET ADJUST AND PROGRAMMABLE GAIN       16         ADC INPUT BLACK LEVEL ADJUST       17         OVERALL SIGNAL FLOW SUMMARY       18         CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT       19         REFERENCES       20         POWER MANAGEMENT       20                        | DESCRIPTION              | . 1 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|

| BLOCK DIAGRAM       1         TABLE OF CONTENTS       2         PIN CONFIGURATION       3         ORDERING INFORMATION       3         ORDERING INFORMATION       4         ABSOLUTE MAXIMUM RATINGS       5         RECOMMENDED OPERATING CONDITIONS       5         THERMAL PERFORMANCE       5         ELECTRICAL CHARACTERISTICS       6         INPUT VIDEO SAMPLING       8         SERIAL INTERFACE       10         INTERNAL POWER ON RESET CIRCUIT       11         DEVICE DESCRIPTION       13         INTRODUCTION       13         INTRODUCTION       13         INPUT SAMPLING       14         CDS/NON-ODS PROCESSING       16         ADC INPUT BLACK LEVEL ADJUST       17         OVERALL SIGNAL FLOW SUMMARY       18         CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT       19         PAEFERNCES       20         POWER MANAGEMENT       20         CONTROL INTERFACE       20         NORMAL OPERATION       23         REGISTER MAP       23         REGISTER MAP DESCRIPTION       24         APPLICATIONS INFORMATION       28         RECOMMENDED EXTERNAL COMPONENTS                  | FEATURES                 | . 1 |

| TABLE OF CONTENTS.2PIN CONFIGURATION3ORDERING INFORMATION3PIN DESCRIPTION4ABSOLUTE MAXIMUM RATINGS5RECOMMENDED OPERATING CONDITIONS.5THERMAL PERFORMANCE5ELECTRICAL CHARACTERISTICS6INPUT VIDEO SAMPLING8SERIAL INTERFACE10INTERNAL POWER ON RESET CIRCUIT11DEVICE DESCRIPTION13INTRODUCTION13INTRODUCTION13INTRODUCTION13INTRODUCTION16OFFSET ADJUST AND PROGRAMMABLE GAIN16OFFSET ADJUST AND PROGRAMMABLE GAIN16ADC INPUT BLACK LEVEL ADJUST17OVERALL SIGNAL FLOW SUMMARY20POWER MANAGEMENT20LINE-BY-LINE OPERATION20LINE-BY-LINE OPERATION23REGISTER MAP23REGISTER MAP23REGISTER MAP23REGISTER MAP23REGISTER MAP24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                | APPLICATIONS             | . 1 |

| TABLE OF CONTENTS.2PIN CONFIGURATION3ORDERING INFORMATION3PIN DESCRIPTION4ABSOLUTE MAXIMUM RATINGS5RECOMMENDED OPERATING CONDITIONS.5THERMAL PERFORMANCE5ELECTRICAL CHARACTERISTICS6INPUT VIDEO SAMPLING8SERIAL INTERFACE10INTERNAL POWER ON RESET CIRCUIT11DEVICE DESCRIPTION13INTRODUCTION13INTRODUCTION13INTRODUCTION14OFFSET ADJUST AND PROGRAMMABLE GAIN.16OFFSET ADJUST AND PROGRAMMABLE GAIN.16ADC INPUT BLACK LEVEL ADJUST17OVERALL SIGNAL FLOW SUMMARY.20LINE-BY-LINE OPERATION20LINE-BY-LINE OPERATION20LINE-BY-LINE OPERATION20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP23REGISTER MAP24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29ADDRESS:30                                                                                                                                                                                                                                                                                                                                                   | BLOCK DIAGRAM            | . 1 |

| PIN CONFIGURATION       3         ORDERING INFORMATION       3         PIN DESCRIPTION       4         ABSOLUTE MAXIMUM RATINGS       5         RECOMMENDED OPERATING CONDITIONS       5         THERMAL PERFORMANCE       5         ELECTRICAL CHARACTERISTICS       6         INPUT VIDEO SAMPLING       8         SERIAL INTERFACE       10         INTERNAL POWER ON RESET CIRCUIT       11         DEVICE DESCRIPTION       13         INTRODUCTION       13         INPUT SAMPLING (RLC)       14         CDFSET ADJUST AND PROGRAMMABLE GAIN       16         OFFSET ADJUST AND PROGRAMMABLE GAIN       16         ADC INPUT BLACK LEVEL ADJUST       17         OVERALL SIGNAL FLOW SUMMARY       20         POWER MANAGEMENT       20         POWER MANAGEMENT       20         NORMAL OPERATION       23         REGISTER MAP       23         REGISTER MAP       23         REGISTER MAP DESCRIPTION       24         APPLICATIONS INFORMATION       24         APPLICATIONS INFORMATION       24         RECOMMENDED EXTERNAL COMPONENTS       28         RECOMMENDED EXTERNAL COMPONENT VALUES       28 | TABLE OF CONTENTS        | . 2 |

| ORDERING INFORMATION3PIN DESCRIPTION4ABSOLUTE MAXIMUM RATINGS5RECOMMENDED OPERATING CONDITIONS5THERMAL PERFORMANCE5ELECTRICAL CHARACTERISTICS6INPUT VIDEO SAMPLING8SERIAL INTERFACE10INTERNAL POWER ON RESET CIRCUIT11DEVICE DESCRIPTION13INTRODUCTION13INTRODUCTION13RESET LEVEL CLAMPING (RLC)14CDFSET ADJUST AND PROGRAMMABLE GAIN16OFFSET ADJUST AND PROGRAMMABLE GAIN16OFFSET ADJUST AND PROGRAMMABLE GAIN17OVERALL SIGNAL FLOW SUMMARY18CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION23REGISTER MAP23REGISTER MAP23REGISTER MAP23REGISTER MAP23RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                  | PIN CONFIGURATION        | . 3 |

| PIN DESCRIPTION       4         ABSOLUTE MAXIMUM RATINGS       5         RECOMMENDED OPERATING CONDITIONS       5         THERMAL PERFORMANCE       5         ELECTRICAL CHARACTERISTICS       6         INPUT VIDEO SAMPLING       8         SERIAL INTERFACE       10         INTERNAL POWER ON RESET CIRCUIT       11         DEVICE DESCRIPTION       13         INTRODUCTION       13         INTRODUCTION       13         RESET LEVEL CLAMPING (RLC)       14         CDS/NON-CDS PROCESSING       16         OFFSET ADJUST AND PROGRAMMABLE GAIN       16         OFFSET ADJUST AND PROGRAMMABLE GAIN       17         OVERALL SIGNAL FLOW SUMMARY       18         CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT       19         REFERENCES       20         POWER MANAGEMENT       20         CONTROL INTERFACE       20         NORMAL OPERATION       23         REGISTER MAP       23         REGISTER MAP       23         REGISTER MAP       23         RECOMMENDED EXTERNAL COMPONENTS       28         RECOMMENDED EXTERNAL COMPONENT VALUES       28         PACKAGE DIMENSIONS       29          |                          |     |

| ABSOLUTE MAXIMUM RATINGS5RECOMMENDED OPERATING CONDITIONS5THERMAL PERFORMANCE5ELECTRICAL CHARACTERISTICS6INPUT VIDEO SAMPLING8SERIAL INTERFACE10INTERNAL POWER ON RESET CIRCUIT11DEVICE DESCRIPTION13INTRODUCTION13INPUT SAMPLING13RESET LEVEL CLAMPING (RLC)14CDS/NON-CDS PROCESSING16OFFSET ADJUST AND PROGRAMMABLE GAIN16ADC INPUT BLACK LEVEL ADJUST17OVERALL SIGNAL FLOW SUMMARY18CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                          |                          |     |

| RECOMMENDED OPERATING CONDITIONS5THERMAL PERFORMANCE5ELECTRICAL CHARACTERISTICS6INPUT VIDEO SAMPLING8SERIAL INTERFACE10INTERNAL POWER ON RESET CIRCUIT11DEVICE DESCRIPTION13INTRODUCTION13RESET LEVEL CLAMPING (RLC)14CDS/NON-CDS PROCESSING16OFFSET ADJUST AND PROGRAMMABLE GAIN16ADC INPUT BLACK LEVEL ADJUST17OVERALL SIGNAL FLOW SUMMARY18CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |     |

| THERMAL PERFORMANCE5ELECTRICAL CHARACTERISTICS6INPUT VIDEO SAMPLING8SERIAL INTERFACE10INTERNAL POWER ON RESET CIRCUIT11DEVICE DESCRIPTION13INTRODUCTION13INTRODUCTION13RESET LEVEL CLAMPING (RLC)14CDS/NON-CDS PROCESSING16OFFSET ADJUST AND PROGRAMMABLE GAIN16ADC INPUT BLACK LEVEL ADJUST17OVERALL SIGNAL FLOW SUMMARY20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20POWER MANAGEMENT20LINE-BY-LINE OPERATION22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |     |

| ELECTRICAL CHARACTERISTICS       6         INPUT VIDEO SAMPLING       8         SERIAL INTERFACE       10         INTERNAL POWER ON RESET CIRCUIT       11         DEVICE DESCRIPTION       13         INTRODUCTION       13         INPUT SAMPLING       13         RESET LEVEL CLAMPING (RLC)       14         CDS/NON-CDS PROCESSING       16         OFFSET ADJUST AND PROGRAMMABLE GAIN       16         ADC INPUT BLACK LEVEL ADJUST       17         OVERALL SIGNAL FLOW SUMMARY       18         CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT       19         REFERENCES       20         POWER MANAGEMENT       20         CONTROL INTERFACE       20         NORMAL OPERATION       20         CONTROL INTERFACE       20         NORMAL OPERATING MODES       22         DEVICE CONFIGURATION       23         REGISTER MAP       23         REGISTER MAP       23         REGISTER MAP DESCRIPTION       24         APPLICATIONS INFORMATION       28         RECOMMENDED EXTERNAL COMPONENTS       28         RECOMMENDED EXTERNAL COMPONENT VALUES       28         PACKAGE DIMENSIONS       29      |                          | -   |

| INPUT VIDEO SAMPLING8SERIAL INTERFACE10INTERNAL POWER ON RESET CIRCUIT11DEVICE DESCRIPTION13INTRODUCTION13INPUT SAMPLING13RESET LEVEL CLAMPING (RLC)14CDS/NON-CDS PROCESSING16OFFSET ADJUST AND PROGRAMMABLE GAIN16ADC INPUT BLACK LEVEL ADJUST17OVERALL SIGNAL FLOW SUMMARY18CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |     |

| SERIAL INTERFACE10INTERNAL POWER ON RESET CIRCUIT11DEVICE DESCRIPTION13INTRODUCTION13INPUT SAMPLING13RESET LEVEL CLAMPING (RLC)14CDS/NON-CDS PROCESSING16OFFSET ADJUST AND PROGRAMMABLE GAIN16ADC INPUT BLACK LEVEL ADJUST17OVERALL SIGNAL FLOW SUMMARY18CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |     |

| INTERNAL POWER ON RESET CIRCUIT11DEVICE DESCRIPTION13INTRODUCTION13INPUT SAMPLING13RESET LEVEL CLAMPING (RLC)14CDS/NON-CDS PROCESSING16OFFSET ADJUST AND PROGRAMMABLE GAIN16ADC INPUT BLACK LEVEL ADJUST17OVERALL SIGNAL FLOW SUMMARY18CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |     |

| DEVICE DESCRIPTION13INTRODUCTION13INPUT SAMPLING13RESET LEVEL CLAMPING (RLC)14CDS/NON-CDS PROCESSING16OFFSET ADJUST AND PROGRAMMABLE GAIN16ADC INPUT BLACK LEVEL ADJUST17OVERALL SIGNAL FLOW SUMMARY18CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |     |

| INTRODUCTION13INPUT SAMPLING13RESET LEVEL CLAMPING (RLC)14CDS/NON-CDS PROCESSING16OFFSET ADJUST AND PROGRAMMABLE GAIN16ADC INPUT BLACK LEVEL ADJUST17OVERALL SIGNAL FLOW SUMMARY18CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |     |

| RESET LEVEL CLAMPING (RLC)14CDS/NON-CDS PROCESSING.16OFFSET ADJUST AND PROGRAMMABLE GAIN.16ADC INPUT BLACK LEVEL ADJUST17OVERALL SIGNAL FLOW SUMMARY18CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |     |

| CDS/NON-CDS PROCESSING.16OFFSET ADJUST AND PROGRAMMABLE GAIN.16ADC INPUT BLACK LEVEL ADJUST.17OVERALL SIGNAL FLOW SUMMARY.18CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT.20LINE-BY-LINE OPERATION.20CONTROL INTERFACE.20NORMAL OPERATING MODES.22DEVICE CONFIGURATION.23REGISTER MAP.23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS.29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |     |

| OFFSET ADJUST AND PROGRAMMABLE GAIN.16ADC INPUT BLACK LEVEL ADJUST17OVERALL SIGNAL FLOW SUMMARY18CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |     |

| ADC INPUT BLACK LEVEL ADJUST17OVERALL SIGNAL FLOW SUMMARY18CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |     |

| OVERALL SIGNAL FLOW SUMMARY18CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |     |

| CALCULATING THE OUTPUT CODE FOR A GIVEN INPUT19REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |     |

| REFERENCES20POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |     |

| POWER MANAGEMENT20LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |     |

| LINE-BY-LINE OPERATION20CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |     |

| CONTROL INTERFACE20NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |     |

| NORMAL OPERATING MODES22DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |     |

| DEVICE CONFIGURATION23REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |     |

| REGISTER MAP23REGISTER MAP DESCRIPTION24APPLICATIONS INFORMATION28RECOMMENDED EXTERNAL COMPONENTS28RECOMMENDED EXTERNAL COMPONENT VALUES28PACKAGE DIMENSIONS29IMPORTANT NOTICE30ADDRESS:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |     |

| REGISTER MAP DESCRIPTION       24         APPLICATIONS INFORMATION       28         RECOMMENDED EXTERNAL COMPONENTS       28         RECOMMENDED EXTERNAL COMPONENT VALUES       28         PACKAGE DIMENSIONS       29         IMPORTANT NOTICE       30         ADDRESS:       30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | REGISTER MAP.            | 23  |

| RECOMMENDED EXTERNAL COMPONENTS       28         RECOMMENDED EXTERNAL COMPONENT VALUES       28         PACKAGE DIMENSIONS       29         IMPORTANT NOTICE       30         ADDRESS:       30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | REGISTER MAP DESCRIPTION | 24  |

| RECOMMENDED EXTERNAL COMPONENT VALUES       28         PACKAGE DIMENSIONS       29         IMPORTANT NOTICE       30         ADDRESS:       30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |     |

| PACKAGE DIMENSIONS         29           IMPORTANT NOTICE         30           ADDRESS:         30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |     |

| IMPORTANT NOTICE       30         ADDRESS:       30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |     |

| ADDRESS:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |     |

| REVISION FIGTORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | REVISION HISTORY         | 31  |

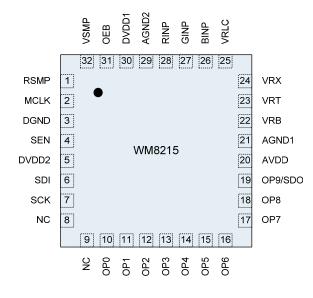

## **PIN CONFIGURATION**

## ORDERING INFORMATION

| DEVICE        | TEMPERATURE<br>RANGE | PACKAGE                                                | MOISTURE<br>SENSITIVITY<br>LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|---------------|----------------------|--------------------------------------------------------|----------------------------------|-------------------------------|

| WM8215CSEFL   | 0 to 70°C            | 32-lead QFN<br>(5x5x0.9mm)<br>(Pb-free)                | MSL1                             | 260°C                         |

| WM8215CSEFL/R | 0 to 70°C            | 32-lead QFN<br>(5x5x0.9mm)<br>(Pb-free, tape and reel) | MSL1                             | 260°C                         |

Note:

Reel quantity = 3,500

## **PIN DESCRIPTION**

| PIN | NAME       | TYPE            | DESCRIPTION                                                                                                                                                                                                                  |

|-----|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RSMP       | Digital input   | Reset sample pulse (when CDS=1) or clamp control                                                                                                                                                                             |

| 2   | MCLK       | Digital input   | Master (ADC) clock. This clock determines the ADC conversion rate.                                                                                                                                                           |

| 3   | DGND       | Supply          | Digital ground.                                                                                                                                                                                                              |

| 4   | SEN        | Digital input   | Enables the serial interface when high.                                                                                                                                                                                      |

| 5   | DVDD2      | Supply          | Digital supply, all digital I/O pins.                                                                                                                                                                                        |

| 6   | SDI        | Digital input   | Serial data input.                                                                                                                                                                                                           |

| 7   | SCK        | Digital input   | Serial clock.                                                                                                                                                                                                                |

| 8   | NC         | No connect      | No internal connection.                                                                                                                                                                                                      |

| 9   | NC         | No connect      | No internal connection.                                                                                                                                                                                                      |

|     |            |                 | Digital output data bus. ADC output data (d9:d0) is available in 10-bit parallel format.                                                                                                                                     |

| 10  | OP[0]      | Digital output  | d0 (LSB)                                                                                                                                                                                                                     |

| 11  | OP[1]      | Digital output  | d1                                                                                                                                                                                                                           |

| 12  | OP[2]      | Digital output  | d2                                                                                                                                                                                                                           |

| 13  | OP[3]      | Digital output  | d3                                                                                                                                                                                                                           |

| 14  | OP[4]      | Digital output  | d4                                                                                                                                                                                                                           |

| 15  | OP[5]      | Digital output  | d5                                                                                                                                                                                                                           |

| 16  | OP[6]      | Digital output  | d6                                                                                                                                                                                                                           |

| 17  | OP[7]      | Digital output  | d7                                                                                                                                                                                                                           |

| 18  | OP[8]      | Digital output  | d8                                                                                                                                                                                                                           |

| 19  | OP[9]/SDO  | Digital output  | d9 (MSB)                                                                                                                                                                                                                     |

|     |            |                 | Alternatively, pin OP[9]/SDO may be used to output register read-back data when OEB=0, OPD(register bit)=0 and SEN has been pulsed high. See Serial Interface description in Device Description section for further details. |

| 20  | AVDD       | Supply          | Analogue supply. This must be operated at the same potential as DVDD1.                                                                                                                                                       |

| 21  | AGND1      | Supply          | Analogue ground.                                                                                                                                                                                                             |

| 22  | VRB        | Analogue output | Lower reference voltage.<br>This pin must be connected to AGND via a decoupling capacitor.                                                                                                                                   |

| 23  | VRT        | Analogue output | Upper reference voltage.<br>This pin must be connected to AGND via a decoupling capacitor.                                                                                                                                   |

| 24  | VRX        | Analogue output | Input return bias voltage.<br>This pin must be connected to AGND via a decoupling capacitor.                                                                                                                                 |

| 25  | VRLC/VBIAS | Analogue I/O    | Selectable analogue output voltage for RLC or single-ended bias reference.<br>This pin would typically be connected to AGND via a decoupling capacitor.<br>VRLC can be externally driven if programmed Hi-Z.                 |

| 26  | BINP       | Analogue input  | Blue channel input video.                                                                                                                                                                                                    |

| 27  | GINP       | Analogue input  | Green channel input video.                                                                                                                                                                                                   |

| 28  | RINP       | Analogue input  | Red channel input video.                                                                                                                                                                                                     |

| 29  | AGND2      | Supply          | Analogue ground.                                                                                                                                                                                                             |

| 30  | DVDD1      | Supply          | Digital supply for logic and clock generator. This must be operated at the same potential as AVDD.                                                                                                                           |

| 31  | OEB        | Digital input   | Output Hi-Z control. All digital outputs set to high-impedance state when input pin OEB=1 or register bit OPD=1.                                                                                                             |

| 32  | VSMP       | Digital input   | Video sample pulse.                                                                                                                                                                                                          |

## **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at  $<30^{\circ}$ C / 85% Relative Humidity. Not normally stored in moisture barrier bag. MSL2 = out of bag storage for 1 year at  $<30^{\circ}$ C / 60% Relative Humidity. Supplied in moisture barrier bag. MSL3 = out of bag storage for 168 hours at  $<30^{\circ}$ C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                                            | MIN                | MAX                 |

|------------------------------------------------------|--------------------|---------------------|

| Analogue supply voltage: AVDD                        | GND - 0.3V         | GND + 4.2V          |

| Digital supply voltages: DVDD1 – 2                   | GND - 0.3V         | GND + 4.2V          |

| Digital ground: DGND                                 | GND - 0.3V         | GND + 0.3V          |

| Analogue grounds: AGND1 – 2                          | GND - 0.3V         | GND + 0.3V          |

| Digital inputs, digital outputs and digital I/O pins | GND - 0.3V         | DVDD2 + 0.3V        |

| Analogue inputs (RINP, GINP, BINP)                   | GND - 0.3V         | AVDD + 0.3V         |

| Other pins                                           | GND - 0.3V         | AVDD + 0.3V         |

| Operating temperature range: T <sub>A</sub>          | 0°C                | +70°C               |

| Storage temperature after soldering                  | -65 <sup>°</sup> C | +150 <sup>°</sup> C |

Notes:

1. GND denotes the voltage of any ground pin.

2. AGND1, AGND2 and DGND pins are intended to be operated at the same potential. Differential voltages between these pins will degrade performance.

## **RECOMMENDED OPERATING CONDITIONS**

| CONDITION                   | SYMBOL         | MIN  | ТҮР | MAX  | UNITS |

|-----------------------------|----------------|------|-----|------|-------|

| Operating temperature range | T <sub>A</sub> | 0    |     | 70   | °C    |

| Analogue supply voltage     | AVDD           | 2.97 | 3.3 | 3.63 | V     |

| Digital core supply voltage | DVDD1          | 2.97 | 3.3 | 3.63 | V     |

| Digital I/O supply voltage  | DVDD2          | 2.97 | 3.3 | 3.63 | V     |

Notes:

1. DVDD2 should be operated at the same potential as DVDD1  $\pm$  0.3V.

## THERMAL PERFORMANCE

| PARAMETER                                | SYMBOL                | TEST CONDITIONS             | MIN | TYP   | MAX | UNIT |

|------------------------------------------|-----------------------|-----------------------------|-----|-------|-----|------|

| Performance                              |                       |                             |     |       |     |      |

| Thermal resistance – junction to case    | $R_{	extsf{	heta}JC}$ | T - 25°0                    |     | 10.27 |     | °C/W |

| Thermal resistance – junction to ambient | $R_{	extsf{	heta}JA}$ | T <sub>ambient</sub> = 25°C |     | 29.45 |     | °C/W |

Notes:

1. Figures given are for package mounted on 4-layer FR4 according to JESD51-5 and JESD51-7.

## **ELECTRICAL CHARACTERISTICS**

#### Test Conditions

AVDD = DVDD1 = DVDD2 = 3.3V, AGND = DGND = 0V, T<sub>A</sub> = 25°C, MCLK = 60MHz unless otherwise stated.

| PARAMETER                                              | SYMBOL               | TEST<br>CONDITIONS                | MIN        | ТҮР    | MAX      | UNIT    |

|--------------------------------------------------------|----------------------|-----------------------------------|------------|--------|----------|---------|

| Overall System Specification (incl                     | uding 10-bit /       | ADC, PGA, Offset and CDS          | functions) |        |          |         |

| Conversion rate                                        |                      |                                   |            | 60     |          | MSPS    |

| Full-scale input voltage range                         |                      | LOWREFS=0, Max Gain               |            | 0.25   |          | Vp-p    |

| (see Note 1)                                           |                      | LOWREFS=0, Min Gain               |            | 3.03   |          | Vp-p    |

|                                                        |                      | LOWREFS=1, Max Gain               |            | 0.15   |          | Vp-p    |

|                                                        |                      | LOWREFS=1, Min Gain               |            | 1.82   |          | Vp-p    |

| Input signal limits (see Note 2)                       | V <sub>IN</sub>      |                                   | AGND-0.3   |        | AVDD+0.3 | V       |

| Input capacitance                                      |                      |                                   |            | 10     |          | pF      |

| Input switching impedance                              |                      |                                   |            | 45     |          | Ω       |

| Full-scale transition error                            |                      | Gain = 0dB;                       |            | 20     |          | mV      |

|                                                        |                      | PGA[8:0] = 14(hex)                |            |        |          |         |

| Zero-scale transition error                            |                      | Gain = 0dB;<br>PGA[8:0] = 14(hex) |            | 20     |          | mV      |

| Differential non-linearity                             | DNL                  |                                   |            | 0.75   |          | LSB     |

| Integral non-linearity                                 | INL                  |                                   |            | 2      |          | LSB     |

| Channel to channel gain matching                       |                      |                                   |            | 1%     |          | %       |

| Output noise                                           |                      | Min Gain                          |            | 0.2    |          | LSB rms |

|                                                        |                      | Max Gain                          |            | 2.15   |          | LSB rms |

| References                                             |                      |                                   |            |        |          |         |

| Upper reference voltage                                | VRT                  | LOWREFS=0                         | 1.95       | 2.05   | 2.25     | V       |

|                                                        |                      | LOWREFS=1                         |            | 1.85   |          | V       |

| Lower reference voltage                                | VRB                  | LOWREFS=0                         | 0.95       | 1.05   | 1.25     | V       |

| 5                                                      |                      | LOWREFS=1                         |            | 1.25   |          | V       |

| Input return bias voltage                              | VRX                  |                                   |            | 1.25   |          | V       |

| Diff. reference voltage (VRT-VRB)                      | V <sub>RTB</sub>     | LOWREFS=0                         | 0.95       | 1.0    | 1.10     | V       |

|                                                        |                      | LOWREFS=1                         | 0.57       | 0.6    | 0.68     | V       |

| Output resistance VRT, VRB, VRX                        |                      |                                   |            | 1      |          | Ω       |

| VRLC/Reset-Level Clamp (RLC)                           |                      | •                                 | 1 1        |        |          |         |

| RLC switching impedance                                |                      |                                   |            | 45     |          | Ω       |

| VRLC short-circuit current                             |                      |                                   |            | 2      |          | mA      |

| VRLC output resistance                                 |                      |                                   |            | 3      |          | Ω       |

| VRLC Hi-Z leakage current                              |                      | VRLC = 0 to AVDD                  |            | -      | 1        | μA      |

| RLCDAC resolution                                      |                      |                                   |            | 4      |          | bits    |

| RLCDAC step size, RLCDACRNG<br>= 0                     | V <sub>RLCSTEP</sub> |                                   |            | 0.173  |          | V/step  |

| RLCDAC step size, RLCDACRNG                            |                      | LOWREFS = 0                       |            | 0.11   |          |         |

| = 1                                                    | V <sub>RLCSTEP</sub> | LOWREFS = 1                       |            | 0.10   |          | V/step  |

| RLCDAC output voltage at<br>code 0(hex), RLCDACRNG = 0 | V <sub>RLCBOT</sub>  |                                   |            | 0.4    |          | V       |

| RLCDAC output voltage at                               | V <sub>RLCBOT</sub>  | LOWREFS = 0                       |            |        |          | V       |

| code 0(hex), RLCDACRNG = 1                             |                      | LOWREFS = 1                       | -          | 0.4    |          |         |

| RLCDAC output voltage at code F(hex) RLCDACRNG, = 0    | V <sub>RLCTOP</sub>  |                                   |            | 3.0    |          | V       |

| RLCDAC output voltage at                               | V <sub>RLCTOP</sub>  | LOWREFS = 0                       |            | 2.05   |          | V       |

| code F(hex), RLCDACRNG = $1$                           | ▼ RLCTOP             | LOWREFS = 1                       | -          | 1.85   |          | v       |

| RLCDAC                                                 | DNL                  |                                   | -0.5       | 1.00   | +0.5     | LSB     |

| RLCDAC                                                 | INL                  |                                   | -0.5       | +/-0.5 | +0.5     | LSB     |

Notes:

1. **Full-scale input voltage** denotes the peak input signal amplitude that can be gained to match the ADC full-scale input range.

2. Input signal limits are the limits within which the full-scale input voltage signal must lie.

**Test Conditions**

AVDD = DVDD1 = DVDD2 = 3.3V, AGND = DGND = 0V, T<sub>A</sub> = 25°C, MCLK = 60MHz unless otherwise stated.

| PARAMETER                                             | SYMBOL           | TEST<br>CONDITIONS    | MIN           | ТҮР                              | MAX         | UNIT    |

|-------------------------------------------------------|------------------|-----------------------|---------------|----------------------------------|-------------|---------|

| Offset DAC, Monotonicity Guara                        | nteed            |                       | •             | •                                | •           | •       |

| Resolution                                            |                  |                       |               | 8                                |             | bits    |

| Differential non-linearity                            | DNL              |                       |               | 0.15                             |             | LSB     |

| Integral non-linearity                                | INL              |                       |               | 0.4                              |             | LSB     |

| Step size                                             |                  |                       |               | 2.00                             |             | mV/step |

| Output voltage                                        |                  | Code 00(hex)          |               | -255                             |             | mV      |

|                                                       |                  | Code FF(hex)          |               | +255                             |             | mV      |

| Programmable Gain Amplifier                           |                  |                       |               |                                  | •           | •       |

| Resolution                                            |                  |                       |               | 9                                |             | bits    |

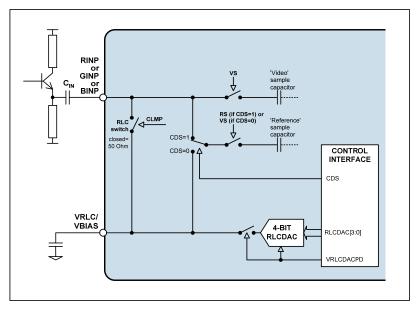

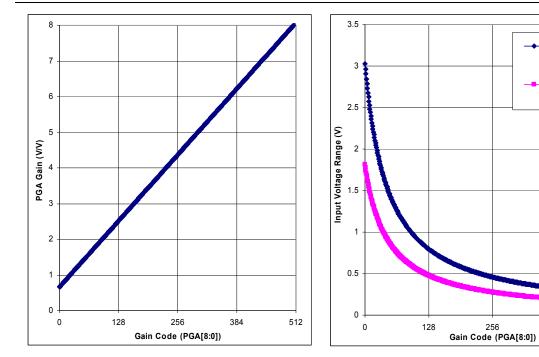

| Gain                                                  |                  |                       | 0.66 -        | $+\frac{7.34}{511}$ * <b>PGA</b> | [8:0]       | V/V     |

| May gain, each channel                                |                  |                       |               |                                  | -           | \//\/   |

| Max gain, each channel                                | G <sub>MAX</sub> |                       |               | 8                                |             | V/V     |

| Min gain, each channel                                | G <sub>MIN</sub> |                       |               | 0.66                             |             | V/V     |

| Gain error, each channel                              |                  |                       |               | 3                                |             | %       |

| Analogue to Digital Converter                         |                  |                       |               | 40                               |             | h. 14 - |

| Resolution                                            |                  |                       |               | 10                               |             | bits    |

| Speed                                                 |                  |                       |               |                                  | 60          | MSPS    |

| Full-scale input range                                |                  | LOWREFS=0             | 1.9           | 2                                | 2.2         | V       |

| (2*(VRT-VRB))                                         |                  | LOWREFS=1             |               | 1.2                              |             | V       |

| DIGITAL SPECIFICATIONS                                |                  |                       |               |                                  |             |         |

| Digital Inputs                                        |                  |                       |               |                                  | -           |         |

| High level input voltage                              | V <sub>IH</sub>  |                       | 0.7 * DVDD2   |                                  |             | V       |

| Low level input voltage                               | V <sub>IL</sub>  |                       |               |                                  | 0.2 * DVDD2 | V       |

| High level input current                              | I <sub>IH</sub>  |                       |               |                                  | 1           | μA      |

| Low level input current                               | I <sub>IL</sub>  |                       |               |                                  | 1           | μΑ      |

| Input capacitance                                     | Cı               |                       |               | 5                                |             | pF      |

| Digital Outputs                                       |                  |                       |               |                                  |             |         |

| High level output voltage                             | V <sub>он</sub>  | I <sub>он</sub> = 1mA | DVDD2 - 0.5   |                                  |             | V       |

| Low level output voltage                              | V <sub>OL</sub>  | I <sub>OL</sub> = 1mA |               |                                  | 0.5         | V       |

| High impedance output current                         | I <sub>OZ</sub>  |                       |               |                                  | 1           | μA      |

| Digital IO Pins                                       |                  |                       |               |                                  |             |         |

| Applied high level input voltage                      | V <sub>IH</sub>  |                       | 0.7 * DVDD2   |                                  |             | V       |

| Applied low level input voltage                       | VIL              |                       | D) (DD0_0_0_5 |                                  | 0.2 * DVDD2 | V       |

| High level output voltage                             | V <sub>OH</sub>  | I <sub>он</sub> = 1mA | DVDD2 - 0.5   |                                  |             | V       |

| Low level output voltage                              | V <sub>OL</sub>  | I <sub>OL</sub> = 1mA |               |                                  | 0.5         | V       |

| Low level input current                               | I <sub>IL</sub>  |                       |               |                                  | 1           | μΑ      |

| High level input current                              | I <sub>IH</sub>  |                       |               | -                                | 1           | μΑ      |

| Input capacitance                                     | C <sub>1</sub>   |                       |               | 5                                |             | pF      |

| High impedance output current                         | l <sub>oz</sub>  |                       |               |                                  | 1           | μA      |

| Supply Currents                                       | 1                |                       |               | 4.10                             |             |         |

| Total supply current – active                         |                  |                       |               | 116                              |             | mA      |

| Analogue supply current – active (three channel mode) |                  |                       |               | 105                              |             | mA      |

| Digital supply current – active                       |                  |                       |               | 11                               |             | mA      |

| (three channel mode)                                  |                  |                       |               |                                  |             |         |

| Supply current – full power down mode                 |                  |                       |               | 20                               |             | μΑ      |

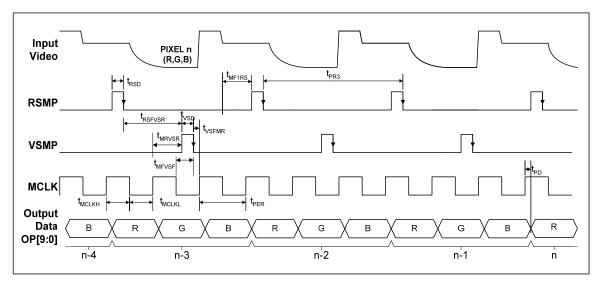

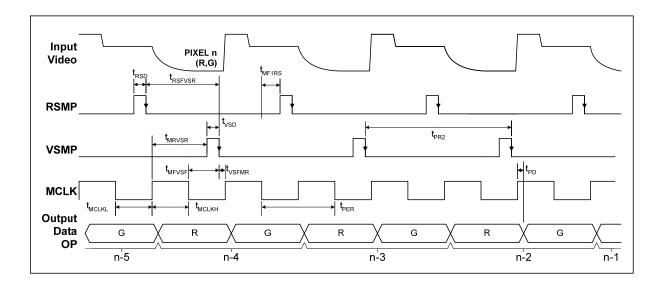

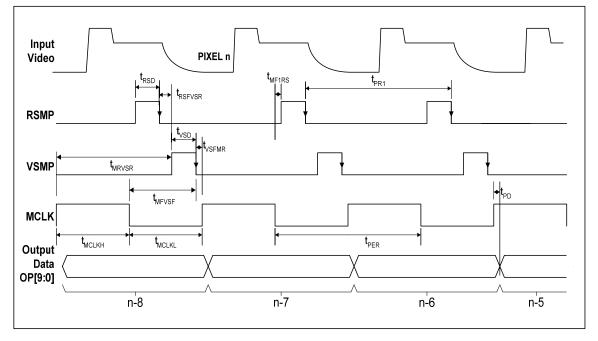

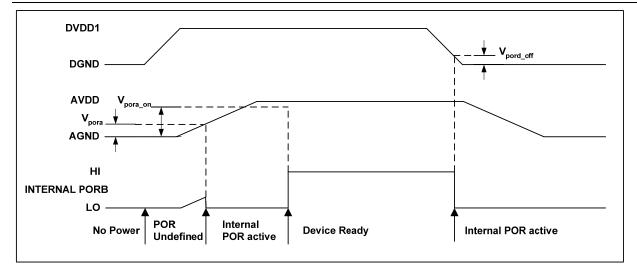

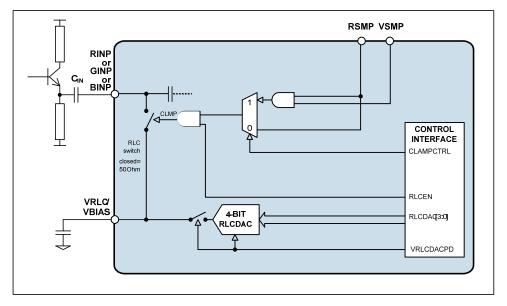

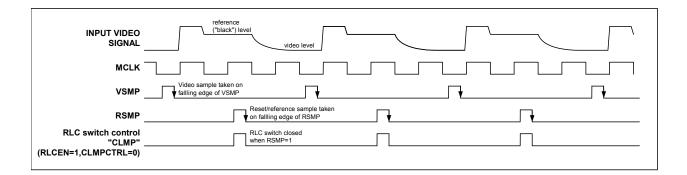

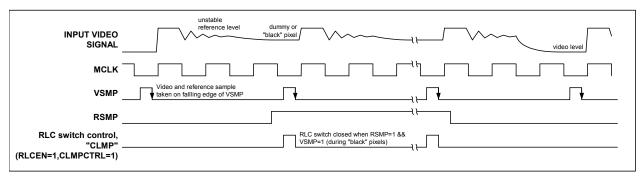

## **INPUT VIDEO SAMPLING**

Figure 1 Three-channel CDS Input Video Timing (CDS=1)

Figure 2 Two-channel CDS Operation (CDS=1)

Figure 3 One-channel CDS Operation (CDS=1)

#### Notes:

- 1. The relationship between input video signal and sample points is controlled by VSMP and RSMP.

- 2. When VSMP is high the input video signal is connected to the Video sampling capacitors.

- 3. When RSMP is high the input video signal is connected to the Reset sampling capacitors.

- 4. RSMP must not go high before the first falling edge of MCLK after VSMP goes low.

- 5. It is required that the falling edge of VSMP should occur before the rising edge of MCLK.

- 6. In 1-channel CDS mode it is not possible to have an equally spaced Video and Reset sample points with a 45MHz MCLK.

- 7. Non-CDS operation is also possible; RSMP is not required in this mode but can be used to control input clamping. Timing constraints between vsmp and mclk remain unchanged for non-CDS operation.

#### **Test Conditions**

AVDD = DVDD1 = DVDD2 = 3.3V, AGND = DGND = 0V, T<sub>A</sub> =  $25^{\circ}$ C, MCLK = 60MHz for 3 and 2-channel mode and 45MHz for 1-channel mode unless otherwise stated.

| PARAMETER                                                                | SYMBOL              | TEST CONDITIONS | MIN  | TYP  | MAX | UNITS |

|--------------------------------------------------------------------------|---------------------|-----------------|------|------|-----|-------|

| MCLK period – 2/3 channel mode                                           | t <sub>PER</sub>    |                 | 16.6 |      |     | ns    |

| 1 channel mode                                                           |                     |                 | 22.2 |      |     |       |

| MCLK high period – 2/3 channel mode                                      | t <sub>MCLKH</sub>  |                 | 6.7  | 8.3  |     | ns    |

| 1 channel mode                                                           |                     |                 |      | 11.1 |     |       |