# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 24-bit 192kHz 2Vrms Multi-Channel CODEC

# DESCRIPTION

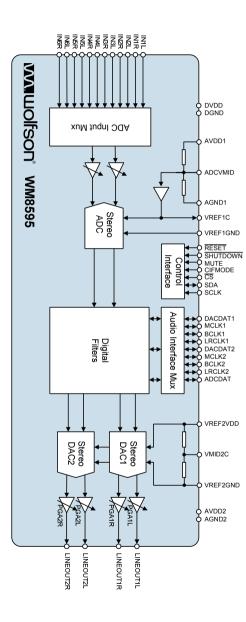

The WM8595 is a high performance multi-channel audio CODEC with flexible input/output selection and digital and analogue volume control. Features include a 24-bit stereo ADC with digital gain control, two 24-bit DACs with independent volume control and clocking, and a range of input/output channel selection options with analogue volume control for flexible routing within current and future audio systems.

The WM8595 has a six stereo input selector which accepts input levels up to 2Vrms. One stereo input can be selected through an input mux to be routed through to the ADC.

The WM8595 outputs two stereo audio channels at line levels up to 2Vrms, driven from independent DACs. The DAC channels include independent digital volume control, and both stereo output channels include analogue volume control with soft ramp.

The WM8595 supports up to 2Vrms analogue inputs, 2Vrms outputs, with sample rates from 32kHz to 192kHz on the DACs, and 32kHz to 96kHz on the ADC.

The WM8595 is controlled via a serial interface with support for 2-wire and 3-wire control with full readback. Control of mute, emergency shutdown and reset can also be achieved by pin selection.

The WM8595 is ideal for audio applications requiring high performance and flexible routing options, including flat panel digital TV and DVD recorder.

The WM8595 is available in a 48-pin QFN package.

# **FEATURES**

- Multi-channel CODEC with 6 stereo input selector and 2 stereo output selector

- 4-channel DAC, 2-channel ADC

- 6x2Vrms stereo input selector to ADC

- 2x2Vrms stereo output

- Audio performance

- DAC: 100dB SNR typical ('A' weighted @ 48kHz)

- DAC: -87dB THD typical

- ADC: 96dB SNR typical ('A' weighted @ 48kHz)

- ADC: -80dB THD typical

- Independent sampling rate for ADC and DACs possible

- DACs sampling frequency 32kHz 192kHz

- ADC sampling frequency 32kHz 96kHz

- DAC digital volume control +12dB to -100dB in 0.5dB steps

- ADC digital volume control from +30dB to -97dB in 0.5dB steps

- ADC input analogue boost control, selectable from 0dB, +3dB, +6dB and +12dB

- Output analogue volume control +6dB to -73.5dB in 0.5dB steps with zero cross or soft ramp to prevent pops and clicks

- Digital multiplexer to interface to multiple digital sources DSP, HDMI, memory card

- 2-wire and 3-wire serial control interface with readback and hardware reset, mute and emergency shutdown pins

- ADC features master or slave clocking modes

- Programmable format audio data interface modes

I2S, LJ, RJ, DSP

- 3.3V / 9V analogue, 3.3V digital supply operation

- 48-pin QFN package

# APPLICATIONS

- Digital Flat Panel TV

- DVD-RW

- Set Top Boxes

# **BLOCK DIAGRAM**

# TABLE OF CONTENTS

| DESCRIPTION1                                             | l |

|----------------------------------------------------------|---|

| FEATURES1                                                | I |

| APPLICATIONS1                                            |   |

| BLOCK DIAGRAM                                            | ) |

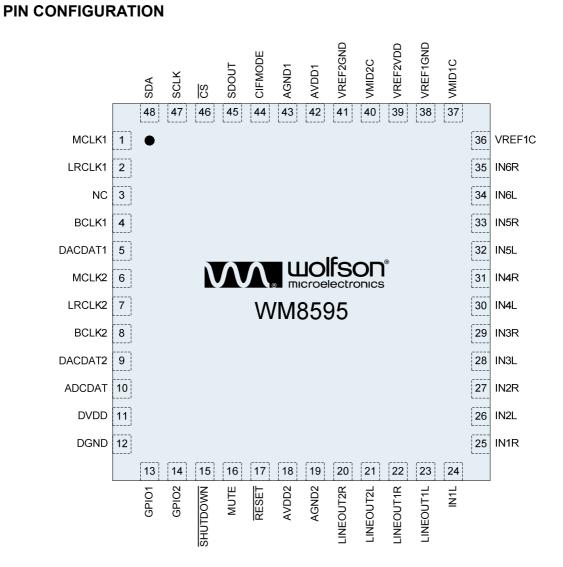

| PIN CONFIGURATION                                        |   |

| PIN DESCRIPTION                                          |   |

| ABSOLUTE MAXIMUM RATINGS                                 | 5 |

| RECOMMENDED OPERATING CONDITIONS7                        | , |

| SUPPLY CURRENT CONSUMPTION                               |   |

| ELECTRICAL CHARACTERISTICS                               | 3 |

| TERMINOLOGY                                              |   |

| MASTER CLOCK TIMING                                      |   |

| RESET TIMING                                             | I |

| DIGITAL AUDIO INTERFACE TIMING – SLAVE MODE              | 2 |

| DIGITAL AUDIO INTERFACE TIMING – MASTER MODE             | 3 |

| CONTROL INTERFACE TIMING – 2-WIRE MODE 14                |   |

| CONTROL INTERFACE TIMING – 3-WIRE MODE 15                |   |

| POWER ON RESET (POR)16                                   |   |

| DEVICE DESCRIPTION                                       |   |

| INTRODUCTION                                             |   |

| CONTROL INTERFACE                                        |   |

| 2-WIRE (SM-BUS COMPATIBLE) SERIAL CONTROL INTERFACE MODE |   |

| 3-WIRE (SPI COMPATIBLE) SERIAL CONTROL INTERFACE MODE    |   |

| DIGITAL AUDIO DATA FORMATS                               |   |

| DIGITAL AUDIO INTERFACE                                  |   |

| DIGITAL AUDIO DATA SAMPLING RATES                        |   |

| DAC FEATURES                                             |   |

| ANALOGUE OUTPUT VOLUME CONTROL                           |   |

| DIGITAL ROUTING CONTROL                                  |   |

| POP AND CLICK PERFORMANCE                                |   |

| GLOBAL ENABLE CONTROL                                    |   |

| EMERGENCY POWER DOWN                                     |   |

| REGISTER MAP                                             |   |

| DIGITAL FILTER CHARACTERISTICS                           |   |

| APPLICATIONS INFORMATION                                 |   |

| RECOMMENDED EXTERNAL COMPONENTS                          |   |

| RECOMMENDED ANALOGUE LOW PASS FILTER                     | ) |

| RELEVANT APPLICATION NOTES                               | ) |

| PACKAGE DIMENSIONS                                       |   |

| IMPORTANT NOTICE                                         |   |

| ADDRESS                                                  |   |

| REVISION HISTORY                                         |   |

# **ORDERING INFORMATION**

| ORDER CODE    | TEMPERATURE<br>RANGE | PACKAGE                                 | MOISTURE SENSITIVITY<br>LEVEL | PACKAGE BODY<br>TEMPERATURE |

|---------------|----------------------|-----------------------------------------|-------------------------------|-----------------------------|

| WM8595GEFL/V  | -40°C to +85°C       | 48-lead QFN<br>(Pb-free)                | MSL3                          | 260°C                       |

| WM8595GEFL/RV | -40°C to +85°C       | 48-lead QFN<br>(Pb-free, tape and reel) | MSL3                          | 260°C                       |

Note:

Reel quantity = 2200

# **PIN DESCRIPTION**

| PIN | NAME      | ТҮРЕ                 | DESCRIPTION                                                        |

|-----|-----------|----------------------|--------------------------------------------------------------------|

| 1   | MCLK1     | Digital Input/Output | Audio interface port 1 master clock input/output                   |

| 2   | LRCLK1    | Digital Input/Output | Audio interface port 1 left/right clock input/output               |

| 3   | N/C       |                      | No internal connection                                             |

| 4   | BCLK1     | Digital Input/Output | Audio interface port 1 bit clock input/output                      |

| 5   | DACDAT1   | Digital Input        | Audio interface port 1 data input for DAC1                         |

| 6   | MCLK2     | Digital Input/Output | Audio interface port 2 master clock input/output                   |

| 7   | LRCLK2    | Digital Input/Output | Audio interface port 2 left/right clock input/output               |

| 8   | BCLK2     | Digital Input/Output | Audio interface port 2 bit clock input/output                      |

| 9   | DACDAT2   | Digital Input        | Audio interface port 2 data input for DAC2                         |

| 10  | ADCDAT    | Digital Output       | Audio interface port 3 data output for ADC                         |

| 11  | DVDD      | Supply               | Digital supply                                                     |

| 12  | DGND      | Supply               | Digital ground                                                     |

| 13  | GPIO1     | Digital Input/Output | General purpose input/output 1                                     |

| 14  | GPIO2     | Digital Input/Output | General purpose input/output 2                                     |

| 15  | SHUTDOWN  | Digital Input        | Emergency shutdown                                                 |

| 16  | MUTE      | Digital Input        | Hardware DAC mute                                                  |

| 17  | RESET     | Digital Input        | Hardware reset                                                     |

| 18  | AVDD2     | Supply               | Analogue 9V supply                                                 |

| 19  | AGND2     | Supply               | Analogue 9V ground                                                 |

| 20  | LINEOUT2R | Analogue Output      | Output channel 2 right                                             |

| 21  | LINEOUT2L | Analogue Output      | Output channel 2 left                                              |

| 22  | LINEOUT1R | Analogue Output      | Output channel 1 right                                             |

| 23  | LINEOUT1L | Analogue Output      | Output channel 1 left                                              |

| 24  | IN1L      | Analogue Input       | Input channel 1 left                                               |

| 25  | IN1R      | Analogue Input       | Input channel 1 right                                              |

| 26  | IN2L      | Analogue Input       | Input channel 2 left                                               |

| 27  | IN2R      | Analogue Input       | Input channel 2 right                                              |

| 28  | IN3L      | Analogue Input       | Input channel 3 left                                               |

| 29  | IN3R      | Analogue Input       | Input channel 3 right                                              |

| 30  | IN4L      | Analogue Input       | Input channel 4 left                                               |

| 31  | IN4R      | Analogue Input       | Input channel 4 right                                              |

| 32  | IN5L      | Analogue Input       | Input channel 5 left                                               |

| 33  | IN5R      | Analogue Input       | Input channel 5 right                                              |

| 34  | IN6L      | Analogue Input       | Input channel 6 left                                               |

| 35  | IN6R      | Analogue Input       | Input channel 6 right                                              |

| 36  | VREF1C    | Analogue Output      | Positive reference for ADC                                         |

| 37  | VMID1C    | Analogue Output      | Midrail divider decoupling pin for ADC                             |

| 38  | VREF1GND  | Analogue Input       | Ground reference for ADC                                           |

| 39  | VREF2VDD  | Analogue Input       | Positive reference for DACs                                        |

| 40  | VMID2C    | Analogue Output      | Midrail divider decoupling pin for DACs                            |

| 41  | VREF2GND  | Analogue Input       | Ground reference for DACs                                          |

| 42  | AVDD1     | Supply               | Analogue 3.3V supply                                               |

| 43  | AGND1     | Supply               | Analogue 3.3V ground                                               |

| 44  | CIFMODE   | Digital Input        | 2-wire/3-wire mode select                                          |

| 45  | SDOUT     | Digital Output       | Serial Data output for 3-wire readback                             |

| 45  | CS        | Digital Input        | 3-wire serial control interface latch                              |

| 40  | SCLK      | <b>.</b> .           |                                                                    |

|     |           | Digital Input        | Software mode: serial control interface clock signal               |

| 48  | SDA       | Digital Input        | Software mode: bi-directional serial control interface data signal |

PD, Rev 4.2, January 2011

# **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag. MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag. MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                                            | MIN         | MAX          |

|------------------------------------------------------|-------------|--------------|

| Digital supply voltage, DVDD                         | -0.3V       | +4.5V        |

| Analogue supply voltage, AVDD1                       | -0.3V       | +7V          |

| Analogue supply voltage, AVDD2                       | -0.3V       | +15V         |

| Voltage range digital inputs                         | DGND -0.3V  | DVDD + 0.3V  |

| Voltage range analogue inputs                        | AGND – 2.4V | AVDD1 + 2.4V |

| Master Clock Frequency                               |             | 38.462MHz    |

| Ambient temperature (supplies applied)               | -55°C       | +125°C       |

| Storage temperature                                  | -65°C       | +150°C       |

| Pb free package body temperature (reflow 10 seconds) |             | +260°C       |

| Package body temperature (soldering 2 minutes)       |             | +183°C       |

Note:

1. Analogue and digital grounds must always be within 0.3V of each other.

# THERMAL PERFORMANCE

| PARAMETER                                | SYMBOL                | TEST<br>CONDITIONS | MIN | ТҮР | МАХ | UNIT |

|------------------------------------------|-----------------------|--------------------|-----|-----|-----|------|

| Thermal resistance – junction to ambient | $R_{	extsf{	heta}JA}$ |                    |     | TBD |     | °C/W |

| Thermal resistance – junction to case    | $R_{	extsf{	heta}JC}$ |                    |     | TBD |     | °C/W |

Notes:

1. Figures given for package mounted on 4-layer FR4 according to JESD51-7. (No forced air flow is assumed).

2. Thermal performance figures are estimated.

# **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                   | SYMBOL         | TEST CONDITIONS | MIN  | TYP | MAX | UNIT |

|-----------------------------|----------------|-----------------|------|-----|-----|------|

| Digital power supply        | DVDD           |                 | 2.97 | 3.3 | 3.6 | V    |

| Analogue power supply       | AVDD1          |                 | 2.97 | 3.3 | 3.6 | V    |

| Analogue power supply       | AVDD2          |                 | 8.1  | 9   | 9.9 | V    |

| Ground                      | DGND/AGND1/    |                 |      | 0   |     | V    |

|                             | AGND2          |                 |      |     |     |      |

| Operating temperature range | T <sub>A</sub> |                 | -40  |     | +85 | °C   |

#### Notes:

- 1. Digital supply (DVDD) must never be more than 0.3V greater than AVDD1 in normal operation.

- 2. Digital ground (DGND) and analogue grounds (AGND1, AGND2) must never be more than 0.3V apart.

# SUPPLY CURRENT CONSUMPTION

#### **Test Conditions**

AVDD2=9V, AVDD1=DVDD=3.3V, AGND1=AGND2=0V, DGND=0V, T\_A=+25°C, fs=48kHz, MCLK=256fs unless otherwise stated

| PARAMETER                 | SYMBOL                 | TEST CONDITIONS              | MIN | TYP  | MAX | UNIT |

|---------------------------|------------------------|------------------------------|-----|------|-----|------|

| ADC Record (DACs disabled | )                      | · · ·                        |     |      |     |      |

| Digital supply current    | I <sub>DVDD</sub>      |                              |     | 8.6  |     | mA   |

| Analogue supply 1 current | AVDD1                  | fs=48kHz, 256fs<br>Quiescent |     | 9.2  |     | mA   |

| Analogue supply 2 current | I <sub>AVDD2</sub>     | Quiescent                    |     | 0.01 |     | mA   |

| DAC Playback (ADC disable | d, one DAC disabled    | )                            |     |      |     |      |

| Digital supply current    | IDVDD                  |                              |     | 5.5  |     | mA   |

| Analogue supply 1 current | I <sub>AVDD1</sub>     | fs=48kHz, 256fs<br>Quiescent |     | 6.5  |     | mA   |

| Analogue supply 2 current | AVDD2                  |                              |     | 2.0  |     | mA   |

| Digital supply current    | I <sub>DVDD</sub>      | (- 00) U - 050(-             |     | 9.5  |     | mA   |

| Analogue supply 1 current | AVDD1                  | fs=96kHz, 256fs              |     | 7.0  |     | mA   |

| Analogue supply 2 current | AVDD2                  | Quiescent                    |     | 2.0  |     | mA   |

| Digital supply current    | I <sub>DVDD</sub>      | (- 400LLL- 050(-             |     | 10.0 |     | mA   |

| Analogue supply 1 current | AVDD1                  | fs=192kHz, 256fs             |     | 7.0  |     | mA   |

| Analogue supply 2 current | I <sub>AVDD2</sub>     | Quiescent                    |     | 2.0  |     | mA   |

| ADC Record, DAC Playback  | (all circuit blocks er | nabled)                      |     |      |     |      |

| Digital supply current    | IDVDD                  | fa- 40kl k- 050fa            |     | 17.0 |     | mA   |

| Analogue supply 1 current | AVDD1                  | fs=48kHz, 256fs              |     | 20.0 |     | mA   |

| Analogue supply 2 current | AVDD2                  | Quiescent                    |     | 11.0 |     | mA   |

# **ELECTRICAL CHARACTERISTICS**

# **Test Conditions**

AVDD2=9V, AVDD1=DVDD=3.3V, AGND1=AGND2=0V, DGND=0V, T\_A=+25°C, 1kHz signal, fs=48kHz, MCLK=256fs unless otherwise stated

| PARAMETER                                | SYMBOL          | TEST CONDITIONS                       | MIN        | TYP               | MAX        | UNIT   |

|------------------------------------------|-----------------|---------------------------------------|------------|-------------------|------------|--------|

| Digital logic levels                     |                 | -                                     |            | •                 |            |        |

| Input low level                          | V <sub>IL</sub> |                                       |            |                   | 0.3xDVDD   | V      |

| Input high level                         | VIH             |                                       | 0.7xDVDD   |                   |            | V      |

| Output low level                         | V <sub>OL</sub> |                                       |            |                   | 0.1 x DVDD | V      |

| Output high level                        | V <sub>OH</sub> |                                       | 0.9 x DVDD |                   |            | V      |

| Digital input leakage current            |                 |                                       |            | ±0.2              |            | μA     |

| Digital input capacitance                |                 |                                       |            | 5                 |            | pF     |

| Analogue Reference Levels                |                 |                                       | I          |                   |            |        |

| ADC Midrail Voltage                      | VMID1C          |                                       |            | AVDD1/2           |            | V      |

| ADC Buffered Positive                    | VREF1C          |                                       |            | VMID1C            |            | V      |

| Reference Voltage                        |                 |                                       |            |                   |            |        |

| DAC Midrail Voltage                      | VMID2C          |                                       |            | VREF2VDD/2        |            | V      |

| Potential divider resistance             |                 | AVDD1 to VMID1C                       |            | 100               |            | kΩ     |

|                                          |                 | VMID1C to AGND1                       |            |                   |            |        |

|                                          |                 | VREF2VDD to VMID2C                    |            | 19                |            | kΩ     |

|                                          |                 | VMID2C to VREF2GND                    |            | (Note 2)          |            |        |

|                                          |                 | VMID_SEL[1:0] = 01                    |            |                   |            |        |

| Analogue Line Outputs                    |                 |                                       |            |                   |            |        |

| Output signal level (0dB)                |                 |                                       | -10%       | 2.0x<br>AVDD1/3.3 | +10%       | Vrms   |

| Maximum capacitance load                 |                 |                                       |            |                   | 11         | nF     |

| Minimum resistance load                  |                 |                                       | 1          |                   |            | kΩ     |

| Analogue Inputs                          |                 | <u>.</u>                              |            | -                 |            |        |

| Input signal level (0dB)                 |                 |                                       |            | 2.0 x             |            | Maria  |

|                                          |                 |                                       |            | AVDD1/3.3         |            | Vrms   |

| Input impedance                          |                 |                                       |            | 48                |            | kΩ     |

| Input capacitance                        |                 |                                       |            | 5                 |            | pF     |

| DAC Performance (DAC1 to LI              | NEOUT1L/R, DA   | C2 to LINEOUT2L/R)                    |            |                   |            |        |

| Signal to Noise Ratio <sup>1,5</sup>     | SNR             | A-weighted                            | 90         | 100               |            | dB     |

| -                                        |                 | @ fs = 48kHz                          |            |                   |            |        |

|                                          |                 | A-weighted                            |            | 100               |            | dB     |

|                                          |                 | @ fs = 96kHz                          |            |                   |            |        |

|                                          |                 | A-weighted                            |            | 100               |            | dB     |

|                                          |                 | @ fs = 192kHz                         |            |                   |            |        |

| Dynamic Range <sup>2,5</sup>             | DNR             | A-weighted, -60dB full<br>scale input | 90         | 100               |            | dB     |

| Total Harmonic Distortion <sup>3,5</sup> | THD             | 1kHz, 0dBFS                           |            | -87               | -80        | dB     |

|                                          |                 | @ fs = 48kHz                          |            |                   |            |        |

|                                          |                 | 1kHz, 0dBFS                           |            | -86               |            | dB     |

|                                          |                 | @ fs = 96kHz                          |            |                   |            |        |

|                                          |                 | 1kHz, 0dBFS                           |            | -85               |            | dB     |

|                                          |                 | @ fs = 192kHz                         |            | -                 |            | -      |

| Channel Separation <sup>4,5</sup>        |                 | 1kHz                                  |            | 110               |            | dB     |

| Channel Level Matching                   |                 |                                       |            | 0.1               |            | dB     |

| Channel Phase Deviation                  |                 | 1kHz                                  |            | 0.01              |            | Degree |

| Power supply rejection ratio             | PSRR            | 1kHz, 100mVpp                         |            | 50                |            | dB     |

|                                          |                 | 20Hz to 20kHz,<br>100mVpp             |            | 45                |            | dB     |

PD, Rev 4.2, January 2011

# Production Data

# **Test Conditions**

$AVDD2=9V, AVDD1=DVDD=3.3V, AGND1=AGND2=0V, DGND=0V, T_{A}=+25^{\circ}C, 1kHz \ signal, fs=48kHz, MCLK=256 fs \ unless \ otherwise \ stated$

| PARAMETER                                | SYMBOL | TEST CONDITIONS                      | MIN | TYP   | MAX | UNIT   |

|------------------------------------------|--------|--------------------------------------|-----|-------|-----|--------|

| ADC Performance                          |        |                                      |     |       |     |        |

| Signal to Noise Ratio <sup>1,5</sup>     | SNR    | A-weighted, 0dB gain<br>@ fs = 48kHz | 85  | 96    |     | dB     |

|                                          |        | A-weighted, 0dB gain<br>@ fs = 96kHz |     | 98    |     | dB     |

| Dynamic Range <sup>2,5</sup>             | DNR    | A-weighted, -60dB full scale input   | 85  | 96    |     | dB     |

| Total Harmonic Distortion <sup>3,5</sup> | THD    | 1kHz, -1dBFS<br>@ fs = 48kHz         |     | -80   | -70 | dB     |

|                                          |        | 1kHz, -1dBFS<br>@ fs = 96kHz         |     | -78   |     | dB     |

| Channel Separation <sup>4,5</sup>        |        | 1kHz                                 |     | 110   |     | dB     |

| Channel Level Matching                   |        |                                      |     | 0.1   |     | dB     |

| Channel Phase Deviation                  |        | 1kHz                                 |     | 0.01  |     | Degree |

| Power Supply Rejection Ratio             | PSRR   | 1kHz, 100mVpp                        |     | 70    |     | dB     |

|                                          |        | 20Hz to 20kHz,<br>100mVpp            |     | 52    |     | dB     |

| Digital Volume Control                   |        |                                      |     |       |     |        |

| ADC minimum digital volume               |        |                                      |     | -97   |     | dB     |

| ADC maximum digital volume               |        |                                      |     | +30   |     | dB     |

| ADC volume step size                     |        |                                      |     | 0.5   |     | dB     |

| DAC minimum digital volume               |        |                                      |     | -100  |     | dB     |

| DAC maximum digital volume               |        |                                      |     | +12   |     | dB     |

| DAC volume step size                     |        |                                      |     | 0.5   |     | dB     |

| Analogue Volume Control                  |        |                                      |     |       |     |        |

| Minimum gain                             |        |                                      |     | -73.5 |     | dB     |

| Maximum gain                             |        |                                      |     | +6    |     | dB     |

| Step size                                |        |                                      |     | 0.5   |     | dB     |

| Mute attenuation                         |        |                                      |     | 120   |     | dB     |

| Crosstalk                                |        |                                      |     |       |     |        |

| DAC to ADC                               |        | 1kHz signal,                         |     | 100   |     | dB     |

|                                          |        | ADC fs=48kHz,                        |     |       |     |        |

|                                          |        | DAC fs=44.1kHz                       |     |       |     |        |

|                                          |        | 20kHz signal,                        |     | 100   |     | dB     |

|                                          |        | ADC fs=48kHz,                        |     |       |     |        |

|                                          |        | DAC fs=44.1kHz                       |     | ļ     |     |        |

| ADC to DAC                               |        | 1kHz signal,                         |     | 100   |     | dB     |

|                                          |        | ADC fs=48kHz,                        |     |       |     |        |

|                                          |        | DAC fs=44.1kHz                       |     |       |     |        |

|                                          |        | 20kHz signal,                        |     | 100   |     | dB     |

|                                          |        | ADC fs=48kHz,                        |     |       |     |        |

|                                          |        | DAC fs=44.1kHz                       |     |       |     |        |

# TERMINOLOGY

- 1. Signal-to-noise ratio (dBFS) SNR is the difference in level between a reference full scale output signal and the device output with no signal applied. This ratio is also called idle channel noise. (No Auto-zero or Automute function is employed in achieving these results).

- Dynamic range (dBFS) DNR is a measure of the difference in level between the highest and lowest components of a signal. Normally a THD measurement at -60dBFS. The measured signal is then corrected by adding 60dB to the result, e.g. THD @ -60dBFS = -30dB, DNR = 90dB.

- 3. Total Harmonic Distortion (dBFS) THD is the difference in level between a reference full scale output signal and the first seven odd harmonics of the output signal. To calculate the ratio, the fundamental frequency of the output signal is notched out and an RMS value of the next seven odd harmonics is calculated.

- 4. Channel Separation (dB) Also known as Cross-Talk. This is a measure of the amount one channel is isolated from the other. Normally measured by sending a full scale signal down one channel and measuring the other.

- 5. All performance measurements carried out with 20kHz low pass filter, and where noted an A-weighted filter. Failure to use such a filter will result in higher THD and lower SNR and Dynamic Range readings than are found in the Electrical Characteristics. The low pass filter removes out of band noise; although it is not audible it may affect dynamic specification values.

#### Notes:

- 1. All minimum and maximum values are subject to change.

- 2. This resistance is selectable using VMID\_SEL[1:0] see Figure 47 for full details.

- 3. See p81 for details of extended input impedance configuration.

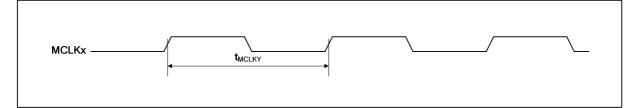

# MASTER CLOCK TIMING

# Figure 1 MCLK Timing

#### Test Conditions

| AVDD1, DVDD = $3.3V$ , AVDD2 = $9V$ , AGND1, AGND2, DGND = $0V$ , $T_A = +25^{\circ}C$ |                    |       |     |       |      |  |  |

|----------------------------------------------------------------------------------------|--------------------|-------|-----|-------|------|--|--|

| PARAMETER                                                                              | SYMBOL             | MIN   | TYP | MAX   | UNIT |  |  |

| Master Clock Timing Information                                                        |                    |       |     |       |      |  |  |

| MCLK System clock cycle time                                                           | t <sub>MCLKY</sub> | 27    |     | 120   | ns   |  |  |

| MCLK Duty cycle                                                                        |                    | 40:60 |     | 60:40 | %    |  |  |

| MCLK Period Jitter                                                                     |                    |       |     | 200   | ps   |  |  |

| MCLK Rise/Fall times                                                                   |                    |       |     | 10    | ns   |  |  |

Table 1 Master Clock Timing Requirements

# **RESET TIMING**

| RESET |  |

|-------|--|

|       |  |

# Figure 2 RESET Timing

**Test Conditions**

AVDD1, DVDD = 3.3V, AVDD2 = 9V, AGND1, AGND2, DGND = 0V,  $T_A = +25^{\circ}C$

| PARAMETER                | SYMBOL             | MIN | TYP | МАХ | UNIT |

|--------------------------|--------------------|-----|-----|-----|------|

| RESET Timing Information |                    |     |     |     |      |

| RESET pulsewidth low     | T <sub>RESET</sub> | 10  |     |     | ns   |

Table 2 RESET Timing Requirements

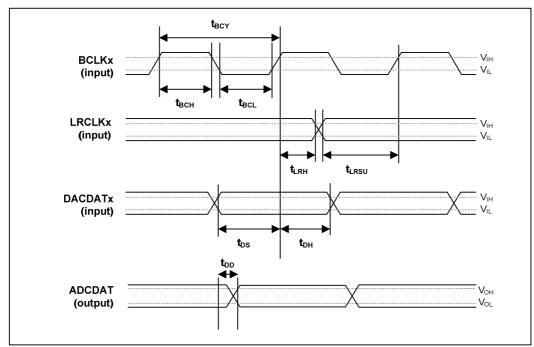

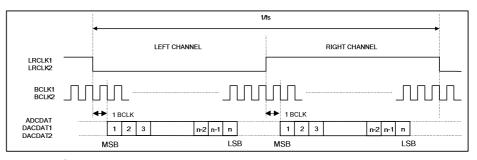

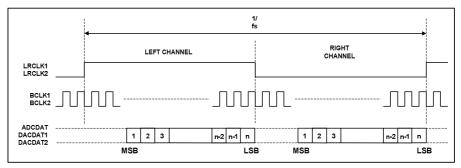

Figure 3 Slave Mode Digital Audio Data Timing

#### **Test Conditions**

AVDD1, DVDD = 3.3V, AVDD2 = 9V, AGND1, AGND2, DGND = 0V, T<sub>A</sub> =  $+25^{\circ}C$ , Slave Mode, fs = 48kHz, MCLK = 256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                                | SYMBOL            | MIN | ТҮР | MAX | UNIT |

|----------------------------------------------------------|-------------------|-----|-----|-----|------|

| Audio Data Input Timing Information                      |                   |     |     |     |      |

| BCLK cycle time                                          | t <sub>BCY</sub>  | 80  |     |     | ns   |

| BCLK pulse width high                                    | t <sub>всн</sub>  | 30  |     |     | ns   |

| BCLK pulse width low                                     | t <sub>BCL</sub>  | 30  |     |     | ns   |

| LRCLK set-up time to BCLK rising edge                    | t <sub>LRSU</sub> | 22  |     |     | ns   |

| LRCLK hold time from BCLK rising edge                    | t <sub>LRH</sub>  | 25  |     |     | ns   |

| DACDAT (input) hold time from LRCLK rising edge          | t <sub>DH</sub>   | 25  |     |     | ns   |

| DACDAT (input) set-up time to BCLK rising edge           | t <sub>DS</sub>   | 25  |     |     | ns   |

| ADCDAT (output) propagation delay from BCLK falling edge | t <sub>DD</sub>   | 4   |     | 16  | ns   |

Table 3 Slave Mode Audio Interface Timing

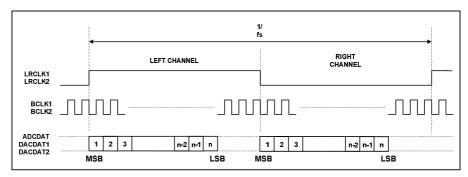

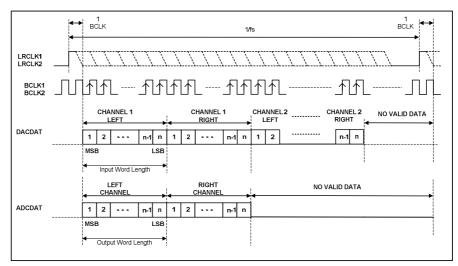

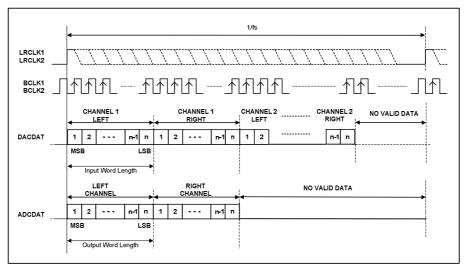

# **DIGITAL AUDIO INTERFACE TIMING – MASTER MODE**

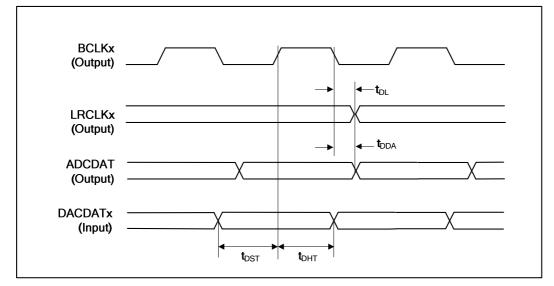

Figure 4 Master Mode Digital Audio Data Timing

#### **Test Conditions**

AVDD1, DVDD = 3.3V, AVDD2 = 9V, AGND1, AGND2, DGND = 0V,  $T_A = +25^{\circ}C$ , Slave Mode, fs = 48kHz, MCLK = 256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                                | SYMBOL           | MIN | TYP | MAX | UNIT |

|----------------------------------------------------------|------------------|-----|-----|-----|------|

| Audio Data Input Timing Information                      |                  |     |     |     |      |

| LRCLK propagation delay from BCLK falling edge           | t <sub>DL</sub>  | 4   |     | 16  | ns   |

| ADCDAT (output) propagation delay from BCLK falling edge | t <sub>DDA</sub> | 4   |     | 16  | ns   |

| DACDAT (input) setup time to BCLK rising edge            | t <sub>DST</sub> | 22  |     |     | ns   |

| DACDAT (input) hold time to BCLK rising edge             | t <sub>DHT</sub> | 25  |     |     | ns   |

Table 4 Master Mode Audio Interface Timing

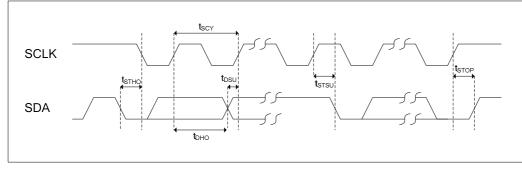

# **CONTROL INTERFACE TIMING – 2-WIRE MODE**

Figure 5 Control Interface Timing – 2-Wire Serial Control Mode

#### **Test Conditions**

AVDD1, DVDD = 3.3V, AVDD2 = 9V, AGND1, AGND2, DGND = 0V,  $T_A$  = +25°C, Slave Mode, fs = 48kHz, MCLK = 256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                     | SYMBOL            | MIN   | TYP | MAX   | UNIT |  |  |  |  |

|-----------------------------------------------|-------------------|-------|-----|-------|------|--|--|--|--|

| Program Register Input Information            |                   |       |     |       |      |  |  |  |  |

| SCLK pulse cycle time                         | t <sub>SCY</sub>  | 2500  |     |       | ns   |  |  |  |  |

| SCLK duty cycle                               |                   | 40/60 |     | 60/40 | %    |  |  |  |  |

| SCLK frequency                                |                   |       |     | 400   | kHz  |  |  |  |  |

| Hold Time (Start Condition)                   | t <sub>sтно</sub> | 600   |     |       | ns   |  |  |  |  |

| Setup Time (Start Condition)                  | t <sub>stsu</sub> | 600   |     |       | ns   |  |  |  |  |

| Data Setup Time                               | t <sub>DSU</sub>  | 100   |     |       | ns   |  |  |  |  |

| SDA, SCLK Rise Time                           |                   |       |     | 300   | ns   |  |  |  |  |

| SDA, SCLK Fall Time                           |                   |       |     | 300   | ns   |  |  |  |  |

| Setup Time (Stop Condition)                   | t <sub>STOP</sub> | 600   |     |       | ns   |  |  |  |  |

| Data Hold Time                                | t <sub>DHO</sub>  |       |     | 900   | ns   |  |  |  |  |

| Pulse width of spikes that will be suppressed | t <sub>ps</sub>   | 2     |     | 8     | ns   |  |  |  |  |

Table 5 Control Interface Timing – 2-Wire Serial Control Mode

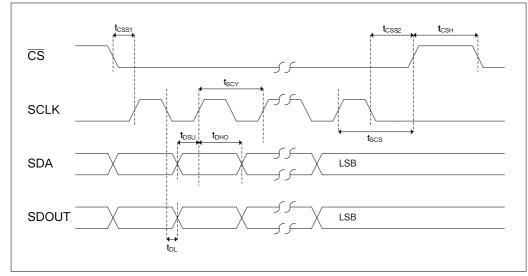

# **CONTROL INTERFACE TIMING – 3-WIRE MODE**

Figure 6 Control Interface Timing – 3-Wire Serial Control Mode

# **Test Conditions**

AVDD1, DVDD = 3.3V, AVDD2 = 9V, AGND1, AGND2, DGND = 0V, T<sub>A</sub> =  $+25^{\circ}C$ , Slave Mode, fs = 48kHz, MCLK = 256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                      | SYMBOL            | MIN   | TYP | MAX   | UNIT |

|------------------------------------------------|-------------------|-------|-----|-------|------|

| Program Register Input Information             |                   |       |     |       |      |

| SCLK rising edge to CS rising edge             | t <sub>scs</sub>  | 80    |     |       | ns   |

| SCLK pulse cycle time                          | tscy              | 160   |     |       | ns   |

| SCLK duty cycle                                |                   | 40/60 |     | 60/40 | %    |

| SDA to SCLK set-up time                        | t <sub>DSU</sub>  | 20    |     |       | ns   |

| SDA hold time from SCLK rising edge            | t <sub>DHO</sub>  | 40    |     |       | ns   |

| SDOUT propagation delay from SCLK falling edge | t <sub>DL</sub>   |       |     | 5     | ns   |

| CS pulse width high                            | t <sub>CSH</sub>  | 40    |     |       | ns   |

| CS falling to SCLK rising                      | t <sub>CSS1</sub> | 40    |     |       | ns   |

| SCLK failing to CS rising                      | t <sub>CSS2</sub> | 40    |     |       | ns   |

| Pulse width of spikes that will be suppressed  | t <sub>ps</sub>   | 2     |     | 8     | ns   |

Table 6 Control Interface Timing – 3-Wire Serial Control Mode

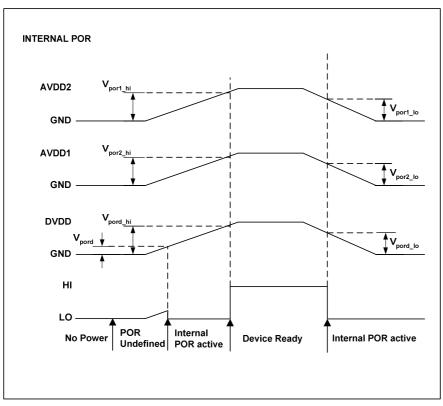

# **POWER ON RESET (POR)**

#### Figure 1 Power Supply Timing Requirements

#### **Test Conditions**

$\begin{array}{l} \mathsf{DVDD}=3.3\mathsf{V}, \ \mathsf{AVDD1}=3.3\mathsf{V}, \ \mathsf{AVDD2}=9\mathsf{V} \ \mathsf{DGND}=\mathsf{AGND1}=\mathsf{AGND2}=0\mathsf{V}, \ \mathsf{T}_{\mathsf{A}}=+25^{\mathrm{o}}\mathsf{C}, \ \mathsf{T}_{\mathsf{A}\_max}=+125^{\mathrm{o}}\mathsf{C}, \ \mathsf{T}_{\mathsf{A}\_min}=-25^{\mathrm{o}}\mathsf{C}\\ \mathsf{AVDD1}_{max}=\mathsf{DVDD}_{max}=3.63\mathsf{V}, \ \mathsf{AVDD1}_{min}=\mathsf{DVDD}_{mim}=2.97\mathsf{V}\\ \mathsf{AVDD2}_{max}=9.9\mathsf{V}, \ \mathsf{AVDD2}_{min}=8.1\mathsf{V} \end{array}$

| PARAMETER                                        | SYMBOL                                | TEST CONDITIONS    | MIN  | TYP  | MAX  | UNIT |  |  |  |

|--------------------------------------------------|---------------------------------------|--------------------|------|------|------|------|--|--|--|

| Power Supply Input Timing                        | Power Supply Input Timing Information |                    |      |      |      |      |  |  |  |

| VDD level to POR defined<br>(DVDD rising)        | V <sub>pord</sub>                     | Measured from DGND | 0.27 | 0.36 | 0.60 | V    |  |  |  |

| VDD level to POR rising edge (DVDD rising)       | V <sub>pord_hi</sub>                  | Measured from DGND | 1.34 | 1.88 | 2.32 | V    |  |  |  |

| VDD level to POR falling edge (DVDD falling)     | Vpord_lo                              | Measured from DGND | 1.32 | 1.86 | 2.30 | V    |  |  |  |

| VDD level to POR rising edge (AVDD1 rising)      | Vpor1_hi                              | Measured from DGND | 1.65 | 1.68 | 1.85 | V    |  |  |  |

| VDD level to POR falling<br>edge (AVDD1 falling) | Vpor1_lo                              | Measured from DGND | 1.63 | 1.65 | 1.83 | V    |  |  |  |

| VDD level to POR rising edge (AVDD2 rising)      | V <sub>por2_hi</sub>                  | Measured from DGND | 1.80 | 1.86 | 2.04 | V    |  |  |  |

| VDD level to POR falling edge (AVDD2 falling)    | Vpor2_lo                              | Measured from DGND | 1.76 | 1.8  | 2.02 | V    |  |  |  |

Table 7 Power on Reset

# **DEVICE DESCRIPTION**

# INTRODUCTION

The WM8595 is a high performance multi-channel audio CODEC with 2Vrms line level inputs and outputs and flexible digital input / output switching. The device comprises a 24-bit stereo ADC, two 24-bit stereo DACs with independent sampling rates and digital volume control, two stereo PGAs in the output path, a flexible digital audio interface multiplexer, a flexible analogue input multiplexer. Analogue inputs and outputs are all at 2Vrms line level, minimising external component count.

The DACs can operate from independent left/right clocks, bit clocks and master clocks with independent data inputs. Alternatively, the DACs can be synchronised to use the same clocks with independent data inputs.

The ADC uses a separate left/right clock, bit clock and master clock, allowing independent recording and playback in audio applications. The ADC audio interface can be configured to operate in either master or slave clocking mode. In master mode, left/right clocks and bit clocks are all outputs. In slave mode, left/right clocks and bit clocks are all inputs.

The ADC includes digital gain control, allowing signals to be gained and attenuated between +30dB and -97dB in 0.5dB steps.

The DACs include independent digital volume control, which is adjustable between +12dB and -100 dB in 0.5dB steps. The DACs can be configured to output stereo audio data and a range of mono audio options.

The input analogue multiplexer accepts six stereo line level inputs at up to 2Vrms, and allows any stereo input to be routed to the input of the ADC.

The output PGAs have optional zero cross functionality, with gain adjustable between +6dB and - 73.5dB in 0.5dB steps, and configurable soft ramp rate. Analogue audio is output at 2Vrms line level.

The digital audio interface multiplexer allows flexible routing of the digital signals internal to the device between the independent ADC, DAC1 and DAC2 audio interfaces from the digital audio ports. By integrating this functionality into the WM8595, the external component count and board space normally required to switch between various digital audio sources can be significantly reduced.

Control of the internal functionality of the device is by 2-wire or 3-wire serial control interface with readback. The interface may be asynchronous to the audio data interface as control data will be resynchronised to the audio processing internally. In addition, control of mute, emergency shutdown and reset may also be achieved by pin control.

Operation using system clocks of 128fs, 192fs, 256fs, 384fs, 512fs, 768fs or 1152fs is provided. ADC and DACs may be clocked independently. Sampling rates from 32kHz to 192kHz are supported for both DACs provided the appropriate master clocks are input. Sampling rates from 32kHz to 96kHz are supported for the ADC provided the appropriate master clock is input.

The audio data interface supports right justified, left justified, and I2S interface formats along with a highly flexible DSP serial port interface format.

# **CONTROL INTERFACE**

Control of the WM8595 is achieved by a 2-wire SM-bus-compliant or 3-wire SPI compliant serial interface with readback. Software interface mode is selected using the CIFMODE pin as shown in Table 8 below:

| CIFMODE (PIN 44) | INTERFACE FORMAT |

|------------------|------------------|

| Low              | 2 wire           |

| High             | 3 wire           |

Table 8 Control Interface Mode Selection

# 2-WIRE (SM-BUS COMPATIBLE) SERIAL CONTROL INTERFACE MODE

Many devices can be controlled by the same bus, and each device has a unique 7-bit address.

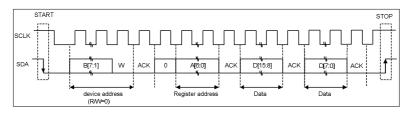

#### **REGISTER WRITE**

The controller indicates the start of data transfer with a high to low transition on SDA while SCLK remains high. This indicates that a device address and data will follow. All devices on the 2-wire bus respond to the start condition and shift in the next eight bits on SDA (7-bit address and read/write bit, MSB first). If the device address received matches the address of the WM8595, the WM8595 responds by pulling SDA low on the next clock pulse (ACK). If the address is not recognised, the WM8595 returns to the idle condition and waits for a new start condition with valid address.

When the WM8595 has acknowledged a correct address, the controller sends the first byte of control data (B23 to B16, i.e. the WM8595 register address). The WM8595 then acknowledges the first data byte by pulling SDA low for one SCLK pulse. The controller then sends a second byte of control data (B15 to B8, i.e. the first 8 bits of register data), and the WM8595 acknowledges again by pulling SDA low for one SCLK pulse. Finally, the controller sends a third byte of control data (B7 to B0, i.e. the final 8 bits of register data), and the WM8595 acknowledges again by pulling SDA low for one SCLK pulse.

The transfer of data is complete when there is a low to high transition on SDA while SCLK is high. After receiving a complete address and data sequence the WM8595 returns to the idle state and waits for another start condition. If a start or stop condition is detected out of sequence at any point during data transfer (i.e. SDA changes while SCLK is high), the WM8595 reverts to the idle condition.

The WM8595 device 2-wire write address is 34h (0110100) or 36h (0110110), selectable by control of CS.

| CS (PIN 46) | 2-WIRE BUS ADDRESS (B[7:1]) |  |  |

|-------------|-----------------------------|--|--|

| 0           | 34h (011010)                |  |  |

| 1           | 36h (011011)                |  |  |

Table 9 2-Wire Control Interface Bus Address Selection

Figure 7 2-Wire Write Protocol

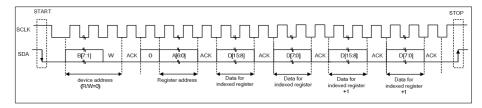

#### AUTO-INCREMENT REGISTER WRITE

It is possible to write to multiple consecutive registers using the auto-increment feature. When AUTO\_INC is set, the register write protocol follows the method shown in Figure 8

. As with normal register writes, the controller indicates the start of data transfer with a high to low transition on SDA while SCLK remains high, and all devices on the bus receive the device address.

When the WM8595 has acknowledged a correct address, the controller sends the first byte of control data (A6 to A0, i.e. the WM8595 initial register address). The WM8595 then acknowledges the first control data byte by pulling SDA low for one SCLK pulse. The controller then sends a byte of register data. The WM8595 acknowledges the first byte of register data, auto-increments the register address to be written to, and waits for the next byte of register data. Subsequent bytes of register data can be written to consecutive registers of the WM8595 without setting up the device and register address.

The transfer of data is complete when there is a low to high transition on SDA while SCLK is high.

Figure 8 2-Wire Auto-Increment Register Write

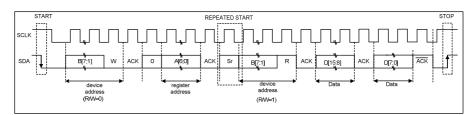

#### **REGISTER READBACK**

The WM8595 allows readback of all registers with data output on the bidirectional SDA pin. The protocol is similar to that used to write to the device. The controller will issue the device address followed by a write bit, and the register index will then be passed to the WM8595.

At this point the controller will issue a repeated start condition and resend the device address along with a read bit. The WM8595 will acknowledge this and the WM8595 will become a slave transmitter.

The WM8595 will place the data from the indexed register onto SDA MSB first. When the controller receives the first byte of data, it acknowledges it. When the controller receives the second and final byte of data it will not acknowledge receipt of the data indicating that it will resume master transmitter control of SDA. The controller will then issue a stop command completing the read cycle.

Figure 9 2-wire Read Protocol

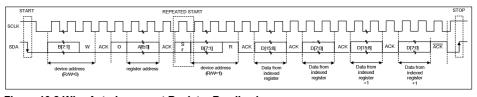

#### AUTO-INCREMENT REGISTER READBACK

It is possible to read from multiple consecutive registers in continuous readback mode. Continuous readback mode is selected by setting AUTO\_INC. In continuous readback mode, the WM8595 will return the indexed register first, followed by consecutive registers in increasing index order until the controller issues a stop sequence.

Figure 10 2-Wire Auto-Increment Register Readback

# 3-WIRE (SPI COMPATIBLE) SERIAL CONTROL INTERFACE MODE

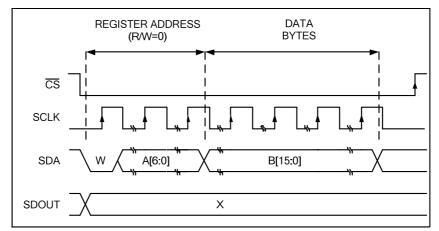

# **REGISTER WRITE**

SDA is used for the program data, SCLK is used to clock in the program data and CS is use to latch in the program data. SDA is sampled on the rising edge of SCLK. The 3-wire interface write protocol is shown in Figure 11.

Figure 11 3-Wire Serial Interface Write Protocol

- W indicates write operation.

- A[6:0] is the register index.

- B[15:0] is the data to be written to the register indexed.

- CS is edge sensitive the data is latched on the rising edge of /CS.

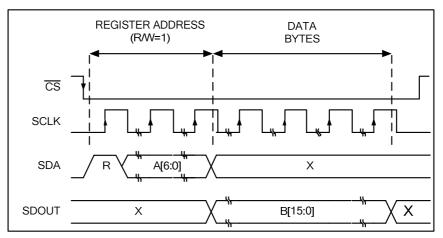

#### **REGISTER READ-BACK**

The read-only status registers can be read back via the SDOUT pin. Read Back is enabled when the R/W bit is high. The data can then be read by writing to the appropriate register address, to which the device will respond with data.

Figure 12 3-Wire Serial Interface Readback Protocol

#### **REGISTER RESET**

Any write to register R0 (00h) will reset the WM8595. All register bits are reset to their default values.

#### **DEVICE ID AND REVISION**

Reading from register R0 returns the device ID. Reading from register R1 returns the device revision number.

| REGISTER<br>ADDRESS | BIT  | LABEL               | DEFAULT              | DESCRIPTION                                                                                                                                    |

|---------------------|------|---------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| R0<br>DEVICE ID     | 15:0 | DEVICE_ID<br>[15:0] | 10000101<br>10010101 | Device ID<br>A read of this register will return the device                                                                                    |

| 00h                 |      |                     |                      | ID, 0x8595.                                                                                                                                    |

| R1                  | 7:0  | REVNUM              | N/A                  | Device Revision                                                                                                                                |

| REVISION<br>01h     |      | [7:0]               |                      | A read of this register will return the device<br>revision number. This number is sequentially<br>incremented if the device design is updated. |

Table 10 Device ID and Revision Number

# **DIGITAL AUDIO DATA FORMATS**

The WM8595 supports a range of common audio interface formats:

- I<sup>2</sup>S

- Left Justified (LJ)

- Right Justified (RJ)

- DSP Mode A

- DSP Mode B

All formats send the MSB first and support word lengths of 16, 20, 24 and 32 bits, with the exception of 32 bit RJ mode, which is not supported.

Audio data for each stereo channel is time multiplexed with the interface's left/right clock indicating whether the left or right channel is present. The left/right clock is also used as a timing reference to indicate the beginning or end of the data words.

In LJ, RJ and I<sup>2</sup>S modes, the minimum number of bit clock periods per left/right clock period is two times the selected word length. The left/right clock must be high for a minimum of bit clock periods equivalent to the word length, and low for the same period. For example, for a word length of 24 bits, the left/right clock must be high for a minimum of 24 bit clock periods and low for a minimum of 24 bit clock periods. Any mark to space ratio is acceptable for the left/right clock provided these requirements are met.

In DSP modes A and B, left and right channels must be time multiplexed and input on DACDAT. LRCLK is used as a frame synchronisation signal to identify the MSB of the first input word. The minimum number of bit clock periods per left/right clock period is two times the selected word length. Any mark to space ratio is acceptable for the left/right clock provided the rising edge is correctly positioned.

# **I2S MODE**

In I<sup>2</sup>S mode, the MSB of input data is sampled on the second rising edge of bit clock following a left/right clock transition. The MSB of output data changes on the first falling edge of bit clock following a left/right clock transition, and may be sampled on the next rising edge of bit clock. Left/right clocks are low during the left channel audio data samples and high during the right channel audio data samples.

Figure 13 I2S Mode Timing

#### LEFT JUSTIFIED (LJ) MODE

In LJ mode, the MSB of the input data is sampled by the WM8595 on the first rising edge of bit clock following a left/right clock transition. The MSB of output data changes on the same falling edge of bit clock as left/right clock and may be sampled on the next rising edge of bit clock. Left/right clock is high during the left channel audio data samples and low during the right channel audio data samples.

Figure 14 LJ Mode Timing

#### **RIGHT JUSTIFIED (RJ) MODE**

In RJ mode the LSB of input data is sampled on the rising edge of bit clock preceding a left/right clock transition. The LSB of output data changes on the falling edge of bit clock preceding a left/right clock transition, and may be sampled on the next rising edge of bit clock. Left/right clock is high during the left channel audio data samples and low during the right channel audio data samples.

Figure 15 RJ Mode Timing

# DSP MODE A

In DSP Mode A, the MSB of channel 1 left data input is sampled on the second rising edge of bit clock following a left/right clock rising edge. Channel 1 right data then follows. The MSB of output data changes on the first falling edge of bit clock following a left/right clock transition and may be sampled on the rising edge of bit clock. The right channel data is contiguous with the left channel data.

Figure 16 DSP Mode A Timing

## DSP MODE B

In DSP Mode B, the MSB of channel 1 left data input is sampled on the first bit clock rising edge following a left/right clock rising edge. Channel 1 right data then follows. The MSB of output data changes on the same falling edge of BCLK as the low to high left/right clock transition and may be sampled on the rising edge of bit clock. The right channel data is contiguous with the left channel data.

Figure 17 DSP Mode B Timing

# DIGITAL AUDIO INTERFACE CONTROL

The control of the audio interface formats is achieved by register write. Dynamically changing the audio data format may cause erroneous operation and is not recommended.

Interface timing is such that the input data and left/right clock are sampled on the rising edge of the interface bit clock. Output data changes on the falling edge of the interface bit clock. By setting the appropriate bit clock and left/right clock polarity bits, the WM8595 ADC and DACs can sample data on the opposite clock edges.

The control of audio interface formats and clock polarities is summarised in Table 11.

| REGISTER<br>ADDRESS | BIT | LABEL    | DEFAULT | DESCRIPTION                                                       |

|---------------------|-----|----------|---------|-------------------------------------------------------------------|

| R2                  | 1:0 | DAC1_    | 10      | DAC1 Audio Interface Format                                       |

| DAC1_CTRL1          |     | FMT[1:0] |         | 00 = Right Justified                                              |

| 02h                 |     |          |         | 01 = Left Justified                                               |

|                     |     |          |         | 10 = I <sup>2</sup> S                                             |

|                     |     |          |         | 11 = DSP                                                          |

|                     | 3:2 | DAC1_    | 10      | DAC1 Audio Interface Word Length                                  |

|                     |     | WL[1:0]  |         | 00 = 16-bit                                                       |

|                     |     |          |         | 01 = 20-bit                                                       |

|                     |     |          |         | 10 = 24-bit                                                       |

|                     |     |          |         | 11 = 32-bit (not available in Right Justified mode)               |

|                     | 4   | DAC1_BCP | 0       | DAC1 BCLK Polarity                                                |

|                     |     |          |         | 0 = DACBCLK not inverted - data latched on<br>rising edge of BCLK |

|                     |     |          |         | 1 = DACBCLK inverted - data latched on<br>falling edge of BCLK    |

# Production Data

# WM8595

| REGISTER<br>ADDRESS | BIT | LABEL    | DEFAULT | DESCRIPTION                                                       |

|---------------------|-----|----------|---------|-------------------------------------------------------------------|

|                     | 5   | DAC1 LRP | 0       | DAC1 LRCLK Polarity                                               |

|                     |     | _        |         | 0 = DACLRCLK not inverted                                         |

|                     |     |          |         | 1 = DACLRCLK inverted                                             |

| R7                  | 1:0 | DAC2_    | 10      | DAC2 Audio Interface Format                                       |

| DAC2_CTRL1          |     | FMT[1:0] |         | 00 = Right Justified                                              |

| 07h                 |     |          |         | 01 = Left Justified                                               |

|                     |     |          |         | $10 = I^2 S$                                                      |

|                     |     |          |         | 11 = DSP                                                          |

|                     | 3:2 | DAC2_    | 10      | DAC2 Audio Interface Word Length                                  |

|                     |     | WL[1:0]  |         | 00 = 16-bit                                                       |

|                     |     |          |         | 01 = 20-bit                                                       |

|                     |     |          |         | 10 = 24-bit                                                       |

|                     |     |          |         | 11 = 32-bit (not available in Right Justified                     |

|                     |     |          |         | mode)                                                             |

|                     | 4   | DAC2_BCP | 0       | DAC2 BCLK Polarity                                                |

|                     |     |          |         | 0 = DACBCLK not inverted - data latched on<br>rising edge of BCLK |

|                     |     |          |         | 1 = DACBCLK inverted - data latched on<br>falling edge of BCLK    |

|                     | 5   | DAC2_LRP | 0       | DAC2 LRCLK Polarity                                               |

|                     |     |          |         | 0 = DACLRCLK not inverted                                         |

|                     |     |          |         | 1 = DACLRCLK inverted                                             |

| R13                 | 1:0 | ADC_     | 10      | ADC Audio Interface Format                                        |

| ADC_CTRL1           |     | FMT[1:0] |         | 00 = Right Justified                                              |

| 0Dh                 |     |          |         | 01 = Left Justified                                               |

|                     |     |          |         | $10 = I^2 S$                                                      |

|                     |     |          |         | 11 = DSP                                                          |

|                     | 3:2 | ADC_     | 10      | ADC Audio Interface Word Length                                   |

|                     |     | WL[1:0]  |         | 00 = 16-bit                                                       |

|                     |     |          |         | 01 = 20-bit                                                       |

|                     |     |          |         | 10 = 24-bit                                                       |

|                     |     |          |         | 11 = 32-bit (not available in Right Justified mode)               |

|                     | 4   | ADC_BCP  | 0       | ADC BCLK Polarity                                                 |

|                     |     |          |         | 0 = ADCBCLK not inverted - data latched on<br>rising edge of BCLK |

|                     |     |          |         | 1 = ADCBCLK inverted - data latched on<br>falling edge of BCLK    |

|                     | 5   | ADC LRP  | 0       | ADC LRCLK Polarity                                                |

|                     | Ŭ   |          | Ŭ       | 0 = ADCLRCLK not inverted                                         |

|                     |     |          |         | 1 = ADCLRCLK inverted                                             |

Table 11 Audio Interface Control