Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 24-bit, 192kHz Stereo CODEC with 5 Channel I/P Multiplexer

# **DESCRIPTION**

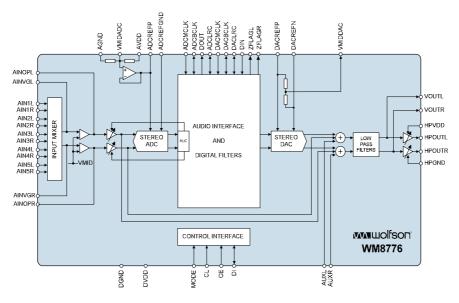

The WM8776 is a high performance, stereo audio CODEC with five channel input selector. The WM8776 is ideal for surround sound processing applications for home hi-fi, DVD-RW and other audio visual equipment.

A stereo 24-bit multi-bit sigma delta ADC is used with a five stereo channel input mixer. Each ADC channel has programmable gain control with automatic level control. Digital audio output word lengths from 16-32 bits and sampling rates from 32kHz to 96kHz are supported.

A stereo 24-bit multi-bit sigma delta DAC is used with digital audio input word lengths from 16-32 bits and sampling rates from 32kHz to 192kHz. The DAC has an input mixer allowing an external analogue signal to be mixed with the DAC signal. There are also Headphone and line outputs, with volume controls for the headphones.

The WM8776 supports fully independent sample rates for the ADC and DAC. The audio data interface supports I<sup>2</sup>S, left justified, right justified and DSP formats.

The device is controlled in software via a 2 or 3 wire serial interface, selected by the MODE pin, which provides access to all features including channel selection, volume controls, mutes, and de-emphasis facilities.

The device is available in a 48-pin TQFP package.

# **BLOCK DIAGRAM**

### **FEATURES**

- Audio Performance

- 108dB SNR ('A' weighted @ 48kHz) DAC

- 102dB SNR ('A' weighted @ 48kHz) ADC

- DAC Sampling Frequency: 32kHz 192kHz

- ADC Sampling Frequency: 32kHz 96kHz

- Five stereo ADC inputs with analogue gain adjust from +24dB to -21dB in 0.5dB steps

- Programmable Limiter or Automatic Level Control (ALC)

- Stereo DAC with independent analogue and digital volume controls

- Stereo Headphone and Line Output

- 3-Wire SPI Compatible or 2-Wire Software Serial Control Interface

- · Master or Slave Clocking Mode

- Programmable Audio Data Interface Modes

- I<sup>2</sup>S. Left. Right Justified or DSP

- 16/20/24/32 bit Word Lengths

- Analogue Bypass Path Feature

- Selectable AUX input to the volume controls

- 2.7V to 5.5V Analogue, 2.7V to 3.6V Digital supply Operation

## **APPLICATIONS**

- Surround Sound AV Processors and Hi-Fi systems

- DVD-RW

# **TABLE OF CONTENTS**

| DESCRIPTION                                            | 1            |

|--------------------------------------------------------|--------------|

| FEATURES                                               | 1            |

| APPLICATIONS                                           | 1            |

| BLOCK DIAGRAM                                          | 1            |

| TABLE OF CONTENTS                                      | 2            |

| PIN CONFIGURATION                                      | 3            |

| ORDERING INFORMATION                                   | 3            |

| PIN DESCRIPTION                                        |              |

| ABSOLUTE MAXIMUM RATINGS                               |              |

| ELECTRICAL CHARACTERISTICS                             |              |

| TERMINOLOGY                                            | _            |

| MASTER CLOCK TIMING                                    | 9            |

| DIGITAL AUDIO INTERFACE – MASTER MODE                  | . 10         |

| DIGITAL AUDIO INTERFACE - SLAVE MODE                   | . 11         |

| 3-WIRE MPU INTERFACE TIMING                            | . 12         |

| CONTROL INTERFACE TIMING – 2-WIRE MODE                 |              |

| INTERNAL POWER ON RESET CIRCUIT                        |              |

| DEVICE DESCRIPTION                                     |              |

| INTRODUCTION                                           |              |

| AUDIO DATA SAMPLING RATES                              |              |

| ZERO DETECT                                            | . 18         |

| POWERDOWN MODES                                        |              |

| DIGITAL AUDIO INTERFACE                                |              |

| CONTROL INTERFACE OPERATIONCONTROL INTERFACE REGISTERS |              |

| LIMITER / AUTOMATIC LEVEL CONTROL (ALC)                | . ZO<br>. 21 |

| REGISTER MAP                                           | . 54<br>41   |

| DIGITAL FILTER CHARACTERISTICS                         |              |

| DAC FILTER RESPONSES                                   | _            |

| ADC FILTER RESPONSES                                   |              |

| ADC HIGH PASS FILTER                                   |              |

| DIGITAL DE-EMPHASIS CHARACTERISTICS                    | . 52         |

| APPLICATIONS INFORMATION                               |              |

| EXTERNAL CIRCUIT CONFIGURATION                         |              |

| RECOMMENDED EXTERNAL COMPONENTS                        |              |

| PACKAGE DIMENSIONS                                     | .56          |

| PACKAGE DIMENSIONS                                     | .56          |

| IMPORTANT NOTICE                                       | .57          |

| ADDRESS:                                               | . 57         |

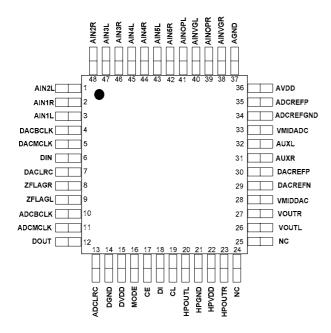

# **PIN CONFIGURATION**

# **ORDERING INFORMATION**

| DEVICE        | TEMPERATURE<br>RANGE | PACKAGE                                 | MOISTURE<br>SENSITIVITY LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|---------------|----------------------|-----------------------------------------|-------------------------------|-------------------------------|

| WM8776SEFT/V  | -25 to +85°C         | 48-pin TQFP<br>(Pb-free)                | MSL2<br>(drybagged)           | 260°C                         |

| WM8776SEFT/RV | -25 to +85°C         | 48-pin TQFP<br>(Pb-free, tape and reel) | MSL2<br>(drybagged)           | 260°C                         |

Note:

Reel quantity = 2,200

# **PIN DESCRIPTION**

| PIN | NAME      | TYPE                 | DESCRIPTION                                                          |

|-----|-----------|----------------------|----------------------------------------------------------------------|

| 1   | AIN2L     | 1                    | Channel 2 left input multiplexor virtual ground                      |

|     |           | Analogue Input       | 1 1                                                                  |

| 2   | AIN1R     | Analogue Input       | Channel 1 right input multiplexor virtual ground                     |

| 3   | AIN1L     | Analogue Input       | Channel 1 left input multiplexor virtual ground                      |

| 4   | DACBCLK   | Digital input/output | DAC audio interface bit clock                                        |

| 5   | DACMCLK   | Digital input        | Master DAC clock; 256, 384, 512 or 768fs (fs = word clock frequency) |

| 6   | DIN       | Digital Input        | DAC data input                                                       |

| 7   | DACLRC    | Digital input/output | DAC left/right word clock                                            |

| 8   | ZFLAGR    | Open Drain output    | DAC Right Zero Flag output (external pull-up resistor required)      |

| 9   | ZFLAGL    | Open Drain output    | DAC Left Zero Flag output (external pull-up resistor required)       |

| 10  | ADCBCLK   | Digital input/output | ADC audio interface bit clock                                        |

| 11  | ADCMCLK   | Digital input        | ADC audio interface master clock                                     |

| 12  | DOUT      | Digital output       | ADC data output                                                      |

| 13  | ADCLRC    | Digital input/output | ADC left/right word clock                                            |

| 14  | DGND      | Supply               | Digital negative supply                                              |

| 15  | DVDD      | Supply               | Digital positive supply                                              |

| 16  | MODE      | Digital input        | Control interface mode select                                        |

| 17  | CE        | Digital input        | Serial interface Latch signal                                        |

| 18  | DI        | Digital input        | Serial interface data                                                |

| 19  | CL        | Digital input        | Serial interface clock                                               |

| 20  | HPOUTL    | Analogue Output      | Headphone left channel output                                        |

| 21  | HPGND     | Supply               | Headphone negative supply                                            |

| 22  | HPVDD     | Supply               | Headphone positive supply                                            |

| 23  | HPOUTR    | Analogue Output      | Headphone right channel output                                       |

| 24  | NC        | Not bonded           |                                                                      |

| 25  | NC        | Not bonded           |                                                                      |

| 26  | VOUTL     | Analogue output      | DAC channel left output                                              |

| 27  | VOUTR     | Analogue output      | DAC channel right output                                             |

| 28  | VMIDDAC   | Analogue output      | DAC midrail decoupling pin ; 10uF external decoupling                |

| 29  | DACREFN   | Analogue input       | DAC negative reference input                                         |

| 30  | DACREFP   | Analogue input       | DAC positive reference input                                         |

| 31  | AUXR      | Analogue input       | DAC mixer right channel input                                        |

| 32  | AUXL      | Analogue input       | DAC mixer left channel input                                         |

| 33  | VMIDADC   | Analogue Output      | ADC midrail divider decoupling pin; 10uF external decoupling         |

| 34  | ADCREFGND | Supply               | ADC negative supply and substrate connection                         |

| 35  | ADCREFP   | Analogue Output      | ADC positive reference decoupling pin; 10uF external decoupling      |

| 36  | AVDD      | Supply               | Analogue positive supply                                             |

| 37  | AGND      | Supply               | Analogue negative supply and subVstrate connection                   |

| 38  | AINVGR    | Analogue Input       | Right channel multiplexor virtual ground                             |

| 39  | AINOPR    | Analogue Output      | Right channel multiplexor output                                     |

| 40  | AINVGL    | Analogue Input       | Left channel multiplexor virtual ground                              |

| 41  | AINOPL    | Analogue Output      | Left channel multiplexor output                                      |

| 42  | AIN5R     | Analogue Input       | Channel 5 right input multiplexor virtual ground                     |

| 43  | AIN5L     | Analogue Input       | Channel 5 left input multiplexor virtual ground                      |

| 44  | AIN4R     | Analogue Input       | Channel 4 right input multiplexor virtual ground                     |

| 45  | AIN4L     | Analogue Input       | Channel 4 left input multiplexor virtual ground                      |

| 46  | AIN3R     | Analogue Input       | Channel 3 right input multiplexor virtual ground                     |

| 47  | AIN3L     | Analogue Input       | Channel 3 left input multiplexor virtual ground                      |

| 48  | AIN2R     | Analogue Input       | Channel 2 right input multiplexor virtual ground                     |

$\mbox{\bf Note}: \mbox{\bf Digital input pins have Schmitt trigger input buffers.}$

## **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device

Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                                                                                       | MIN        | MAX         |

|-------------------------------------------------------------------------------------------------|------------|-------------|

| Digital supply voltage                                                                          | -0.3V      | +3.63V      |

| Analogue supply voltage                                                                         | -0.3V      | +7V         |

| Voltage range digital inputs (MCLK, DIN, ADCLRC, DACLRC, ADCBCLK, DACBCLK, DI, CL, CE and MODE) | DGND -0.3V | DVDD + 0.3V |

| Voltage range analogue inputs                                                                   | AGND -0.3V | AVDD +0.3V  |

| Master Clock Frequency                                                                          |            | 37MHz       |

| Operating temperature range, T <sub>A</sub>                                                     | -25°C      | +85°C       |

| Storage temperature                                                                             | -65°C      | +150°C      |

#### Notes:

## RECOMMENDED OPERATING CONDITIONS

| PARAMETER               | SYMBOL                               | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|-------------------------|--------------------------------------|-----------------|------|-----|------|------|

| Digital supply range    | DVDD                                 |                 | 2.7  |     | 3.6  | >    |

| Analogue supply range   | AVDD, HPVDD,<br>DACREFP              |                 | 2.7  |     | 5.5  | V    |

| Ground                  | AGND, DGND,<br>DACREFN,<br>ADCREFGND |                 |      | 0   |      | ٧    |

| Difference DGND to AGND |                                      |                 | -0.3 | 0   | +0.3 | ٧    |

Note: digital supply DVDD must never be more than 0.3V greater than AVDD.

<sup>1.</sup> Analogue and digital grounds must always be within 0.3V of each other.

# **ELECTRICAL CHARACTERISTICS**

# **Test Conditions**

$AVDD = 5V,\ DVDD = 3.3V,\ AGND = 0V,\ DGND = 0V,\ T_A = +25^{\circ}C,\ fs = 48kHz,\ MCLK = 256fs\ unless\ otherwise\ stated.$

| PARAMETER                                   | SYMBOL            | TEST CONDITIONS                               | MIN        | TYP             | MAX        | UNIT |

|---------------------------------------------|-------------------|-----------------------------------------------|------------|-----------------|------------|------|

| Digital Logic Levels (TTL Levels            | )                 |                                               | l .        |                 | 1          |      |

| Input LOW level                             | V <sub>IL</sub>   |                                               |            |                 | 0.8        | V    |

| Input HIGH level                            | V <sub>IH</sub>   |                                               | 2.0        |                 |            | V    |

| Output LOW                                  | V <sub>OL</sub>   | I <sub>OL</sub> =1mA                          |            |                 | 0.1 x DVDD | V    |

| Output HIGH                                 | V <sub>OH</sub>   | I <sub>OH</sub> =1mA                          | 0.9 x DVDD |                 |            | V    |

| Analogue Reference Levels                   | 9:1               | 711                                           | I.         |                 | I I        |      |

| Reference voltage                           | $V_{VMID}$        |                                               |            | AVDD/2          |            | V    |

| Potential divider resistance                | R <sub>VMID</sub> |                                               |            | 50k             |            | Ω    |

| DAC Performance (Load = 10k Ω               |                   |                                               |            |                 | l l        |      |

| 0dBFs Full scale output voltage             | , , ,             |                                               |            | 1.0 x           |            | Vrms |

| , ,                                         |                   |                                               |            | AVDD/5          |            |      |

| SNR (Note 1,2)                              |                   | A-weighted,                                   | 102        | 108             |            | dB   |

| ,                                           |                   | @ fs = 48kHz                                  |            |                 |            |      |

| SNR (Note 1,2)                              |                   | A-weighted                                    |            | 108             |            | dB   |

| , , ,                                       |                   | @ fs = 96kHz                                  |            |                 |            |      |

| Dynamic Range (Note 2)                      | DNR               | A-weighted, -60dB                             |            | 108             |            | dB   |

| , ,                                         |                   | full scale input                              |            |                 |            |      |

| Total Harmonic Distortion (THD)             |                   | 1kHz, 0dBFs                                   |            | -97             | -90        | dB   |

| DAC channel separation                      |                   |                                               |            | 100             |            | dB   |

| Power Supply Rejection Ratio                | PSRR              | 1kHz 100mVpp                                  |            | 50              |            | dB   |

|                                             |                   | 20Hz to 20kHz                                 |            | 45              |            | dB   |

|                                             |                   | 100mVpp                                       |            |                 |            |      |

| Headphone Buffer                            |                   |                                               |            |                 |            |      |

| Maximum Output voltage                      |                   |                                               |            | 0.9             |            | Vrms |

| Max Output Power (Note 4)                   | Po                | $R_L = 32 \Omega$                             |            | 25              |            | mW   |

|                                             |                   | $R_L = 16 \Omega$                             |            | 50              |            | mW   |

| SNR (Note 1,2)                              |                   | A-weighted                                    | 85         | 92              |            | dB   |

| Headphone analogue Volume<br>Gain Step Size |                   |                                               | 0.5        | 1               | 1.5        | dB   |

| Headphone analogue Volume<br>Gain Range     |                   | 1kHz Input                                    | -73        |                 | +6         | dB   |

| Headphone analogue Volume Mute Attenuation  |                   | 1kHz Input, 0dB gain                          |            | 100             |            | dB   |

| Total Harmonic Distortion                   | THD               | 1kHz, R <sub>L</sub> = 32Ω @ P <sub>o</sub> = |            | -80             | -60        | dB   |

|                                             |                   | 10mW rms                                      |            | 0.01            | 0.1        | %    |

|                                             |                   | $1 \text{kHz}, R_L = 32\Omega @ P_0 =$        |            | -77             | -55        | dB   |

|                                             |                   | 20mW rms                                      |            | 0.014           | 1.0        | %    |

| Power Supply Rejection Ratio                | PSRR              | 20Hz to 20kHz, without supply decoupling      |            | -40             |            | dB   |

| ADC Performance                             |                   |                                               |            |                 |            |      |

| Input Signal Level (0dB)                    |                   |                                               |            | 1.0 x<br>AVDD/5 |            | Vrms |

| SNR (Note 1,2)                              |                   | A-weighted, 0dB gain<br>@ fs = 48kHz          | 97         | 102             |            | dB   |

| SNR (Note 1,2)                              |                   | A-weighted, 0dB gain @ fs = 96kHz 64 x OSR    |            | 100             |            | dB   |

| Dynamic Range (note 2)                      |                   | A-weighted, -60dB full scale input            |            | 102             |            | dB   |

|                                             |                   | iuii soait iliput                             | I          |                 | 1          |      |

#### **Test Conditions**

AVDD = 5V, DVDD = 3.3V, AGND = 0V, DGND = 0V, TA = +25°C, fs = 48kHz, MCLK = 256fs unless otherwise stated.

|                                    |               | 1kHz, -1dBFs             |              | -95         | -85   | dB   |

|------------------------------------|---------------|--------------------------|--------------|-------------|-------|------|

| ADC Channel Separation             |               | 1kHz Input               |              | 90          |       | dB   |

| Programmable Gain Step Size        |               |                          | 0.25         | 0.5         | 0.75  | dB   |

| Programmable Gain Range (Analogue) |               | 1kHz Input               | -21          |             | +24   | dB   |

| Programmable Gain Range (Digital)  |               | 1kHz Input               | -103         |             | -21.5 | dB   |

| Analogue Mute Attenuation (Note 6) |               | 1kHz Input, 0dB gain     |              | 76          |       | dB   |

| Power Supply Rejection Ratio       | PSRR          | 1kHz 100mVpp             |              | 50          |       | dB   |

|                                    |               | 20Hz to 20kHz<br>100mVpp |              | 45          |       | dB   |

| Analogue Input (AIN) to Analogu    | ue output (VO | UT) (Load=10kΩ, 50pF, g  | ain = 0dB) l | Bypass Mode |       |      |

| 0dB Full scale output voltage      |               |                          |              | 1.0 x       |       | Vrms |

|                                    |               |                          |              | AVDD/5      |       |      |

| SNR (Note 1)                       |               |                          | 99           | 103         |       | dB   |

| THD                                |               | 1kHz, 0dB                |              | -93         |       | dB   |

|                                    |               | 1kHz, -3dB               |              | -95         |       | dB   |

| Power Supply Rejection Ratio       | PSRR          | 1kHz 100mVpp             |              | 50          |       | dB   |

|                                    |               | 20Hz to 20kHz<br>100mVpp |              | 45          |       | dB   |

| Mute Attenuation                   |               | 1kHz, 0dB                |              | 100         |       | dB   |

| Supply Current                     |               |                          |              |             |       |      |

| Analogue supply current            |               | AVDD = 5V                |              | 48          |       | mA   |

| Digital supply current             |               | DVDD = 3.3V              |              | 8           | _     | mA   |

| Aux Input (AUX/L/R) to Analogu     | e output (VOU | IT L/R)( Load=10kΩ, 50pF | , gain = 0d  | B)          |       |      |

| SNR                                |               |                          |              | 108         |       | dB   |

| THD                                |               |                          |              | -95         | _     | dB   |

### Notes:

- Ratio of output level with 1kHz full scale input, to the output level with all zeros into the digital input, measured 'A' weighted.

- All performance measurements done with 20kHz low pass filter, and where noted an A-weight filter. Failure to use such a filter will result in higher THD+N and lower SNR and Dynamic Range readings than are found in the Electrical Characteristics. The low pass filter removes out of band noise; although it is not audible it may affect dynamic specification values.

- 3. VMID decoupled with 10uF and 0.1uF capacitors (smaller values may result in reduced performance).

- 4. Harmonic distortion on the headphone output decreases with output power.

- 5. All performance measurement done using certain timings conditions (Please refer to section 'Digital Audio Interface').

- 6. A full digital MUTE can be achieved if the ADC gain (LAG/RAG) is set to minimum.

#### **TERMINOLOGY**

- 1. Signal-to-noise ratio (dB) SNR is a measure of the difference in level between the full scale output and the output with no signal applied. (No Auto-zero or Automute function is employed in achieving these results).

- Dynamic range (dB) DNR is a measure of the difference between the highest and lowest portions of a signal. Normally a THD+N measurement at 60dB below full scale. The measured signal is then corrected by adding the 60dB to it. (e.g. THD+N @ -60dB= -32dB, DR= 92dB).

- 3. THD+N (dB) THD+N is a ratio, of the rms values, of (Noise + Distortion)/Signal.

- 4. Stop band attenuation (dB) Is the degree to which the frequency spectrum is attenuated (outside audio band).

5. Channel Separation (dB) - Also known as Cross-Talk. This is a measure of the amount one channel is isolated from the other. Normally measured by sending a full scale signal down one channel and measuring the other.

6. Pass-Band Ripple - Any variation of the frequency response in the pass-band region.

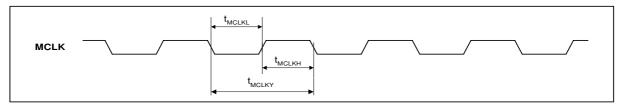

# **MASTER CLOCK TIMING**

Figure 1 Master Clock Timing Requirements

#### **Test Conditions**

AVDD = 5V, DVDD = 3.3V, AGND = 0V, AGND, DGND = 0V,  $T_A = +25^{\circ}C$ , fs = 48kHz, ADC/DACMCLK = 256fs unless otherwise stated.

| PARAMETER                                 | SYMBOL             | TEST CONDITIONS       | MIN   | TYP | MAX   | UNIT          |

|-------------------------------------------|--------------------|-----------------------|-------|-----|-------|---------------|

| System Clock Timing Informati             | on                 |                       |       |     |       |               |

| ADC/DACMCLK System clock pulse width high | t <sub>MCLKH</sub> |                       | 11    |     |       | ns            |

| ADC/DACMCLK System clock pulse width low  | t <sub>MCLKL</sub> |                       | 11    |     |       | ns            |

| ADC/DACMCLK System clock cycle time       | t <sub>MCLKY</sub> |                       | 28    |     | 1000  | ns            |

| ADC/DACMCLK Duty cycle                    |                    |                       | 40:60 |     | 60:40 |               |

| Power-saving mode activated               |                    | After MCLK stopped    | 2     |     | 10    | μs            |

| Normal mode resumed                       |                    | After MCLK re-started | 0.5   |     | 1     | MCLK<br>cycle |

**Table 1 Master Clock Timing Requirements**

### Note:

If MCLK period is longer than maximum specified above, power-saving mode is entered and DACs are powered down with internal digital audio filters being reset. In this power-saving mode, all registers will retain their values and can be accessed in the normal manner through the control interface. Once MCLK is restored, the DACs are automatically powered up, but a write to the volume update register bit is required to restore the correct volume settings.

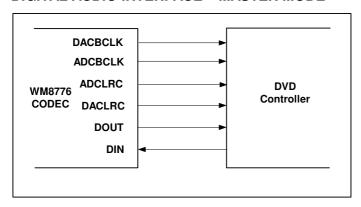

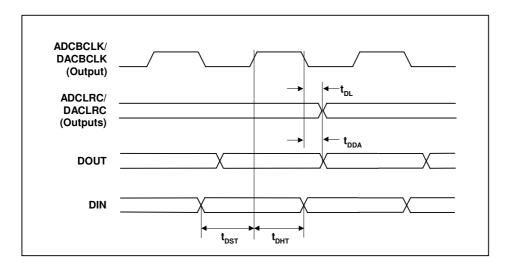

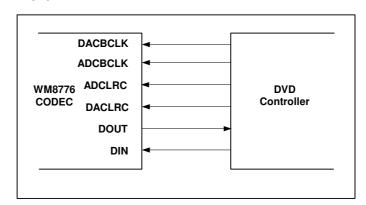

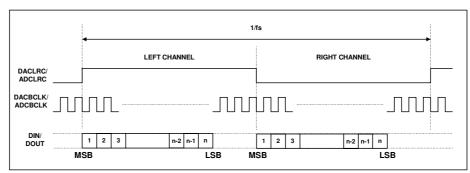

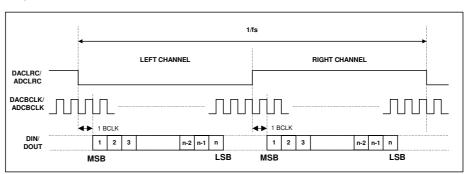

# **DIGITAL AUDIO INTERFACE - MASTER MODE**

Figure 2 Audio Interface - Master Mode

Figure 3 Digital Audio Data Timing – Master Mode

## **Test Conditions**

AVDD = 5V, DVDD = 3.3V, AGND, DGND = 0V,  $T_A = +25^{\circ}C$ , Master Mode, fs = 48kHz, ADC/DACMCLK = 256fs unless otherwise stated.

| PARAMETER                                                        | SYMBOL           | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------------------------------------------------------|------------------|-----------------|-----|-----|-----|------|

| Audio Data Input Timing Info                                     | ormation         |                 |     |     |     |      |

| ADC/DACLRC propagation<br>delay from ADC/DACBCLK<br>falling edge | t <sub>DL</sub>  |                 | 0   |     | 10  | ns   |

| DOUT propagation delay from ADCBCLK falling edge                 | t <sub>DDA</sub> |                 | 0   |     | 10  | ns   |

| DIN setup time to DACBCLK rising edge                            | t <sub>DST</sub> |                 | 10  |     |     | ns   |

| DIN hold time from DACBCLK rising edge                           | t <sub>DHT</sub> |                 | 10  |     |     | ns   |

Table 2 Digital Audio Data Timing – Master Mode

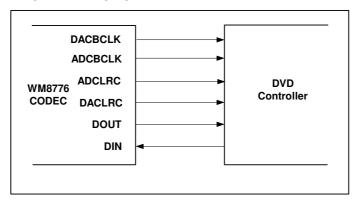

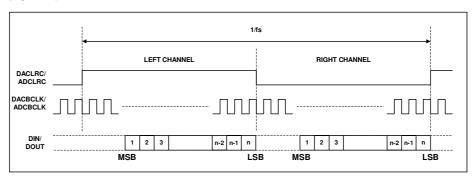

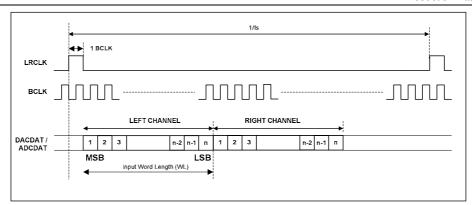

# **DIGITAL AUDIO INTERFACE – SLAVE MODE**

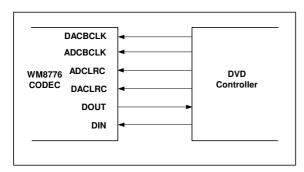

Figure 4 Audio Interface - Slave Mode

Figure 5 Digital Audio Data Timing – Slave Mode

### **Test Conditions**

AVDD = 5V, DVDD = 3.3V, AGND = 0V, DGND = 0V,  $T_A = +25^{\circ}C$ , Slave Mode, fs = 48kHz, ADC/DACMCLK = 256fs unless otherwise stated.

| PARAMETER                                                  | SYMBOL            | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------------------------------------------------|-------------------|-----------------|-----|-----|-----|------|

| Audio Data Input Timing Info                               | ormation          |                 | •   |     |     | •    |

| ADC/DACBCLK cycle time                                     | t <sub>BCY</sub>  |                 | 50  |     |     | ns   |

| ADC/DACBCLK pulse width high                               | tвсн              |                 | 20  |     |     | ns   |

| ADC/DACBCLK pulse width low                                | t <sub>BCL</sub>  |                 | 20  |     |     | ns   |

| DACLRC/ADCLRC set-up<br>time to ADC/DACBCLK<br>rising edge | t <sub>LRSU</sub> |                 | 10  |     |     | ns   |

| DACLRC/ADCLRC hold<br>time from ADC/DACBCLK<br>rising edge | t <sub>LRH</sub>  |                 | 10  |     |     | ns   |

| DIN set-up time to<br>DACBCLK rising edge                  | t <sub>DS</sub>   |                 | 10  |     |     | ns   |

| DIN hold time from DACBCLK rising edge                     | t <sub>DH</sub>   |                 | 10  |     |     | ns   |

| DOUT propagation delay from ADCBCLK falling edge           | t <sub>DD</sub>   |                 | 0   |     | 10  | ns   |

Table 3 Digital Audio Data Timing - Slave Mode

**Note:** ADCLRC and DACLRC should be synchronous with MCLK, although the WM8776 interface is tolerant of phase variations or jitter on these signals.

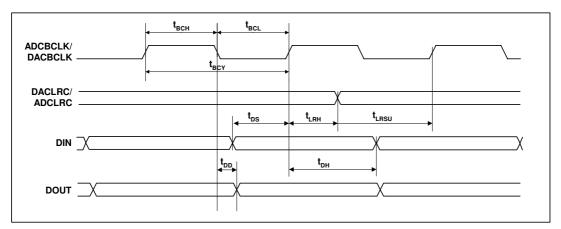

# **3-WIRE MPU INTERFACE TIMING**

Figure 6 SPI Compatible (3-wire) Control Interface Input Timing (MODE=1)

| PARAMETER                        | SYMBOL           | MIN | TYP | MAX | UNIT |

|----------------------------------|------------------|-----|-----|-----|------|

| CL rising edge to CE rising edge | t <sub>SCS</sub> | 60  |     |     | ns   |

| CL pulse cycle time              | t <sub>SCY</sub> | 80  |     |     | ns   |

| CL pulse width low               | tscl             | 30  |     |     | ns   |

| CL pulse width high              | t <sub>scн</sub> | 30  |     |     | ns   |

| DI to CL set-up time             | t <sub>DSU</sub> | 20  |     |     | ns   |

| CL to DI hold time               | t <sub>DHO</sub> | 20  |     |     | ns   |

| CE pulse width low               | t <sub>CSL</sub> | 20  |     |     | ns   |

| CE pulse width high              | t <sub>CSH</sub> | 20  |     |     | ns   |

| CE rising to CL rising           | t <sub>CSS</sub> | 20  |     |     | ns   |

Table 4 3-wire SPI Compatible Control Interface Input Timing Information

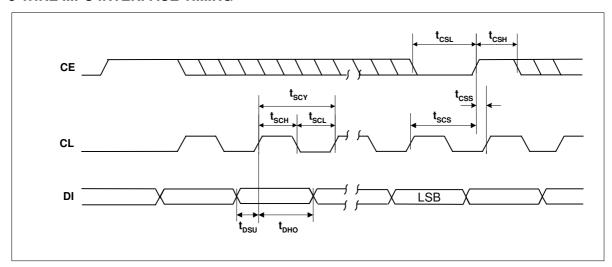

# **CONTROL INTERFACE TIMING – 2-WIRE MODE**

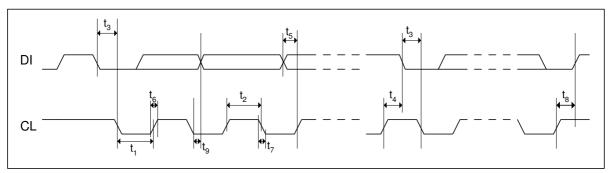

Figure 7 Control Interface Timing – 2-Wire Serial Control Mode (MODE=0)

### **Test Conditions**

$AVDD = 5V, \, DVDD = 3.3V, \, AGND, \, DGND = 0V, \, T_A \, = +25^{\circ}C, \, fs = 48kHz, \, MCLK = 256fs \, unless \, otherwise \, stated \, decomposition of the contraction of$

| PARAMETER                                     | SYMBOL          | MIN | TYP | MAX | UNIT |  |  |

|-----------------------------------------------|-----------------|-----|-----|-----|------|--|--|

| Program Register Input Information            |                 |     |     |     |      |  |  |

| CL Frequency                                  |                 | 0   |     | 526 | kHz  |  |  |

| CL Low Pulse-Width                            | t <sub>1</sub>  | 1.3 |     |     | us   |  |  |

| CL High Pulse-Width                           | t <sub>2</sub>  | 600 |     |     | ns   |  |  |

| Hold Time (Start Condition)                   | t <sub>3</sub>  | 600 |     |     | ns   |  |  |

| Setup Time (Start Condition)                  | t <sub>4</sub>  | 600 |     |     | ns   |  |  |

| Data Setup Time                               | t <sub>5</sub>  | 100 |     |     | ns   |  |  |

| DI, CL Rise Time                              | t <sub>6</sub>  |     |     | 300 | ns   |  |  |

| DI, CL Fall Time                              | t <sub>7</sub>  |     |     | 300 | ns   |  |  |

| Setup Time (Stop Condition)                   | t <sub>8</sub>  | 600 |     |     | ns   |  |  |

| Data Hold Time                                | t <sub>9</sub>  |     |     | 900 | ns   |  |  |

| Pulse width of spikes that will be suppressed | t <sub>ps</sub> | 0   |     | 5   | ns   |  |  |

Table 5 2-wire Control Interface Timing Information

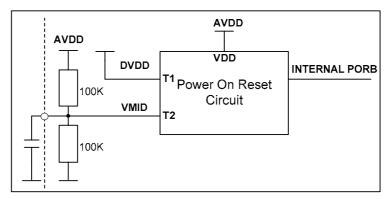

# INTERNAL POWER ON RESET CIRCUIT

Figure 8 Internal Power on Reset Circuit Schematic

The WM8776 includes an internal Power on Reset Circuit which is used reset the digital logic into a default state after power up.

Figure 8 shows a schematic of the internal POR circuit. The POR circuit is powered from AVDD. The circuit monitors DVDD and VMID and asserts PORB low if DVDD or VMID are below the minimum threshold Vpor\_off.

On power up, the POR circuit requires AVDD to be present to operate. PORB is asserted low until AVDD and DVDD and VMID are established. When AVDD, DVDD, and VMID have been established, PORB is released high, all registers are in their default state and writes to the digital interface may take place.

On power down, PORB is asserted low whenever DVDD or VMID drop below the minimum threshold  $Vpor\_off$ .

If AVDD is removed at any time, the internal Power on Reset circuit is powered down and PORB will follow AVDD.

In most applications the time required for the device to release PORB high will be determined by the charge time of the VMID node.

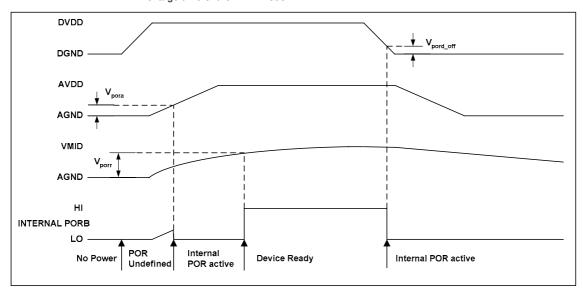

Figure 9 Typical Power up Sequence where DVDD is Powered before AVDD

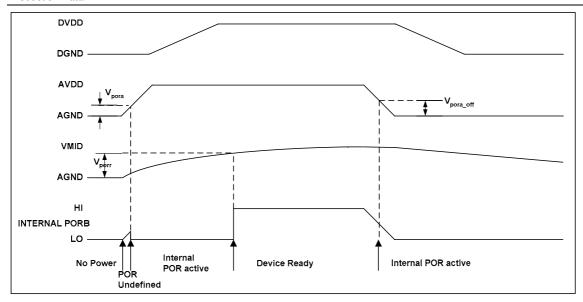

Figure 10 Typical Power up Sequence where AVDD is Powered before DVDD

| SYMBOL                | MIN | TYP | MAX | UNIT |

|-----------------------|-----|-----|-----|------|

| $V_{pora}$            | 0.5 | 0.7 | 1.0 | V    |

| $V_{porr}$            | 0.5 | 0.7 | 1.1 | V    |

| $V_{pora\_off}$       | 1.0 | 1.4 | 2.0 | V    |

| V <sub>pord_off</sub> | 0.6 | 0.8 | 1.0 | V    |

In a real application the designer is unlikely to have control of the relative power up sequence of AVDD and DVDD. Using the POR circuit to monitor VMID ensures a reasonable delay between applying power to the device and Device Ready.

Figure 9 and Figure 10 show typical power up scenarios in a real system. Both AVDD and DVDD must be established and VMID must have reached the threshold Vporr before the device is ready and can be written to. Any writes to the device before Device Ready will be ignored.

Figure 9 shows DVDD powering up before AVDD. Figure 10 shows AVDD powering up before DVDD. In both cases, the time from applying power to Device Ready is dominated by the charge time of VMID.

A 10uF cap is recommended for decoupling on VMID. The charge time for VMID will dominate the time required for the device to become ready after power is applied. The time required for VMID to reach the threshold is a function of the VMID resistor string and the decoupling capacitor. The Resistor string has an typical equivalent resistance of  $50k\Omega$  (+/-20%). Assuming a 10uF capacitor, the time required for VMID to reach threshold of 1V is approx 110ms.

## **DEVICE DESCRIPTION**

## INTRODUCTION

WM8776 is a complete 2-channel DAC, 2-channel ADC audio CODEC, with flexible input multiplexor including digital interpolation and decimation filters, multi-bit sigma delta stereo ADC, and switched capacitor multi-bit sigma delta DACs with analogue volume controls on each channel and output smoothing filters. It is available in a single package and controlled by either a 3-wire or 2-wire software interface. The 3-wire interface is compatible with the SPI standard.

An analogue bypass path option is available, to allow stereo analogue signals from any of the 5 stereo inputs to be sent to the stereo outputs via the main volume controls. This allows a purely analogue input to analogue output high quality signal path to be implemented if required.

The DAC and ADC have separate left/right clocks, bit clocks, master clocks and data I/Os. The Audio Interface may be configured to operate in either master or slave mode. In Slave mode ADCLRC, DACLRC, ADCBCLK and DACBCLK are all inputs. In Master mode ADCLRC, DACLRC, ADCBCLK are outputs.

The input multiplexor to the ADC is configured to allow large signal levels to be input to the ADC, using external resistors to reduce the amplitude of larger signals to within the normal operating range of the ADC. The ADC has an analogue input PGA and a digital gain control, accessed by one register write. The input PGA allows input signals to be gained up to +24dB and attenuated down to -21dB in 0.5dB steps. The digital gain control allows attenuation from -21.5dB to -103dB in 0.5dB steps. This allows the user maximum flexibility in the use of the ADC.

The DAC has its own digital volume control, which is adjustable between 0dB and -127.5dB in 0.5dB steps. There is also an analogue volume control on the headphone outputs, which is adjustable between +6dB and -73dB in 1dB steps. The analogue and digital volume controls may be operated independently. In addition a zero cross detect circuit is provided for both analogue and digital volume controls. When analogue volume zero-cross detection is enabled the attenuation values are only updated when the input signal to the gain stage is close to the analogue ground level. The digital volume control detects a transition through the zero point before updating the volume. This minimises audible clicks and 'zipper' noise as the gain values change.

The DAC output incorporates an input selector and mixer allowing a signal to be either switched into the signal path in place of the DAC signal or mixed with the DAC signal before the volume control. Use of external resistors allows larger input levels to be accepted by the device, giving maximum user flexibility.

Internal functionality is controlled by CE, CL, DI and MODE input pins. The MODE pin determines which of the two control interface modes is selected.

Operation using system clock of 128fs, 192fs, 256fs, 384fs, 512fs or 768fs is provided. In Slave mode selection between clock rates is automatically controlled. In master mode the master clock to sample rate ratio is set by control bits ADCRATE and DACRATE. ADC and DAC may run at different rates and have their own bit clocks and master clocks.

The audio data interface supports right, left and I<sup>2</sup>S interface formats along with a highly flexible DSP serial port interface.

### **AUDIO DATA SAMPLING RATES**

In a typical digital audio system there is only one central clock source producing a reference clock to which all audio data processing is synchronised. This clock is often referred to as the audio system's Master Clock. The WM8776 uses separate master clocks for the ADC and DAC. The external master system clocks can be applied directly through the ADCMCLK and DACMCLK input pins with no software configuration necessary. In a system where there are a number of possible sources for the reference clock it is recommended that the clock source with the lowest jitter be used to optimise the performance of the ADC and DAC.

The master clock for WM8776 supports DAC and ADC audio sampling rates from 256fs to 768fs, where fs is the audio sampling frequency (DACLRC or ADCLRC) typically 32kHz, 44.1kHz, 48kHz or 96kHz (the DAC also supports operation at 128fs and 192fs and 192kHz sample rate). The master clock is used to operate the digital filters and the noise shaping circuits.

In Slave mode the WM8776 has a master detection circuit that automatically determines the relationship between the master clock frequency and the sampling rate (to within +/- 32 system clocks). If there is a greater than 32 clocks error the interface is disabled and maintains the output level at the last sample. The master clock should be synchronised with ADCLRC/DACLRC for optical performance, although the WM8776 is tolerant of phase variations or jitter on this clock. Table 6 shows the typical master clock frequency inputs for the WM8776.

The signal processing for the WM8776 typically operates at an oversampling rate of 128fs for both ADC and DAC. The exception to this for the DAC is for operation with a 128/192fs system clock, e.g. for 192kHz operation where the oversampling rate is 64fs. For ADC operation at 96kHz it is recommended that the user set the ADCOSR bit. This changes the ADC signal processing oversample rate to 64fs.

| SAMPLING<br>RATE | System Clock Frequency (MHz) |        |             |             |             |             |  |  |  |  |

|------------------|------------------------------|--------|-------------|-------------|-------------|-------------|--|--|--|--|

| (DACLRC/         | 128fs                        | 192fs  | 256fs       | 384fs       | 512fs       | 768fs       |  |  |  |  |

| ADCLRC)          | DAC ONLY                     |        |             |             |             |             |  |  |  |  |

| 32kHz            | 4.096                        | 6.144  | 8.192       | 12.288      | 16.384      | 24.576      |  |  |  |  |

| 44.1kHz          | 5.6448                       | 8.467  | 11.2896     | 16.9340     | 22.5792     | 33.8688     |  |  |  |  |

| 48kHz            | 6.144                        | 9.216  | 12.288      | 18.432      | 24.576      | 36.864      |  |  |  |  |

| 96kHz            | 12.288                       | 18.432 | 24.576      | 36.864      | Unavailable | Unavailable |  |  |  |  |

| 192kHz           | 24.576                       | 36.864 | Unavailable | Unavailable | Unavailable | Unavailable |  |  |  |  |

Table 6 System Clock Frequencies Versus Sampling Rate

In Master mode DACBCLK, ADCBCLK, DACLRC and ADCLRC are generated by the WM8776. The frequencies of ADCLRC and DACLRC are set by setting the required ratio of DACMCLK to DACLRC and ADCMCLK to ADCLRC using the DACRATE and ADCRATE control bits (Table 7).

| ADCRATE[2:0]/<br>DACRATE[2:0] | ADCMCLK/DACMCLK:<br>ADCLRC/DACLRC<br>RATIO |

|-------------------------------|--------------------------------------------|

| 000                           | 128fs (DAC Only)                           |

| 001                           | 192fs (DAC Only)                           |

| 010                           | 256fs                                      |

| 011                           | 384fs                                      |

| 100                           | 512fs                                      |

| 101                           | 768fs                                      |

Table 7 Master Mode MCLK: ADCLRC/DACLRC Ratio Select

Table 8 shows the settings for ADCRATE and DACRATE for common sample rates and ADCMCLK/DACMCLK frequencies.

| SAMPLING<br>RATE | System Clock Frequency (MHz) |                 |                             |                             |                             |                             |  |  |  |

|------------------|------------------------------|-----------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--|--|--|

| (DACLRC/         | 128fs                        | 192fs           | 256fs                       | 384fs                       | 512fs                       | 768fs                       |  |  |  |

| ADCLRC)          | DACRATE<br>=000              | DACRATE<br>=001 | ADCRATE/<br>DACRATE<br>=010 | ADCRATE/<br>DACRATE<br>=011 | ADCRATE/<br>DACRATE<br>=100 | ADCRATE/<br>DACRATE<br>=101 |  |  |  |

| 32kHz            | 4.096                        | 6.144           | 8.192                       | 12.288                      | 16.384                      | 24.576                      |  |  |  |

| 44.1kHz          | 5.6448                       | 8.467           | 11.2896                     | 16.9340                     | 22.5792                     | 33.8688                     |  |  |  |

| 48kHz            | 6.144                        | 9.216           | 12.288                      | 18.432                      | 24.576                      | 36.864                      |  |  |  |

| 96kHz            | 12.288                       | 18.432          | 24.576                      | 36.864                      | Unavailable                 | Unavailable                 |  |  |  |

| 192kHz           | 24.576                       | 36.864          | Unavailable                 | Unavailable                 | Unavailable                 | Unavailable                 |  |  |  |

Table 8 Master Mode ADC/DACLRC Frequency Selection

ADCBCLK and DACBCLK are also generated by the WM8776. The frequency of ADCBCLK and DACBCLK depends on the mode of operation.

In 128/192fs modes (DACRATE=000 or 001) BCLK = MCLK/2. In 256/384/512fs modes (ADCRATE/DACRATE=010 or 011 or 100) BCLK = MCLK/4. However if DSP mode is selected as the audio interface mode then BCLK=MCLK. Note that DSP mode cannot be used in 128fs mode for word lengths greater than 16 bits or in 192fs mode for word lengths greater than 24 bits.

### **ZERO DETECT**

The WM8776 has a zero detect circuit for each DAC channel, which detects when 1024 consecutive zero samples have been input. The two zero flag outputs (ZFLAGL and ZFLAGR) may be programmed to output the zero detect signals (see Table 9) that may then be used to control external muting circuits. A '1' on ZFLAGL or ZFLAGR indicates a zero detect. The zero detect may also be used to automatically enable the PGA mute by setting IZD. The zero flag output may be disabled by setting DZFM to 00. The zero flag signal for each DAC channel will only be enabled if it is enabled as an input to the output summing stage.

| DZFM[1:0] | ZFLAGL               | ZFLAGR              |

|-----------|----------------------|---------------------|

| 00        | Zero flag disabled   | Zero flag disabled  |

| 01        | Left channel zero    | Right channel zero  |

| 10        | Both channel zero    | Both channel zero   |

| 11        | Either channels zero | Either channel zero |

**Table 9 Zero Flag Output Select**

## **POWERDOWN MODES**

The WM8776 has powerdown control bits allowing specific parts of the WM8776 to be powered off when not being used. The 5-channel input source selector and input buffer may be powered down using control bit AINPD. When AINPD is set all inputs to the source selector (AIN1I/R to AIN5L/R) are switched to a buffered VMIDADC. Control bit ADCPD powers off the ADC and also the ADC input PGAs. The stereo DAC has a separate powerdown control bit, DACPD allowing the DAC and analogue output mixer to be powered off when not in use. This also switches the analogue outputs VOUTL/R to VMIDDAC to maintain a dc level on the output.

Setting AINPD, ADCPD and DACPD will powerdown everything except the references VMIDADC, ADCREF and VMIDDAC. These may be powered down by setting PDWN. Setting PDWN will override all other powerdown control bits. It is recommended that AINPD, HPPD, ADCPD and DACPD are set before setting PDWN. The default is for all blocks to be enabled other than HPPD.

## **DIGITAL AUDIO INTERFACE**

#### **MASTER AND SLAVE MODES**

The audio interface operates in either Slave or Master mode, selectable using the MS control bit. In both Master and Slave modes DIN is always an input to the WM8776 and DOUT is always an output. The default is Slave mode.

In Slave mode (MS=0) ADCLRC, DACLRC, ADCBCLK and DACBCLK are inputs to the WM8776 (Figure 11). DIN and DACLRC are sampled by the WM8776 on the rising edge of DACBCLK, ADCLRC is sampled on the rising edge of ADCBCLK. ADC data is output on DOUT and changes on the falling edge of ADCBCLK. By setting control bit BCLKINV the polarity of ADCBCLK and DACBCLK may be reversed so that DIN and DACLRC are sampled on the falling edge of DACBCLK, ADCLRC is sampled on the falling edge of ADCBCLK and DOUT changes on the rising edge of ADCBCLK.

Figure 11 Slave Mode

In Master mode (MS=1) ADCLRC, DACLRC, ADCBCLK and DACBCLK are outputs from the WM8776 (Figure 12). ADCLRC, DACLRC, ADCBCLK and DACBCLK are generated by the WM8776. DIN is sampled by the WM8776 on the rising edge of DACBCLK so the controller must output DAC data that changes on the falling edge of DACBCLK. ADC data is output on DOUT and changes on the falling edge of ADCBCLK. By setting control bit BCLKINV, the polarity of ADCBCLK and DACBCLK may be reversed so that DIN is sampled on the falling edge of DACBCLK and DOUT changes on the rising edge of ADCBCLK.

Figure 12 Master Mode

#### **AUDIO INTERFACE FORMATS**

Audio data is applied to the internal DAC filters or output from the ADC filters, via the Digital Audio Interface. 5 popular interface formats are supported:

- Left Justified mode

- Right Justified mode

- I<sup>2</sup>S mode

- DSP mode A

- DSP mode B

All 5 formats send the MSB first and support word lengths of 16, 20, 24 and 32 bits, with the exception of 32 bit right justified mode, which is not supported.

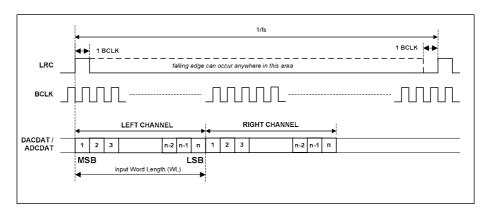

In left justified, right justified and I<sup>2</sup>S modes, the digital audio interface receives DAC data on the DIN input and outputs ADC data on DOUT. Audio Data for each stereo channel is time multiplexed with ADCLRC/DACLRC indicating whether the left or right channel is present. ADCLRC/DACLRC is also used as a timing reference to indicate the beginning or end of the data words.

In left justified, right justified and I<sup>2</sup>S modes; the minimum number of BCLKs per DACLRC/ADCLRC period is 2 times the selected word length. ADCLRC/DACLRC must be high for a minimum of word length BCLKs and low for a minimum of word length BCLKs. Any mark to space ratio on ADCLRC/DACLRC is acceptable provided the above requirements are met.

In DSP modes A or B, DACLRC is used as a frame sync signal to identify the MSB of the first word. The minimum number of DACBCLKs per DACLRC period is 2 times the selected word length. Any mark to space ratio is acceptable on DACLRC provided the rising edge is correctly positioned. The ADC data may also be output in DSP modes A or B, with ADCLRC used as a frame sync to identify the MSB of the first word. The minimum number of ADCBCLKs per ADCLRC period is 2 times the selected word length.

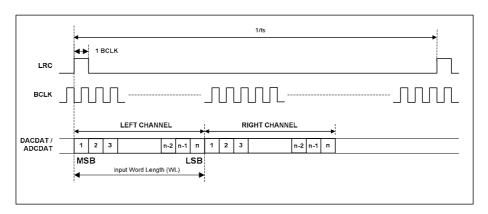

### **LEFT JUSTIFIED MODE**

In left justified mode, the MSB of DIN is sampled by the WM8776 on the first rising edge of DACBCLK following a DACLRC transition. The MSB of the ADC data is output on DOUT and changes on the same falling edge of ADCBCLK as ADCLRC and may be sampled on the rising edge of ADCBCLK. ADCLRC and DACLRC are high during the left samples and low during the right samples (Figure 13).

Figure 13 Left Justified Mode Timing Diagram

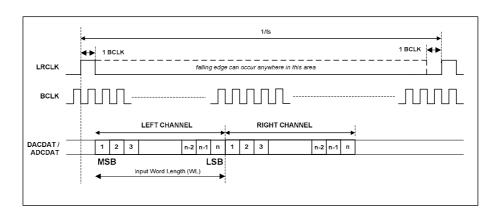

#### **RIGHT JUSTIFIED MODE**

In right justified mode, the LSB of DIN is sampled by the WM8776 on the rising edge of DACBCLK preceding a DACLRC transition. The LSB of the ADC data is output on DOUT and changes on the falling edge of ADCBCLK preceding a ADCLRC transition and may be sampled on the rising edge of ADCBCLK. ADCLRC and DACLRC are high during the left samples and low during the right samples (Figure 14).

Figure 14 Right Justified Mode Timing Diagram

### I2S MODE

In  $l^2S$  mode, the MSB of DIN is sampled by the WM8776 on the second rising edge of DACBCLK following a DACLRC transition. The MSB of the ADC data is output on DOUT and changes on the first falling edge of ADCBCLK following an ADCLRC transition and may be sampled on the rising edge of ADCBCLK. ADCLRC and DACLRC are low during the left samples and high during the right samples.

Figure 15 I<sup>2</sup>S Mode Timing Diagram

### **DSP MODES**

In DSP/PCM mode, the left channel MSB is available on either the 1<sup>st</sup> (mode B) or 2<sup>nd</sup> (mode A) rising edge of BCLK (selectable by LRP) following a rising edge of LRC. Right channel data immediately follows left channel data. Depending on word length, BCLK frequency and sample rate, there may be unused BCLK cycles between the LSB of the right channel data and the next sample.

In device master mode, the LRC output will resemble the frame pulse shown in Figure 16 and Figure 17. In device slave mode, Figure 18 and Figure 19, it is possible to use any length of frame pulse less than 1/fs, providing the falling edge of the frame pulse occurs greater than one BCLK period before the rising edge of the next frame pulse.

Figure 16 DSP/PCM Mode Audio Interface (mode A, LRP=0, Master)

Figure 17 DSP/PCM Mode Audio Interface (mode B, LRP=1, Master)

Figure 18 DSP/PCM Mode Audio Interface (mode A, LRP=0, Slave)

Figure 19 DSP/PCM Mode Audio Interface (mode B, LRP=0, Slave)

## **CONTROL INTERFACE OPERATION**

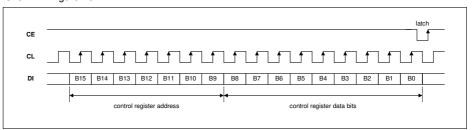

The WM8776 is controlled by writing to registers through a serial control interface. A control word consists of 16 bits. The first 7 bits (B15 to B9) are address bits that select which control register is accessed. The remaining 9 bits (B8 to B0) are data bits, corresponding to the 9 bits in each control register. The control interface can operate as either a 3-wire or 2-wire MPU interface. The MODE pin selects the interface format, as shown in Table 10.

| MODE | Control Mode     |

|------|------------------|

| 0    | 2 wire interface |

| 1    | 3 wire interface |

Table 10 Control Interface Selection via MODE Pin

# 3-WIRE (SPI COMPATIBLE) SERIAL CONTROL MODE

In 3-wire mode, every rising edge of CL clocks in one data bit from the DI pin. A rising edge on CE latches in a complete control word consisting of the last 16 bits. The 3-wire interface protocol is shown in Figure 20.

Figure 20 3-wire SPI Compatible Interface

- 1. B[15:9] are Control Address Bits

- 2. B[8:0] are Control Data Bits

- 3. CE is edge sensitive the data is latched on the rising edge of CE.

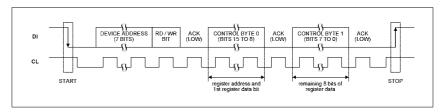

#### 2-WIRE SERIAL CONTROL MODE

The WM8776 supports software control via a 2-wire serial bus. Many devices can be controlled by the same bus, and each device has a unique 7-bit address (this is not the same as the 7-bit address of each register in the WM8776).

The WM8776 operates as a slave device only. The controller indicates the start of data transfer with a high to low transition on DI while CL remains high. This indicates that a device address and data will follow. All devices on the 2-wire bus respond to the start condition and shift in the next eight bits on DI (7-bit address + Read/Write bit, MSB first). If the device address received matches the address of the WM8776 and the R/W bit is '0', indicating a write, then the WM8776 responds by pulling DI low on the next clock pulse (ACK). If the address is not recognised or the R/W bit is '1', the WM8776 returns to the idle condition and wait for a new start condition and valid address.

Once the WM8776 has acknowledged a correct address, the controller sends the first byte of control data (B15 to B8, i.e. the WM8776 register address plus the first bit of register data). The WM8776 then acknowledges the first data byte by pulling DI low for one clock pulse. The controller then sends the second byte of control data (B7 to B0, i.e. the remaining 8 bits of register data), and the WM8776 acknowledges again by pulling DI low.

The transfer of data is complete when there is a low to high transition on DI while CL is high. After receiving a complete address and data sequence the WM8776 returns to the idle state and waits for another start condition. If a start or stop condition is detected out of sequence at any point during data transfer (i.e. DI changes while CL is high), the device jumps to the idle condition.

Figure 21 2-wire Serial Interface

- 1. B[15:9] are Control Address Bits

- 2. B[8:0] are Control Data Bits

The WM8776 has two possible device addresses, which can be selected using the CE pin.

| CE STATE | DEVICE ADDRESS    |

|----------|-------------------|

| Low      | 0011010 (0 x 34h) |

| High     | 0011011 (0 x 36h) |

Table 11 2-Wire MPU Interface Address Selection

### **CONTROL INTERFACE REGISTERS**

### **DIGITAL AUDIO INTERFACE CONTROL REGISTER**

Interface format is selected via the FMT[1:0] register bits:

| REGISTER ADDRESS      | BIT | LABEL  | DEFAULT | DESCRIPTION                  |

|-----------------------|-----|--------|---------|------------------------------|

| R10 (0Ah)             | 1:0 | DACFMT | 10      | Interface format Select      |

| 0001010               |     | [1:0]  |         | 00 : right justified mode    |

| DAC Interface Control |     |        |         | 01: left justified mode      |

| R11 (0Bh)             | 1:0 | ADCFMT | 10      | 10: I <sup>2</sup> S mode    |

| 0001011               |     | [1:0]  |         | 11: DSP (early or late) mode |

| ADC Interface Control |     |        |         |                              |

In left justified, right justified or  $I^2S$  modes, the LRP register bit controls the polarity of ADCLRC/DACLRC. If this bit is set high, the expected polarity of ADCLRC/DACLRC will be the opposite of that shown Figure 13, Figure 14, etc. Note that if this feature is used as a means of swapping the left and right channels, a 1 sample phase difference will be introduced. In DSP modes, the LRP register bit is used to select between early and late modes.

| REGISTER ADDRESS      | BIT | LABEL  | DEFAULT | DESCRIPTION                                         |

|-----------------------|-----|--------|---------|-----------------------------------------------------|

| R10 (0Ah)             | 2   | DACLRP | 0       | In left/right/ I <sup>2</sup> S modes:              |

| 0001010               |     |        |         | ADCLRC/DACLRC Polarity (normal)                     |

| DAC Interface Control |     |        |         | 0 : normal ADCLRC/DACLRC polarity                   |

| R11 (0Bh)<br>0001011  | 2   | ADCLRP | 0       | 1: inverted ADCLRC/DACLRC     polarity In DSP mode: |

| ADC Interface Control |     |        |         | 0 : Early DSP mode                                  |

|                       |     |        |         | 1: Late DSP mode                                    |

By default, ADCLRC, DACLRC and DIN are sampled on the rising edge of ADCBCLK and DACBCLK and should ideally change on the falling edge. Data sources that change ADCLRC/DACLRC and DIN on the rising edge of ADCBCLK/DACBCLK can be supported by setting the BCP register bit. Setting BCP to 1 inverts the polarity of BCLK to the inverse of that shown in Figure 13, Figure 14, etc.

| REGISTER ADDRESS      | BIT | LABEL  | DEFAULT | DESCRIPTION               |

|-----------------------|-----|--------|---------|---------------------------|

| R10 (0Ah)             | 3   | DACBCP | 0       | BCLK Polarity (DSP modes) |

| 0001010               |     |        |         | 0 : normal BCLK polarity  |

| DAC Interface Control |     |        |         | 1: inverted BCLK polarity |

| R11 (0Bh)             | 3   | ADCBCP | 0       |                           |

| 0001011               |     |        |         |                           |

| ADC Interface Control |     |        |         |                           |

The WL[1:0] bits are used to control the input word length.

| REGISTER ADDRESS      | BIT | LABEL | DEFAULT | DESCRIPTION      |

|-----------------------|-----|-------|---------|------------------|

| R10 (0Ah)             | 5:4 | DACWL | 10      | Word Length      |

| 0001010               |     | [1:0] |         | 00 : 16 bit data |

| DAC Interface Control |     |       |         | 01: 20 bit data  |

| R11 (0Bh)             | 5:4 | ADCWL | 10      | 10: 24 bit data  |

| 0001011               |     | [1:0] |         | 11: 32 bit data  |

| ADC Interface Control |     |       |         |                  |

Note: If 32-bit mode is selected in right justified mode, the WM8776 defaults to 24 bits.

In all modes, the data is signed 2's complement. The digital filters always input 24-bit data. If the DAC is programmed to receive 16 or 20 bit data, the WM8776 pads the unused LSBs with zeros. If the DAC is programmed into 32 bit mode, the 8 LSBs are ignored.

**Note:** In 24 bit I<sup>2</sup>S mode, any width of 24 bits or less is supported provided that ADCLRC/DACLRC is high for a minimum of 24 BCLKs and low for a minimum of 24 BCLKs.