# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Complete Data Sheet

DS083 (v5.0) June 21, 2011

## Module 1: Introduction and Overview

#### 10 pages

- Summary of Features

- General Description

- Architecture

- IP Core and Reference Support

- Device/Package Combinations and Maximum I/O

- Ordering Information

## Module 2: Functional Description

#### 60 pages

- Functional Description: RocketIO<sup>™</sup> X Multi-Gigabit Transceiver

- Functional Description: RocketIO Multi-Gigabit

Transceiver

- Functional Description: Processor Block

- Functional Description: PowerPC<sup>™</sup> 405 Core

- Functional Description: FPGA

- Input/Output Blocks (IOBs)

- Digitally Controlled Impedance (DCI)

- On-Chip Differential Termination

- Configurable Logic Blocks (CLBs)

- 3-State Buffers

- CLB/Slice Configurations

- 18-Kb Block SelectRAM™ Resources

- 18-Bit x 18-Bit Multipliers

- Global Clock Multiplexer Buffers

- Digital Clock Manager (DCM)

- Routing

- Configuration

Module 3: DC and Switching Characteristics

#### 59 pages

- Electrical Characteristics

- Performance Characteristics

- Switching Characteristics

- Pin-to-Pin Output Parameter Guidelines

- Pin-to-Pin Input Parameter Guidelines

- DCM Timing Parameters

- Source-Synchronous Switching Characteristics

## Module 4: Pinout Information

#### 302 pages

- Pin Definitions

- Pinout Tables

- FG256/FGG256 Wire-Bond Fine-Pitch BGA Package

- FG456/FGG456 Wire-Bond Fine-Pitch BGA Package

- FG676/FGG676 Wire-Bond Fine-Pitch BGA Package

- FF672 Flip-Chip Fine-Pitch BGA Package

- FF896 Flip-Chip Fine-Pitch BGA Package

- FF1148 Flip-Chip Fine-Pitch BGA Package

- FF1152 Flip-Chip Fine-Pitch BGA Package

- FF1517 Flip-Chip Fine-Pitch BGA Package

- FF1696 Flip-Chip Fine-Pitch BGA Package

- FF1704 Flip-Chip Fine-Pitch BGA Package

IMPORTANT NOTE: Page, figure, and table numbers begin at 1 for each module, and each module has its own Revision History at the end. Use the PDF "Bookmarks" pane for easy navigation in this volume.

© 2000–2011 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. PowerPC is a trademark of IBM Corp. and is used under license. All other trademarks are the property of their respective owners.

www.xilinx.com

Product Specification

## Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Introduction and Overview

DS083 (v5.0) June 21, 2011

#### **Product Specification**

## Summary of Virtex-II Pro™ / Virtex-II Pro X Features

- High-Performance Platform FPGA Solution, Including

- Up to twenty RocketIO<sup>™</sup> or RocketIO X embedded Multi-Gigabit Transceivers (MGTs)

- Up to two IBM PowerPC<sup>™</sup> RISC processor blocks

- Based on Virtex-II<sup>™</sup> Platform FPGA Technology

- Flexible logic resources

- SRAM-based in-system configuration

- Active Interconnect technology

- SelectRAM™+ memory hierarchy

- Dedicated 18-bit x 18-bit multiplier blocks

- High-performance clock management circuitry

- SelectI/O<sup>™</sup>-Ultra technology

- XCITE Digitally Controlled Impedance (DCI) I/O

Virtex-II Pro / Virtex-II Pro X family members and resources are shown in Table 1.

#### Table 1: Virtex-II Pro / Virtex-II Pro X FPGA Family Members

|                       | RocketIO                    | PowerPC             |                               |        | = 4 slices =<br>128 bits) |                      | Block SelectRAM+ |                       |      | Maximum          |

|-----------------------|-----------------------------|---------------------|-------------------------------|--------|---------------------------|----------------------|------------------|-----------------------|------|------------------|

| Device <sup>(1)</sup> | Transceiver<br>Blocks       | Processor<br>Blocks | Logic<br>Cells <sup>(2)</sup> | Slices | Max Distr<br>RAM (Kb)     | Multiplier<br>Blocks | 18 Kb<br>Blocks  | Max Block<br>RAM (Kb) | DCMs | User<br>I/O Pads |

| XC2VP2                | 4                           | 0                   | 3,168                         | 1,408  | 44                        | 12                   | 12               | 216                   | 4    | 204              |

| XC2VP4                | 4                           | 1                   | 6,768                         | 3,008  | 94                        | 28                   | 28               | 504                   | 4    | 348              |

| XC2VP7                | 8                           | 1                   | 11,088                        | 4,928  | 154                       | 44                   | 44               | 792                   | 4    | 396              |

| XC2VP20               | 8                           | 2                   | 20,880                        | 9,280  | 290                       | 88                   | 88               | 1,584                 | 8    | 564              |

| XC2VPX20              | 8(4)                        | 1                   | 22,032                        | 9,792  | 306                       | 88                   | 88               | 1,584                 | 8    | 552              |

| XC2VP30               | 8                           | 2                   | 30,816                        | 13,696 | 428                       | 136                  | 136              | 2,448                 | 8    | 644              |

| XC2VP40               | 0 <sup>(3)</sup> , 8, or 12 | 2                   | 43,632                        | 19,392 | 606                       | 192                  | 192              | 3,456                 | 8    | 804              |

| XC2VP50               | 0 <sup>(3)</sup> or 16      | 2                   | 53,136                        | 23,616 | 738                       | 232                  | 232              | 4,176                 | 8    | 852              |

| XC2VP70               | 16 or 20                    | 2                   | 74,448                        | 33,088 | 1,034                     | 328                  | 328              | 5,904                 | 8    | 996              |

| XC2VPX70              | 20 <sup>(4)</sup>           | 2                   | 74,448                        | 33,088 | 1,034                     | 308                  | 308              | 5,544                 | 8    | 992              |

| XC2VP100              | 0 <sup>(3)</sup> or 20      | 2                   | 99,216                        | 44,096 | 1,378                     | 444                  | 444              | 7,992                 | 12   | 1,164            |

#### Notes:

- 1. -7 speed grade devices are not available in Industrial grade.

- 2. Logic Cell ≈ (1) 4-input LUT + (1)FF + Carry Logic

3. These devices can be ordered in a configuration without RocketIO transceivers. See Table 3 for package configurations.

4. Virtex-II Pro X devices equipped with RocketIO X transceiver cores.

## RocketIO X Transceiver Features (XC2VPX20 and XC2VPX70 Only)

- Variable-Speed Full-Duplex Transceiver (XC2VPX20) Allowing 2.488 Gb/s to 6.25 Gb/s Baud Transfer Rates.

- Includes specific baud rates used by various standards, as listed in Table 4, Module 2.

- Fixed-Speed Full-Duplex Tranceiver (XC2VPX70) Operating at 4.25 Gb/s Baud Transfer Rate.

- Eight or Twenty Transceiver Modules on an FPGA, Depending upon Device

- Monolithic Clock Synthesis and Clock Recovery

- Eliminates the need for external components

- Automatic Lock-to-Reference Function

- Programmable Serial Output Differential Swing

- 200 mV to 1600 mV, peak-peak

- Allows compatibility with other serial system voltage levels

- Programmable Pre-emphasis Levels 0 to 500%

- Telecom/Datacom Support Modes

- "x8" and "x10" clocking/data paths

- 64B/66B clocking support

© 2000–2011 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. PowerPC is a trademark of IBM Corp. and is used under license. All other trademarks are the property of their respective owners.

##

#### Product Not Recommended For New Designs Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Introduction and Overview

- Programmable Receiver Equalization

- Internal AC Coupling

- On-Chip 50Ω Termination

- Eliminates the need for external termination resistors

- Pre- and Post-Driver Serial and Parallel TX-to-RX

## RocketIO Transceiver Features (All Except XC2VPX20 and XC2VPX70)

- Full-Duplex Serial Transceiver (SERDES) Capable of Baud Rates from 600 Mb/s to 3.125 Gb/s

- 100 Gb/s Duplex Data Rate (20 Channels)

- Monolithic Clock Synthesis and Clock Recovery (CDR)

- Fibre Channel, 10G Fibre Channel, Gigabit Ethernet, 10 Gb Attachment Unit Interface (XAUI), and Infiniband-Compliant Transceivers

- 8-, 16-, or 32-bit Selectable Internal FPGA Interface

- 8B/10B Encoder and Decoder (optional)

- PowerPC RISC Processor Block Features (All Except XC2VP2)

- Embedded 300+ MHz Harvard Architecture Block

- Low Power Consumption: 0.9 mW/MHz

- Five-Stage Data Path Pipeline

- Hardware Multiply/Divide Unit

- Thirty-Two 32-bit General Purpose Registers

- 16 KB Two-Way Set-Associative Instruction Cache

- 16 KB Two-Way Set-Associative Data Cache

## Virtex-II Pro Platform FPGA Technology (All Devices)

- SelectRAM+ Memory Hierarchy

- Up to 8 Mb of True Dual-Port RAM in 18 Kb block SelectRAM+ resources

- Up to 1,378 Kb of distributed SelectRAM+ resources

- High-performance interfaces to external memory

- Arithmetic Functions

- Dedicated 18-bit x 18-bit multiplier blocks

- Fast look-ahead carry logic chains

- Flexible Logic Resources

- Up to 88,192 internal registers/latches with Clock Enable

- Up to 88,192 look-up tables (LUTs) or cascadable variable (1 to 16 bits) shift registers

- Wide multiplexers and wide-input function support

- Horizontal cascade chain and Sum-of-Products support

- Internal 3-state busing

- High-Performance Clock Management Circuitry

- Up to twelve Digital Clock Manager (DCM) modules

- Precise clock de-skew

1. Refer to XAPP653 for more information.

- Internal Loopback Modes for Testing Operability

- Programmable Comma Detection

- Allows for any protocol

- Allows for detection of any 10-bit character

- 8B/10B and 64B/66B Encoding Blocks

- $50\Omega/75\Omega$  on-chip Selectable Transmit and Receive Terminations

- Programmable Comma Detection

- Channel Bonding Support (from 2 to 20 Channels)

- Rate Matching via Insertion/Deletion Characters

- Four Levels of Selectable Pre-Emphasis

- Five Levels of Output Differential Voltage

- Per-Channel Internal Loopback Modes

- 2.5V Transceiver Supply Voltage

- Memory Management Unit (MMU)

- 64-entry unified Translation Look-aside Buffers (TLB)

- Variable page sizes (1 KB to 16 MB)

- Dedicated On-Chip Memory (OCM) Interface

- Supports IBM CoreConnect™ Bus Architecture

- Debug and Trace Support

- Timer Facilities

- · Flexible frequency synthesis

- High-resolution phase shifting

- 16 global clock multiplexer buffers in all parts

- Active Interconnect Technology

- Fourth-generation segmented routing structure

- Fast, predictable routing delay, independent of fanout

- Deep sub-micron noise immunity benefits

- SelectIO™-Ultra Technology

- Up to 1,164 user I/Os

- Twenty-two single-ended standards and ten differential standards

- Programmable LVCMOS sink/source current (2 mA to 24 mA) per I/O

- XCITE Digitally Controlled Impedance (DCI) I/O

- PCI/PCI-X support <sup>(1)</sup>

- Differential signaling

- 840 Mb/s Low-Voltage Differential Signaling I/O (LVDS) with current mode drivers

- On-chip differential termination

- Bus LVDS I/O

vices)

- HyperTransport (LDT) I/O with current driver buffers

- Built-in DDR input and output registers

- Proprietary high-performance SelectLink technology for communications between Xilinx devices

- · High-bandwidth data path

- Double Data Rate (DDR) link

- Web-based HDL generation methodology

- SRAM-Based In-System Configuration

- Fast SelectMAP<sup>™</sup> configuration

- Triple Data Encryption Standard (DES) security option (bitstream encryption)

- IEEE 1532 support

- Partial reconfiguration

- Unlimited reprogrammability

- Readback capability

- Supported by Xilinx Foundation<sup>™</sup> and Alliance Series<sup>™</sup> Development Systems

- Integrated VHDL and Verilog design flows

- ChipScope™ Integrated Logic Analyzer

- 0.13 µm Nine-Layer Copper Process with 90 nm High-Speed Transistors

- 1.5V (V<sub>CCINT</sub>) core power supply, dedicated 2.5V V<sub>CCAUX</sub> auxiliary and V<sub>CCO</sub> I/O power supplies

- IEEE 1149.1 Compatible Boundary-Scan Logic Support

- Flip-Chip and Wire-Bond Ball Grid Array (BGA) Packages in Standard 1.00 mm Pitch.

- Wire-Bond BGA Devices Available in Pb-Free Packaging (<u>www.xilinx.com/pbfree</u>)

- Each Device 100% Factory Tested

## **General Description**

The Virtex-II Pro and Virtex-II Pro X families contain platform FPGAs for designs that are based on IP cores and customized modules. The family incorporates multi-gigabit transceivers and PowerPC CPU blocks in Virtex-II Pro Series FPGA architecture. It empowers complete solutions for telecommunication, wireless, networking, video, and DSP applications.

The leading-edge  $0.13 \,\mu\text{m}$  CMOS nine-layer copper process and Virtex-II Pro architecture are optimized for high performance designs in a wide range of densities. Combining a wide variety of flexible features and IP cores, the Virtex-II Pro family enhances programmable logic design capabilities and is a powerful alternative to mask-programmed gate arrays.

## Architecture

#### **Array Overview**

Virtex-II Pro and Virtex-II Pro X devices are user-programmable gate arrays with various configurable elements and embedded blocks optimized for high-density and high-performance system designs. Virtex-II Pro devices implement the following functionality:

- Embedded high-speed serial transceivers enable data bit rate up to 3.125 Gb/s per channel (RocketIO) or 6.25 Gb/s (RocketIO X).

- Embedded IBM PowerPC 405 RISC processor blocks provide performance up to 400 MHz.

- SelectIO-Ultra blocks provide the interface between package pins and the internal configurable logic. Most popular and leading-edge I/O standards are supported by the programmable IOBs.

- Configurable Logic Blocks (CLBs) provide functional elements for combinatorial and synchronous logic, including basic storage elements. BUFTs (3-state buffers) associated with each CLB element drive dedicated segmentable horizontal routing resources.

- Block SelectRAM+ memory modules provide large 18 Kb storage elements of True Dual-Port RAM.

- Embedded multiplier blocks are 18-bit x 18-bit dedicated multipliers.

- Digital Clock Manager (DCM) blocks provide self-calibrating, fully digital solutions for clock distribution delay compensation, clock multiplication and division, and coarse- and fine-grained clock phase shifting.

A new generation of programmable routing resources called Active Interconnect Technology interconnects all these elements. The general routing matrix (GRM) is an array of routing switches. Each programmable element is tied to a switch matrix, allowing multiple connections to the general routing matrix. The overall programmable interconnection is hierarchical and supports high-speed designs.

All programmable elements, including the routing resources, are controlled by values stored in static memory cells. These values are loaded in the memory cells during configuration and can be reloaded to change the functions of the programmable elements.

#### **Features**

This section briefly describes Virtex-II Pro / Virtex-II Pro X features. For more details, refer to Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description.

#### RocketIO / RocketIO X MGT Cores

The RocketIO and RocketIO X Multi-Gigabit Transceivers are flexible parallel-to-serial and serial-to-parallel embedded transceiver cores used for high-bandwidth interconnection between buses, backplanes, or other subsystems.

Multiple user instantiations in an FPGA are possible, providing up to 100 Gb/s (RocketIO) or 170 Gb/s (RocketIO X) of full-duplex raw data transfer. Each channel can be operated at a maximum data transfer rate of 3.125 Gb/s (RocketIO) or 6.25 Gb/s (RocketIO X).

Each RocketIO or RocketIO X core implements the following technology:

- Serializer and deserializer (SERDES)

- Monolithic clock synthesis and clock recovery (CDR)

- 10 Gigabit Attachment Unit Interface (XAUI) Fibre Channel (3.1875 Gb/s XAUI), Infiniband, PCI Express, Aurora, SXI-5 (SFI-5,/SPI-5), and OC-48 compatibility<sup>(1)</sup>

- 8/16/32-bit (RocketIO) or 8/16/32/64-bit (RocketIO X) selectable FPGA interface

- 8B/10B (RocketIO) or 8B/10B and 64B/66B (RocketIO X) encoder and decoder with bypassing option on each channel

- Channel bonding support (two to twenty channels)

- Elastic buffers for inter-chip deskewing and channel-to-channel alignment

- Receiver clock recovery tolerance of up to 75 non-transitioning bits

- 50Ω (RocketIO X) or 50Ω /75Ω selectable (RocketIO) on-chip transmit and receive terminations

- Programmable comma detection and word alignment

- Rate matching via insertion/deletion characters

- Automatic lock-to-reference function

- Programmable pre-emphasis support

- Per-channel serial and parallel transmitter-to-receiver internal loopback modes

- Optional transmit and receive data inversion

- Cyclic Redundancy Check support (RocketIO only)

#### PowerPC 405 Processor Block

The PPC405 RISC CPU can execute instructions at a sustained rate of one instruction per cycle. On-chip instruction and data cache reduce design complexity and improve system throughput.

The PPC405 features include:

- PowerPC RISC CPU

- Implements the PowerPC User Instruction Set Architecture (UISA) and extensions for embedded applications

- Thirty-two 32-bit general purpose registers (GPRs)

- Static branch prediction

- Five-stage pipeline with single-cycle execution of most instructions, including loads/stores

- Unaligned and aligned load/store support to cache, main memory, and on-chip memory

- Hardware multiply/divide for faster integer arithmetic (4-cycle multiply, 35-cycle divide)

- Enhanced string and multiple-word handling

- Big/little endian operation support

- Storage Control

- Separate instruction and data cache units, both two-way set-associative and non-blocking

- Eight words (32 bytes) per cache line

- 16 KB array Instruction Cache Unit (ICU), 16 KB array Data Cache Unit (DCU)

- Operand forwarding during instruction cache line fill

- Copy-back or write-through DCU strategy

- Doubleword instruction fetch from cache improves branch latency

- Virtual mode memory management unit (MMU)

- Translation of the 4 GB logical address space into physical addresses

- Software control of page replacement strategy

- Supports multiple simultaneous page sizes ranging from 1 KB to 16 MB

- OCM controllers provide dedicated interfaces between Block SelectRAM+ memory and processor block instruction and data paths for high-speed access

- PowerPC timer facilities

- 64-bit time base

- Programmable interval timer (PIT)

- Fixed interval timer (FIT)

- Watchdog timer (WDT)

- Debug Support

- Internal debug mode

- External debug mode

- Debug Wait mode

- Real Time Trace debug mode

- Enhanced debug support with logical operators

- Instruction trace and trace-back support

- Forward or backward trace

- Two hardware interrupt levels support

- Advanced power management support

#### Input/Output Blocks (IOBs)

IOBs are programmable and can be categorized as follows:

- Input block with an optional single data rate (SDR) or double data rate (DDR) register

- Output block with an optional SDR or DDR register and an optional 3-state buffer to be driven directly or through an SDR or DDR register

- Bidirectional block (any combination of input and output configurations)

These registers are either edge-triggered D-type flip-flops or level-sensitive latches.

IOBs support the following single-ended I/O standards:

- LVTTL, LVCMOS (3.3V,<sup>(2)</sup> 2.5V, 1.8V, and 1.5V)

- PCI-X compatible (133 MHz and 66 MHz) at 3.3V<sup>(3)</sup>

- PCI compliant (66 MHz and 33 MHz) at 3.3V<sup>(3)</sup>

- GTL and GTLP

<sup>1.</sup> Refer to Table 4, Module 2 for detailed information about RocketIO and RocketIO X transceiver compatible protocols.

<sup>2.</sup> Refer to XAPP659 for more information.

<sup>3.</sup> Refer to XAPP653 for more information.

- HSTL (1.5V and 1.8V, Class I, II, III, and IV)

- SSTL (1.8V and 2.5V, Class I and II)

The DCI I/O feature automatically provides on-chip termination for each single-ended I/O standard.

The IOB elements also support the following differential signaling I/O standards:

- LVDS and Extended LVDS (2.5V)

- BLVDS (Bus LVDS)

- ULVDS

- LDT

- LVPECL (2.5V)

Two adjacent pads are used for each differential pair. Two or four IOBs connect to one switch matrix to access the routing resources. On-chip differential termination is available for LVDS, LVDS Extended, ULVDS, and LDT standards.

#### Configurable Logic Blocks (CLBs)

CLB resources include four slices and two 3-state buffers. Each slice is equivalent and contains:

- Two function generators (F & G)

- Two storage elements

- Arithmetic logic gates

- Large multiplexers

- Wide function capability

- Fast carry look-ahead chain

- Horizontal cascade chain (OR gate)

The function generators F & G are configurable as 4-input look-up tables (LUTs), as 16-bit shift registers, or as 16-bit distributed SelectRAM+ memory.

In addition, the two storage elements are either edge-triggered D-type flip-flops or level-sensitive latches.

Each CLB has internal fast interconnect and connects to a switch matrix to access general routing resources.

#### Block SelectRAM+ Memory

The block SelectRAM+ memory resources are 18 Kb of True Dual-Port RAM, programmable from 16K x 1 bit to 512 x 36 bit, in various depth and width configurations. Each port is totally synchronous and independent, offering three "read-during-write" modes. Block SelectRAM+ memory is cascadable to implement large embedded storage blocks. Supported memory configurations for dual-port and single-port modes are shown in Table 2.

#### Table 2: Dual-Port and Single-Port Configurations

| 16K x 1 bit | 4K x 4 bits | 1K x 18 bits  |

|-------------|-------------|---------------|

| 8K x 2 bits | 2K x 9 bits | 512 x 36 bits |

#### 18 X 18 Bit Multipliers

A multiplier block is associated with each SelectRAM+ memory block. The multiplier block is a dedicated 18 x 18-bit 2s complement signed multiplier, and is optimized for operations based on the block SelectRAM+ content on one port. The 18 x 18 multiplier can be used independently of the block SelectRAM+ resource. Read/multiply/accumulate operations and DSP filter structures are extremely efficient.

Both the SelectRAM+ memory and the multiplier resource are connected to four switch matrices to access the general routing resources.

#### Global Clocking

The DCM and global clock multiplexer buffers provide a complete solution for designing high-speed clock schemes.

Up to twelve DCM blocks are available. To generate deskewed internal or external clocks, each DCM can be used to eliminate clock distribution delay. The DCM also provides 90-, 180-, and 270-degree phase-shifted versions of its output clocks. Fine-grained phase shifting offers high-resolution phase adjustments in increments of  $1/_{256}$  of the clock period. Very flexible frequency synthesis provides a clock output frequency equal to a fractional or integer multiple of the input clock frequency. For exact timing parameters, see Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics.

Virtex-II Pro devices have 16 global clock MUX buffers, with up to eight clock nets per quadrant. Each clock MUX buffer can select one of the two clock inputs and switch glitch-free from one clock to the other. Each DCM can send up to four of its clock outputs to global clock buffers on the same edge. Any global clock pin can drive any DCM on the same edge.

#### **Routing Resources**

The IOB, CLB, block SelectRAM+, multiplier, and DCM elements all use the same interconnect scheme and the same access to the global routing matrix. Timing models are shared, greatly improving the predictability of the performance of high-speed designs.

There are a total of 16 global clock lines, with eight available per quadrant. In addition, 24 vertical and horizontal long lines per row or column, as well as massive secondary and local routing resources, provide fast interconnect. Virtex-II Pro buffered interconnects are relatively unaffected by net fanout, and the interconnect layout is designed to minimize crosstalk.

Horizontal and vertical routing resources for each row or column include:

- 24 long lines

- 120 hex lines

- 40 double lines

- 16 direct connect lines (total in all four directions)

#### **Boundary Scan**

Boundary-scan instructions and associated data registers support a standard methodology for accessing and configuring Virtex-II Pro devices, complying with IEEE standards 1149.1 and 1532. A system mode and a test mode are implemented. In system mode, a Virtex-II Pro device will continue to function while executing non-test Boundary-Scan instructions. In test mode, Boundary-Scan test instructions control the I/O pins for testing purposes. The Virtex-II Pro Test Access Port (TAP) supports BYPASS, PRELOAD, SAMPLE, IDCODE, and USERCODE non-test instructions. The EXTEST, INTEST, and HIGHZ test instructions are also supported.

#### Configuration

Virtex-II Pro / Virtex-II Pro devices are configured by loading the bitstream into internal configuration memory using one of the following modes:

- Slave-serial mode

- Master-serial mode

- Slave SelectMAP mode

- Master SelectMAP mode

- Boundary-Scan mode (IEEE 1532)

A Data Encryption Standard (DES) decryptor is available on-chip to secure the bitstreams. One or two triple-DES key sets can be used to optionally encrypt the configuration data.

The Xilinx System Advanced Configuration Environment (System ACE) family offers high-capacity and flexible solution for FPGA configuration as well as program/data storage for the processor. See <u>DS080</u>, *System ACE CompactFlash Solution* for more information.

#### Readback and Integrated Logic Analyzer

Configuration data stored in Virtex-II Pro / Virtex-II Pro configuration memory can be read back for verification. Along with the configuration data, the contents of all flip-flops and latches, distributed SelectRAM+, and block SelectRAM+ memory resources can be read back. This capability is useful for real-time debugging. The Xilinx ChipScope Integrated Logic Analyzer (ILA) cores and Integrated Bus Analyzer (IBA) cores, along with the ChipScope Pro Analyzer software, provide a complete solution for accessing and verifying user designs within Virtex-II Pro devices.

## **IP Core and Reference Support**

Intellectual Property is part of the Platform FPGA solution. In addition to the existing FPGA fabric cores, the list below shows some of the currently available hardware and software intellectual properties specially developed for Virtex-II Pro / Virtex-II Pro X by Xilinx. Each IP core is modular, portable, Real-Time Operating System (RTOS) independent, and CoreConnect compatible for ease of design migration. Refer to <u>www.xilinx.com/ipcenter</u> for the latest and most complete list of cores.

#### Hardware Cores

- Bus Infrastructure cores (arbiters, bridges, and more)

- Memory cores (DDR, Flash, and more)

- Peripheral cores (UART, IIC, and more)

- Networking cores (ATM, Ethernet, and more)

#### **Software Cores**

- Boot code

- Test code

- Device drivers

- Protocol stacks

- RTOS integration

- Customized board support package

## Virtex-II Pro / Virtex-II Pro X Device/Package Combinations and Maximum I/Os

Offerings include ball grid array (BGA) packages with 1.0 mm pitch. In addition to traditional wire-bond interconnect (FG/FGG packages), flip-chip interconnect (FF packages) is used in some of the BGA offerings. Flip-chip interconnect construction supports more I/Os than are possible in wire-bond versions of similar packages, providing a high pin count and excellent power dissipation.

The device/package combination table (Table 3) details the maximum number of user I/Os and RocketIO / RocketIO X MGTs for each device and package using wire-bond or flip-chip technology.

The FF1148 and FF1696 packages have no RocketIO transceivers bonded out. Extra SelectIO-Ultra resources occupy available pins in these packages, resulting in a higher user I/O count. These packages are available for the XC2VP40, XC2VP50, and XC2VP100 devices only.

The I/Os per package count includes all user I/Os except the 15 control pins (CCLK, DONE, M0, M1, M2, PROG\_B, PWRDWN\_B, TCK, TDI, TDO, TMS, HSWAP\_EN, DXN, DXP, and RSVD), VBATT, and the RocketIO / RocketIO X transceiver pins.

| Package <sup>(1)</sup> | FG256/<br>FGG256 | FG456/<br>FGG456 | FG676   | FF672   | FF896                | FF1152  | FF1148   | FF1517  | FF1704      | FF1696                 |

|------------------------|------------------|------------------|---------|---------|----------------------|---------|----------|---------|-------------|------------------------|

| Pitch (mm)             | 1.00             | 1.00             | 1.00    | 1.00    | 1.00                 | 1.00    | 1.00     | 1.00    | 1.00        | 1.00                   |

| Size (mm)              | 17 x 17          | 23 x 23          | 26 x 26 | 27 x 27 | 31 x 31              | 35 x 35 | 35 x 35  | 40 x 40 | 42.5 x 42.5 | 42.5 x 42.5            |

| XC2VP2                 | 140/4            | 156/4            |         | 204/4   |                      |         |          |         |             |                        |

| XC2VP4                 | 140/4            | 248/4            |         | 348/4   |                      |         |          |         |             |                        |

| XC2VP7                 |                  | 248/8            |         | 396/8   | 396/8                |         |          |         |             |                        |

| XC2VP20                |                  |                  | 404/8   |         | 556/8                | 564/8   |          |         |             |                        |

| XC2VPX20               |                  |                  |         |         | 552/8 <sup>(2)</sup> |         |          |         |             |                        |

| XC2VP30                |                  |                  | 416/8   |         | 556/8                | 644/8   |          |         |             |                        |

| XC2VP40                |                  |                  | 416/8   |         |                      | 692/12  | 804/0(3) |         |             |                        |

| XC2VP50                |                  |                  |         |         |                      | 692/16  | 812/0(3) | 852/16  |             |                        |

| XC2VP70                |                  |                  |         |         |                      |         |          | 964/16  | 996/20      |                        |

| XC2VPX70               |                  |                  |         |         |                      |         |          |         | 992/20(2)   |                        |

| XC2VP100               |                  |                  |         |         |                      |         |          |         | 1,040/20    | 1,164/0 <sup>(3)</sup> |

#### Table 3: Virtex-II Pro Device/Package Combinations and Maximum Number of Available I/Os

#### Notes:

1. Wirebond packages FG256, FG456, and FG676 are also available in Pb-free versions FGG256, FGG456, and FGG676. See Virtex-II Pro Ordering Examples for details on how to order.

2. Virtex-II Pro X device is equipped with RocketIO X transceiver cores.

3. The RocketIO transceivers in devices in the FF1148 and FF1696 packages are not bonded out to the package pins.

## Maximum Performance

Maximum performance of the RocketIO / RocketIO X transceiver and the PowerPC processor block varies, depending on package style and speed grade. See Table 4 for details. Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics contains the rest of the FPGA fabric performance parameters.

#### Table 4: Maximum RocketIO / RocketIO X Transceiver and Processor Block Performance

| Device                               | <b>-7</b> <sup>(1)</sup> | -6                  | -5                  | Units |

|--------------------------------------|--------------------------|---------------------|---------------------|-------|

| RocketIO X Transceiver FlipChip (FF) | N/A                      | 6.25 <sup>(3)</sup> | 4.25 <sup>(3)</sup> | Gb/s  |

| RocketIO Transceiver FlipChip (FF)   | 3.125                    | 3.125               | 2.0                 | Gb/s  |

| RocketIO Transceiver Wirebond (FG)   | 2.5                      | 2.5                 | 2.0                 | Gb/s  |

| PowerPC Processor Block              | 400 <sup>(2)</sup>       | 350 <sup>(2)</sup>  | 300                 | MHz   |

#### Notes:

1. -7 speed grade devices are not available in Industrial grade.

2. IMPORTANT! When CPMC405CLOCK runs at speeds greater than 350 MHz in -7 Commercial grade dual-processor devices, or greater than 300 MHz in -6 Industrial grade dual-processor devices, users must implement the technology presented in <u>XAPP755</u>, "PowerPC 405 Clock Macro for -7(C) and -6(I) Speed Grade Dual-Processor Devices." Refer to Table 1 to identify dual-processor devices.

3. XC2VPX70 is only available at fixed 4.25 Gb/s baud rate.

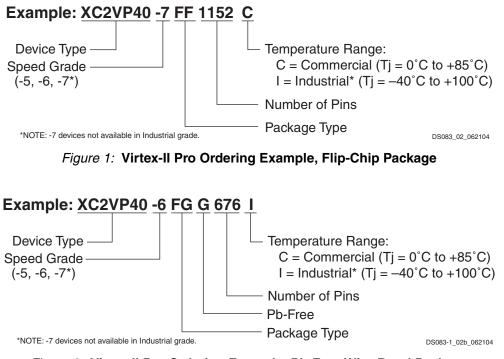

## Virtex-II Pro Ordering Examples

Virtex-II Pro ordering examples are shown in Figure 1 (flip-chip package) and Figure 2 (Pb-free wire-bond package).

Figure 2: Virtex-II Pro Ordering Example, Pb-Free Wire-Bond Package

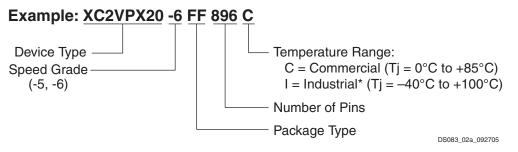

## Virtex-II Pro X Ordering Example

A Virtex-II Pro X ordering example is shown in Figure 3.

Figure 3: Virtex-II Pro X Ordering Example, Flip-Chip Package

## **Revision History**

This section records the change history for this module of the data sheet.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 01/31/02 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 06/13/02 | 2.0     | New Virtex-II Pro family members. New timing parameters per speedsfile v1.62.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 09/03/02 | 2.1     | Updates to Table 1 and Table 3. Processor Block information added to Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 09/27/02 | 2.2     | In Table 1, correct max number of XC2VP30 I/Os to 644.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 11/20/02 | 2.3     | Add bullet items for 3.3V I/O features.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 01/20/03 | 2.4     | <ul> <li>In Table 3, add FG676 package option for XC2VP20, XC2VP30, and XC2VP40.</li> <li>Remove FF1517 package option for XC2VP40.</li> </ul>                                                                                                                                                                                                                                                                                                                                                  |  |

| 03/24/03 | 2.4.1   | <ul> <li>Correct number of single-ended I/O standards from 19 to 22.</li> <li>Correct minimum RocketIO serial speed from 622 Mbps to 600 Mbps.</li> </ul>                                                                                                                                                                                                                                                                                                                                       |  |

| 08/25/03 | 2.4.2   | Add footnote referring to XAPP659 to callout for 3.3V I/O standards on page 4.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 12/10/03 | 3.0     | • XC2VP2 through XC2VP70 speed grades -5, -6, and -7, and XC2VP100 speed grades -5 and -6, are released to <b>Production status</b> .                                                                                                                                                                                                                                                                                                                                                           |  |

| 02/19/04 | 3.1     | <ul> <li>Table 1: Corrected number of RocketIO transceiver blocks for XC2VP40.</li> <li>Section Virtex-II Pro Platform FPGA Technology (All Devices): Updated number of differential standards supported from six to ten.</li> <li>Section Input/Output Blocks (IOBs): Added text stating that differential termination is available for LVDS, LVDS Extended, ULVDS, and LDT standards.</li> <li>Figure 1: Added note stating that -7 devices are not available in Industrial grade.</li> </ul> |  |

| 03/09/04 | 3.1.1   | • Recompiled for backward compatibility with Acrobat 4 and above. No content changes.                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 06/30/04 | 4.0     | Merged in DS110-1 (Module 1 of Virtex-II Pro X data sheet). Added information on available Pb-free packages.                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 11/17/04 | 4.1     | No changes in Module 1 for this revision.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 03/01/05 | 4.2     | Table 3: Corrected number of RocketIO transceivers for XC2VP7-FG456.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 06/20/05 | 4.3     | No changes in Module 1 for this revision.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 09/15/05 | 4.4     | <ul> <li>Changed all instances of 10.3125 Gb/s (RocketIO transceiver maximum bit rate) to 6.25 Gb/s.</li> <li>Changed all instances of 412.5 Gb/s (RocketIO X transceiver maximum multi-channel raw data transfer rate) to 250 Gb/s.</li> </ul>                                                                                                                                                                                                                                                 |  |

| 10/10/05 | 4.5     | <ul> <li>Changed XC2VPX70 variable baud rate specification to fixed-rate operation at 4.25 Gb/s.</li> <li>Changed maximum performance for -7 Virtex-II Pro X MGT (Table 4) to N/A.</li> </ul>                                                                                                                                                                                                                                                                                                   |  |

| 03/05/07 | 4.6     | No changes in Module 1 for this revision.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 11/05/07 | 4.7     | Updated copyright notice and legal disclaimer.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 06/21/11 | 5.0     | Added Product Not Recommended for New Designs banner.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

## **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

## **Virtex-II Pro Data Sheet**

The Virtex-II Pro Data Sheet contains the following modules:

- Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Introduction and Overview (Module 1)

- Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description (Module 2)

- Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics (Module 3)

- Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Pinout Information (Module 4)

## Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description

DS083 (v5.0) June 21, 2011

#### **Product Specification**

## Virtex-II Pro<sup>(1)</sup> Array Functional Description

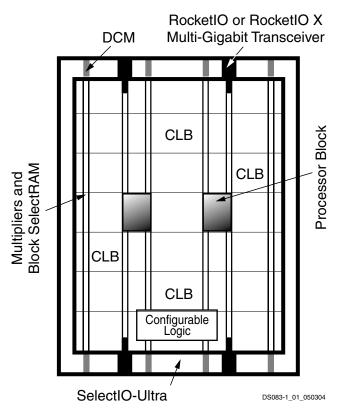

#### Figure 1: Virtex-II Pro Generic Architecture Overview

This module describes the following Virtex<sup>™</sup>-II Pro functional components, as shown in Figure 1:

- Embedded RocketIO<sup>™</sup> (up to 3.125 Gb/s) or RocketIO X (up to 6.25 Gb/s) Multi-Gigabit Transceivers (MGTs)

- Processor blocks with embedded IBM PowerPC<sup>™</sup> 405 RISC CPU core (PPC405) and integration circuitry.

- FPGA fabric based on Virtex-II architecture.

#### **Virtex-II Pro User Guides**

Virtex-II Pro User Guides cover theory of operation in more detail, and include implementation details, primitives and attributes, command/instruction sets, and many HDL code examples where appropriate. All parameter specifications are given only in Module 3 of this Data Sheet.

These User Guides are available:

- For detailed descriptions of PPC405 embedded core programming models and internal core operations, see <u>PowerPC Processor Reference Guide</u> and <u>PowerPC</u> 405 Processor Block Reference Guide.

- For detailed RocketIO transceiver digital/analog design considerations, see RocketIO Transceiver User Guide.

- For detailed RocketIO X transceiver digital/analog design considerations, see <u>RocketIO X Transceiver</u> <u>User Guide</u>,

- For detailed descriptions of the FPGA fabric (CLB, IOB, DCM, etc.), see <u>Virtex-II Pro Platform FPGA User</u> <u>Guide</u>.

All of the documents above, as well as a complete listing and description of Xilinx-developed Intellectual Property cores for Virtex-II Pro, are available on the Xilinx website.

#### **Contents of This Module**

- Functional Description: RocketIO X Multi-Gigabit Transceiver (MGT)

- Functional Description: RocketIO Multi-Gigabit Transceiver (MGT)

- Functional Description: Processor Block

- Functional Description: Embedded PowerPC 405 Core

- Functional Description: FPGA

- Revision History

#### Virtex-II Pro Compared to Virtex-II Devices

Virtex-II Pro devices are built on the Virtex-II FPGA architecture. Most FPGA features are identical to Virtex-II devices. Major differences are described below:

- The Virtex-II Pro FPGA family is the first to incorporate embedded PPC405 and RocketIO/RocketIO X cores.

- $V_{CCAUX}$ , the auxiliary supply voltage, is 2.5V instead of 3.3V as for Virtex-II devices. Advanced processing at 0.13  $\mu$ m has resulted in a smaller die, faster speed, and lower power consumption.

- Virtex-II Pro devices are neither bitstream-compatible nor pin-compatible with Virtex-II devices. However, Virtex-II designs can be compiled into Virtex-II Pro devices.

- On-chip input LVDS differential termination is available.

- SSTL3, AGP-2X/AGP, LVPECL\_33, LVDS\_33, and LVDSEXT\_33 standards are not supported.

- The open-drain output pin TDO does not have an internal pull-up resistor.

<sup>1.</sup> Unless otherwise noted, "Virtex-II Pro" refers to members of the Virtex-II Pro and/or Virtex-II Pro X families.

<sup>© 2000–2011</sup> Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. PowerPC is a trademark of IBM Corp. and is used under license. All other trademarks are the property of their respective owners.

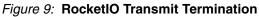

## Functional Description: RocketIO X Multi-Gigabit Transceiver (MGT)

This section summarizes the features of the RocketIO X multi-gigabit transceiver. For an in-depth discussion of the RocketIO X MGT, including digital and analog design considerations, refer to the <u>RocketIO X Transceiver User</u> <u>Guide.</u>

#### **RocketIO X Overview**

Either eight or twenty RocketIO X MGTs are available on the XC2VPX20 and XC2VPX70 devices, respectively. The XC2VPX20 MGT is designed to operate at any baud rate in the range of 2.488 Gb/s to 6.25 Gb/s per channel. This includes specific baud rates used by various standards as listed in Table 1. The XC2VPX70 MGT operates at a fixed 4.25 Gb/s per channel.

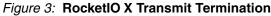

The RocketIO X MGT consists of the *Physical Media Attachment* (PMA) and *Physical Coding Sublayer* (PCS). The PMA contains the 6.25 Gb/s serializer/deserializer (SERDES), TX/RX buffers, clock generator, and clock recovery circuitry. The RocketIO X PCS has been significantly updated relative to the RocketIO PCS. In addition to the existing RocketIO PCS features, the RocketIO X PCS features 64B/66B encoder/decoder/scrambler/descrambler and SONET compatibility.

#### **PMA**

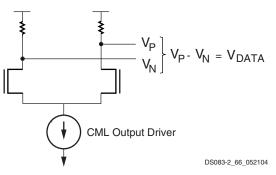

#### Transmitter Output

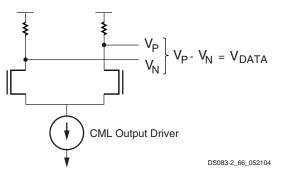

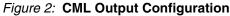

The RocketIOX transceiver is implemented in *Current Mode Logic* (CML). A CML transmitter output consists of transistors configured as shown in Figure 2. CML uses a positive supply and offers easy interface requirements. In this configuration, both legs of the driver, VP and VN, sink current, with one leg always sinking more current than its complement. The CML output consists of a differential pair with 50 $\Omega$  source resistors. The signal swing is created by switching the current in a common-source differential pair.

See Table 7, page 17, for a summary of the differences between the RocketIO X PMA/PCS and the RocketIO PMA/PCS.

Figure 4, page 3 shows a high-level block diagram of the RocketIO X transceiver and its FPGA interface signals.

| Table | 1:   | Communications Standards Supported by |

|-------|------|---------------------------------------|

| Rock  | etIC | ) X Transceiver <sup>(2)</sup>        |

| Mode                       | Channels<br>(Lanes) <sup>(1)</sup> | I/O Bit Rate<br>(Gb/s) |

|----------------------------|------------------------------------|------------------------|

| SONET OC-48                | 1                                  | 2.488                  |

| PCI Express                | 1, 2, 4, 8, 16                     | 2.5                    |

| Infiniband                 | 1, 4, 12                           | 2.5                    |

| XAUI (10-Gb Ethernet)      | 4                                  | 3.125                  |

| XAUI (10-Gb Fibre Channel) | 4                                  | 3.1875                 |

| Aurora (Xilinx protocol)   | 1, 2, 3, 4,                        | 2.488 to 6.25          |

| Custom Mode                | 1, 2, 3, 4,                        | 2.488 to 6.25          |

Notes:

- 1. One channel is considered to be one transceiver.

- 2. XC2VPX70 operates at a fixed 4.25 Gb/s baud rate.

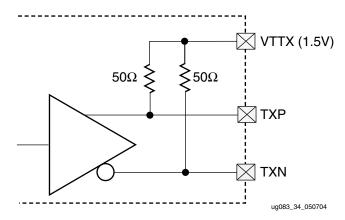

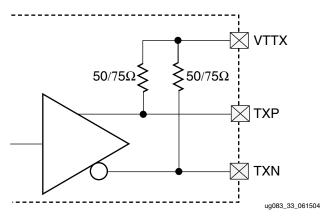

#### Transmitter Termination

On-chip termination is provided at the transmitter, eliminating the need for external termination. The output driver and termination are powered by  $V_{TTX}$  at 1.5V. This configuration uses a CML approach with 50 $\Omega$  termination to TXP and TXN as shown in Figure 3.

#### Figure 4: RocketIO X Transceiver Block Diagram

#### **Output Swing and Emphasis**

The output swing and emphasis levels are fully programmable. Each is controlled via attributes at configuration, and can be modified via the PMA attribute programming bus.

The programmable output swing control can adjust the differential peak-to-peak output level between 200 mV and 1600 mV.

With emphasis, the differential voltage swing is boosted to create a stronger rising or falling waveform. This method compensates for high frequency loss in the transmission media that would otherwise limit the magnitude of this waveform. Lossy transmission lines cause the dissipation of electrical energy. This emphasis technique extends the distance that signals can be driven down lossy line media and increases the signal-to-noise ratio at the receiver.

Emphasis can be described from two perspectives, additive to the smaller voltage ( $V_{SM}$ ) (pre-emphasis) or subtractive from the larger voltage ( $V_{LG}$ ) (de-emphasis). The resulting benefits in compensating for channel loss are identical. It is simply a relative way of specifying the effect at the transmitter.

The equations for calculating pre-emphasis as a percentage and dB are as follows:

$\begin{aligned} \text{Pre-Emphasis}_{\&} &= ((V_{LG} - V_{SM}) / V_{SM}) \times 100 \\ \text{Pre-Emphasis}_{dB} &= 20 \log(V_{LG} / V_{SM}) \end{aligned}$

The equations for calculating de-emphasis as a percentage and dB are as follows:

The pre-emphasis amount can be programmed in discrete steps between 0% and 500%. The de-emphasis amount can be programmed in discrete steps between 0% and 83%.

#### Serializer

The serializer multiplies the reference frequency provided on REFCLK by 10, 16, 20, 32, or 40, depending on the operation mode. The multiplication of the clock is achieved by using an embedded PLL.

Data is converted from parallel to serial format and transmitted on the TXP and TXN differential outputs. The electrical connection of TXP and TXN can be interchanged through configuration. This option can be controlled by an input (TXPOLARITY) at the FPGA transmitter interface.

#### Deserializer

Synchronous serial data reception is facilitated by a clock and data recovery (CDR) circuit. This circuit uses a fully monolithic Phase Lock Loop (PLL), which does not require any external components. The CDR circuit extracts both phase and frequency from the incoming data stream.

The derived clock, RXRECCLK, is generated and locked to as long as it remains within the specified component range.

This clock is presented to the FPGA fabric at 1/10, 1/16, 1/20, 1/32, or 1/40 the incoming data rate depending on the operating mode.

A sufficient number of transitions must be present in the data stream for CDR to work properly. The CDR circuit is guaranteed to work with 8B/10B and 64B/66B encoding. Further, CDR requires approximately 5,000 transitions upon power-up to guarantee locking to the incoming data rate. Once lock is achieved, up to 75 missing transitions can be tolerated before lock to the incoming data stream is lost.

Another feature of CDR is its ability to accept an external precision reference clock, REFCLK, which either acts to clock incoming data or to assist in synchronizing the derived RXRECCLK.

For further clarity, the TXUSRCLK is used to clock data from the FPGA fabric to the TX FIFO. The FIFO depth accounts for the slight phase difference between these two clocks. If the clocks are locked in frequency, then the FIFO acts much like a pass-through buffer.

The receiver can be configured to reverse the RXP and RXN inputs. This can be useful in the event that printed circuit board traces have been reversed.

#### **Receiver Lock Control**

The CDR circuits will lock to the reference clock automatically if the data is not present. For proper operation, the frequency of the reference clock must be within  $\pm 100$  ppm of the nominal frequency.

During normal operation, the receiver PLL automatically locks to incoming data (when present) or to the local reference clock (when data is not present). This is the default configuration for all primitives. This function can be overridden via the PMARXLOCKSEL port

When receive PLL lock is forced to the local reference, phase information from the incoming data stream is ignored. Data continues to be sampled, but synchronous to the local reference rather than relative to edges in the data stream.

#### **Receive Equalization**

In addition to transmit emphasis, the RocketIO X MGT provides a programmable active receive equalization feature to further compensate the effects of channel attenuation at high frequencies.

By adjusting RXFER, the right amount of equalization can be added to reverse the signal degradation caused by a printed circuit board, a backplane, or a line/switch card. RXFER can be set through software configuration or the PMA Attribute Bus.

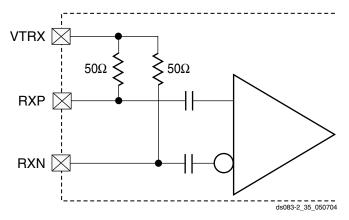

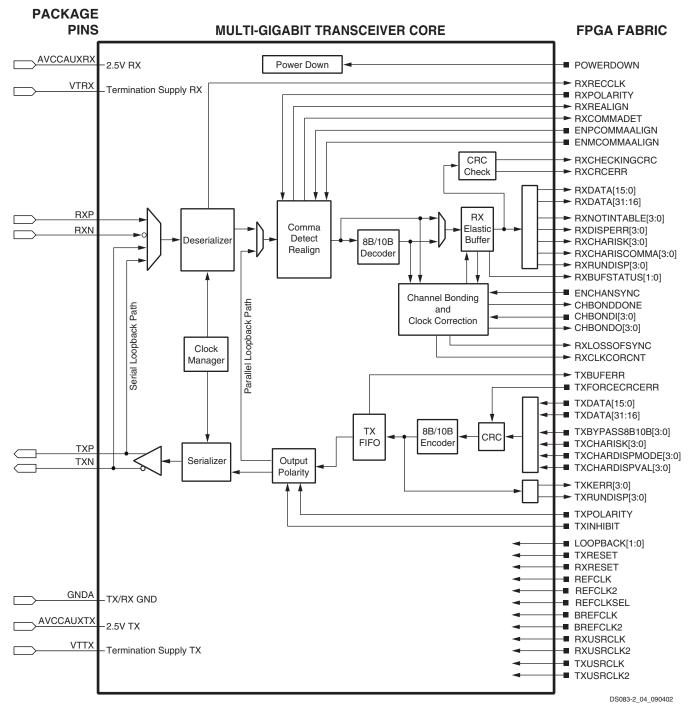

#### **Receiver Termination**

On-chip termination is provided at the receiver, eliminating the need for external termination. The receiver termination supply ( $V_{TRX}$ ) is the center tap of differential termination to

RXP and RXN as shown in Figure 5. This supports multiple termination styles, including high-side, low-side, and differential (floating or active). This configuration supports receiver termination compatible to Virtex-II Pro devices,

using a CML (high-side) termination to an active supply of 1.8V - 2.5V. For DC coupling of two Virtex-II Pro X devices, a 1.5V CML termination for VTRX is recommended.

Figure 5: RocketIO X Receive Termination

#### PCS

#### Fabric Data Interface

Internally, the PCS operates in either 2-byte mode (16/20 bits) or 4-byte mode (32/40 bits). When in 2-byte mode, the FPGA fabric interface can either be 1, 2, or 4 bytes wide. When in 4-byte mode, the FPGA fabric interface can either be 4 or 8 bytes wide. When accompanied by the predefined modes of the PMA, the user thus has a large combination of protocols and data rates from which to choose.

USRCLK2 clocks data on the fabric side, while USRCLK clocks data on the PCS side. This creates distinct USRCLK/USRCLK2 frequency ratios for different combinations of fabric and internal data widths. Table 2 summarizes the USRCLK2-to-USRCLK ratios for the different possible combinations of data widths.

|                      | Frequency Ratio of USRCLK:USRCLK2 |                               |  |  |

|----------------------|-----------------------------------|-------------------------------|--|--|

| Fabric<br>Data Width | 2-Byte Internal<br>Data Width     | 4-Byte Internal<br>Data Width |  |  |

| 1 byte               | 1:2 <sup>(1)</sup>                | N/A                           |  |  |

| 2 byte               | 1:1                               | N/A                           |  |  |

| 4 byte               | 2:1 <sup>(1)</sup>                | 1:1                           |  |  |

| 8 byte               | N/A                               | 2:1 <sup>(1)</sup>            |  |  |

#### Table 2: Clock Ratios for Various Data Widths

#### Notes:

1. Each edge of slower clock must align with falling edge of faster clock.

As a general guide, use 2-byte internal data width mode when the serial speed is below 5 Gb/s, and 4-byte internal data width mode when the serial speed is greater than 5 Gb/s. In 2-byte mode, the PCS processes 4-byte data every other byte. No fixed phase relationship is assumed between REFCLK, RXRECCLK, and/or any other clock that is not tied to either of these clocks. When RXUSRCLK and RXUSRCLK2 have different frequencies, each edge of the slower clock is aligned to a falling edge of the faster clock. The same relationships apply to TXUSRCLK and TXUSRCLK2.

#### FPGA Transmit Interface

The FPGA can send either one, two, or four characters of data to the transmitter. Each character can be either 8 bits or 10 bits wide. If 8-bit data is applied, the additional inputs become control signals for the 8B/10B encoder. When the 8B/10B encoder is bypassed, the 10-bit character order is generated as follows:

| TXCHARDISPN | IODE[0]       | (first bit transmitted) |

|-------------|---------------|-------------------------|

| TXCHARDISP  | /AL[0]        |                         |

| TXDATA[7:0] | (last bit tra | ansmitted is TXDATA[0]) |

#### 64B/66B Encoder/Decoder

The RocketIO X PCS features a 64B/66B encoder/decoder, scrambler/descrambler, and gearbox functions that can be bypassed as needed. The encoder is compliant with IEEE 802.3ae specifications.

#### Scrambler/Gearbox

The bypassable scrambler operates on the read side of the transmit FIFO. The scrambler uses the following generator polynomial to scramble 64B/66B payload data:

$$G(x) = 1 + x^{39} + x^{58}$$

The scrambler works in conjunction with the gearbox, which frames 64B/66B data for the PMA. The gearbox should always be enabled when using the 64B/66B protocal.

#### **Disparity Control**

The 8B/10B encoder is initialized with a negative running disparity. Unique control allows forcing the current running disparity state.

TXRUNDISP signals its current running disparity. This may be useful in those cases where there is a need to manipulate the initial running disparity value.

Bits TXCHARDISPMODE and TXCHARDISPVAL control the generation of running disparity before each byte.

For example, the transceiver can generate the sequence

```

K28.5+ K28.5+ K28.5- K28.5-

Or

K28.5- K28.5- K28.5+ K28.5+

```

by specifying inverted running disparity for the second and fourth bytes.

#### Transmit FIFO

Proper operation of the circuit is only possible if the FPGA clock (TXUSRCLK) is frequency-locked to the reference clock (REFCLK). Phase variations up to one clock cycle are allowable. The FIFO has a depth of four. Overflow or underflow conditions are detected and signaled at the interface. Bypassing of this FIFO is programmable.

#### 8B/10B Encoder

Note: In the RocketIO transceiver, the most-significant byte is sent first; in the RocketIO X transceiver, the least-significant byte is sent first.

A bypassable 8B/10B encoder is included. The encoder uses the same 256 data characters and 12 control characters used by Gigabit Ethernet, Fibre Channel, and InfiniBand.

The encoder accepts 8 bits of data along with a K-character signal for a total of 9 bits per character applied, and generates a 10 bit character for transmission. If the K-character signal is High, the data is encoded into one of the twelve possible K-characters available in the 8B/10B code. If the K-character input is Low, the 8 bits are encoded as standard data. If the K-character input is High, and a user applies other than one of the twelve possible combinations, TXKERR indicates the error.

#### 8B/10B Decoder

Note: In the RocketIO transceiver, the most-significant byte is sent first; in the RocketIO X transceiver, the least-significant byte is sent first.

An optional 8B/10B decoder is included. A programmable option allows the decoder to be bypassed. When the 8B/10B decoder is bypassed, the 10-bit character order is, for example,

| RXCHARISK[0] | (first bit received)             |

|--------------|----------------------------------|

| RXRUNDISP[0] |                                  |

| RXDATA[7:0]  | (last bit received is RXDATA[0]) |

The decoder uses the same table that is used for Gigabit Ethernet, Fibre Channel, and InfiniBand. In addition to

decoding all data and K-characters, the decoder has several extra features. The decoder separately detects both "disparity errors" and "out-of-band" errors. A disparity error is the reception of 10-bit character that exists within the 8B/10B table but has an incorrect disparity. An out-of-band error is the reception of a 10-bit character that does not exist within the 8B/10B table. It is possible to obtain an out-of-band error without having a disparity error. The proper disparity is always computed for both legal and illegal characters. The current running disparity is available at the RXRUNDISP signal.

The 8B/10B decoder performs a unique operation if out-of-band data is detected. If out-of-band data is detected, the decoder signals the error and passes the illegal 10-bits through and places them on the outputs. This can be used for debugging purposes if desired.

The decoder also signals the reception of one of the 12 valid K-characters. In addition, a programmable comma detect is included. The comma detect signal registers a comma on the receipt of any comma+, comma–, or both. Since the comma is defined as a 7-bit character, this includes several out-of-band characters. Another option allows the decoder to detect only the three defined commas (K28.1, K28.5, and K28.7) as comma+, comma–, or both. In total, there are six possible options, three for valid commas and three for "any comma."

Note that all bytes (1, 2, 4, or 8) at the RX FPGA interface each have their own individual 8B/10B indicators (K-character, disparity error, out-of-band error, current running disparity, and comma detect).

#### **Receiver Buffer**

The receiver includes buffers (FIFOs) in the datapath. This section gives the reasons for including the buffers and outlines their operation.

The receiver buffer is required for two reasons:

- *Clock correction* to accommodate the slight difference in frequency between the recovered clock RXRECCLK and the internal FPGA user clock RXUSRCLK

- *Channel bonding* to allow realignment of the input stream to ensure proper alignment of data being read through multiple transceivers

The receiver uses an *elastic buffer*, where "elastic" refers to the ability to modify the read pointer for clock correction and channel bonding.

#### **Comma Detection**

Word alignment is dependent on the state of comma detect bits. If comma detect is enabled, the transceiver recognizes up to two 10-bit preprogrammed characters. Upon detection of the character or characters, the comma detect output is driven high and the data is synchronously aligned. If a comma is detected and the data is aligned, no further alignment alteration takes place. If a comma is received and realignment is necessary, the data is realigned and an indication is given at the receiver interface. The realignment indicator is a distinct output.

The transceiver continuously monitors the data for the presence of the 10-bit character(s). Upon each occurrence of a 10-bit character, the data is checked for word alignment. If comma detect is disabled, the data is not aligned to any particular pattern. The programmable option allows a user to align data on comma+, comma-, both, or a unique user-defined and programmed sequence.

Comma detection has been expanded beyond 10-bit symbol detection and alignment to include 8-bit symbol detection and alignment for 16-, 20-, 32-, and 40-bit paths. The ability to detect symbols, and then either align to 1-word, 2-word, or 4-word boundaries is included. The RXSLIDE input allows the user to "slide" or "slip" the alignment by one bit in each 16-, 20-, 32- and 40-bit mode at any time for SONET applications. Comma detection can be bypassed when needed.

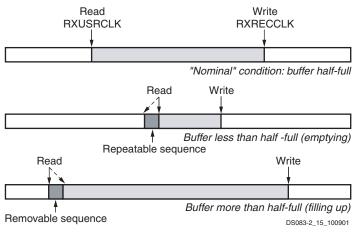

#### **Clock Correction**

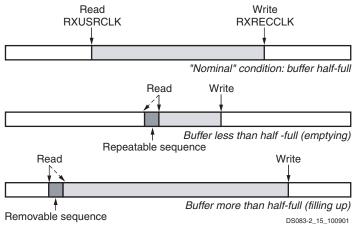

RXRECCLK (the recovered clock) reflects the data rate of the incoming data. RXUSRCLK defines the rate at which the FPGA fabric consumes the data. Ideally, these rates are identical. However, since the clocks typically have different sources, one of the clocks will be faster than the other. The receiver buffer accommodates this difference between the clock rates. See Figure 6.

Figure 6: Clock Correction in Receiver

Nominally, the buffer is always half full. This is shown in the top buffer, Figure 6, where the shaded area represents buffered data not yet read. Received data is inserted via the write pointer under control of RXRECCLK. The FPGA fabric reads data via the read pointer under control of RXUS-RCLK. The half full/half empty condition of the buffer gives a cushion for the differing clock rates. This operation continues indefinitely, regardless of whether or not "meaningful" data is being received. When there is no meaningful data to be received, the incoming data will consist of IDLE characters or other padding.

If RXUSRCLK is faster than RXRECCLK, the buffer becomes more empty over time. The clock correction logic corrects for this by decrementing the read pointer to reread a repeatable byte sequence. This is shown in the middle buffer, Figure 6, where the solid read pointer decrements to the value represented by the dashed pointer. By decrementing the read pointer instead of incrementing it in the usual fashion, the buffer is partially refilled. The transceiver design will repeat a single repeatable byte sequence when necessary to refill a buffer. If the byte sequence length is greater than one, and if attribute CLK\_COR\_REPEAT\_WAIT is 0, then the transceiver may repeat the same sequence multiple times until the buffer is refilled to the desired extent.

Similarly, if RXUSRCLK is slower than RXRECCLK, the buffer will fill up over time. The clock correction logic corrects for this by incrementing the read pointer to skip over a removable byte sequence that need not appear in the final FPGA fabric byte stream. This is shown in the bottom buffer, Figure 6, where the solid read pointer increments to the value represented by the dashed pointer. This accelerates the emptying of the buffer, preventing its overflow. The transceiver design will skip a single byte sequence when necessary to partially empty a buffer. If attribute CLK\_COR\_REPEAT\_WAIT is 0, the transceiver may also skip two consecutive removable byte sequences in one step to further empty the buffer when necessary.

These operations require the clock correction logic to recognize a byte sequence that can be freely repeated or omitted in the incoming data stream. This sequence is generally an IDLE sequence, or other sequence comprised of special values that occur in the gaps separating packets of meaningful data. These gaps are required to occur sufficiently often to facilitate the timely execution of clock correction.

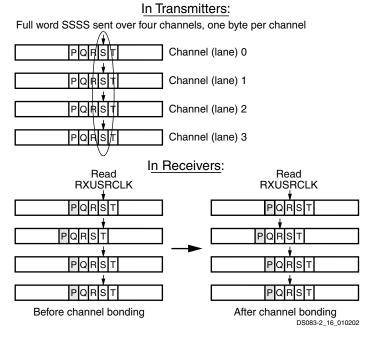

#### **Channel Bonding**

Some gigabit I/O standards such as Infiniband specify the use of multiple transceivers in parallel for even higher data rates. Words of data are split into bytes, with each byte sent over a separate channel (transceiver). See Figure 7.

The top half of the figure shows the transmission of words split across four transceivers (channels or lanes). PPPP, QQQQ, RRRR, SSSS, and TTTT represent words sent over the four channels.

The bottom-left portion of Figure 7 shows the initial situation in the FPGA's receivers at the other end of the four channels. Due to variations in transmission delay—especially if the channels are routed through repeaters—the FPGA fabric might not correctly assemble the bytes into complete words. The bottom-left illustration shows the incorrect assembly of data words PQPP, QRQQ, RSRR, and so forth. To support correction of this misalignment, the data stream includes special byte sequences that define corresponding points in the several channels. In the bottom half of Figure 7, the shaded "P" bytes represent these special characters. Each receiver recognizes the "P" channel bonding character, and remembers its location in the buffer. At some point, one transceiver designated as the master instructs all the transceivers to align to the channel bonding character "P" (or to some location relative to the channel bonding character).

After this operation, words transmitted to the FPGA fabric are properly aligned: RRRR, SSSS, TTTT, and so forth, as shown in the bottom-right portion of Figure 7. To ensure that the channels remain properly aligned following the channel bonding operation, the master transceiver must also control the clock correction operations described in the previous section for all channel-bonded transceivers.

#### Transmitter Buffer

The transmitter's buffer write pointer (TXUSRCLK) is frequency-locked to its read pointer (REFCLK). Therefore, clock correction and channel bonding are not required. The purpose of the transmitter's buffer is to accommodate a phase difference between TXUSRCLK and REFCLK. A simple FIFO suffices for this purpose. A FIFO depth of four will permit reliable operation with simple detection of overflow or underflow, which could occur if the clocks are not frequency-locked.

Figure 7: Channel Bonding (Alignment)

#### **RocketIO X Configuration**

This section outlines functions that can be selected or controlled by configuration. Xilinx implementation software supports the transceiver primitives shown in Table 3.

Table 3: Supported RocketIO X Transceiver Primitives

| Primitive          | Description                   |

|--------------------|-------------------------------|

| GT10_CUSTOM        | Fully customizable by user    |

| GT10_OC48_1        | SONET OC-48, 1-byte data path |

| GT10_OC48_2        | SONET OC-48, 2-byte data path |

| GT10_OC48_4        | SONET OC-48, 4-byte data path |

| GT10_PCI_EXPRESS_1 | PCI Express, 1-byte data path |

| GT10_PCI_EXPRESS_2 | PCI Express, 2-byte data path |

| GT10_PCI_EXPRESS_4 | PCI Express, 4-byte data path |

| GT10_INFINIBAND_1  | Infiniband, 1-byte data path  |

| GT10_INFINIBAND_2  | Infiniband, 2-byte data path  |

| GT10_INFINIBAND_4  | Infiniband, 4-byte data path  |

### **Other RocketIO X Features and Notes**

#### Loopback

In order to facilitate testing without having the need to either apply patterns or measure data at GHz rates, four programmable loop-back features are available.

The first option, serial loopback, is available in two modes: *pre-driver* and *post-driver*.