Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Zynq-7000 All Programmable SoC (XC7Z030, XC7Z045, and XC7Z100): DC and AC Switching Characteristics

DS191 (v1.3) March 27, 2013

**Preliminary Product Specification**

## Introduction

Zynq<sup>TM</sup>-7000 All Programmable SoCs are available in -3, -2, and -1 speed grades, with -3 having the highest performance. Zynq-7000 device DC and AC characteristics are specified in commercial, extended, and industrial temperature ranges. Except the operating temperature range or unless otherwise noted, all the DC and AC electrical parameters are the same for a particular speed grade (that is, the timing characteristics of a -1 speed grade industrial device are the same as for a -1 speed grade commercial device). However, only selected speed grades and/or devices are available in the commercial, extended, or industrial temperature ranges.

All supply voltage and junction temperature specifications are representative of worst-case conditions. The parameters included are common to popular designs and typical applications.

This Zynq-7000 AP SoC (XC7Z030, XC7Z045, and XC7Z100) data sheet, part of an overall set of documentation on the Zynq-7000 devices, is available on the Xilinx website at <a href="https://www.xilinx.com/zynq">www.xilinx.com/zynq</a>. All specifications are subject to change without notice.

## DC Characteristics

Table 1: Absolute Maximum Ratings (1)

| Symbol                                      | Description                                                                          | Min  | Max                                          | Units |

|---------------------------------------------|--------------------------------------------------------------------------------------|------|----------------------------------------------|-------|

| Processing Sys                              | tem (PS)                                                                             |      |                                              |       |

| V <sub>CCPINT</sub>                         | PS primary logic supply                                                              | -0.5 | 1.1                                          | V     |

| V <sub>CCPAUX</sub>                         | PS auxiliary supply voltage                                                          | -0.5 | 2.0                                          | V     |

| V <sub>CCPLL</sub>                          | PS PLL supply                                                                        | -0.5 | 2.0                                          | V     |

| V <sub>CCO_DDR</sub>                        | PS DDR I/O supply                                                                    | -0.5 | 2.0                                          | V     |

| V <sub>CCO_MIO</sub> <sup>(2)</sup>         | PS MIO I/O supply                                                                    | -0.5 | 3.6                                          | ٧     |

| V <sub>PREF</sub>                           | PS input reference voltage                                                           | -0.5 | 2.0                                          | V     |

| V <sub>PIN</sub> <sup>(2)(3)(4)(5)(6)</sup> | PS DDR and MIO I/O input voltage                                                     | -0.5 | $V_{CCO\_DDR} + 0.5$<br>$V_{CCO\_MIO} + 0.5$ | V     |

|                                             | PS DDR and MIO I/O input voltage for V <sub>REF</sub> and differential I/O standards | -0.5 | 2.625                                        | V     |

| Programmable                                | Logic (PL)                                                                           |      |                                              |       |

| V <sub>CCINT</sub>                          | PL internal supply voltage                                                           | -0.5 | 1.1                                          | V     |

| V <sub>CCAUX</sub>                          | PL auxiliary supply voltage                                                          | -0.5 | 2.0                                          | V     |

| V <sub>CCBRAM</sub>                         | PL supply voltage for the block RAM memories                                         | -0.5 | 1.1                                          | ٧     |

| V                                           | PL output drivers supply voltage for 3.3V HR I/O banks                               | -0.5 | 3.6                                          | V     |

| V <sub>CCO</sub>                            | PL output drivers supply voltage for 1.8V HP I/O banks                               | -0.5 | 2.0                                          | V     |

| V <sub>CCAUX_IO</sub>                       | Auxiliary supply voltage                                                             | -0.5 | 2.06                                         | V     |

| V <sub>REF</sub>                            | Input reference voltage                                                              | -0.5 | 2.0                                          | V     |

| V <sub>IN</sub> (3)(4)(5)(6)                | I/O input voltage                                                                    | -0.5 | V <sub>CCO</sub> + 0.5                       | V     |

|                                             | I/O input voltage for V <sub>REF</sub> and differential I/O standards                | -0.5 | 2.625                                        | V     |

<sup>©</sup> Copyright 2012–2013 Xilinx, Inc. Xilinx, the Xilinx logo, Zynq, Virtex, Artix, Kintex, Spartan, ISE, Vivado and other designated brands included herein are trademarks of Xilinx in the United States and other countries. AMBA, AMBA Designer, ARM, Cortex-A9, CoreSight, Cortex, PrimeCell, ARM Powered, and ARM Connected Partner are trademarks of ARM Ltd. All other trademarks are the property of their respective owners.

Table 1: Absolute Maximum Ratings (1) (Cont'd)

| Symbol                   | Description                                                                              | Min      | Max   | Units |

|--------------------------|------------------------------------------------------------------------------------------|----------|-------|-------|

| V <sub>CCBATT</sub>      | Key memory battery backup supply                                                         | -0.5     | 2.0   | V     |

| GTX Transceive           | er                                                                                       |          |       |       |

| V <sub>MGTAVCC</sub>     | Analog supply voltage for the GTX transmitter and receiver circuits                      | -0.5     | 1.1   | V     |

| V <sub>MGTAVTT</sub>     | Analog supply voltage for the GTX transmitter and receiver termination circuits          | -0.5     | 1.32  | V     |

| V <sub>MGTVCCAUX</sub>   | Auxiliary analog Quad PLL (QPLL) voltage supply for the GTX transceivers                 | -0.5     | 1.935 | V     |

| V <sub>MGTREFCLK</sub>   | GTX transceiver reference clock absolute input voltage                                   | -0.5     | 1.32  | V     |

| V <sub>MGTAVTTRCAL</sub> | Analog supply voltage for the resistor calibration circuit of the GTX transceiver column | -0.5     | 1.32  | V     |

| V <sub>IN</sub>          | Receiver (RXP/RXN) and Transmitter (TXP/TXN) absolute input voltage                      | -0.5     | 1.26  | V     |

| I <sub>DCIN</sub>        | DC input current for receiver input pins DC coupled V <sub>MGTAVTT</sub> = 1.2V          | _        | 14    | mA    |

| I <sub>DCOUT</sub>       | DC output current for transmitter pins DC coupled V <sub>MGTAVTT</sub> = 1.2V            | _        | 14    | mA    |

| XADC                     |                                                                                          | <u>'</u> |       |       |

| V <sub>CCADC</sub>       | XADC supply relative to GNDADC                                                           | -0.5     | 2.0   | V     |

| V <sub>REFP</sub>        | XADC reference input relative to GNDADC                                                  | -0.5     | 2.0   | V     |

| Temperature              |                                                                                          | <u>'</u> |       |       |

| T <sub>STG</sub>         | Storage temperature (ambient)                                                            | -65      | 150   | °C    |

| т                        | Maximum soldering temperature for Pb/Sn component bodies (7)                             | _        | +220  | °C    |

| T <sub>SOL</sub>         | Maximum soldering temperature for Pb-free component bodies (7)                           | _        | +260  | °C    |

| T <sub>j</sub>           | Maximum junction temperature <sup>(7)</sup>                                              | _        | +125  | °C    |

- Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time might affect device reliability.

- 2. Applies to both MIO supply banks  $V_{CCO\_MIO0}$  and  $V_{CCO\_MIO1}$ .

- 3. The lower absolute voltage specification always applies.

- 4. For I/O operation, refer to <u>UG471</u>: 7 Series FPGAs SelectIO Resources User Guide or <u>UG585</u>, Zynq-7000 All Programmable SoC Technical Reference Manual.

- 5. The maximum limit applied to DC signals.

- 6. For maximum undershoot and overshoot AC specifications, see Table 4 and Table 5.

- 7. For soldering guidelines and thermal considerations, see UG865, Zynq-7000 All Programmable SoC Packaging and Pinout Specification.

Table 2: Recommended Operating Conditions (1)(2)

| Symbol                              | Description                                                                       | Min   | Тур  | Max                                                        | Units |

|-------------------------------------|-----------------------------------------------------------------------------------|-------|------|------------------------------------------------------------|-------|

| PS                                  |                                                                                   |       |      |                                                            |       |

| V <sub>CCPINT</sub> <sup>(3)</sup>  | PS internal supply voltage                                                        | 0.95  | 1.00 | 1.05                                                       | V     |

| V <sub>CCPAUX</sub>                 | PS auxiliary supply voltage                                                       | 1.71  | 1.80 | 1.89                                                       | V     |

| V <sub>CCPLL</sub>                  | PS PLL supply voltage                                                             | 1.71  | 1.80 | 1.89                                                       | V     |

| V <sub>CCO_DDR</sub>                | PS DDR supply voltage                                                             | 1.14  |      | 1.89                                                       | V     |

| V <sub>CCO_MIO</sub> <sup>(4)</sup> | PS supply voltage for MIO banks                                                   | 1.71  | _    | 3.465                                                      | V     |

| V <sub>PIN</sub> <sup>(5)</sup>     | PS DDR and MIO I/O input voltage                                                  | -0.20 | _    | V <sub>CCO_DDR</sub> + 0.20<br>V <sub>CCO_MIO</sub> + 0.20 | V     |

|                                     | PS DDR and MIO I/O input voltage for $\rm V_{REF}$ and differential I/O standards | -0.20 | _    | 2.625                                                      | V     |

Table 2: Recommended Operating Conditions (1)(2) (Cont'd)

| Symbol                               | Description                                                                                                    | Min   | Тур  | Max                     | Units |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------|-------|------|-------------------------|-------|

| PL                                   |                                                                                                                |       | •    |                         | ,     |

| V <sub>CCINT</sub>                   | Internal supply voltage                                                                                        | 0.97  | 1.00 | 1.03                    | V     |

| V <sub>CCAUX</sub>                   | Auxiliary supply voltage                                                                                       | 1.71  | 1.80 | 1.89                    | V     |

| V <sub>CCBRAM</sub>                  | Block RAM supply voltage                                                                                       | 0.97  | 1.00 | 1.03                    | V     |

| V (6)(7)                             | Supply voltage for 3.3V HR I/O banks                                                                           | 1.14  | _    | 3.465                   | V     |

| V <sub>CCO</sub> <sup>(6)(7)</sup>   | Supply voltage for 1.8V HP I/O banks                                                                           | 1.14  | _    | 1.89                    | V     |

| V                                    | Auxiliary supply voltage when set to 1.8V                                                                      | 1.71  | 1.80 | 1.89                    | V     |

| V <sub>CCAUX_IO</sub>                | Auxiliary supply voltage when set to 2.0V                                                                      | 1.94  | 2.00 | 2.06                    | V     |

| N (5)                                | I/O input voltage                                                                                              | -0.20 | _    | V <sub>CCO</sub> + 0.20 | V     |

| V <sub>IN</sub> <sup>(5)</sup>       | I/O input voltage for V <sub>REF</sub> and differential I/O standards                                          | -0.20 | _    | 2.625                   |       |

| I <sub>IN</sub> (8)                  | Maximum current through any (PS or PL) pin in a powered or unpowered bank when forward biasing the clamp diode | -     | _    | 10                      | mA    |

| V <sub>CCBATT</sub> <sup>(9)</sup>   | Battery voltage                                                                                                | 1.0   | _    | 1.89                    | V     |

| GTX Transceiver                      |                                                                                                                |       |      |                         | •     |

| (10)                                 | Analog supply voltage for the GTX transceiver QPLL frequency range $\leq 10.3125~\text{GHz}^{(11)(12)}$        | 0.97  | 1.0  | 1.08                    | V     |

| V <sub>MGTAVCC</sub> <sup>(10)</sup> | Analog supply voltage for the GTX transceiver QPLL frequency range > 10.3125 GHz                               | 1.02  | 1.05 | 1.08                    |       |

| V <sub>MGTAVTT</sub> <sup>(10)</sup> | Analog supply voltage for the GTX transmitter and receiver termination circuits                                | 1.17  | 1.2  | 1.23                    | ٧     |

| V <sub>MGTVCCAUX</sub> (10)          | Auxiliary analog QPLL voltage supply for the transceivers                                                      | 1.75  | 1.80 | 1.85                    | V     |

| V <sub>MGTAVTTRCAL</sub> (10)        | Analog supply voltage for the resistor calibration circuit of the GTX transceiver column                       | 1.17  | 1.2  | 1.23                    | V     |

| XADC                                 |                                                                                                                |       | 1    |                         | "     |

| V <sub>CCADC</sub>                   | XADC supply relative to GNDADC                                                                                 | 1.71  | 1.80 | 1.89                    | V     |

| V <sub>REFP</sub>                    | Externally supplied reference voltage                                                                          | 1.20  | 1.25 | 1.30                    | V     |

| Temperature                          |                                                                                                                |       |      |                         |       |

|                                      | Junction temperature operating range for commercial (C) temperature devices                                    | 0     | _    | 85                      | °C    |

| T <sub>j</sub>                       | Junction temperature operating range for extended (E) temperature devices                                      | 0     | _    | 100                     | °C    |

|                                      | Junction temperature operating range for industrial (I) temperature devices                                    | -40   | _    | 100                     | °C    |

- 1. All voltages are relative to ground. The PL and PS share a common ground.

- 2. For the design of the power distribution system consult <u>UG933</u>, *Zynq-7000 All Programmable SoC PCB Design and Pin Planning Guide*.

- 3. When the processor cores operate  $F_{CPU\_6X4X\_621\_MAX}$  at 1 GHz (-3E speed grade), the  $V_{CCPINT}$  minimum is 0.97V and the  $V_{CCPINT}$  maximum is 1.03V.

- Applies to both MIO supply banks V<sub>CCO MIO0</sub> and V<sub>CCO MIO1</sub>.

- 5. The lower absolute voltage specification always applies.

- 6. Configuration data is retained even if  $V_{\mbox{\footnotesize CCO}}$  drops to 0V.

- 7. Includes V<sub>CCO</sub> of 1.2V, 1.5V, 1.8V, 2.5V, and 3.3V.

- 8. A total of 200 mA per PS or PL bank should not be exceeded.

- 9.  $V_{CCBATT}$  is required only when using bitstream encryption. If battery is not used, connect  $V_{CCBATT}$  to either ground or  $V_{CCAUX}$ .

- 10. Each voltage listed requires the filter circuit described in UG476: 7 Series FPGAs GTX/GTH Transceivers User Guide.

- 11. For data rates  $\leq$  10.3125 Gb/s,  $V_{MGTAVCC}$  should be 1.0V  $\pm$ 3% for lower power consumption.

- 12. For lower power consumption,  $V_{MGTAVCC}$  should be 1.0V ±3% over the entire CPLL frequency range.

Table 3: DC Characteristics Over Recommended Operating Conditions

| Symbol                              | Description                                                                                                                                                                     | Min  | Typ <sup>(1)</sup> | Max | Units |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-----|-------|

| V <sub>DRINT</sub>                  | Data retention V <sub>CCINT</sub> voltage (below which configuration data might be lost)                                                                                        | 0.75 | _                  | _   | V     |

| V <sub>DRI</sub>                    | Data retention V <sub>CCAUX</sub> voltage (below which configuration data might be lost)                                                                                        | 1.5  | _                  | _   | ٧     |

| I <sub>REF</sub>                    | V <sub>REF</sub> leakage current per pin                                                                                                                                        | _    | _                  | 15  | μΑ    |

| IL                                  | Input or output leakage current per pin (sample-tested)                                                                                                                         | -    | _                  | 15  | μΑ    |

| C <sub>IN</sub> <sup>(2)</sup>      | PL die input capacitance at the pad                                                                                                                                             | _    | _                  | 8   | pF    |

| C <sub>PIN</sub> <sup>(2)</sup>     | PS die input capacitance at the pad                                                                                                                                             | _    | _                  | 8   | pF    |

|                                     | Pad pull-up (when selected) @ V <sub>IN</sub> = 0V, V <sub>CCO</sub> = 3.3V                                                                                                     | 90   | _                  | 330 | μA    |

|                                     | Pad pull-up (when selected) @ V <sub>IN</sub> = 0V, V <sub>CCO</sub> = 2.5V                                                                                                     | 68   | _                  | 250 | μA    |

| I <sub>RPU</sub>                    | Pad pull-up (when selected) @ V <sub>IN</sub> = 0V, V <sub>CCO</sub> = 1.8V                                                                                                     | 34   | _                  | 220 | μA    |

|                                     | Pad pull-up (when selected) @ V <sub>IN</sub> = 0V, V <sub>CCO</sub> = 1.5V                                                                                                     | 23   | _                  | 150 | μA    |

|                                     | Pad pull-up (when selected) @ V <sub>IN</sub> = 0V, V <sub>CCO</sub> = 1.2V                                                                                                     | 12   | _                  | 120 | μA    |

| 1                                   | Pad pull-down (when selected) @ V <sub>IN</sub> = 3.3V                                                                                                                          | 68   | _                  | 330 | μA    |

| I <sub>RPD</sub>                    | Pad pull-down (when selected) @ V <sub>IN</sub> = 1.8V                                                                                                                          | 45   | _                  | 180 | μA    |

| I <sub>CCADC</sub>                  | Analog supply current, analog circuits in powered up state                                                                                                                      | _    | _                  | 25  | mA    |

| I <sub>BATT</sub> (3)               | Battery supply current                                                                                                                                                          | _    | _                  | 150 | nA    |

|                                     | Thevenin equivalent resistance of programmable input termination to $V_{\rm CCO}/2$ (UNTUNED_SPLIT_40) for commercial (C), industrial (I), and extended (E) temperature devices | 28   | 40                 | 55  | Ω     |

| R <sub>IN_TERM</sub> <sup>(4)</sup> | Thevenin equivalent resistance of programmable input termination to $V_{\rm CCO}/2$ (UNTUNED_SPLIT_50) for commercial (C), industrial (I), and extended (E) temperature devices | 35   | 50                 | 65  | Ω     |

|                                     | Thevenin equivalent resistance of programmable input termination to $V_{\rm CCO}/2$ (UNTUNED_SPLIT_60) for commercial (C), industrial (I), and extended (E) temperature devices | 44   | 60                 | 83  | Ω     |

| n                                   | Temperature diode ideality factor                                                                                                                                               | _    | 1.010              | _   | _     |

| r                                   | Temperature diode series resistance                                                                                                                                             | _    | 2                  | _   | Ω     |

|                                     |                                                                                                                                                                                 | -    |                    |     |       |

- 1. Typical values are specified at nominal voltage, 25°C.

- 2. This measurement represents the die capacitance at the pad, not including the package.

- 3. Maximum value specified for worst case process at 25°C.

- 4. Termination resistance to a  $V_{CCO}/2$  level.

Table 4: V<sub>IN</sub> Maximum Allowed AC Voltage Overshoot and Undershoot for PS I/O and 3.3V HR I/O Banks<sup>(1)</sup>

| AC Voltage Overshoot    | % of UI @-40°C to 100°C | AC Voltage Undershoot | % of UI @-40°C to 100°C |

|-------------------------|-------------------------|-----------------------|-------------------------|

| V <sub>CCO</sub> + 0.40 | 100                     | -0.40                 | 100                     |

| V <sub>CCO</sub> + 0.45 | 100                     | -0.45                 | 61.7                    |

| V <sub>CCO</sub> + 0.50 | 100                     | -0.50                 | 25.8                    |

| V <sub>CCO</sub> + 0.55 | 100                     | -0.55                 | 11.0                    |

| V <sub>CCO</sub> + 0.60 | 46.6                    | -0.60                 | 4.77                    |

| V <sub>CCO</sub> + 0.65 | 21.2                    | -0.65                 | 2.10                    |

| V <sub>CCO</sub> + 0.70 | 9.75                    | -0.70                 | 0.94                    |

| V <sub>CCO</sub> + 0.75 | 4.55                    | -0.75                 | 0.43                    |

| V <sub>CCO</sub> + 0.80 | 2.15                    | -0.80                 | 0.20                    |

| V <sub>CCO</sub> + 0.85 | 1.02                    | -0.85                 | 0.09                    |

| V <sub>CCO</sub> + 0.90 | 0.49                    | -0.90                 | 0.04                    |

| V <sub>CCO</sub> + 0.95 | 0.24                    | -0.95                 | 0.02                    |

Table 5: V<sub>IN</sub> Maximum Allowed AC Voltage Overshoot and Undershoot for PL 1.8V HP I/O Banks<sup>(1)(2)</sup>

| AC Voltage Overshoot    | % of UI @-40°C to 100°C | AC Voltage Undershoot | % of UI @-40°C to 100°C |

|-------------------------|-------------------------|-----------------------|-------------------------|

| V <sub>CCO</sub> + 0.40 | 100                     | -0.40                 | 100                     |

| V <sub>CCO</sub> + 0.45 | 100                     | -0.45                 | 100                     |

| V <sub>CCO</sub> + 0.50 | 100                     | -0.50                 | 100                     |

| V <sub>CCO</sub> + 0.55 | 100                     | -0.55                 | 100                     |

| V <sub>CCO</sub> + 0.60 | 50.0                    | -0.60                 | 50.0                    |

| V <sub>CCO</sub> + 0.65 | 50.0                    | -0.65                 | 50.0                    |

| V <sub>CCO</sub> + 0.70 | 47.0                    | -0.70                 | 50.0                    |

| V <sub>CCO</sub> + 0.75 | 21.2                    | -0.75                 | 50.0                    |

| V <sub>CCO</sub> + 0.80 | 9.71                    | -0.80                 | 50.0                    |

| V <sub>CCO</sub> + 0.85 | 4.51                    | -0.85                 | 28.4                    |

| V <sub>CCO</sub> + 0.90 | 2.12                    | -0.90                 | 12.7                    |

| V <sub>CCO</sub> + 0.95 | 1.01                    | -0.95                 | 5.79                    |

- 1. A total of 200 mA per bank should not be exceeded.

- 2. For UI smaller than 20 μs.

<sup>1.</sup> A total of 200 mA per bank should not be exceeded.

Table 6: Typical Quiescent Supply Current

| Cumbal                 | Decemention                                       | Dovice  |     | Speed Grade |     | Unito |

|------------------------|---------------------------------------------------|---------|-----|-------------|-----|-------|

| Symbol                 | Description                                       | Device  | -3  | -2          | -1  | Units |

|                        |                                                   | XC7Z030 | 122 | 122         | 122 | mA    |

| I <sub>CCPINTQ</sub>   | PS quiescent V <sub>CCPINT</sub> supply current   | XC7Z045 | 122 | 122         | 122 | mA    |

|                        |                                                   | XC7Z100 |     |             |     | mA    |

|                        |                                                   | XC7Z030 | 13  | 13          | 13  | mA    |

| I <sub>CCPAUXQ</sub>   | PS quiescent V <sub>CCPAUX</sub> supply current   | XC7Z045 | 13  | 13          | 13  | mA    |

|                        |                                                   | XC7Z100 |     |             |     | mA    |

|                        |                                                   | XC7Z030 | 4   | 4           | 4   | mA    |

| ICCDDRQ                | PS quiescent V <sub>CCO_DDR</sub> supply current  | XC7Z045 | 4   | 4           | 4   | mA    |

|                        |                                                   | XC7Z100 |     |             |     | mA    |

| I <sub>CCINTQ</sub>    | PL quiescent V <sub>CCINT</sub> supply current    | XC7Z030 | 246 | 246         | 246 | mA    |

|                        |                                                   | XC7Z045 | 611 | 611         | 611 | mA    |

|                        |                                                   | XC7Z100 |     |             |     | mA    |

| I <sub>CCAUXQ</sub>    | PL quiescent V <sub>CCAUX</sub> supply current    | XC7Z030 | 56  | 56          | 56  | mA    |

|                        |                                                   | XC7Z045 | 131 | 131         | 131 | mA    |

|                        |                                                   | XC7Z100 |     |             |     | mA    |

| I <sub>CCAUX_IOQ</sub> | PL quiescent V <sub>CCAUX_IO</sub> supply current | XC7Z030 | 2   | 2           | 2   | mA    |

|                        |                                                   | XC7Z045 | 2   | 2           | 2   | mA    |

|                        |                                                   | XC7Z100 |     |             |     | mA    |

| Iccoq                  | PL quiescent V <sub>CCO</sub> supply current      | XC7Z030 | 4   | 4           | 4   | mA    |

|                        |                                                   | XC7Z045 | 4   | 4           | 4   | mA    |

|                        |                                                   | XC7Z100 |     |             |     | mA    |

| I <sub>CCBRAMQ</sub>   | PL quiescent V <sub>CCBRAM</sub> supply current   | XC7Z030 | 11  | 11          | 11  | mA    |

|                        |                                                   | XC7Z045 | 23  | 23          | 23  | mA    |

|                        |                                                   | XC7Z100 |     |             |     | mA    |

- 1. Typical values are specified at nominal voltage, 85°C junction temperatures (T<sub>i</sub>) with single-ended SelectIO resources.

- 2. Typical values are for blank configured devices with no output current loads, no active input pull-up resistors, all I/O pins are 3-state and floating.

- 3. Use the Xilinx Power Estimator (XPE) spreadsheet tool (download at <a href="http://www.xilinx.com/power">http://www.xilinx.com/power</a>) to calculate static power consumption for conditions other than those specified.

# **PS Power-On/Off Power Supply Requirements**

The recommended power-on sequence is  $V_{CCPINT}$ ,  $V_{CCPAUX}$  and  $V_{CCPLL}$  together, then the PS  $V_{CCO}$  supplies ( $V_{CCO\_MIO0}$ ,  $V_{CCO\_MIO1}$ , and  $V_{CCO\_DDR}$ ) to achieve minimum current draw and ensure that the I/Os are 3-stated at power-on. The recommended power-off sequence is the reverse of the power-on sequence. If  $V_{CCPAUX}$ ,  $V_{CCPLL}$  and the PS  $V_{CCO}$  supplies ( $V_{CCO\_MIO0}$ ,  $V_{CCO\_MIO1}$ , and  $V_{CCO\_DDR}$ ) have the same recommended voltage levels, then they can be powered by the same supply and ramped simultaneously. Xilinx recommends powering  $V_{CCPLL}$  with the same supply as  $V_{CCPAUX}$ , with an optional ferrite bead filter.

For  $V_{CCO\_MIO0}$  and  $V_{CCO\_MIO1}$  voltages of 3.3V:

- The voltage difference between V<sub>CCO\_MIO0</sub> /V<sub>CCO\_MIO1</sub> and V<sub>CCPAUX</sub> must not exceed 2.625V for longer than T<sub>VCCO2VCCAUX</sub> for each power-on/off cycle to maintain device reliability levels.

- The T<sub>VCCO2VCCAUX</sub> time can be allocated in any percentage between the power-on and power-off ramps.

## **PS Power-on Reset**

The PS provides the power on reset (PS\_POR\_B) input signal which must be held Low until all PS power supplies are stable and within operating limits. Additionally, PS\_POR\_B must be held Low until PS\_CLK is stable for 2,000 clocks.

## PL Power-On/Off Power Supply Sequencing

The recommended power-on sequence is  $V_{CCINT}$ ,  $V_{CCBRAM}$ ,  $V_{CCAUX}$ ,  $V_{CCAUX\_IO}$ , and  $V_{CCO}$  to achieve minimum current draw and ensure that the I/Os are 3-stated at power-on. The recommended power-off sequence is the reverse of the power-on sequence. If  $V_{CCINT}$  and  $V_{CCBRAM}$  have the same recommended voltage levels then both can be powered by the same supply and ramped simultaneously. If  $V_{CCAUX\_IO}$ , and  $V_{CCO}$  have the same recommended voltage levels then they can be powered by the same supply and ramped simultaneously.

For V<sub>CCO</sub> voltages of 3.3V in HR I/O banks and configuration bank 0:

- The voltage difference between V<sub>CCO</sub> and V<sub>CCAUX</sub> must not exceed 2.625V for longer than T<sub>VCCO2VCCAUX</sub> for each power-on/off cycle to maintain device reliability levels.

- The T<sub>VCCO2VCCAUX</sub> time can be allocated in any percentage between the power-on and power-off ramps.

The recommended power-on sequence to achieve minimum current draw for the GTX transceivers is  $V_{CCINT}$ ,  $V_{MGTAVCC}$ ,  $V_{MGTAVCC}$ ,  $V_{MGTAVCC}$ ,  $V_{MGTAVCC}$ ,  $V_{MGTAVCC}$ . There is no recommended sequencing for  $V_{MGTAVCCAUX}$ . Both  $V_{MGTAVCC}$  and  $V_{CCINT}$  can be ramped simultaneously. The recommended power-off sequence is the reverse of the power-on sequence to achieve minimum current draw.

If these recommended sequences are not met, current drawn from  $V_{MGTAVTT}$  can be higher than specifications during power-up and power-down.

- When V<sub>MGTAVTT</sub> is powered before V<sub>MGTAVCC</sub> and V<sub>MGTAVTT</sub> V<sub>MGTAVCC</sub> > 150 mV and V<sub>MGTAVCC</sub> < 0.7V, the V<sub>MGTAVTT</sub> current draw can increase by 460 mA per transceiver during V<sub>MGTAVCC</sub> ramp up. The duration of the current draw can be up to 0.3 x T<sub>MGTAVCC</sub> (ramp time from GND to 90% of V<sub>MGTAVCC</sub>). The reverse is true for power-down.

- When V<sub>MGTAVTT</sub> is powered before V<sub>CCINT</sub> and V<sub>MGTAVTT</sub> V<sub>CCINT</sub> > 150 mV and V<sub>CCINT</sub> < 0.7V, the V<sub>MGTAVTT</sub> current draw can increase by 50 mA per transceiver during V<sub>CCINT</sub> ramp up. The duration of the current draw can be up to 0.3 x T<sub>VCCINT</sub> (ramp time from GND to 90% of V<sub>CCINT</sub>). The reverse is true for power-down.

# **PS—PL Power Sequencing**

The PS and PL power supplies are fully independent. There are no sequencing requirements between the PS ( $V_{CCPINT}$ ,  $V_{CCPAUX}$ ,  $V_{CCPLL}$ ,  $V_{CCO\_DDR}$ ,  $V_{CCO\_MIO0}$ , and  $V_{CCO\_MIO1}$ ) and PL ( $V_{CCINT}$ ,  $V_{CCBRAM}$ ,  $V_{CCAUX}$ ,  $V_{CCO}$ ,  $V_{CCAUX\_IO}$ ,  $V_{MGTAVCC}$ ,  $V_{MGTAVCCAUX}$ , and  $V_{CCADC}$ ) power supplies.

# **Power Supply and PS Reset Requirements**

Table 7 shows the minimum current, in addition to  $I_{CCQ}$ , that is required by Zynq-7000 devices for proper power-on and configuration. If the current minimums shown in Table 6 and Table 7 are met, the device powers on after all five supplies have passed through their power-on reset threshold voltages. The Zynq-7000 device must not be configured until after  $V_{CCINT}$  is applied. Once initialized and configured, use the Xilinx Power Estimator (XPE) tools to estimate current drain on these supplies.

Table 7: Power-On Current for Zyng-7000 Devices(1)

| Device  | I <sub>CCPINTMIN</sub> Typ <sup>(2)</sup> | I <sub>CCPAUXMIN</sub> Typ <sup>(2)</sup> | I <sub>CCDDRMIN</sub> Typ <sup>(2)</sup>    | I <sub>CCINTMIN</sub> Typ <sup>(2)</sup> | I <sub>CCAUXMIN</sub> Typ <sup>(2)</sup> | I <sub>CCOMIN</sub> Typ <sup>(2)</sup>   | I <sub>CCAUX_IOMIN</sub> Typ <sup>(2)</sup>   | I <sub>CCBRAMMIN</sub> Typ <sup>(2)</sup> | Units |

|---------|-------------------------------------------|-------------------------------------------|---------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|-----------------------------------------------|-------------------------------------------|-------|

| XC7Z030 | I <sub>CCPINTQ</sub> +<br>70 mA           | I <sub>CCPAUXQ</sub> +<br>40 mA           | I <sub>CCDDRQ</sub> +<br>130 mA<br>per bank | I <sub>CCINTQ</sub> +<br>900 mA          | I <sub>CCAUXQ</sub> +<br>60 mÅ           | I <sub>CCOQ</sub> +<br>90 mA<br>per bank | I <sub>CCOAUXIOQ</sub> +<br>40 mA<br>per bank | I <sub>CCBRAMQ</sub> +<br>90 mA           | mA    |

| XC7Z045 | I <sub>CCPINTQ</sub> + 70 mÅ              | I <sub>CCPAUXQ</sub> + 40 mA              | I <sub>CCDDRQ</sub> +<br>130 mA<br>per bank | I <sub>CCINTQ</sub> +<br>1400 mA         | I <sub>CCAUXQ</sub> + 60 mÅ              | I <sub>CCOQ</sub> +<br>90 mA<br>per bank | I <sub>CCOAUXIOQ</sub> +<br>40 mA<br>per bank | I <sub>CCBRAMQ</sub> + 90 mA              | mA    |

| XC7Z100 |                                           |                                           |                                             |                                          |                                          |                                          |                                               |                                           | mA    |

#### Notes:

- 1. Use the Xilinx Power Estimator (XPE) spreadsheet tool (download at http://www.xilinx.com/power) to calculate maximum power-on currents.

- Typical values are specified at nominal voltage, 25°C.

Table 8: Power Supply Ramp Time

| Symbol                    | Description                                                                     | Min                         | Max | Units |    |

|---------------------------|---------------------------------------------------------------------------------|-----------------------------|-----|-------|----|

| T <sub>VCCPINT</sub>      | Ramp time from GND to 90% of V <sub>CCPINT</sub>                                |                             | 0.2 | 50    | ms |

| T <sub>VCCPAUX</sub>      | Ramp time from GND to 90% of V <sub>CCPAUX</sub>                                |                             | 0.2 | 50    | ms |

| T <sub>VCCO_DDR</sub>     | Ramp time from GND to 90% of V <sub>CCO_DDR</sub>                               |                             | 0.2 | 50    | ms |

| T <sub>VCCO_MIO</sub>     | Ramp time from GND to 90% of V <sub>CCO_MIO</sub>                               |                             | 0.2 | 50    | ms |

| T <sub>VCCINT</sub>       | Ramp time from GND to 90% of V <sub>CCINT</sub>                                 |                             | 0.2 | 50    | ms |

| T <sub>VCCO</sub>         | Ramp time from GND to 90% of V <sub>CCO</sub>                                   | 0.2                         | 50  | ms    |    |

| T <sub>VCCAUX</sub>       | Ramp time from GND to 90% of V <sub>CCAUX</sub>                                 | 0.2                         | 50  | ms    |    |

| T <sub>VCCAUX_IO</sub>    | Ramp time from GND to 90% of V <sub>CCAUX_IO</sub>                              | 0.2                         | 50  | ms    |    |

| T <sub>VCCBRAM</sub>      | Ramp time from GND to 90% of V <sub>CCBRAM</sub>                                |                             | 0.2 | 50    | ms |

| _                         | Allowed time per power cycle for V <sub>CCO</sub> – V <sub>CCAUX</sub> > 2.625V | $T_J = 100^{\circ}C^{(1)}$  | -   | 500   |    |

| T <sub>VCCO2</sub> VCCAUX | and V <sub>CCO_MIO</sub> - V <sub>CCPAUX</sub> > 2.625V                         | $T_{J} = 85^{\circ}C^{(1)}$ | -   | 800   | ms |

| T <sub>MGTAVCC</sub>      | Ramp time from GND to 90% of V <sub>MGTAVCC</sub>                               | 0.2                         | 50  | ms    |    |

| T <sub>MGTAVTT</sub>      | Ramp time from GND to 90% of V <sub>MGTAVTT</sub>                               | 0.2                         | 50  | ms    |    |

| T <sub>MGTVCCAUX</sub>    | Ramp time from GND to 90% of V <sub>MGTVCCAUX</sub>                             |                             | 0.2 | 50    | ms |

#### Notes:

Based on 240,000 power cycles with nominal V<sub>CCO</sub> of 3.3V or 36,500 power cycles with a worst case V<sub>CCO</sub> of 3.465V.

# **DC Input and Output Levels**

Values for  $V_{IL}$  and  $V_{IH}$  are recommended input voltages. Values for  $I_{OL}$  and  $I_{OH}$  are guaranteed over the recommended operating conditions at the  $V_{OL}$  and  $V_{OH}$  test points. Only selected standards are tested. These are chosen to ensure that all standards meet their specifications. The selected standards are tested at a minimum  $V_{CCO}$  with the respective  $V_{OL}$  and  $V_{OH}$  voltage levels shown. Other standards are sample tested.

## PS I/O Levels

Table 9: PS DC Input and Output Levels(1)

| Bank  | I/O       |        | V <sub>IL</sub>           |                           | V <sub>IH</sub>              | V <sub>OL</sub>                 | V <sub>OH</sub>                 | I <sub>OL</sub> | I <sub>OH</sub> |

|-------|-----------|--------|---------------------------|---------------------------|------------------------------|---------------------------------|---------------------------------|-----------------|-----------------|

| Dalik | Standard  | V, Min | V, Max                    | V, Min                    | V, Max                       | V, Max                          | V, Min                          | mA              | mA              |

| MIO   | LVCMOS18  | -0.300 | 35% V <sub>CCO_MIO</sub>  | 65% V <sub>CCO_MIO</sub>  | $V_{CCO\_MIO} + 0.300$       | 0.450                           | V <sub>CCO_MIO</sub> - 0.450    | 8               | -8              |

| MIO   | LVCMOS25  | -0.300 | 0.700                     | 1.700                     | $V_{CCO\_MIO} + 0.300$       | 0.400                           | V <sub>CCO_MIO</sub> - 0.400    | 8               | -8              |

| MIO   | LVCMOS33  | -0.300 | 0.800                     | 2.000                     | 3.450                        | 0.400                           | V <sub>CCO_MIO</sub> - 0.400    | 8               | -8              |

| MIO   | HSTL_I_18 | -0.300 | V <sub>PREF</sub> – 0.100 | V <sub>PREF</sub> + 0.100 | $V_{CCO\_MIO} + 0.300$       | 0.400                           | V <sub>CCO_MIO</sub> - 0.400    | 8               | -8              |

| DDR   | SSTL18_I  | -0.300 | V <sub>PREF</sub> – 0.125 | V <sub>PREF</sub> + 0.125 | V <sub>CCO_DDR</sub> + 0.300 | V <sub>CCO_DDR</sub> /2 - 0.470 | V <sub>CCO_DDR</sub> /2 + 0.470 | 8               | -8              |

| DDR   | SSTL15    | -0.300 | V <sub>PREF</sub> – 0.100 | V <sub>PREF</sub> + 0.100 | V <sub>CCO_DDR</sub> + 0.300 | V <sub>CCO_DDR</sub> /2 - 0.175 | V <sub>CCO_DDR</sub> /2 + 0.175 | 13.0            | -13.0           |

| DDR   | SSTL135   | -0.300 | V <sub>PREF</sub> – 0.090 | V <sub>PREF</sub> + 0.090 | V <sub>CCO_DDR</sub> + 0.300 | V <sub>CCO_DDR</sub> /2 - 0.150 | V <sub>CCO_DDR</sub> /2 + 0.150 | 13.0            | -13.0           |

| DDR   | HSUL_12   | -0.300 | V <sub>PREF</sub> - 0.130 | V <sub>PREF</sub> + 0.130 | V <sub>CCO_DDR</sub> + 0.300 | 20% V <sub>CCO_DDR</sub>        | 80% V <sub>CCO_DDR</sub>        | 0.1             | -0.1            |

#### Notes:

Table 10: PS Complementary Differential DC Input and Output Levels

| Bank I/O Standard |               | V <sub>ICM</sub> <sup>(1)</sup> |       | V <sub>ID</sub> <sup>(2)</sup> |       | V <sub>OL</sub> (3) | V <sub>OH</sub> <sup>(4)</sup>    | I <sub>OL</sub>                   | I <sub>OH</sub> |         |

|-------------------|---------------|---------------------------------|-------|--------------------------------|-------|---------------------|-----------------------------------|-----------------------------------|-----------------|---------|

| Dalik             | V, Mir        |                                 | V,Typ | V, Max                         | V,Min | V, Max              | V, Max                            | V, Min                            | mA, Max         | mA, Min |

| DDR               | DIFF_HSUL_12  | 0.300                           | 0.600 | 0.850                          | 0.100 | -                   | 20% V <sub>CCO</sub>              | 80% V <sub>CCO</sub>              | 0.100           | -0.100  |

| DDR               | DIFF_SSTL135  | 0.300                           | 0.675 | 1.000                          | 0.100 | _                   | (V <sub>CCO_DDR</sub> /2) - 0.150 | $(V_{CCO\_DDR}/2) + 0.150$        | 13.0            | -13.0   |

| DDR               | DIFF_SSTL15   | 0.300                           | 0.750 | 1.125                          | 0.100 | _                   | (V <sub>CCO_DDR</sub> /2) - 0.175 | (V <sub>CCO_DDR</sub> /2) + 0.175 | 13.0            | -13.0   |

| DDR               | DIFF_SSTL18_I | 0.300                           | 0.900 | 1.425                          | 0.100 | _                   | (V <sub>CCO_DDR</sub> /2) - 0.470 | $(V_{CCO\_DDR}/2) + 0.470$        | 8.00            | -8.00   |

- V<sub>ICM</sub> is the input common mode voltage.

- 2.  $V_{ID}$  is the input differential voltage  $(Q-\overline{Q})$ .

- 3. V<sub>OL</sub> is the single-ended low-output voltage.

- 4.  $V_{OH}$  is the single-ended high-output voltage.

Tested according to relevant specifications.

## PL I/O Levels

Table 11: SelectIO DC Input and Output Levels(1)(2)

| I/O Standard          |        | V <sub>IL</sub>          | VII                      | 4                        | V <sub>OL</sub>             | V <sub>OH</sub>             | I <sub>OL</sub> | I <sub>OH</sub> |

|-----------------------|--------|--------------------------|--------------------------|--------------------------|-----------------------------|-----------------------------|-----------------|-----------------|

| I/O Standard          | V, Min | V, Max                   | V, Min                   | V, Max                   | V, Max                      | V, Min                      | mA              | mA              |

| HSTL_I                | -0.300 | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | $V_{CCO} + 0.300$        | 0.400                       | V <sub>CCO</sub> - 0.400    | 8               | -8              |

| HSTL_I_12             | -0.300 | V <sub>REF</sub> – 0.080 | V <sub>REF</sub> + 0.080 | $V_{CCO} + 0.300$        | 25% V <sub>CCO</sub>        | 75% V <sub>CCO</sub>        | 6.3             | -6.3            |

| HSTL_I_18             | -0.300 | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | $V_{CCO} + 0.300$        | 0.400                       | V <sub>CCO</sub> - 0.400    | 8               | -8              |

| HSTL_II               | -0.300 | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | $V_{CCO} + 0.300$        | 0.400                       | V <sub>CCO</sub> - 0.400    | 16              | -16             |

| HSTL_II_18            | -0.300 | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | $V_{CCO} + 0.300$        | 0.400                       | V <sub>CCO</sub> - 0.400    | 16              | -16             |

| HSUL_12               | -0.300 | V <sub>REF</sub> – 0.130 | V <sub>REF</sub> + 0.130 | $V_{CCO} + 0.300$        | 20% V <sub>CCO</sub>        | 80% V <sub>CCO</sub>        | 0.1             | -0.1            |

| LVCMOS12              | -0.300 | 35% V <sub>CCO</sub>     | 65% V <sub>CCO</sub>     | $V_{CCO} + 0.300$        | 0.400                       | V <sub>CCO</sub> - 0.400    | Note 3          | Note 3          |

| LVCMOS15,<br>LVDCI_15 | -0.300 | 35% V <sub>CCO</sub>     | 65% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.300 | 25% V <sub>CCO</sub>        | 75% V <sub>CCO</sub>        | Note 4          | Note 4          |

| LVCMOS18,<br>LVDCI_18 | -0.300 | 35% V <sub>CCO</sub>     | 65% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.300 | 0.450                       | V <sub>CCO</sub> - 0.450    | Note 5          | Note 5          |

| LVCMOS25              | -0.300 | 0.700                    | 1.700                    | $V_{CCO} + 0.300$        | 0.400                       | V <sub>CCO</sub> - 0.400    | Note 6          | Note 6          |

| LVCMOS33              | -0.300 | 0.800                    | 2.000                    | 3.450                    | 0.400                       | V <sub>CCO</sub> - 0.400    | Note 6          | Note 6          |

| LVTTL                 | -0.300 | 0.800                    | 2.000                    | 3.450                    | 0.400                       | 2.400                       | Note 7          | Note 7          |

| MOBILE_DDR            | -0.300 | 20% V <sub>CCO</sub>     | 80% V <sub>CCO</sub>     | $V_{CCO} + 0.300$        | 10% V <sub>CCO</sub>        | 90% V <sub>CCO</sub>        | 0.1             | -0.1            |

| PCl33_3               | -0.500 | 30% V <sub>CCO</sub>     | 50% V <sub>CCO</sub>     | $V_{CCO} + 0.500$        | 10% V <sub>CCO</sub>        | 90% V <sub>CCO</sub>        | 1.5             | -0.5            |

| SSTL12                | -0.300 | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | $V_{CCO} + 0.300$        | V <sub>CCO</sub> /2 - 0.150 | V <sub>CCO</sub> /2 + 0.150 | 14.25           | -14.25          |

| SSTL135               | -0.300 | V <sub>REF</sub> - 0.090 | V <sub>REF</sub> + 0.090 | V <sub>CCO</sub> + 0.300 | V <sub>CCO</sub> /2 - 0.150 | V <sub>CCO</sub> /2 + 0.150 | 13.0            | -13.0           |

| SSTL135_R             | -0.300 | V <sub>REF</sub> - 0.090 | V <sub>REF</sub> + 0.090 | V <sub>CCO</sub> + 0.300 | V <sub>CCO</sub> /2 - 0.150 | V <sub>CCO</sub> /2 + 0.150 | 8.9             | -8.9            |

| SSTL15                | -0.300 | V <sub>REF</sub> – 0.100 | V <sub>REF</sub> + 0.100 | $V_{CCO} + 0.300$        | V <sub>CCO</sub> /2 - 0.175 | V <sub>CCO</sub> /2 + 0.175 | 13.0            | -13.0           |

| SSTL15_R              | -0.300 | V <sub>REF</sub> - 0.100 | V <sub>REF</sub> + 0.100 | $V_{CCO} + 0.300$        | V <sub>CCO</sub> /2 - 0.175 | V <sub>CCO</sub> /2 + 0.175 | 8.9             | -8.9            |

| SSTL18_I              | -0.300 | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | $V_{CCO} + 0.300$        | V <sub>CCO</sub> /2 - 0.470 | V <sub>CCO</sub> /2 + 0.470 | 8               | -8              |

| SSTL18_II             | -0.300 | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCO</sub> + 0.300 | V <sub>CCO</sub> /2 - 0.600 | V <sub>CCO</sub> /2 + 0.600 | 13.4            | -13.4           |

- 1. Tested according to relevant specifications.

- 2. 3.3V and 2.5V standards are only supported in 3.3V I/O banks.

- 3. Supported drive strengths of 2, 4, 6, or 8 mA in HP I/O banks and 4, 8, or 12 mA in HR I/O banks.

- 4. Supported drive strengths of 2, 4, 6, 8, 12, or 16 mA in HP I/O banks and 4, 8, 12, or 16 mA in HR I/O banks.

- 5. Supported drive strengths of 2, 4, 6, 8, 12, or 16 mA in HP I/O banks and 4, 8, 12, 16, or 24 mA in HR I/O banks.

- 6. Supported drive strengths of 4, 8, 12, or 16 mA

- 7. Supported drive strengths of 4, 8, 12, 16, or 24 mA

- 8. For detailed interface specific DC voltage levels, see <u>UG471</u>: 7 Series FPGAs SelectIO Resources User Guide.

Table 12: Differential SelectIO DC Input and Output Levels

| I/O Standard |        | l      |                    | V <sub>ID</sub> <sup>(2)</sup> |        | V <sub>OCM</sub> <sup>(3)</sup> |                         |                         | V <sub>OD</sub> <sup>(4)</sup> |        |        |        |

|--------------|--------|--------|--------------------|--------------------------------|--------|---------------------------------|-------------------------|-------------------------|--------------------------------|--------|--------|--------|

| 70 Standard  | V, Min | V, Typ | V, Max             | V, Min                         | V, Typ | V, Max                          | V, Min                  | V, Typ                  | V, Max                         | V, Min | V, Typ | V, Max |

| BLVDS_25     | 0.300  | 1.200  | 1.425              | 0.100                          | -      | _                               | -                       | 1.250                   | _                              | Note 5 |        |        |

| MINI_LVDS_25 | 0.300  | 1.200  | V <sub>CCAUX</sub> | 0.200                          | 0.400  | 0.600                           | 1.000                   | 1.200                   | 1.400                          | 0.300  | 0.450  | 0.600  |

| PPDS_25      | 0.200  | 0.900  | V <sub>CCAUX</sub> | 0.100                          | 0.250  | 0.400                           | 0.500                   | 0.950                   | 1.400                          | 0.100  | 0.250  | 0.400  |

| RSDS_25      | 0.300  | 0.900  | 1.500              | 0.100                          | 0.350  | 0.600                           | 1.000                   | 1.200                   | 1.400                          | 0.100  | 0.350  | 0.600  |

| TMDS_33      | 2.700  | 2.965  | 3.230              | 0.150                          | 0.675  | 1.200                           | V <sub>CCO</sub> -0.405 | V <sub>CCO</sub> -0.300 | V <sub>CCO</sub> -0.190        | 0.400  | 0.600  | 0.800  |

- 1. V<sub>ICM</sub> is the input common mode voltage.

- 2.  $V_{ID}$  is the input differential voltage (Q  $\overline{Q}$ ).

- 3. V<sub>OCM</sub> is the output common mode voltage.

- 4.  $V_{OD}$  is the output differential voltage  $(Q \overline{Q})$ .

- V<sub>OD</sub> for BLVDS will vary significantly depending on topology and loading.

- LVDS\_25 is specified in Table 14.

- 7. LVDS is specified in Table 15.

Table 13: Complementary Differential SelectIO DC Input and Output Levels

|                 |        | V <sub>ICM</sub> <sup>(1)</sup> |        | V <sub>IC</sub> | ) <sup>(2)</sup> | V <sub>OL</sub> (3)           | V <sub>OH</sub> <sup>(4)</sup> | I <sub>OL</sub> | I <sub>OH</sub> |

|-----------------|--------|---------------------------------|--------|-----------------|------------------|-------------------------------|--------------------------------|-----------------|-----------------|

| I/O Standard    | V, Min | V, Typ                          | V, Max | V,<br>Min       | V, Max           | V, Max                        | V, Min                         | mA, Max         | mA, Min         |

| DIFF_HSTL_I     | 0.300  | 0.750                           | 1.125  | 0.100           | _                | 0.400                         | V <sub>CCO</sub> -0.400        | 8.00            | -8.00           |

| DIFF_HSTL_I_18  | 0.300  | 0.900                           | 1.425  | 0.100           | _                | 0.400                         | V <sub>CCO</sub> -0.400        | 8.00            | -8.00           |

| DIFF_HSTL_II    | 0.300  | 0.750                           | 1.125  | 0.100           | _                | 0.400                         | V <sub>CCO</sub> -0.400        | 16.00           | -16.00          |

| DIFF_HSTL_II_18 | 0.300  | 0.900                           | 1.425  | 0.100           | _                | 0.400                         | V <sub>CCO</sub> -0.400        | 16.00           | -16.00          |

| DIFF_HSUL_12    | 0.300  | 0.600                           | 0.850  | 0.100           | _                | 20% V <sub>CCO</sub>          | 80% V <sub>CCO</sub>           | 0.100           | -0.100          |

| DIFF_MOBILE_DDR | 0.300  | 0.900                           | 1.425  | 0.100           | _                | 10% V <sub>CCO</sub>          | 90% V <sub>CCO</sub>           | 0.100           | -0.100          |

| DIFF_SSTL12     | 0.300  | 0.600                           | 0.850  | 0.100           | _                | (V <sub>CCO</sub> /2) - 0.150 | $(V_{CCO}/2) + 0.150$          | 14.25           | -14.25          |

| DIFF_SSTL135    | 0.300  | 0.675                           | 1.000  | 0.100           | _                | (V <sub>CCO</sub> /2) - 0.150 | $(V_{CCO}/2) + 0.150$          | 13.0            | -13.0           |

| DIFF_SSTL135_R  | 0.300  | 0.675                           | 1.000  | 0.100           | _                | (V <sub>CCO</sub> /2) - 0.150 | $(V_{CCO}/2) + 0.150$          | 8.9             | -8.9            |

| DIFF_SSTL15     | 0.300  | 0.750                           | 1.125  | 0.100           | _                | (V <sub>CCO</sub> /2) – 0.175 | $(V_{CCO}/2) + 0.175$          | 13.0            | -13.0           |

| DIFF_SSTL15_R   | 0.300  | 0.750                           | 1.125  | 0.100           | _                | (V <sub>CCO</sub> /2) - 0.175 | $(V_{CCO}/2) + 0.175$          | 8.9             | -8.9            |

| DIFF_SSTL18_I   | 0.300  | 0.900                           | 1.425  | 0.100           | _                | (V <sub>CCO</sub> /2) - 0.470 | $(V_{CCO}/2) + 0.470$          | 8.00            | -8.00           |

| DIFF_SSTL18_II  | 0.300  | 0.900                           | 1.425  | 0.100           | _                | (V <sub>CCO</sub> /2) - 0.600 | $(V_{CCO}/2) + 0.600$          | 13.4            | -13.4           |

- 1. V<sub>ICM</sub> is the input common mode voltage.

- 2.  $V_{ID}$  is the input differential voltage  $(Q \overline{Q})$ .

- 3.  $V_{OL}$  is the single-ended low-output voltage.

- 4. V<sub>OH</sub> is the single-ended high-output voltage.

# LVDS DC Specifications (LVDS\_25)

The LVDS\_25 standard is available in the HR I/O banks. See <u>UG471</u>: 7 Series FPGAs SelectIO Resources User Guide for more information.

Table 14: LVDS\_25 DC Specifications

| Symbol             | DC Parameter                                                                                           | Conditions                                             | Min   | Тур   | Max   | Units |

|--------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------|-------|-------|-------|

| V <sub>CCO</sub>   | Supply Voltage                                                                                         |                                                        | 2.375 | 2.500 | 2.625 | V     |

| V <sub>OH</sub>    | Output High Voltage for Q and Q                                                                        | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | _     | _     | 1.675 | V     |

| V <sub>OL</sub>    | Output Low Voltage for Q and Q                                                                         | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 0.700 | _     | _     | V     |

| V <sub>ODIFF</sub> | Differential Output Voltage $(Q - \overline{Q})$ , $Q = \text{High}$                                   | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 247   | 350   | 600   | mV    |

| V <sub>OCM</sub>   | Output Common-Mode Voltage                                                                             | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 1.000 | 1.250 | 1.425 | V     |

| V <sub>IDIFF</sub> | Differential Input Voltage $(Q - \overline{Q})$ , $Q = High(\overline{Q} - Q)$ , $\overline{Q} = High$ |                                                        |       | 350   | 600   | mV    |

| V <sub>ICM</sub>   | Input Common-Mode Voltage                                                                              |                                                        |       | 1.200 | 1.425 | V     |

# LVDS DC Specifications (LVDS)

The LVDS standard is available in the HP I/O banks. See <u>UG471</u>: 7 Series FPGAs SelectIO Resources User Guide for more information.

Table 15: LVDS DC Specifications

| Symbol             | DC Parameter                                                                                                            | Conditions                                             | Min   | Тур   | Max   | Units |

|--------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------|-------|-------|-------|

| V <sub>CCO</sub>   | Supply Voltage                                                                                                          |                                                        | 1.710 | 1.800 | 1.890 | V     |

| V <sub>OH</sub>    | Output High Voltage for Q and Q                                                                                         | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | _     | _     | 1.675 | V     |

| V <sub>OL</sub>    | Output Low Voltage for Q and Q                                                                                          | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 0.825 | _     | _     | V     |

| V <sub>ODIFF</sub> | Differential Output Voltage $(Q - \overline{Q})$ , $Q = \text{High } (\overline{Q} - Q)$ , $\overline{Q} = \text{High}$ | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 247   | 350   | 600   | mV    |

| V <sub>OCM</sub>   | Output Common-Mode Voltage                                                                                              | $R_T = 100 \Omega$ across Q and $\overline{Q}$ signals | 1.000 | 1.250 | 1.425 | V     |

| V <sub>IDIFF</sub> | Differential Input Voltage $(Q - \overline{Q})$ , $Q = \text{High } (\overline{Q} - Q)$ , $\overline{Q} = \text{High}$  | Common-mode input voltage = 1.25V                      | 100   | 350   | 600   | mV    |

| V <sub>ICM</sub>   | Input Common-Mode Voltage                                                                                               | Differential input voltage = ±350 mV                   | 0.300 | 1.200 | 1.425 | V     |

# **AC Switching Characteristics**

All values represented in this data sheet are based on the speed specifications in ISE® Design Suite 14.5 v1.06 and Vivado® Design Suite 2013.1 v1.06 for the -3, -2, and -1 speed grades.

Switching characteristics are specified on a per-speed-grade basis and can be designated as Advance, Preliminary, or Production. Each designation is defined as follows:

## Advance Product Specification

These specifications are based on simulations only and are typically available soon after device design specifications are frozen. Although speed grades with this designation are considered relatively stable and conservative, some underreporting might still occur.

## **Preliminary Product Specification**

These specifications are based on complete ES (engineering sample) silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting delays is greatly reduced as compared to Advance data.

## Production Product Specification

These specifications are released once enough production silicon of a particular device family member has been characterized to provide full correlation between specifications and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to Production before faster speed grades.

## **Testing of AC Switching Characteristics**

Internal timing parameters are derived from measuring internal test patterns. All AC switching characteristics are representative of worst-case supply voltage and junction temperature conditions.

For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer and back-annotate to the simulation net list. Unless otherwise noted, values apply to all Zyng-7000 devices.

# **Speed Grade Designations**

Since individual family members are produced at different times, the migration from one category to another depends completely on the status of the fabrication process for each device. Table 16 correlates the current status of each Zynq-7000 device on a per speed grade basis.

Table 16: Zyng-7000 Device Speed Grade Designations

| Davisa  | Speed Grade Designations |             |            |  |  |  |  |

|---------|--------------------------|-------------|------------|--|--|--|--|

| Device  | Advance                  | Preliminary | Production |  |  |  |  |

| XC7Z030 |                          | -3          | -2, -1     |  |  |  |  |

| XC7Z045 |                          | -3          | -2, -1     |  |  |  |  |

| XC7Z100 |                          | -2, -1      |            |  |  |  |  |

## **Production Silicon and Software Status**

In some cases, a particular family member (and speed grade) is released to production before a speed specification is released with the correct label (Advance, Preliminary, Production). Any labeling discrepancies are corrected in subsequent speed specification releases.

Table 17 lists the production released Zynq-7000 device, speed grade, and the minimum corresponding supported speed specification version and software revisions. The software and speed specifications listed are the minimum releases required for production. All subsequent releases of software and speed specifications are valid.

Table 17: Zynq-7000 Device Production Software and Speed Specification Release

| Device  | Speed Grade Designations |                                        |    |  |  |  |

|---------|--------------------------|----------------------------------------|----|--|--|--|

| Device  | -3                       | -2                                     | -1 |  |  |  |

| XC7Z030 |                          | ISE 14.5 v1.06 and Vivado 2013.1 v1.06 |    |  |  |  |

| XC7Z045 |                          | ISE 14.5 v1.06 and Vivado 2013.1 v1.06 |    |  |  |  |

| XC7Z100 |                          |                                        |    |  |  |  |

#### Notes

## **PS Performance Characteristics**

For further design requirement details, refer to UG585, Zynq-7000 All Programmable SoC Technical Reference Manual.

Table 18: CPU Clock Domains Performance

| Comphal                                         | Clock Ratio | Description                    | S    | Speed Grade |     |       |  |

|-------------------------------------------------|-------------|--------------------------------|------|-------------|-----|-------|--|

| Symbol                                          | Clock Hatio | Description                    | -3   | -2          | -1  | Units |  |

| F <sub>CPU_6X4X_621_MAX</sub> <sup>(1)(2)</sup> |             | Maximum CPU clock frequency    | 1000 | 733         | 667 | MHz   |  |

| F <sub>CPU_3X2X_621_MAX</sub>                   | 6:2:1       | Maximum CPU_3X clock frequency | 500  | 367         | 333 | MHz   |  |

| F <sub>CPU_2X_621_MAX</sub>                     | 6:2:1       | Maximum CPU_2X clock frequency | 333  | 244         | 222 | MHz   |  |

| F <sub>CPU_1X_621_MAX</sub>                     |             | Maximum CPU_1X clock frequency | 167  | 122         | 111 | MHz   |  |

| F <sub>CPU_6X4X_421_MAX</sub> <sup>(1)</sup>    |             | Maximum CPU clock frequency    | 710  | 600         | 533 | MHz   |  |

| F <sub>CPU_3X2X_421_MAX</sub>                   | 4:2:1       | Maximum CPU_3X clock frequency | 355  | 300         | 267 | MHz   |  |

| F <sub>CPU_2X_421_MAX</sub>                     | 4.2.1       | Maximum CPU_2X clock frequency | 355  | 300         | 267 | MHz   |  |

| F <sub>CPU_1X_421_MAX</sub>                     |             | Maximum CPU_1X clock frequency | 178  | 150         | 133 | MHz   |  |

## Notes:

- The maximum frequency during BootROM execution is 500 MHz across all speed specifications.

- When the processor cores operate F<sub>CPU\_6X4X\_621\_MAX</sub> at 1 GHz (-3E speed grade), the V<sub>CCPINT</sub> minimum is 0.97V and the V<sub>CCPINT</sub> maximum is 1.03V.

Table 19: PS DDR Clock Domains Performance

| Symbol                    | Decembries                           | ,    | Units |      |       |

|---------------------------|--------------------------------------|------|-------|------|-------|

|                           | Description                          | -3   | -2    | -1   | Units |

| F <sub>DDR3_MAX</sub>     | Maximum DDR3 interface performance   | 1333 | 1066  | 1066 | Mb/s  |

| F <sub>DDR3L_MAX</sub>    | Maximum DDR3L interface performance  | 800  | 800   | 800  | Mb/s  |

| F <sub>DDR2_MAX</sub>     | Maximum DDR2 interface performance   | 800  | 800   | 800  | Mb/s  |

| F <sub>LPDDR2_MAX</sub>   | Maximum LPDDR2 interface performance | 800  | 800   | 800  | Mb/s  |

| F <sub>DDRCLK_2XMAX</sub> | Maximum DDR_2X clock frequency       | 444  | 408   | 355  | MHz   |

#### Notes:

All performance numbers apply to both internal and external V<sub>REF</sub> configurations.

Blank entries indicate a device and/or speed grade in advance or preliminary status.

# **PS Switching Characteristics**

## **Clocks**

Table 20: System Reference Clock Input Requirements

| Symbol               | Description                       | Min | Тур | Max  | Units |

|----------------------|-----------------------------------|-----|-----|------|-------|

| T <sub>JTPSCLK</sub> | PS_CLK RMS clock jitter tolerance | _   | _   | ±0.5 | %     |

| T <sub>DCPSCLK</sub> | PS_CLK duty cycle                 | 40  | _   | 60   | %     |

| T <sub>RFPSCLK</sub> | PS_CLK rise and fall time         | _   | 4   | _    | ns    |

| F <sub>PSCLK</sub>   | PS_CLK frequency                  | 30  | _   | 60   | MHz   |

#### Notes:

## Table 21: PS PLL Switching Characteristics

| Symbol                  | Description                  | 5    | Units |      |        |

|-------------------------|------------------------------|------|-------|------|--------|

|                         | Description                  | -3   | -2    | -1   | Office |

| T <sub>LOCK_PSPLL</sub> | PLL maximum lock time        | 60   | 60    | 60   | μs     |

| F <sub>PSPLL_MAX</sub>  | PLL maximum output frequency | 2000 | 1800  | 1600 | MHz    |

| F <sub>PSPLL_MIN</sub>  | PLL minimum output frequency | 780  | 780   | 780  | MHz    |

## **Resets**

## Table 22: PS Reset Requirements

| Symbol             | Description                                     | Min | Тур | Max | Units               |

|--------------------|-------------------------------------------------|-----|-----|-----|---------------------|

| T <sub>PSPOR</sub> | Required PS_POR_B assertion time <sup>(1)</sup> | 100 | _   | _   | μs                  |

| T <sub>PSRST</sub> | Required PS_SRST_B assertion time               | 3   | _   | _   | PS_CLK Clock Cycles |

#### Notes:

# **PS Configuration**

## Table 23: Processor Configuration Access Port Switching Characteristics

| Symbol              | Description                                                  | Min | Тур | Max | Units |

|---------------------|--------------------------------------------------------------|-----|-----|-----|-------|

| F <sub>PCAPCK</sub> | Maximum processor configuration access port (PCAP) frequency | -   | -   | 100 | MHz   |

<sup>1.</sup> Tested to commercial (C) and extended (E) temperature ranges only. See Temperature in Table 2.

<sup>1.</sup> PS\_POR\_B needs to be asserted low until PS supply voltages reach minimum levels.

# **DDR Memory Interfaces**

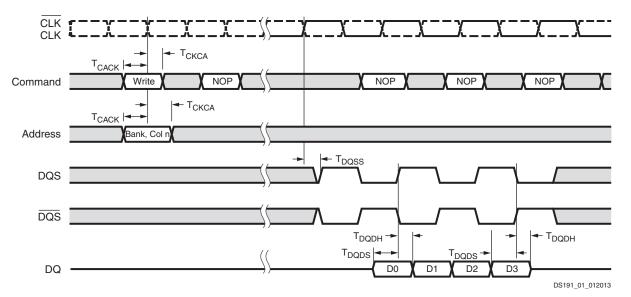

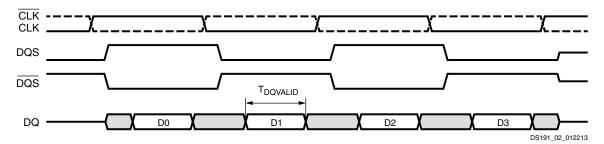

Table 24: DDR3 Interface Switching Characteristics (1333 Mb/s)(1)

| Symbol                           | Description                                           | Min   | Max  | Units           |

|----------------------------------|-------------------------------------------------------|-------|------|-----------------|

| T <sub>DQVALID</sub>             | Input data valid window                               | 500   | _    | ps              |

| T <sub>DQDS</sub> <sup>(2)</sup> | Output DQ to DQS skew                                 | 95    | _    | ps              |

| T <sub>DQDH</sub> (3)            | Output DQS to DQ skew                                 | 222   | _    | ps              |

| T <sub>DQSS</sub>                | Output clock to DQS skew                              | -0.11 | 0.08 | T <sub>CK</sub> |

| T <sub>CACK</sub> <sup>(4)</sup> | Command/address output setup time with respect to CLK | 465   | _    | ps              |

| T <sub>CKCA</sub> <sup>(5)</sup> | Command/address output hold time with respect to CLK  | 528   | _    | ps              |

#### Notes:

- 1. Recommended  $V_{CCO\_DDR} = 1.5V \pm 5\%$ .

- 2. Measurement is taken from either the rising edge of DQ that crosses V<sub>II</sub> (AC) or the falling edge of DQ that crosses V<sub>II</sub> (AC) to V<sub>RFF</sub> of DQS.

- 3. Measurement is taken from either the rising edge of DQ that crosses V<sub>IL</sub>(DC) or the falling edge of DQ that crosses V<sub>IH</sub>(DC) to V<sub>REF</sub> of DQS.

- Measurement is taken from either the rising edge of CMD/ADDR that crosses V<sub>IH</sub>(AC) or the falling edge of CMD/ADDR that crosses V<sub>IL</sub>(AC) to V<sub>REF</sub> of CLK.

- Measurement is taken from either the rising edge of CMD/ADDR that crosses V<sub>IL</sub>(DC) or the falling edge of CMD/ADDR that crosses V<sub>IH</sub>(DC) to V<sub>REF</sub> of CLK.

## Table 25: DDR3 Interface Switching Characteristics (1066 Mb/s)(1)

| Symbol                           | Description                                           | Min   | Max  | Units           |

|----------------------------------|-------------------------------------------------------|-------|------|-----------------|

| T <sub>DQVALID</sub>             | Input data valid window                               | 500   | -    | ps              |

| T <sub>DQDS</sub> (2)            | Output DQ to DQS skew                                 | 100   | _    | ps              |

| T <sub>DQDH</sub> (3)            | Output DQS to DQ skew                                 | 315   | -    | ps              |

| T <sub>DQSS</sub>                | Output clock to DQS skew                              | -0.10 | 0.10 | T <sub>CK</sub> |

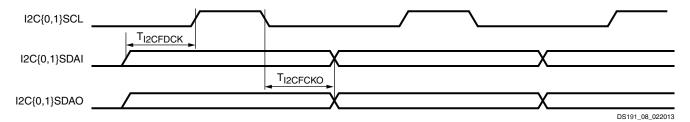

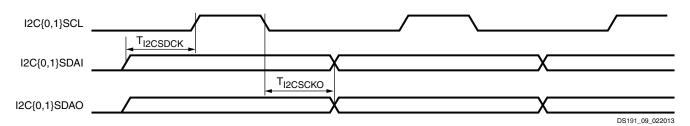

| T <sub>CACK</sub> <sup>(4)</sup> | Command/address output setup time with respect to CLK | 560   | -    | ps              |